Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                                       |

|-------------------------|--------------------------------------------------------------------------------|

| Туре                    | SC3850 Single Core                                                             |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 1GHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 576kB                                                                          |

| Voltage - I/O           | 2.50V                                                                          |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | 0°C ~ 105°C (TJ)                                                               |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8251sag1000b        |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

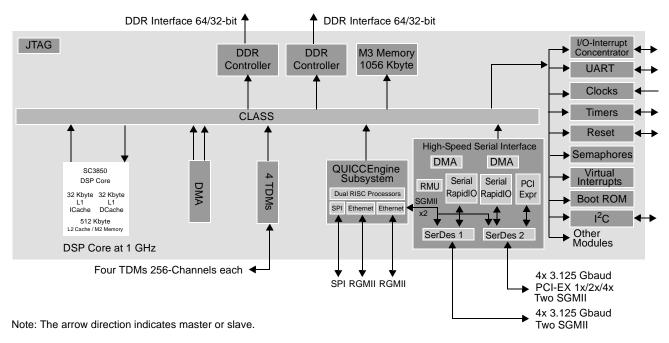

Figure 1. MSC8251 Block Diagram

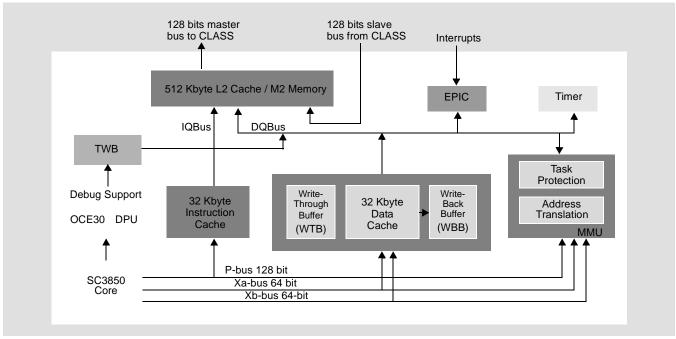

Figure 2. StarCore SC3850 DSP Subsystem Block Diagram

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|------------------------------|------------------------|--------------------|

| H25         | SXCVSS1                      | Ground                 | N/A                |

| H26         | SXCVDD1                      | Power                  | N/A                |

| H27         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |

| H28         | SR1_RXD3/SG2_RX <sup>4</sup> | I                      | SXCVDD1            |

| J1          | M2DQS1                       | I/O                    | GVDD2              |

| J2          | M2DQS1                       | I/O                    | GVDD2              |

| J3          | M2DQ10                       | I/O                    | GVDD2              |

| J4          | M2DQ11                       | I/O                    | GVDD2              |

| J5          | M2DQ14                       | I/O                    | GVDD2              |

| J6          | M2DQ23                       | I/O                    | GVDD2              |

| J7          | M2ODT0                       | 0                      | GVDD2              |

| J8          | M2A12                        | 0                      | GVDD2              |

| J9          | M2A14                        | 0                      | GVDD2              |

| J10         | VSS                          | Ground                 | N/A                |

| J11         | GVDD2                        | Power                  | N/A                |

| J12         | VSS                          | Ground                 | N/A                |

| J13         | GVDD2                        | Power                  | N/A                |

| J14         | VSS                          | Ground                 | N/A                |

| J15         | GVDD2                        | Power                  | N/A                |

| J16         | VSS                          | Ground                 | N/A                |

| J17         | GVDD2                        | Power                  | N/A                |

| J18         | VSS                          | Ground                 | N/A                |

| J19         | GVDD2                        | Power                  | N/A                |

| J20         | Reserved                     | NC                     | _                  |

| J21         | Reserved                     | NC                     | _                  |

| J22         | Reserved                     | NC                     | _                  |

| J23         | SXPVDD1                      | Power                  | N/A                |

| J24         | SXPVSS1                      | Ground                 | N/A                |

| J25         | SXCVDD1                      | Power                  | N/A                |

| J26         | SXCVSS1                      | Ground                 | N/A                |

| J27         | SXCVDD1                      | Power                  | N/A                |

| J28         | SXCVSS1                      | Ground                 | N/A                |

| K1          | VSS                          | Ground                 | N/A                |

| K2          | GVDD2                        | Power                  | N/A                |

| K3          | M2DM1                        | 0                      | GVDD2              |

| K4          | VSS                          | Ground                 | N/A                |

| K5          | GVDD2                        | Power                  | N/A                |

| K6          | M2DQ0                        | I/O                    | GVDD2              |

| K7          | VSS                          | Ground                 | N/A                |

| K8          | GVDD2                        | Power                  | N/A                |

| K9          | M2DQ5                        | I/O                    | GVDD2              |

| K10         | VSS                          | Ground                 | N/A                |

| K11         | VDD                          | Power                  | N/A                |

| K12         | VSS                          | Ground                 | N/A                |

| K13         | VDD                          | Power                  | N/A                |

| K14         | VSS                          | Ground                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| K15         | VDD                                  | Power                  | N/A                |

| K16         | VSS                                  | Ground                 | N/A                |

| K17         | VSS                                  | Ground                 | N/A                |

| K18         | VSS                                  | Ground                 | N/A                |

| K19         | VDD                                  | Power                  | N/A                |

| K20         | Reserved                             | NC                     | _                  |

| K21         | Reserved                             | NC                     | _                  |

| K22         | Reserved                             | NC                     | _                  |

| K23         | SXPVDD2                              | Power                  | N/A                |

| K24         | SXPVSS2                              | Ground                 | N/A                |

| K25         | SXCVDD2                              | Power                  | N/A                |

| K26         | SXCVSS2                              | Ground                 | N/A                |

| K27         | SXCVDD2                              | Power                  | N/A                |

| K28         | SXCVSS2                              | Ground                 | N/A                |

| L1          | M2DQ9                                | I/O                    | GVDD2              |

| L2          | M2DQ12                               | I/O                    | GVDD2              |

| L3          | M2DQ13                               | I/O                    | GVDD2              |

| L4          | M2DQS0                               | I/O                    | GVDD2              |

| L5          | M2DQS0                               | I/O                    | GVDD2              |

| L6          | M2DM0                                | 0                      | GVDD2              |

| L7          | M2DQ3                                | I/O                    | GVDD2              |

| L8          | M2DQ2                                | I/O                    | GVDD2              |

| L9          | M2DQ4                                | I/O                    | GVDD2              |

| L10         | VDD                                  | Power                  | N/A                |

| L11         | VSS                                  | Ground                 | N/A                |

| L12         | M3VDD                                | Power                  | N/A                |

| L13         | VSS                                  | Ground                 | N/A                |

| L14         | VSS                                  | Ground                 | N/A                |

| L15         | VSS                                  | Ground                 | N/A                |

| L16         | VSS                                  | Ground                 | N/A                |

| L17         | VSS                                  | Ground                 | N/A                |

| L18         | VDD                                  | Power                  | N/A                |

| L19         | VSS                                  | Ground                 | N/A                |

| L20         | Reserved                             | NC                     |                    |

| L21         | Reserved                             | NC                     |                    |

| L22         | Reserved                             | NC                     | _                  |

| <br>L23     | SR2_TXD3/PE_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD2            |

| L24         | SR2_TXD3/PE_TXD3/SG2_TX <sup>4</sup> | 0                      | SXPVDD2            |

| L25         | SXCVSS2                              | Ground                 | N/A                |

| L26         | SXCVDD2                              | Power                  | N/A                |

| L27         | SR2_RXD3/PE_RXD3/SG2_RX <sup>4</sup> |                        | SXCVDD2            |

| L28         | SR2_RXD3/PE_RXD3/SG2_RX <sup>4</sup> | <br>I                  | SXCVDD2            |

| M1          | M2DQ8                                | I/O                    | GVDD2              |

| M2          | VSS                                  | Ground                 | N/A                |

| M3          | GVDD2                                | Power                  | N/A                |

| M4          | M2DQ15                               | I/O                    | GVDD2              |

| Ball Number | Signal Name <sup>1,2</sup>           | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|--------------------------------------|------------------------|--------------------|

| N23         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N24         | SR2_TXD2/PE_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD2            |

| N25         | SXCVDD2                              | Power                  | N/A                |

| N26         | SXCVSS2                              | Ground                 | N/A                |

| N27         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD2            |

| N28         | SR2_RXD2/PE_RXD2/SG1_RX <sup>4</sup> | I                      | SXCVDD2            |

| P1          | CLKIN                                | I                      | QVDD               |

| P2          | EE0                                  | I                      | QVDD               |

| P3          | QVDD                                 | Power                  | N/A                |

| P4          | VSS                                  | Ground                 | N/A                |

| P5          | STOP_BS                              | 1                      | QVDD               |

| P6          | QVDD                                 | Power                  | N/A                |

| P7          | VSS                                  | Ground                 | N/A                |

| P8          | PLL0_AVDD <sup>9</sup>               | Power                  | VDD                |

| P9          | PLL2_AVDD <sup>9</sup>               | Power                  | VDD                |

| P10         | VSS                                  | Ground                 | N/A                |

| P11         | VDD                                  | Power                  | N/A                |

| P12         | VSS                                  | Ground                 | N/A                |

| P13         | VDD                                  | Power                  | N/A                |

| P14         | VSS                                  | Ground                 | N/A                |

| P15         | VSS                                  | Ground                 | N/A                |

| P16         | VSS                                  | Ground                 | N/A                |

| P17         | VSS                                  | Ground                 | N/A                |

| P18         | VSS                                  | Ground                 | N/A                |

| P19         | VDD                                  | Power                  | N/A                |

| P20         | Reserved                             | NC                     |                    |

| P21         | Reserved                             | NC                     |                    |

| P22         | Reserved                             | NC                     |                    |

| P23         | SXPVDD2                              | Power                  | N/A                |

| P24         | SXPVSS2                              | Ground                 | N/A                |

| P25         | SR2_PLL_AGND <sup>9</sup>            | Ground                 | SXCVSS2            |

| P26         | SR2_PLL_AVDD <sup>9</sup>            | Power                  | SXCVDD2            |

| P27         | SXCVSS2                              | Ground                 | N/A                |

| P28         | SXCVDD2                              | Power                  | N/A                |

| R1          | VSS                                  | Ground                 | N/A                |

| R2          | NMI                                  |                        | QVDD               |

| R3          | NMI_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R4          | HRESET <sup>6,7</sup>                |                        | QVDD               |

| R5          | INT_OUT <sup>6</sup>                 | 0                      | QVDD               |

| R6          | EE1                                  | 0                      | QVDD               |

| R7          | VSS                                  | Ground                 | N/A                |

| R8          | PLL1_AVDD <sup>9</sup>               | Power                  | VDD                |

| R9          | VSS                                  | Ground                 | N/A                |

| R10         | VDD                                  | Power                  | N/A                |

| R10         | VSS                                  | Non-user               | N/A                |

| R12         | VDD                                  | Power                  | N/A<br>N/A         |

| Ball Number | Signal Name <sup>1,2</sup>    | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------|------------------------|--------------------|

| R13         | VSS                           | Ground                 | N/A                |

| R14         | VDD                           | Power                  | N/A                |

| R15         | VSS                           | Ground                 | N/A                |

| R16         | VSS                           | Ground                 | N/A                |

| R17         | VSS                           | Ground                 | N/A                |

| R18         | VDD                           | Power                  | N/A                |

| R19         | VSS                           | Ground                 | N/A                |

| R20         | VSS                           | Non-user               | N/A                |

| R21         | SXPVSS2                       | Ground                 | N/A                |

| R22         | SXPVDD2                       | Power                  | N/A                |

| R23         | SR2_TXD1/PE_TXD1 <sup>4</sup> | 0                      | SXPVDD2            |

| R24         | SR2_TXD1/PE_TXD1 <sup>4</sup> | 0                      | SXPVDD2            |

| R25         | SXCVSS2                       | Ground                 | N/A                |

| R26         | SXCVDD2                       | Power                  | N/A                |

| R27         | SR2_RXD1/PE_RXD1 <sup>4</sup> | I                      | SXCVDD2            |

| R28         | SR2_RXD1/PE_RXD1 <sup>4</sup> | I                      | SXCVDD2            |

| T1          | VSS                           | Ground                 | N/A                |

| T2          | тск                           | I                      | QVDD               |

| Т3          | SRESET <sup>6,7</sup>         | I/O                    | QVDD               |

| T4          | TDI                           | I                      | QVDD               |

| T5          | VSS                           | Ground                 | N/A                |

| Т6          | TDO                           | 0                      | QVDD               |

| T7          | VSS                           | Ground                 | N/A                |

| Т8          | VSS                           | Ground                 | N/A                |

| Т9          | QVDD                          | Power                  | N/A                |

| T10         | VSS                           | Ground                 | N/A                |

| T11         | VDD                           | Power                  | N/A                |

| T12         | VSS                           | Ground                 | N/A                |

| T13         | M3VDD                         | Power                  | N/A                |

| T14         | VSS                           | Ground                 | N/A                |

| T15         | VDD                           | Power                  | N/A                |

| T16         | VSS                           | Ground                 | N/A                |

| T17         | VSS                           | Ground                 | N/A                |

| T18         | VSS                           | Ground                 | N/A                |

| T19         | VDD                           | Power                  | N/A                |

| T20         | VSS                           | Ground                 | N/A                |

| T21         | VSS                           | Non-user               | N/A                |

| T22         | SR2_IMP_CAL_RX                | I                      | SXCVDD2            |

| T23         | SXPVSS2                       | Ground                 | N/A                |

| T24         | SXPVDD2                       | Power                  | N/A                |

| T25         | SR2_REF_CLK                   | I                      | SXCVDD2            |

| T26         | SR2_REF_CLK                   | l                      | SXCVDD2            |

| T27         | Reserved                      | NC                     | —                  |

| T28         | Reserved                      | NC                     | —                  |

| U1          | M1DQ8                         | I/O                    | GVDD1              |

| U2          | VSS                           | Ground                 | N/A                |

| Ball Number | Signal Name <sup>1,2</sup>          | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------------|------------------------|--------------------|

| AB1         | M1DQS2                              | I/O                    | GVDD1              |

| AB2         | M1DQS2                              | I/O                    | GVDD1              |

| AB3         | M1DQ19                              | I/O                    | GVDD1              |

| AB4         | M1DM2                               | 0                      | GVDD1              |

| AB5         | M1DQ21                              | I/O                    | GVDD1              |

| AB6         | M1DQ22                              | I/O                    | GVDD1              |

| AB7         | M1CKE0                              | 0                      | GVDD1              |

| AB8         | M1A11                               | 0                      | GVDD1              |

| AB9         | M1A7                                | 0                      | GVDD1              |

| AB10        | M1CK2                               | 0                      | GVDD1              |

| AB11        | M1APAR_OUT                          | 0                      | GVDD1              |

| AB12        | M1ODT1                              | 0                      | GVDD1              |

| AB13        | M1APAR_IN                           | Ι                      | GVDD1              |

| AB14        | M1DQ43                              | I/O                    | GVDD1              |

| AB15        | M1DM5                               | 0                      | GVDD1              |

| AB16        | M1DQ44                              | I/O                    | GVDD1              |

| AB17        | M1DQ40                              | I/O                    | GVDD1              |

| AB18        | M1DQ59                              | I/O                    | GVDD1              |

| AB19        | M1DM7                               | 0                      | GVDD1              |

| AB20        | M1DQ60                              | I/O                    | GVDD1              |

| AB21        | VSS                                 | Ground                 | N/A                |

| AB22        | GPIO31/I2C_SDA <sup>5,8</sup>       | I/O                    | NVDD               |

| AB23        | GPIO27/TMR4/RCW_SRC0 <sup>5,8</sup> | I/O                    | NVDD               |

| AB24        | GPIO25/TMR2/RCW_SRC1 <sup>5,8</sup> | I/O                    | NVDD               |

| AB25        | GPIO24/TMR1/RCW_SRC2 <sup>5,8</sup> | I/O                    | NVDD               |

| AB26        | GPIO10/IRQ10/RC10 <sup>5,8</sup>    | I/O                    | NVDD               |

| AB27        | GPIO5/IRQ5/RC5 <sup>5,8</sup>       | I/O                    | NVDD               |

| AB28        | GPIO0/IRQ0/RC0 <sup>5,8</sup>       | I/O                    | NVDD               |

| AC1         | VSS                                 | Ground                 | N/A                |

| AC2         | GVDD1                               | Power                  | N/A                |

| AC3         | M1DQ16                              | I/O                    | GVDD1              |

| AC4         | VSS                                 | Ground                 | N/A                |

| AC5         | GVDD1                               | Power                  | N/A                |

| AC6         | M1DQ17                              | I/O                    | GVDD1              |

| AC7         | VSS                                 | Ground                 | N/A                |

| AC8         | GVDD1                               | Power                  | N/A                |

| AC9         | M1BA2                               | 0                      | GVDD1              |

| AC10        | VSS                                 | Ground                 | N/A                |

| AC11        | GVDD1                               | Power                  | N/A                |

| AC12        | M1A4                                | 0                      | GVDD1              |

| AC13        | VSS                                 | Ground                 | N/A                |

| AC14        | GVDD1                               | Power                  | N/A                |

| AC15        | M1DQ42                              | I/O                    | GVDD1              |

| AC16        | VSS                                 | Ground                 | N/A                |

| AC17        | GVDD1                               | Power                  | N/A                |

| AC18        | M1DQ58                              | I/O                    | GVDD1              |

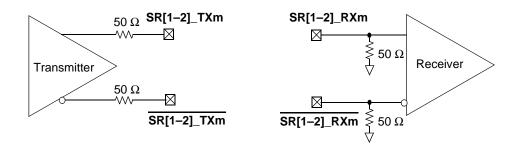

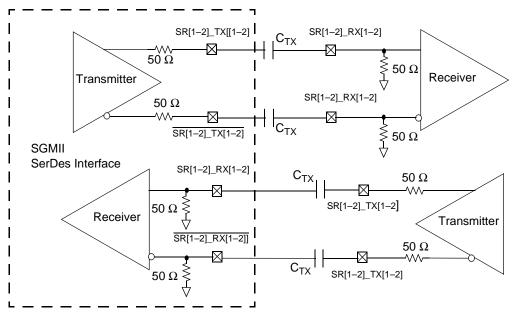

# 2.5.2.3 SerDes Transmitter and Receiver Reference Circuits

Figure 6 shows the reference circuits for SerDes data lane transmitter and receiver.

Note: The [1–2] indicates the specific SerDes Interface (1 or 2) and the m indicates the specific channel within that interface (0,1,2,3). Actual signals are assigned by the HRCW assignments at reset (see **Chapter 5**, *Reset* in the reference manual for details)

Figure 6. SerDes Transmitter and Receiver Reference Circuits

# 2.5.3 DC-Level Requirements for SerDes Interfaces

The following subsections define the DC-level requirements for the SerDes reference clocks, the PCI Express data lines, the Serial RapidIO data lines, and the SGMII data lines.

# 2.5.3.1 DC-Level Requirements for SerDes Reference Clocks

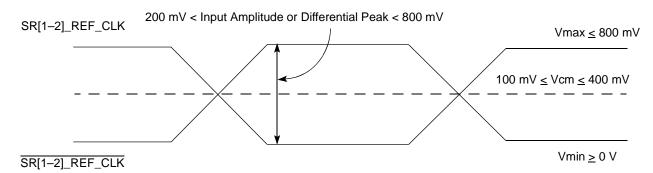

The DC-level requirement for the SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs, as described below:

- Differential Mode

- The input amplitude of the differential clock must be between 400 mV and 1600 mV differential peak-peak (or between 200 mV and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing of less than 800 mV and greater than 200 mV. This requirement is the same for both external DC-coupled or AC-coupled connection.

- For an external DC-coupled connection, the maximum average current requirements sets the requirement for average voltage (common mode voltage) as between 100 mV and 400 mV. Figure 7 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

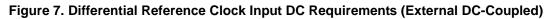

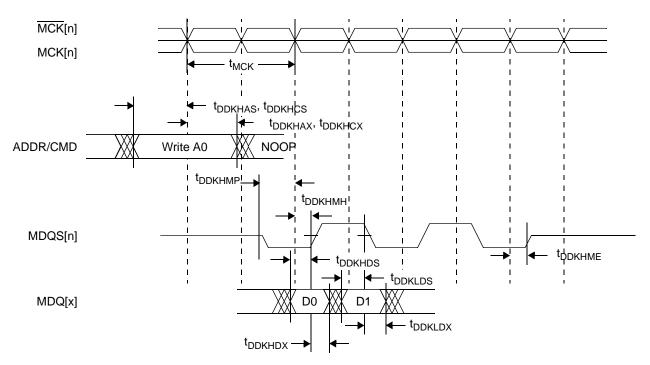

Figure 11 shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 11. DDR2 and DDR3 SDRAM Interface Input Timing Diagram

## 2.6.1.2 DDR SDRAM Output AC Timing Specifications

Table 21 provides the output AC timing specifications for the DDR SDRAM interface.

| Parameter                                                                                   | Symbol <sup>1</sup>                         | Min                          | Max                          | Unit     | Notes |

|---------------------------------------------------------------------------------------------|---------------------------------------------|------------------------------|------------------------------|----------|-------|

| MCK[n] cycle time                                                                           | t <sub>MCK</sub>                            | 2.5                          | 5                            | ns       | 2     |

| ADDR/CMD output setup with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate     | <sup>t</sup> DDKHAS                         | 0.917<br>1.10                |                              | ns<br>ns | 3     |

| ADDR/CMD output hold with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate      | <sup>t</sup> ddkhax                         | 0.767<br>1.02                |                              | ns<br>ns | 3     |

| MCSn output setup with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate         | <sup>t</sup> DDKHCS                         | 0.917<br>1.10                |                              | ns<br>ns | 3     |

| MCSn output hold with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate          | <sup>t</sup> DDKHCX                         | 0.767<br>1.02                |                              | ns<br>ns | 3     |

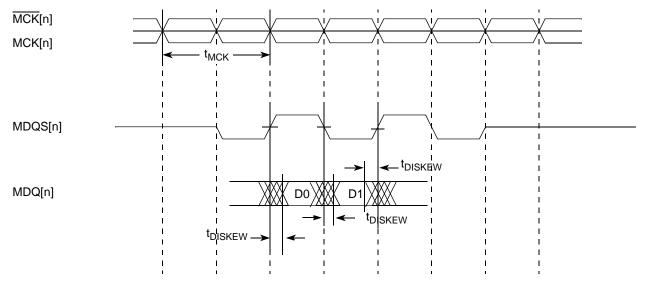

| MCK to MDQS Skew<br>• 800 MHz data rate<br>• 667 MHz data rate                              | t <sub>DDKHMH</sub>                         | -0.4<br>-0.6                 | 0.375<br>0.6                 | ns       | 4     |

| MDQ/MECC/MDM output setup with respect to MDQS <ul> <li>800 MHz</li> <li>667 MHz</li> </ul> | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 300<br>375                   |                              | ps<br>ps | 5     |

| MDQ/MECC/MDM output hold with respect to MDQS<br>• 800 MHz<br>• 667 MHz                     | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 300<br>375                   |                              | ps<br>ps | 5     |

| MDQS preamble                                                                               | t <sub>DDKHMP</sub>                         | $-0.9 	imes t_{MCK}$         |                              | ns       | _     |

| MDQS postamble                                                                              | t <sub>DDKHME</sub>                         | $-0.4 \times t_{\text{MCK}}$ | $-0.6 \times t_{\text{MCK}}$ | ns       | —     |

### Table 21. DDR SDRAM Output AC Timing Specifications

### Table 21. DDR SDRAM Output AC Timing Specifications (continued)

|        |          | Parameter                                                                                                                                                                                                                                                                                                | Symbol <sup>1</sup>                                                                                     | Min                                                                                                                    | Max                                                                                                                     | Unit                                                      | Notes                              |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------|

| Notes: | 1.       | The symbols used for timing specifications for<br>inputs and t <sub>(first two letters of functional block)</sub> (refere<br>(DD) from the rising or falling edge of the refer<br>t <sub>DDKHAS</sub> symbolizes DDR timing (DD) for the<br>(A) are setup (S) or output valid time. Also, t <sub>D</sub> | ence)(state)(signal)(s<br>erence clock (KH<br>e time t <sub>MCK</sub> mem<br><sub>DKLDX</sub> symbolize | <sub>state)</sub> for outputs. Output<br>I or KL) until the output<br>ory clock reference (K<br>as DDR timing (DD) for | ut hold time can be rea<br>it went invalid (AX or I<br>) goes from the high (I                                          | ad as DDR<br>DX). For exa<br>H) state unt                 | timing<br>ample,<br>til outputs    |

|        | 2.<br>3. | <u> </u>                                                                                                                                                                                                                                                                                                 |                                                                                                         |                                                                                                                        |                                                                                                                         |                                                           |                                    |

|        | 4.       | Note that t <sub>DDKHMH</sub> follows the symbol converting from the rising edge of the MCK(n) clock (KH the DQSS override bits in the TIMING_CFG_CLK_CNTL register. The timing parameters adjustment value. See the <i>MSC8251 Refere</i> enabled by use of these bits.                                 | ntions described<br>) until the MDQS<br>_2 register. This<br>listed in the table                        | in note 1. For example<br>signal is valid (MH). t<br>will typically be set to<br>assume that these tw                  | e, t <sub>DDKHMH</sub> describes t<br><sub>DDKHMH</sub> can be modifi<br>the same delay as the<br>vo parameters have be | the DDR timed through<br>clock adjuster<br>clock adjuster | control of<br>st in the<br>he same |

|        | 5.       | Determined by maximum possible skew betw<br>(MECC), or data mask (MDM). The data stro                                                                                                                                                                                                                    |                                                                                                         | · · ·                                                                                                                  |                                                                                                                         | · · · ·                                                   |                                    |

|        | 6.       | At recommended operating conditions with V                                                                                                                                                                                                                                                               | / <sub>DDDDR</sub> (1.5 V or                                                                            | 1,8 V) ± 5%.                                                                                                           |                                                                                                                         |                                                           |                                    |

**Note:** For the ADDR/CMD setup and hold specifications in Table 21, it is assumed that the clock control register is set to adjust the memory clocks by <sup>1</sup>/<sub>2</sub> applied cycle.

Figure 12 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement ( $t_{DDKHMH}$ ).

Figure 12. MCK to MDQS Timing

Figure 13 shows the DDR SDRAM output timing diagram.

Figure 13. DDR SDRAM Output Timing

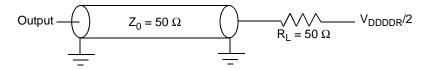

Figure 14 provides the AC test load for the DDR2 and DDR3 controller bus.

Figure 14. DDR2 and DDR3 Controller Bus AC Test Load

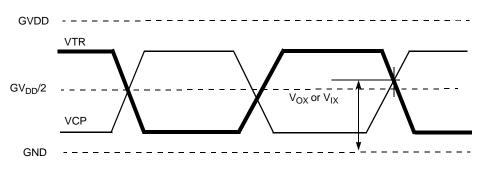

## 2.6.1.3 DDR2 and DDR3 SDRAM Differential Timing Specifications

This section describes the DC and AC differential timing specifications for the DDR2 and DDR3 SDRAM controller interface. Figure 15 shows the differential timing specification.

Figure 15. DDR2 and DDR3 SDRAM Differential Timing Specifications

Note: VTR specifies the true input signal (such as MCK or MDQS) and VCP is the complementary input signal (such as  $\overline{MCK}$  or  $\overline{MDQS}$ ).

#### **Electrical Characteristics**

Table 22 provides the DDR2 differential specifications for the differential signals MDQS/MDQS and MCK/MCK.

#### Table 22. DDR2 SDRAM Differential Electrical Characteristics

| Parameter                                  | Symbol            | Min                | Мах                | Unit |

|--------------------------------------------|-------------------|--------------------|--------------------|------|

| Input AC differential cross-point voltage  | V <sub>IXAC</sub> | 0.5 × GVDD – 0.175 | 0.5 × GVDD + 0.175 | V    |

| Output AC differential cross-point voltage | V <sub>OXAC</sub> | 0.5 × GVDD – 0.125 | 0.5 × GVDD + 0.125 | V    |

Table 23 provides the DDR3 differential specifications for the differential signals MDQS/MDQS and MCK/MCK.

### Table 23. DDR3 SDRAM Differential Electrical Characteristics

| Parameter                                  | Symbol            | Min                | Мах                | Unit |

|--------------------------------------------|-------------------|--------------------|--------------------|------|

| Input AC differential cross-point voltage  | V <sub>IXAC</sub> | 0.5 × GVDD – 0.150 | 0.5 × GVDD + 0.150 | V    |

| Output AC differential cross-point voltage | V <sub>OXAC</sub> | 0.5 × GVDD – 0.115 | 0.5 × GVDD + 0.115 | V    |

# 2.6.2 HSSI AC Timing Specifications

The following subsections define the AC timing requirements for the SerDes reference clocks, the PCI Express data lines, the Serial RapidIO data lines, and the SGMII data lines.

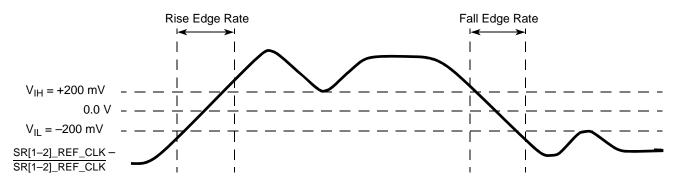

## 2.6.2.1 AC Requirements for SerDes Reference Clock

Table 24 lists AC requirements for the SerDes reference clocks.

Note: Specifications are valid at the recommended operating conditions listed in Table 3.

| Parameter                                                                                                                   | Symbol                                 | Min  | Typical | Max  | Units | Notes |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------|------|-------|-------|--|--|--|

| SR[1-2]_REF_CLK/SR[1-2]_REF_CLK<br>frequency range                                                                          | <sup>t</sup> CLK_REF                   | -    | 100/125 | _    | MHz   | 1     |  |  |  |

| SR[1–2]_REF_CLK/SR[1–2]_REF_CLK clock<br>frequency tolerance                                                                | <sup>t</sup> CLK_TOL                   | -350 | _       | 350  | ppm   | _     |  |  |  |

| SR[1–2]_REF_CLK/SR[1–2]_REF_CLK<br>reference clock duty cycle (measured at 1.6 V)                                           | t <sub>CLK_DUTY</sub>                  | 40   | 50      | 60   | %     | _     |  |  |  |

| SR[1–2]_REF_CLK/SR[1–2]_REF_CLK max deterministic peak-peak jitter at 10 <sup>-6</sup> BER                                  | <sup>t</sup> clk_dj                    | -    | _       | 42   | ps    | _     |  |  |  |

| SR[1–2]_REF_CLK/SR[1–2]_REF_CLK total reference clock jitter at 10 <sup>-6</sup> BER (peak-to-peak jitter at ref_clk input) | <sup>t</sup> clk_tj                    | _    | _       | 86   | ps    | 2     |  |  |  |

| SR[1–2]_REF_CLK/SR[1–2]_REF_CLK<br>rising/falling edge rate                                                                 | t <sub>CLKRR</sub> /t <sub>CLKFR</sub> | 1    | —       | 4    | V/ns  | 3     |  |  |  |

| Differential input high voltage                                                                                             | V <sub>IH</sub>                        | 200  | —       | —    | mV    | 4     |  |  |  |

| Differential input low voltage                                                                                              | V <sub>IL</sub>                        | —    | —       | -200 | mV    | 4     |  |  |  |

| Rising edge rate (SR[1–2]_REF_CLK) to falling<br>edge rate (SR[1–2]_REF_CLK) matching                                       | Rise-Fall<br>Matching                  | —    | —       | 20   | %     | 5, 6  |  |  |  |

### Table 24. SR[1–2]\_REF\_CLK and SR[1–2]\_REF\_CLK Input Clock Requirements

# Table 24. SR[1–2]\_REF\_CLK and SR[1–2]\_REF\_CLK Input Clock Requirements (continued)

|        |    | Parameter                                                                                                                                                                                                                                                                                                                | Symbol                                                              | Min                                                     | Typical                                                           | Мах                              | Units        | Notes                   |

|--------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|--------------|-------------------------|

| Notes: | 1. | Caution: Only 100 and 125 have b                                                                                                                                                                                                                                                                                         | een tested. Other va                                                | alues will not wo                                       | ork correctly with                                                | n the rest of the                | system.      |                         |

|        | 2. | Limits from PCI Express CEM Rev                                                                                                                                                                                                                                                                                          | 1.0a                                                                |                                                         |                                                                   |                                  |              |                         |

|        | 3. | <u>Measured from -200 mV to +200 mV on the differential waveform (derived from SR[1-2]_REF_CLK minus</u><br><u>SR[1-2]_REF_CLK</u> ). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV<br>measurement window is centered on the differential zero crossing. See Figure 16. |                                                                     |                                                         |                                                                   |                                  | 0 mV         |                         |

|        | 4. | Measurement taken from different                                                                                                                                                                                                                                                                                         | al waveform                                                         | -                                                       | -                                                                 |                                  |              |                         |

|        | 5. | Measurement taken from single-er                                                                                                                                                                                                                                                                                         | nded waveform                                                       |                                                         |                                                                   |                                  |              |                         |

|        | 6. | Matching applies to rising edge for<br>200 mV window centered on the m<br>median cross point is used to calc<br>rise edge rate of SR[1–2]_REF_CI<br>difference should not exceed 20%                                                                                                                                     | edian cross point w<br>ulate the voltage thre<br>.K should be compa | here SR[1–2]_F<br>esholds that the<br>red to the fall e | REF_CLK rising<br>oscilloscope us<br>dge rate of SR[ <sup>2</sup> | meets SR[1–2<br>ses for the edge | ]_REF_CLK fa | alling. The<br>ons. The |

Figure 16. Differential Measurement Points for Rise and Fall Time

#### Figure 17. Single-Ended Measurement Points for Rise and Fall Time Matching

# 2.6.2.2 PCI Express AC Physical Layer Specifications

The AC requirements for PCI Express implementations have separate requirements for the Tx and Rx lines. The MSC8251 supports a 2.5 Gbps PCI Express interface defined by the *PCI Express Base Specification, Revision 1.0a.* The transmitter specifications are defined in Table 25 and the receiver specifications are defined in Table 26. The parameters are specified at the component pins. the AC timing specifications do not include REF\_CLK jitter.

Note: Specifications are valid at the recommended operating conditions listed in Table 3.

### Table 25. PCI Express (2.5 Gbps) Differential Transmitter (Tx) Output AC Specifications

| Parameter                                                                     | Symbol                                       | Min    | Typical | Мах    | Units | Notes |

|-------------------------------------------------------------------------------|----------------------------------------------|--------|---------|--------|-------|-------|

| Unit interval                                                                 | UI                                           | 399.88 | 400.00  | 400.12 | ps    | 1     |

| Minimum Tx eye width                                                          | T <sub>TX-EYE</sub>                          | 0.70   | _       | _      | UI    | 2, 3  |

| Maximum time between the jitter median and maximum deviation from the median. | T <sub>TX-EYE-MEDIAN-</sub><br>to-MAX-JITTER | _      | _       | 0.15   | UI    | 3, 4  |

| AC coupling capacitor                                                         | C <sub>TX</sub>                              | 75     | _       | 200    | nF    | 5     |

Notes: 1. Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. No test load is necessarily associated with this value.

2. The maximum transmitter jitter can be derived as  $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$  UI.

3. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 8 and measured over any 250 consecutive Tx UIs. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the transmitter collected over any 250 consecutive Tx UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total Tx jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. Jitter is defined as the measurement variation of the crossing points (V<sub>TX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data.

4. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI.

5. All transmitters shall be AC-coupled. The AC coupling is required either within the media or within the transmitting component itself. The SerDes transmitter does not have built-in Tx capacitance. An external AC coupling capacitor is required.

### Table 26. PCI Express (2.5 Gbps) Differential Receiver (Rx) Input AC Specifications

| Parameter                                                                     | Symbol                                       | Min    | Typical | Мах    | Units | Notes   |

|-------------------------------------------------------------------------------|----------------------------------------------|--------|---------|--------|-------|---------|

| Unit Interval                                                                 | UI                                           | 399.88 | 400.00  | 400.12 | ps    | 1       |

| Minimum receiver eye width                                                    | T <sub>RX-EYE</sub>                          | 0.4    | —       | —      | UI    | 2, 3, 4 |

| Maximum time between the jitter median and maximum deviation from the median. | T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | _      | _       | 0.3    | UI    | 3, 4, 5 |

Notes: 1. Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. No test load is necessarily associated with this value.

2. The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as  $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$  UI.

3. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 8 should be used as the Rx device when taking measurements. If the clocks to the Rx and Tx are not derived from the same reference clock, the Tx UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

4. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the Rx and Tx are not derived from the same reference clock, the Tx UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

5. Jitter is defined as the measurement variation of the crossing points (V<sub>RX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI. It is recommended that the recovered Tx UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

# 2.6.5 Ethernet Timing

This section describes the AC electrical characteristics for the Ethernet interface.

There are programmable delay units (PDU) that should be programmed differently for each interface to meet timing. There is a general configuration register 4 (GCR4) used to configure the timing. For additional information, see the *MSC8251 Reference Manual*.

# 2.6.5.1 Management Interface Timing

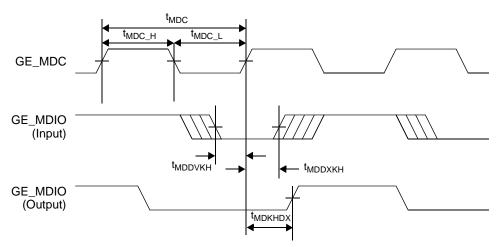

Table 33 lists the timer input Ethernet controller management interface timing specifications shown in Figure 24.

| Table 33. Ethernet Controller Management Interface Tir | nina |

|--------------------------------------------------------|------|

|--------------------------------------------------------|------|

| Characteristics                          | Symbol              | Min | Max | Unit |

|------------------------------------------|---------------------|-----|-----|------|

| GE_MDC frequency                         | f <sub>MDC</sub>    | —   | 2.5 | MHz  |

| GE_MDC period                            | t <sub>MDC</sub>    | 400 | —   | ns   |

| GE_MDC clock pulse width high            | t <sub>MDC_H</sub>  | 160 | _   | ns   |

| GE_MDC clock pulse width low             | t <sub>MDC_L</sub>  | 160 | _   | ns   |

| GE_MDC to GE_MDIO delay <sup>2</sup>     | t <sub>mdkhdx</sub> | 10  | 70  | ns   |

| GE_MDIO to GE_MDC rising edge setup time | t <sub>mddvkh</sub> | 20  | _   | ns   |

| GE_MDC rising edge to GE_MDIO hold time  | t <sub>mddxkh</sub> | 0   | _   | ns   |

Program the GE\_MDC frequency (f<sub>MDC</sub>) to a maximum value of 2.5 MHz (400 ns period for t<sub>MDC</sub>). The value depends on the source clock and configuration of MIIMCFG[MCS] and UPSMR[MDCP]. For example, for a source clock of 400 MHz to achieve f<sub>MDC</sub> = 2.5 MHz, program MIIMCFG[MCS] = 0x4 and UPSMR[MDCP] = 0. See the *MSC8251 Reference Manual* for configuration details.

2. The value depends on the source clock. For example, for a source clock of 267 MHz, the delay is 70 ns. For a source clock of 333 MHz, the delay is 58 ns.

Figure 24. MII Management Interface Timing

# 2.6.5.2 RGMII AC Timing Specifications

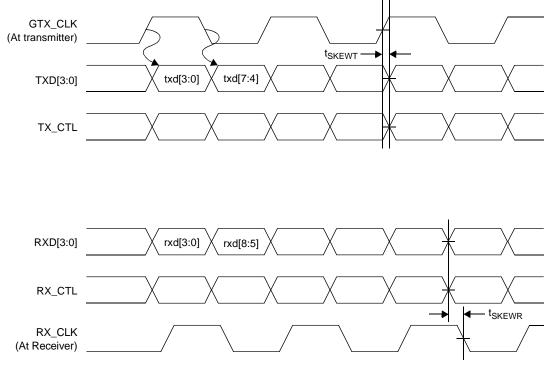

Table 34 presents the RGMII AC timing specifications for applications requiring an on-board delayed clock.

## Table 34. RGMII at 1 Gbps<sup>2</sup> with On-Board Delay<sup>3</sup> AC Timing Specifications

| Parameter/Condition Data to clock output skew (at transmitter) <sup>4</sup> |                      | Symbol                                                                                                                                                                                                                                                                                       | Min                | Тур         | Max         | Unit       |          |

|-----------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------|-------------|------------|----------|

|                                                                             |                      | t <sub>SKEWT</sub>                                                                                                                                                                                                                                                                           | -0.5               | —           | 0.5         | ns         |          |

| Data to cl                                                                  | ock                  | input skew (at receiver) 4                                                                                                                                                                                                                                                                   | t <sub>SKEWR</sub> | 1           | _           | 2.6        | ns       |

| Notes:                                                                      | 1.<br>2.<br>3.<br>4. | At recommended operating conditions with $V_{DDIO}$ of 2.5 V ± 5%.<br>RGMII at 100 Mbps support is guaranteed by design.<br>Program GCR4 as 0x00000000.<br>This implies that PC board design requires clocks to be routed such the less than 2.0 ns is added to the associated clock signal. | nat an additiona   | I trace del | ay of great | er than 1. | 5 ns and |

Table 35 presents the RGMII AC timing specification for applications required non-delayed clock on board.

| Parameter/Condition                                                                 |                                                                                                                                                                                                                                                                                                                                      | Symbol             | Min  | Тур | Мах  | Unit |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-----|------|------|

| Data to clock output skew (at transmitter) <sup>4</sup>                             |                                                                                                                                                                                                                                                                                                                                      | t <sub>SKEWT</sub> | -2.6 | _   | -1.0 | ns   |

| Data to clock input skew (at receiver) <sup>4</sup> t <sub>SKEWR</sub> -0.5 - 0.5 r |                                                                                                                                                                                                                                                                                                                                      |                    |      | ns  |      |      |

| Notes:                                                                              | <ol> <li>Notes: 1. At recommended operating conditions with V<sub>DDIO</sub> of 2.5 V ± 5%.</li> <li>2. RGMII at 100 Mbps support is guaranteed by design.</li> <li>3. GCR4 should be programmed as 0x000CC330.</li> <li>4. This implies that PC board design requires clocks to be routed with no additional trace delay</li> </ol> |                    |      |     |      |      |

Figure 25 shows the RGMII AC timing and multiplexing diagrams.

Figure 25. RGMII AC Timing and Multiplexing

# 2.6.7 Asynchronous Signal Timing

Table 35 lists the asynchronous signal timing specifications.

| Characteristics                                              | Symbol Type Min  |              | Min                   |  |  |

|--------------------------------------------------------------|------------------|--------------|-----------------------|--|--|

| Input                                                        | t <sub>IN</sub>  | Asynchronous | One CLKIN cycle       |  |  |

| Output                                                       | t <sub>out</sub> | Asynchronous | Application dependent |  |  |

| Note: Input value relevant for EE0, IRQ[15–0], and NMI only. |                  |              |                       |  |  |

The following interfaces use the specified asynchronous signals:

• *GPIO*. Signals GPIO[31–0], when used as GPIO signals, that is, when the alternate multiplexed special functions are not selected.

**Note:** When used as a general purpose input (GPI), the input signal should be driven until it is acknowledged by the MSC8251 device, that is, when the expected input value is read from the GPIO data register.

- *EE port.* Signals EE0, EE1.

- *Boot function*. Signal STOP\_BS.

- $I^2C$  interface. Signals I2C\_SCL and I2C\_SDA.

- Interrupt inputs. Signals IRQ[15–0] and NMI.

- Interrupt outputs. Signals INT\_OUT and NMI\_OUT (minimum pulse width is 32 ns).

# 2.6.8 JTAG Signals

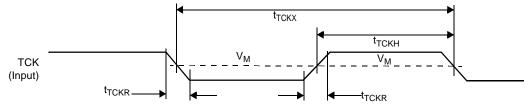

Table 38 lists the JTAG timing specifications shown in Figure 29 through Figure 32.

#### Table 38. JTAG Timing

| Characteristics                                                                              | Symbol              | All frequencies |      | Unit |

|----------------------------------------------------------------------------------------------|---------------------|-----------------|------|------|

| Characteristics                                                                              |                     | Min             | Max  | Unit |

| TCK cycle time                                                                               | t <sub>тскх</sub>   | 36.0            | —    | ns   |

| TCK clock high phase measured at $V_{M} = V_{DDIO}/2$                                        | t <sub>тскн</sub>   | 15.0            | —    | ns   |

| Boundary scan input data setup time                                                          | t <sub>BSVKH</sub>  | 0.0             | —    | ns   |

| Boundary scan input data hold time                                                           | t <sub>BSXKH</sub>  | 15.0            | —    | ns   |

| TCK fall to output data valid                                                                | t <sub>TCKHOV</sub> | _               | 20.0 | ns   |

| TCK fall to output high impedance                                                            | t <sub>TCKHOZ</sub> | _               | 24.0 | ns   |

| TMS, TDI data setup time                                                                     | t <sub>TDIVKH</sub> | 0.0             | —    | ns   |

| TMS, TDI data hold time                                                                      | t <sub>TDIXKH</sub> | 5.0             | —    | ns   |

| TCK fall to TDO data valid                                                                   | t <sub>TDOHOV</sub> | —               | 10.0 | ns   |

| TCK fall to TDO high impedance                                                               | t <sub>TDOHOZ</sub> |                 | 12.0 | ns   |

| TRST assert time                                                                             | t <sub>TRST</sub>   | 100.0           | _    | ns   |

| Note: All timings apply to OnCE module data transfers as well as any other transfers via the | JTAG port.          |                 |      |      |

Figure 29 shows the test clock input timing diagram.

Figure 29. Test Clock Input Timing

# 3 Hardware Design Considerations

The following sections discuss areas to consider when the MSC8251 device is designed into a system.

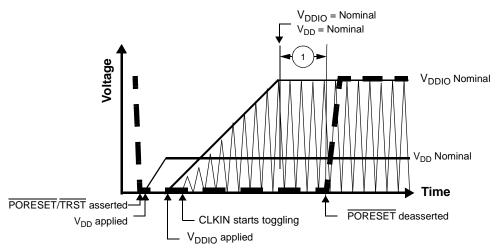

# 3.1 Power Supply Ramp-Up Sequence

The following subsections describe the required device initialization sequence.

# 3.1.1 Clock, Reset, and Supply Coordination

Starting the device requires coordination between several inputs including: clock, reset, and power supplies. follow this guidelines when starting up an MSC8251 device:

- <u>PORESET</u> and <u>TRST</u> must be asserted externally for the duration of the supply ramp-up, using the V<sub>DDIO</sub> supply. TRST deassertion does not have to be synchronized with <u>PORESET</u> deassertion. However, <u>TRST</u> must be deasserted before normal operation begins to ensure correct functionality of the device.

- CLKIN should toggle at least 32 cycles before PORESET deassertion to guarantee correct device operation. The 32 cycles should only be counted from the time after V<sub>DDIO</sub> reaches its nominal value (see timing 1 in Figure 33).

- CLKIN should either be stable low during ramp-up of V<sub>DDIO</sub> supply (and start its swings after ramp-up) or should swing within V<sub>DDIO</sub> range during V<sub>DDIO</sub> ramp-up, so its amplitude grows as V<sub>DDIO</sub> grows during ramp-up.

Figure 33 shows a sequence in which  $V_{DDIO}$  ramps-up after  $V_{DD}$  and CLKIN begins to toggle with the raise of  $V_{DDIO}$  supply.

Figure 33. Supply Ramp-Up Sequence with V<sub>DD</sub> Ramping Before V<sub>DDIO</sub> and CLKIN Starting With V<sub>DDIO</sub>

Note: For details on power-on reset flow and duration, see the Reset chapter in the MSC8251 Reference Manual.

# 3.1.2 Power-On Ramp Time

This section describes the AC electrical specification for the power-on ramp rate requirements for all voltage supplies (including GVDD/SXPVDD/SXCVDD/QVDD/GVDD/NVDD, all VDD supplies, MVREF, and all AVDD supplies). Controlling the power-on ramp time is required to avoid falsely triggering the ESD circuitry. Table 39 defines the power supply ramp time specification.

### Table 39. Power Supply Ramp Rate

|                             | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min                          | Max          | Unit       |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------|------------|

| Required ramp rate. —       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |              | V/s        |

| Notes: 1.<br>2.<br>3.<br>4. | Ramp time is specified as a linear ramp from 10% to 90% of nominal voltage of the specific<br>non-linear (for example, exponential), the maximum rate of change from 200 to 500 mV is th<br>might falsely trigger the ESD circuitry.<br>Required over the full recommended operating temperature range (see Table 3).<br>All supplies must be at their stable values within 50 ms.<br>The GVDD pins can be held low on the application board at powerup. If GVDD is not held low<br>voltage level that depends on the board-level impedance-to-ground. If the impedance is hig<br>theoretically, GVDD can rise up close to the VDD levels. | e most critic<br>ow, then GV | al because f | this range |

# 3.1.3 Power Supply Guidelines

Use the following guidelines for power-up sequencing:

- Couple M3VDD with the VDD power rail using an extremely low impedance path.

- Couple inputs PLL1\_AVDD, PLL2\_AVDD and PLL3\_AVDD with the VDD power rail using an RC filter (see Figure 37).

- There is no dependency in power-on/power-off sequence between the GVDD1, GVDD2, NVDD, and QVDD power rails.

- Couple inputs M1VREF and M2VREF with the GVDD1 and GVDD2 power rails, respectively. They should rise at the same time as or after their respective power rail.

- There is no dependency between RapidIO supplies: SXCVDD1, SXCVDD2, SXPVDD1 and SXPVDD2 and other MSC8251 supplies in the power-on/power-off sequence.

- Couple inputs SR1\_PLL\_AVDD and SR2\_PLL\_AVDD with SXCVDD1 and SXCVDD2 power rails, respectively, using an RC filter (see Figure 38).

External voltage applied to any input line must not exceed the I/O supply voltage related to this line by more than 0.6 V at any time, including during power-up. Some designs require pull-up voltages applied to selected input lines during power-up for configuration purposes. This is an acceptable exception to the rule during start-up. However, each such input can draw up to 80 mA per input pin per MSC8251 device in the system during power-up. An assertion of the inputs to the high voltage level before power-up should be with slew rate less than 4 V/ns.

The device power rails should rise in the following sequence:

1. VDD (and all coupled supplies)

# 3.3 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to compute the resistor value:

Rterm = Rim - Rbuf

where Rim = trace characteristic impedance

Rbuf = clock buffer internal impedance.

# 3.4 SGMII AC-Coupled Serial Link Connection Example

Figure 39 shows an example of a 4-wire AC-coupled serial link connection. For additional layout suggestions, see *AN3556 MSC815x High Speed Serial Interface Hardware Design Considerations*, available on the Freescale website or from your local sales office or representative.

Figure 39. 4-Wire AC-Coupled SGMII Serial Link Connection Example

#### 3.5.1 **DDR Memory Related Pins**

This section discusses the various scenarios that can be used with either of the MSC8251 DDR ports.

The signal names in Table 40, Table 41 and Table 42 are generic names for a DDR SDRAM interface. For actual pin Note: names refer to Table 1.

#### 3.5.1.1 **DDR Interface Is Not Used**

| Signal Name              | Pin Connection |

|--------------------------|----------------|

| MDQ[0-63]                | NC             |

| MDQS[7-0]                | NC             |

| MDQS[7-0]                | NC             |

| MA[15–0]                 | NC             |

| MCK[0-2]                 | NC             |

| MCK[0-2]                 | NC             |

| MCS[1-0]                 | NC             |

| MDM[7-0]                 | NC             |

| MBA[2-0]                 | NC             |

| MCAS                     | NC             |

| MCKE[1-0]                | NC             |

| MODT[1-0]                | NC             |

| MMDIC[1-0]               | NC             |

| MRAS                     | NC             |

| MWE                      | NC             |

| MECC[7-0]                | NC             |

| MDM8                     | NC             |

| MDQS8                    | NC             |

| MDQS8                    | NC             |

| MAPAR_OUT                | NC             |

| MAPAR_IN                 | NC             |

| MVREF <sup>3</sup>       | NC             |

| GVDD1/GVDD2 <sup>3</sup> | NC             |

#### Table 40. Connectivity of DDR Related Pins When the DDR Interface Is Not Used

Clocks and General Configuration Registers chapters in the MSC8251 Reference Manual for details.

For MSC8251 Revision 1 silicon, these pins were connected to GND. For newer revisions of the MSC8251, connecting these 3. pins to GND increases device power consumption.