# E·XFL

### NXP USA Inc. - SPAKDSP311VL150 Datasheet

Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                |

| Туре                    | Fixed Point                                                             |

| Interface               | Host Interface, SSI, SCI                                                |

| Clock Rate              | 150MHz                                                                  |

| Non-Volatile Memory     | ROM (576B)                                                              |

| On-Chip RAM             | 384kB                                                                   |

| Voltage - I/O           | 3.30V                                                                   |

| Voltage - Core          | 1.80V                                                                   |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                      |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 196-LBGA                                                                |

| Supplier Device Package | 196-LBGA (15x15)                                                        |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/spakdsp311vl150 |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

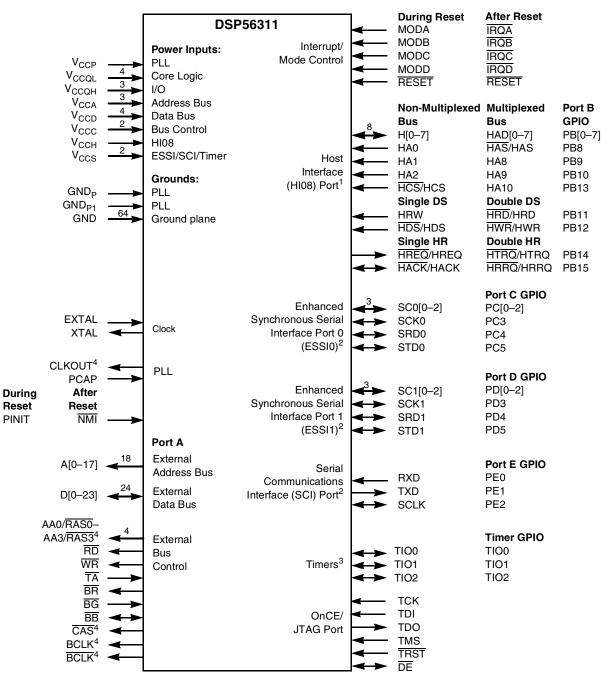

# Signals/Connections

The DSP56311 input and output signals are organized into functional groups as shown in **Table 1-1**. **Figure 1-1** diagrams the DSP56311 signals by functional group. The remainder of this chapter describes the signal pins in each functional group.

| Functional Group                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Number of<br>Signals |     |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|

| Power (V <sub>CC</sub> )                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 20  |

| Ground (GN                                                              | D)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      | 66  |

| Clock                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 2   |

| PLL                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 3   |

| Address bus                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 18  |

| Data bus                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Port A <sup>1</sup>  | 24  |

| Bus control                                                             | Bus control                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |     |

| Interrupt and mode control                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 5   |

| Host interfac                                                           | Host interface (HI08) Port B <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                          |                      |     |

| Enhanced synchronous serial interface (ESSI) Ports C and D <sup>3</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12                   |     |

| Serial communication interface (SCI) Port E <sup>4</sup>                |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                    |     |

| Timer                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                    |     |

| OnCE/JTAG Port                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      | 6   |

| Notes: 1.<br>2.<br>3.<br>4.<br>5.                                       | Port A signals define the external memory interface port, including the external a<br>Port B signals are the HI08 port signals multiplexed with the GPIO signals.<br>Port C and D signals are the two ESSI port signals multiplexed with the GPIO signals.<br>Port E signals are the SCI port signals multiplexed with the GPIO signals.<br>There are 5 signal connections that are not used. These are designated as no co<br><b>Chapter 3</b> ). | gnals.               | , C |

| Table 1-1. | DSP56311 | Functional  | Signal  | Groupings |

|------------|----------|-------------|---------|-----------|

|            | 00011    | i unotionui | orginar | aroupingo |

**Note:** The Clock Output (CLKOUT), BCLK, BCLK, CAS, and RAS[0–3] signals used by other DSP56300 family members are supported by the DSP56311 at operating frequencies up to 100 MHz. Therefore, above 100 MHz, you must enable bus arbitration by setting the Asynchronous Bus Arbitration Enable Bit (ABE) in the operating mode register. When set, the ABE bit eliminates the required set-up and hold times for BB and BG with respect to CLKOUT. In addition, DRAM access is not supported above 100 MHz.

- Notes: 1. The HI08 port supports a non-multiplexed or a multiplexed bus, single or double Data Strobe (DS), and single or double Host Request (HR) configurations. Since each of these modes is configured independently, any combination of these modes is possible. These HI08 signals can also be configured alternatively as GPIO signals (PB[0–15]). Signals with dual designations (for example, HAS/HAS) have configurable polarity.

- The ESSI0, ESSI1, and SCI signals are multiplexed with the Port C GPIO signals (PC[0–5]), Port D GPIO signals (PD[0–5]), and Port E GPIO signals (PE[0–2]), respectively.

- **3.** TIO[0–2] can be configured as GPIO signals.

- 4. CLKOUT, BCLK, BCLK, CAS, and RAS[0-3] are valid only for operating frequencies ≤100 MHz.

Figure 1-1. Signals Identified by Functional Group

DSP56311 Technical Data, Rev. 8

| Power Name        | Description                                                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCP</sub>  | <b>PLL Power</b> — $V_{CC}$ dedicated for PLL use. The voltage should be well-regulated and the input should be provided with an extremely low impedance path to the $V_{CC}$ power rail.           |

| V <sub>CCQL</sub> | Quiet Core (Low) Power—An isolated power for the core processing logic. This input must be isolated externally from all other chip power inputs.                                                    |

| V <sub>CCQH</sub> | <b>Quiet External (High) Power</b> —A quiet power source for I/O lines. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                        |

| V <sub>CCA</sub>  | Address Bus Power—An isolated power for sections of the address bus I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .               |

| V <sub>CCD</sub>  | Data Bus Power—An isolated power for sections of the data bus I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                     |

| V <sub>CCC</sub>  | Bus Control Power—An isolated power for the bus control I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                           |

| V <sub>CCH</sub>  | Host Power—An isolated power for the HI08 I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> .                                         |

| V <sub>CCS</sub>  | <b>ESSI, SCI, and Timer Power</b> —An isolated power for the ESSI, SCI, and timer I/O drivers. This input must be tied externally to all other chip power inputs, <i>except</i> V <sub>CCQL</sub> . |

| Note: The user m  | ust provide adequate external decoupling capacitors for all power connections.                                                                                                                      |

#### Table 1-2. Power Inputs

# 1.2 Ground

### Table 1-3. Grounds

| Name                                                                                         | Description                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND <sub>P</sub>                                                                             | <b>PLL Ground</b> —Ground-dedicated for PLL use. The connection should be provided with an extremely low-impedance path to ground. $V_{CCP}$ should be bypassed to GND <sub>P</sub> by a 0.47 $\mu$ F capacitor located as close as possible to the chip package. |

| GND <sub>P1</sub>                                                                            | <b>PLL Ground 1</b> —Ground-dedicated for PLL use. The connection should be provided with an extremely low-impedance path to ground.                                                                                                                              |

| GND                                                                                          | Ground—Connected to an internal device ground plane.                                                                                                                                                                                                              |

| Note: The user must provide adequate external decoupling capacitors for all GND connections. |                                                                                                                                                                                                                                                                   |

# 1.3 Clock

### Table 1-4. Clock Signals

| Signal Name | Туре   | State During<br>Reset | Signal Description                                                                                                                                   |

|-------------|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTAL       | Input  | Input                 | External Clock/Crystal Input—Interfaces the internal crystal oscillator input to an external crystal or an external clock.                           |

| XTAL        | Output | Chip-driven           | <b>Crystal Output</b> —Connects the internal crystal oscillator output to an external crystal. If an external clock is used, leave XTAL unconnected. |

| Signal<br>Name | Туре          | State During Reset,<br>Stop, or Wait                                                                                                                                                                               | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR             | Output        | Reset: Output<br>(deasserted)<br>State during Stop/Wait<br>depends on BRH bit<br>setting:<br>• BRH = 0: Output,<br>deasserted<br>• BRH = 1: Maintains<br>last state (that is, if<br>asserted, remains<br>asserted) | <b>Bus Request</b> —Asserted when the DSP requests bus mastership. $\overline{BR}$ is deasserted when the DSP no longer needs the bus. $\overline{BR}$ may be asserted or deasserted independently of whether the DSP56311 is a bus master or a bus slave. Bus "parking" allows $\overline{BR}$ to be deasserted even though the DSP56311 is the bus master. (See the description of bus "parking" in the $\overline{BB}$ signal description.) The bus request hold (BRH) bit in the BCR allows $\overline{BR}$ to be asserted under software control even though the DSP does not need the bus. $\overline{BR}$ is typically sent to an external bus arbitrator that controls the priority, parking, and tenure of each master on the same external bus. $\overline{BR}$ is affected only by DSP requests for the external bus, never for the internal bus. During hardware reset, $\overline{BR}$ is deasserted and the arbitration is reset to the bus slave state. |

| BG             | Input         | Ignored Input                                                                                                                                                                                                      | <b>Bus Grant</b> —Asserted by an external bus arbitration circuit when the DSP56311 becomes the next bus master. When $\overline{BG}$ is asserted, the DSP56311 must wait until $\overline{BB}$ is deasserted before taking bus mastership. When $\overline{BG}$ is deasserted, bus mastership is typically given up at the end of the current bus cycle. This may occur in the middle of an instruction that requires more than one external bus cycle for execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |               |                                                                                                                                                                                                                    | <b>Chapter 2.</b> An alternate mode can be invoked: set the asynchronous bus arbitration enable (ABE) bit (Bit 13) in the Operating Mode Register. When this bit is set, $\overline{BG}$ and $\overline{BB}$ are synchronized internally. This eliminates the respective set-up and hold time requirements but adds a required delay between the deassertion of an initial $\overline{BG}$ input and the assertion of a subsequent $\overline{BG}$ input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BB             | Input/ Output | Ignored Input                                                                                                                                                                                                      | <b>Bus Busy</b> —Indicates that the bus is active. Only after $\overline{BB}$ is deasserted can the pending bus master become the bus master (and then assert the signal again). The bus master may keep $\overline{BB}$ asserted after ceasing bus activity regardless of whether $\overline{BR}$ is asserted or deasserted. Called "bus parking," this allows the current bus master to reuse the bus without rearbitration until another device requires the bus. $\overline{BB}$ is deasserted by an "active pull-up" method (that is, $\overline{BB}$ is driven high and then released and held high by an external pull-up resistor).                                                                                                                                                                                                                                                                                                                            |

|                |               |                                                                                                                                                                                                                    | The default operation of this signal requires a set-up and hold time as specified in <b>Chapter 2</b> . An alternative mode can be invoked by setting the ABE bit (Bit 13) in the Operating Mode Register. When this bit is set, $\overline{BG}$ and $\overline{BB}$ are synchronized internally. See $\overline{BG}$ for additional information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |               |                                                                                                                                                                                                                    | Note: BB requires an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CAS            | Output        | Tri-stated                                                                                                                                                                                                         | <b>Column Address Strobe</b> —When the DSP is the bus master, CAS is an active-low output used by DRAM to strobe the column address. Otherwise, if the Bus Mastership Enable (BME) bit in the DRAM control register is cleared, the signal is tristated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |               |                                                                                                                                                                                                                    | Note: DRAM access is not supported above 100 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BCLK           | Output        | Tri-stated                                                                                                                                                                                                         | <b>Bus Clock</b><br>When the DSP is the bus master, BCLK is active when the ATE bit in the Operating<br>Mode Register is set. When BCLK is active and synchronized to CLKOUT by the<br>internal PLL, BCLK precedes CLKOUT by one-fourth of a clock cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                |               |                                                                                                                                                                                                                    | <b>Note:</b> At operating frequencies above 100 MHz, this signal produces a low-amplitude waveform that is not usable externally by other devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BCLK           | Output        | Tri-stated                                                                                                                                                                                                         | Bus Clock Not<br>When the DSP is the bus master, $\overline{\text{BCLK}}$ is the inverse of the BCLK signal. Otherwise, the signal is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |               |                                                                                                                                                                                                                    | <b>Note:</b> At operating frequencies above 100 MHz, this signal produces a low-amplitude waveform that is not usable externally by other devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### Table 1-8. External Bus Control Signals (Continued)

# **1.6 Interrupt and Mode Control**

The interrupt and mode control signals select the chip operating mode as it comes out of hardware reset. After RESET is deasserted, these inputs are hardware interrupt request lines.

| Signal Name | Туре  | State During<br>Reset    | Signal Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODA        | Input | Schmitt-trigger<br>Input | <b>Mode Select A</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQĀ        | Input |                          | <b>External Interrupt Request A</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the STOP or WAIT<br>standby state and IRQA is asserted, the processor exits the STOP or WAIT<br>state.                                                           |

| MODB        | Input | Schmitt-trigger<br>Input | <b>Mode Select B</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQB        | Input |                          | <b>External Interrupt Request B</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the WAIT standby state<br>and IRQB is asserted, the processor exits the WAIT state.                                                                              |

| MODC        | Input | Schmitt-trigger<br>Input | <b>Mode Select C</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| IRQC        | Input |                          | <b>External Interrupt Request C</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the WAIT standby state<br>and IRQC is asserted, the processor exits the WAIT state.                                                                              |

| MODD        | Input | Schmitt-trigger<br>Input | <b>Mode Select D</b> —MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the Operating Mode Register when the RESET signal is deasserted.                                                                                                                                                                                                            |

| ĪRQD        | Input |                          | <b>External Interrupt Request D</b> —After reset, this input becomes a level-<br>sensitive or negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. If the processor is in the WAIT standby state<br>and IRQD is asserted, the processor exits the WAIT state.                                                                              |

| RESET       | Input | Schmitt-trigger<br>Input | <b>Reset</b> —Places the chip in the Reset state and resets the internal phase generator. The Schmitt-trigger input allows a slowly rising input (such as a capacitor charging) to reset the chip reliably. When the RESET signal is deasserted, the initial chip operating mode is latched from the MODA, MODB, MODC, and MODD inputs. The RESET signal must be asserted after powerup. |

| Table 1-9. | Interrupt and | Mode Control |

|------------|---------------|--------------|

|------------|---------------|--------------|

JTAG and OnCE Interface

## 1.12 JTAG and OnCE Interface

The DSP56300 family and in particular the DSP56311 support circuit-board test strategies based on the **IEEE**® **Std.** 1149.1<sup>™</sup> test access port and boundary scan architecture, the industry standard developed under the sponsorship of the Test Technology Committee of IEEE and the JTAG. The OnCE module provides a means to interface nonintrusively with the DSP56300 core and its peripherals so that you can examine registers, memory, or on-chip peripherals. Functions of the OnCE module are provided through the JTAG TAP signals. For programming models, see the chapter on debugging support in the *DSP56300 Family Manual*.

| Signal<br>Name | Туре          | State During<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК            | Input         | Input                 | Test Clock—A test clock input signal to synchronize the JTAG test logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDI            | Input         | Input                 | <b>Test Data Input</b> —A test data serial input signal for test instructions and data. TDI is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TDO            | Output        | Tri-stated            | <b>Test Data Output</b> —A test data serial output signal for test instructions and data. TDO is actively driven in the shift-IR and shift-DR controller states. TDO changes on the falling edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TMS            | Input         | Input                 | <b>Test Mode Select</b> —Sequences the test controller's state machine. TMS is sampled on the rising edge of TCK and has an internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRST           | Input         | Input                 | <b>Test Reset</b> —Înitializes the test controller asynchronously. TRST has an internal pull-up resistor. TRST must be asserted during and after power-up (see EB610/D for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DE             | Input/ Output | Input                 | <b>Debug Event</b> —As an input, initiates Debug mode from an external command controller, and, as an open-drain output, acknowledges that the chip has entered Debug mode. As an input, DE causes the DSP56300 core to finish executing the current instruction, save the instruction pipeline information, enter Debug mode, and wait for commands to be entered from the debug serial input line. This signal is asserted as an output for three clock cycles when the chip enters Debug mode as a result of a debug request or as a result of meeting a breakpoint condition. The DE has an internal pull-up resistor. This signal is not a standard part of the JTAG TAP controller. The signal connects directly to the OnCE module to initiate debug mode directly or to provide a direct external indication that the chip has entered Debug mode. All other interface with the OnCE module must occur through the JTAG port. |

| Table 1-16. | JTAG/OnCE Interface |

|-------------|---------------------|

|             |                     |

## 2.4.4 Reset, Stop, Mode Select, and Interrupt Timing

| N   | Ok ann shailaith a                                                                                                                                                                                                                                                                                                                                            | Farmerstern                                                                                                                                                                                                                                                                                          | 150                                           |                                      |                            |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------|----------------------------|

| No. | Characteristics                                                                                                                                                                                                                                                                                                                                               | Expression                                                                                                                                                                                                                                                                                           | Min                                           | Max                                  | Unit                       |

| 8   | Delay from RESET assertion to all pins at reset value <sup>3</sup>                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                    | _                                             | 26.0                                 | ns                         |

| 9   | <ul> <li>Required RESET duration<sup>4</sup></li> <li>Power on, external clock generator, PLL disabled</li> <li>Power on, external clock generator, PLL enabled</li> <li>Power on, internal oscillator</li> <li>During STOP, XTAL disabled (PCTL Bit 16 = 0)</li> <li>During STOP, XTAL enabled (PCTL Bit 16 = 1)</li> <li>During normal operation</li> </ul> | $\begin{array}{c} \text{Minimum:} \\ 50 \times \text{ET}_{\text{C}} \\ 1000 \times \text{ET}_{\text{C}} \\ 75000 \times \text{ET}_{\text{C}} \\ 75000 \times \text{ET}_{\text{C}} \\ 2.5 \times \text{T}_{\text{C}} \\ 2.5 \times \text{T}_{\text{C}} \\ 2.5 \times \text{T}_{\text{C}} \end{array}$ | 333.3<br>6.67<br>0.50<br>0.50<br>16.7<br>16.7 |                                      | ns<br>µs<br>ms<br>ns<br>ns |

| 10  | <ul> <li>Delay from asynchronous RESET deassertion to first external address output (internal reset deassertion)<sup>5</sup></li> <li>Minimum</li> <li>Maximum</li> </ul>                                                                                                                                                                                     | $3.25 \times T_{C} + 2.0$<br>20.25 × $T_{C} + 10$                                                                                                                                                                                                                                                    | 23.7<br>—                                     | <br>145.0                            | ns<br>ns                   |

| 13  | Mode select set-up time                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                      | 30.0                                          | _                                    | ns                         |

| 14  | Mode select hold time                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                      | 0.0                                           |                                      | ns                         |

| 15  | Minimum edge-triggered interrupt request assertion width                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                      | 6.6                                           | -                                    | ns                         |

| 16  | Minimum edge-triggered interrupt request deassertion width                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                      | 6.6                                           | _                                    | ns                         |

| 17  | <ul> <li>Delay from IRQA, IRQB, IRQC, IRQD, NMI assertion to external memory access address out valid</li> <li>Caused by first interrupt instruction fetch</li> <li>Caused by first interrupt instruction execution</li> </ul>                                                                                                                                | Minimum:<br>$4.25 \times T_{C} + 2.0$<br>$7.25 \times T_{C} + 2.0$                                                                                                                                                                                                                                   | 30.4<br>51.0                                  |                                      | ns<br>ns                   |

| 18  | Delay from IRQA, IRQB, IRQC, IRQD, NMI assertion to general-<br>purpose transfer output valid caused by first interrupt instruction<br>execution                                                                                                                                                                                                              | Minimum:<br>10 × T <sub>C</sub> + 5.0                                                                                                                                                                                                                                                                | 72.0                                          | _                                    | ns                         |

| 19  | Delay from address output valid caused by first interrupt instruction execute to interrupt request deassertion for level sensitive fast interrupts <sup>1, 7, 8</sup>                                                                                                                                                                                         | Maximum:<br>(WS + 3.75) × T <sub>C</sub> - 10.94                                                                                                                                                                                                                                                     | _                                             | Note 8                               | ns                         |

| 20  | Delay from $\overline{RD}$ assertion to interrupt request deassertion for level sensitive fast interrupts ^1, ^7, ^8                                                                                                                                                                                                                                          | Maximum:<br>(WS + 3.25) × T <sub>C</sub> – 10.94                                                                                                                                                                                                                                                     |                                               | Note 8                               | ns                         |

| 21  | Delay from $\overline{WR}$ assertion to interrupt request deassertion for level<br>sensitive fast interrupts <sup>1, 7, 8</sup><br>• DRAM for all WS<br>• SRAM WS = 1<br>• SRAM WS = 2, 3<br>• SRAM WS $\geq$ 4                                                                                                                                               | $\begin{array}{c} \mbox{Maximum:} \\ (WS + 3.5) \times T_C - 10.94 \\ (WS + 3.5) \times T_C - 10.94 \\ (WS + 3) \times T_C - 10.94 \\ (WS + 2.5) \times T_C - 10.94 \end{array}$                                                                                                                     |                                               | Note 8<br>Note 8<br>Note 8<br>Note 8 | ns<br>ns<br>ns<br>ns       |

| 24  | Duration for IRQA assertion to recover from Stop state                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                      | 5.9                                           | _                                    | ns                         |

| 25  | <ul> <li>Delay from IRQA assertion to fetch of first instruction (when exiting Stop)<sup>2, 3</sup></li> <li>PLL is not active during Stop (PCTL Bit 17 = 0) and Stop delay is enabled (Operating Mode Register Bit 6 = 0)</li> </ul>                                                                                                                         | PLC × ET <sub>C</sub> × PDF + (128 K –<br>PLC/2) × T <sub>C</sub>                                                                                                                                                                                                                                    | 1.3                                           | 9.1                                  | ms                         |

|     | <ul> <li>PLL is not active during Stop (PCTL Bit 17 = 0) and Stop delay is not enabled (Operating Mode Register Bit 6 = 1)</li> <li>PLL is active during Stop (PCTL Bit 17 = 1) (Implies No Stop Delay)</li> </ul>                                                                                                                                            | $\begin{array}{c} PLC \times \; ET_{C} \times \; PDF + (23.75 \pm \\ 0.5) \times \; T_{C} \\ (8.25 \pm 0.5) \times \; T_{C} \end{array}$                                                                                                                                                             | 232.5 ns<br>51.7                              | 12.3 ms<br>58.3                      | ns                         |

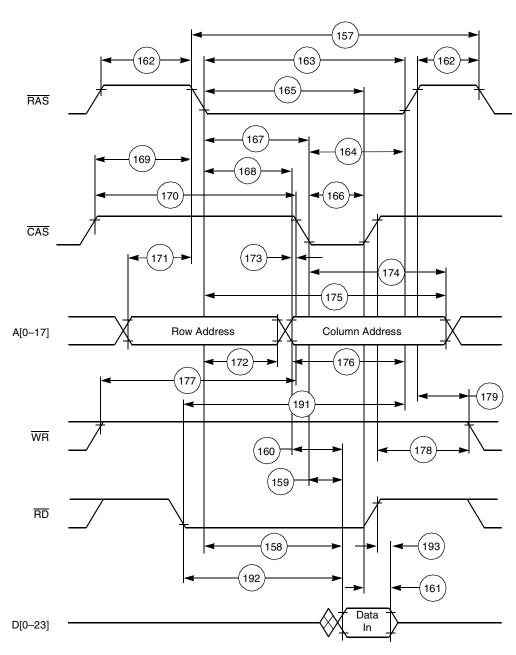

Figure 2-16. DRAM Out-of-Page Read Access

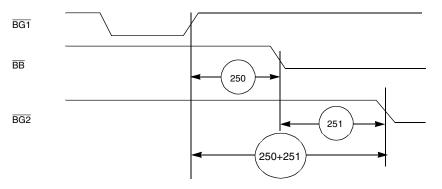

### 2.4.5.3 Asynchronous Bus Arbitration Timings

BG signal for a second DSP56300 device.

| Na     | Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            | Everencian  | 150 MHz |     | - Unit |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------|---------|-----|--------|

| No.    |                                                                                                                                                                                                                                                                                                                                                                                                                                      | Characteristics                            | Expression  | Min     | Max | Unit   |

| 250    | BB as                                                                                                                                                                                                                                                                                                                                                                                                                                | ssertion window from BG input deassertion. | 2.5× Tc + 5 | —       | 22  | ns     |

| 251    | Delay                                                                                                                                                                                                                                                                                                                                                                                                                                | r from BB assertion to BG assertion        | 2× Tc + 5   | 18.3    | -   | ns     |

| Notes: | <ol> <li>Bit 13 in the Operating Mode Register must be set to enable Asynchronous Arbitration mode.</li> <li>At 150 MHz, Asynchronous Arbitration mode is recommended.</li> <li>To guarantee timings 250 and 251, it is recommended that you assert non-overlapping BG inputs to different DSP56300 devices (on the same bus) as shown in Figure 2-19 where BG1 is the BG signal for one DSP56300 device while BG2 is the</li> </ol> |                                            |             |         |     |        |

Figure 2-19. Asynchronous Bus Arbitration Timing

The asynchronous bus arbitration is enabled by internal synchronization circuits on  $\overline{BG}$  and  $\overline{BB}$  inputs. These synchronization circuits add delay from the external signal until it is exposed to internal logic. As a result of this delay, a DSP56300 part may assume mastership and assert  $\overline{BB}$ , for some time after  $\overline{BG}$  is deasserted. This is the reason for timing 250.

Once  $\overline{BB}$  is asserted, there is a synchronization delay from  $\overline{BB}$  assertion to the time this assertion is exposed to other DSP56300 components that are potential masters on the same bus. If  $\overline{BG}$  input is asserted before that time, and  $\overline{BG}$  is asserted and  $\overline{BB}$  is deasserted, another DSP56300 component may assume mastership at the same time. Therefore, some non-overlap period between one  $\overline{BG}$  input active to another  $\overline{BG}$  input active is required. Timing 251 ensures that overlaps are avoided.

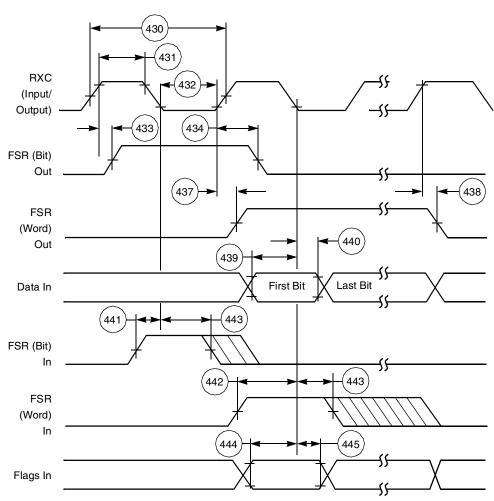

## 2.4.6 Host Interface Timing

| No. | Characteristic <sup>10</sup>                                                                                                                                                                                                                                                                   | Everencion                 | 150          | 150 MHz |          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------|---------|----------|

| NO. | Characteristic                                                                                                                                                                                                                                                                                 | Expression                 | Min          | Max     | - Unit   |

| 317 | Read data strobe assertion width <sup>5</sup><br>HACK assertion width                                                                                                                                                                                                                          | T <sub>C</sub> + 6.5       | 13.1         | —       | ns       |

| 318 | Read data strobe deassertion width <sup>5</sup><br>HACK deassertion width                                                                                                                                                                                                                      |                            | 6.5          | _       | ns       |

| 319 | Read data strobe deassertion width <sup>5</sup> after "Last Data Register" reads <sup>8,11</sup> , or<br>between two consecutive CVR, ICR, or ISR reads <sup>3</sup><br>HACK deassertion width after "Last Data Register" reads <sup>8,11</sup>                                                | $2.5 \times T_{C} + 4.4$   | 20.8         | -       | ns       |

| 320 | Write data strobe assertion width <sup>6</sup>                                                                                                                                                                                                                                                 |                            | 8.7          | -       | ns       |

| 321 | <ul> <li>Write data strobe deassertion width<sup>8</sup></li> <li>HACK write deassertion width</li> <li>after ICR, CVR and "Last Data Register" writes</li> <li>after IVR writes, or<br/>after TXH:TXM:TXL writes (with HLEND= 0), or<br/>after TXL:TXM:TXH writes (with HLEND = 1)</li> </ul> | 2.5 × T <sub>C</sub> + 4.4 | 20.8<br>10.9 | _       | ns<br>ns |

| 322 | HAS assertion width                                                                                                                                                                                                                                                                            |                            | 6.5          | _       | ns       |

| 323 | HAS deassertion to data strobe assertion <sup>4</sup>                                                                                                                                                                                                                                          |                            | 0.0          | _       | ns       |

| 324 | Host data input set-up time before write data strobe deassertion <sup>6</sup>                                                                                                                                                                                                                  |                            | 6.5          | _       | ns       |

| 325 | Host data input hold time after write data strobe deassertion <sup>6</sup>                                                                                                                                                                                                                     |                            | 2.2          | _       | ns       |

| 326 | Read data strobe assertion to output data active from high impedance <sup>5</sup><br>HACK assertion to output data active from high impedance                                                                                                                                                  |                            | 2.2          | _       | ns       |

| 327 | Read data strobe assertion to output data valid <sup>5</sup><br>HACK assertion to output data valid                                                                                                                                                                                            |                            | —            | 16.5    | ns       |

| 328 | Read data strobe deassertion to output data high impedance <sup>5</sup><br>HACK deassertion to output data high impedance                                                                                                                                                                      |                            | —            | 6.5     | ns       |

| 329 | Output data hold time after read data strobe deassertion <sup>5</sup><br>Output data hold time after HACK deassertion                                                                                                                                                                          |                            | 2.2          | _       | ns       |

| 330 | HCS assertion to read data strobe deassertion <sup>5</sup>                                                                                                                                                                                                                                     | T <sub>C</sub> + 6.5       | 13.1         | —       | ns       |

| 331 | HCS assertion to write data strobe deassertion <sup>6</sup>                                                                                                                                                                                                                                    |                            | 6.5          | —       | ns       |

| 332 | HCS assertion to output data valid                                                                                                                                                                                                                                                             |                            | _            | 13.0    | ns       |

| 333 | HCS hold time after data strobe deassertion <sup>4</sup>                                                                                                                                                                                                                                       |                            | 0.0          | _       | ns       |

| 334 | Address (HAD[0–7]) set-up time before HAS deassertion (HMUX=1)                                                                                                                                                                                                                                 |                            | 3.0          | —       | ns       |

| 335 | Address (HAD[0-7]) hold time after HAS deassertion (HMUX=1)                                                                                                                                                                                                                                    |                            | 2.2          | —       | ns       |

| 336 | HA[8–10] (HMUX=1), HA[0–2] (HMUX=0), HR/W set-up time before data strobe assertion <sup>4</sup> <ul> <li>Read</li> <li>Write</li> </ul>                                                                                                                                                        |                            | 0<br>3.0     |         | ns<br>ns |

| 337 | HA[8–10] (HMUX=1), HA[0–2] (HMUX=0), HR/W hold time after data strobe deassertion <sup>4</sup>                                                                                                                                                                                                 |                            | 2.2          | -       | ns       |

| 338 | Delay from read data strobe deassertion to host request assertion for "Last Data Register" read <sup>5, 7, 8</sup>                                                                                                                                                                             | T <sub>C</sub> + 3.5       | 10.1         | -       | ns       |

| 339 | Delay from write data strobe deassertion to host request assertion for "Last Data Register" write <sup>6, 7, 8</sup>                                                                                                                                                                           | $1.5 \times T_{C} + 3.5$   | 13.4         | -       | ns       |

Table 2-14.Host Interface Timings1,2,12

Figure 2-32. ESSI Receiver Timing

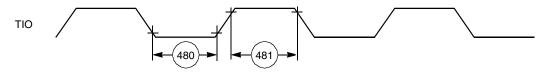

### 2.4.9 Timer Timing

Table 2-17. Timer Timing

| No.                                                                                                                                                                           | Characteristics | Everagion                | 150  | Unit |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|------|------|------|

| NO.                                                                                                                                                                           | Characteristics | Expression               | Min  | Max  | Unit |

| 480                                                                                                                                                                           | TIO Low         | 2 × T <sub>C</sub> + 2.0 | 15.4 | —    | ns   |

| 481                                                                                                                                                                           | TIO High        | 2 × T <sub>C</sub> + 2.0 | 15.4 | —    | ns   |

| Note: $V_{CCQH} = 3.3 \text{ V} \pm 0.3 \text{ V}, V_{CC} = 1.8 \text{ V} \pm 0.1 \text{ V}; T_J = -40^{\circ}\text{C} \text{ to } +100^{\circ}\text{C}, C_L = 50 \text{ pF}$ |                 |                          |      |      |      |

Figure 2-33. TIO Timer Event Input Restrictions

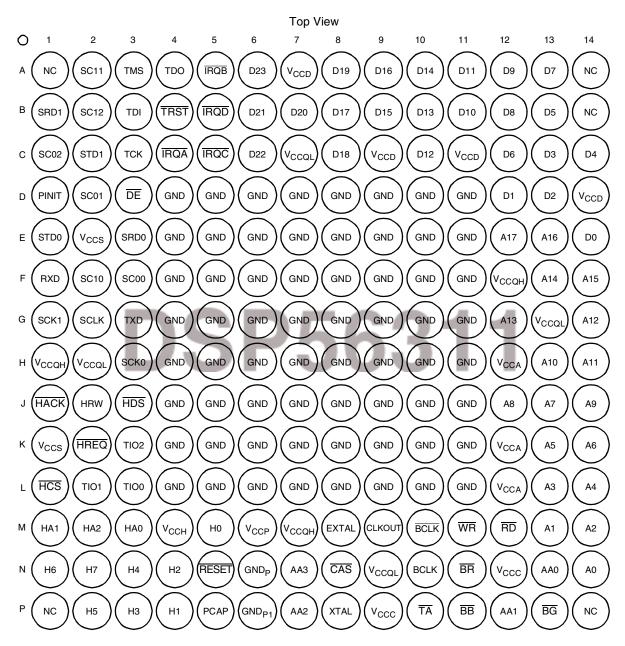

## 3.1 Package Description

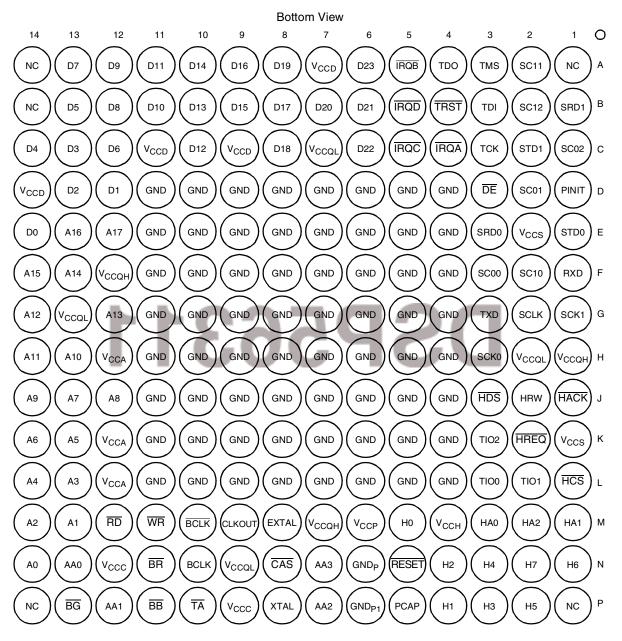

Top and bottom views of the MAP-BGA packages are shown in Figure 3-1 and Figure 3-2 with their pin-outs.

Figure 3-1. DSP56311 MAP-BGA Package, Top View

Figure 3-2. DSP56311 MAP-BGA Package, Bottom View

Package Description

| Ball<br>No. | Signal Name       | Ball<br>No. | Signal Name                      | Ball<br>No. | Signal Name                      |

|-------------|-------------------|-------------|----------------------------------|-------------|----------------------------------|

| F6          | GND               | H3          | SCK0 or PC3                      | J14         | A9                               |

| F7          | GND               | H4          | GND                              | K1          | V <sub>CCS</sub>                 |