# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A8                                                       |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 800MHz                                                                |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                |

| RAM Controllers                 | DDR2, LPDDR, LPDDR2                                                   |

| Graphics Acceleration           | Yes                                                                   |

| Display & Interface Controllers | EPDC, LCD                                                             |

| Ethernet                        | 10/100Mbps (1)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 + PHY (2)                                                     |

| Voltage - I/O                   | 1.2V, 1.875V, 2.775V, 3V                                              |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                       |

| Security Features               | Boot Security, Cryptography, Secure JTAG                              |

| Package / Case                  | 416-LFBGA                                                             |

| Supplier Device Package         | 416-MAPBGA (13x13)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx507cvk8b |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Pixel Processing Pipeline (ePXP)

The ePXP is a high-performance pixel processor capable of 1 pixel/clock performance for combined operations, such as color-space conversion, alpha blending, gamma mapping, and rotation. The ePXP is enhanced with features specifically for grayscale applications working in conjunction with the electrophoretic display controller to form a full grayscale display solution. In addition, the ePXP supports traditional pixel/frame processing paths for still-image and video processing applications, allowing it to interface with the integrated LCD controller (eLCDIF).

Graphics acceleration The i.MX50 provides a 2D graphics accelerator with performance up to 200 Mpix/s.

# 1.1.5 Multilevel Memory System

The multilevel memory system of the i.MX50 is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The i.MX50 supports many types of external memory devices, including DDR2, LPDDR2, LPDDR1, NOR Flash, PSRAM, Cellular RAM, NAND Flash (MLC and SLC) and OneNAND<sup>TM</sup>, and managed NAND including eMMC up to rev. 4.4.

# 1.1.6 Smart Speed<sup>™</sup> Technology

The i.MX50 device has power management throughout the SOC that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart Speed technology enables the designer to deliver a feature-rich product that requires levels of power that are far less than industry expectations.

# 1.1.7 Interface Flexibility

The i.MX50 supports connection to a variety of interfaces, including an LCD controller for displays, two high-speed USB on-the-go-capable PHYs, multiple expansion card ports (high-speed MMC/SDIO host and others), 10/100 Ethernet controller, and a variety of other popular interfaces (for example, UART,  $I^2C$ , and  $I^2S$  serial audio).

# 1.1.8 Advanced Security

The i.MX50 delivers hardware-enabled security features, such as High-Assurance Boot 4 (HAB4) for signed/authenticated firmware images, basic DRM support with random private keys and AES encryption/decryption, and storage and programmability of on-chip fuses.

# 1.2 Features

The i.MX50 applications processor is based on the ARM Cortex-A8 platform and has the following features:

- MMU, L1 instruction cache, and L1 data cache

- Unified L2 cache

- 800 MHz or 1 GHz target frequency of the core (including NEON, VFPv3, and L1 cache)

| Signal Name                             | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMIC_RDY                                | This input may be used by a PMIC to signal to the i.MX50 that the PMIC supply outputs are at operating levels when resuming from STOP mode. The PMIC_RDY input is pin muxed on ALT3 of the I2C3_SCL pin and is in the NVCC_MISC domain.                                                                                                                                                                                                          |

| POP_EMMC_RST<br>(416 PoPBGA Only)       | This pin is the PoP eMMC 4.4 Reset pin. The customer may connect this on their PCB to any free GPIO, or just leave floating for non-4.4 eMMC. This pin does not connect to the i.MX50 die.                                                                                                                                                                                                                                                       |

| POP_LPDDR2_ZQ0/ZQ1<br>(416 PoPBGA Only) | These pins connect to the PoP LPDDR2 DRAM ZQ pins and should be connected on the customer PCB to a 240 $\Omega$ 1% resistor to ground if used. These pins do not connect to the i.MX50 die.                                                                                                                                                                                                                                                      |

| POP_LPDDR2_1.8V<br>(416 PoPBGA Only)    | These pins are the 1.8 V supply for the PoP LPDDR2 DRAM. These pins do not connect to the i.MX50 die.                                                                                                                                                                                                                                                                                                                                            |

| POP_NAND_VCC<br>(416 PoPBGA Only)       | This is the 3.3V I/O and memory supply for the PoP eMMC. Note that most eMMC can operate with a 1.8V I/O or a 3.3V I/O voltage. However, because we tied the eMMC memory and I/O domains together, you can't use the 1.8 V I/O option for the PoP eMMC, only 3.3 V I/O.                                                                                                                                                                          |

| POR_B                                   | This POWER-ON RESET input is a cold reset negative logic input that resets all modules and logic in the IC. The POR_B pin should have an external 68 K pull-up to NVCC_RESET and a 1 $\mu$ F capacitor to ground.<br>Note: The POR_B input must be immediately asserted at power-up and remain asserted until after the last power rail is at its working voltage.                                                                               |

| RESET_IN_B                              | <ul> <li>This warm reset negative logic input resets all modules and logic except for the following:</li> <li>Test logic (JTAG, IOMUXC, DAP)</li> <li>SRTC</li> <li>Cold reset logic of WDOG—Some WDOG logic is only reset by POR_B. See WDOG chapter in the <i>MCIMX50 Applications Processor Reference Manual</i> (MCIMX50RM) for details.</li> </ul>                                                                                          |

| SSI_EXT1_CLK,<br>SSI_EXT2_CLK           | The SSI_EXT1_CLK and SSI_EXT2_CLK outputs are recommended for generating a clock<br>output from the i.MX50. Use of the CKO1 and CKO2 clock outputs is not recommended, as the<br>large number of combinational logic muxes on those signals will impact jitter and duty-cycle.<br>Note that these two clock outputs do not have dedicated pins: SSI_EXT1_CLK is IOMUX ALT3<br>on the OWIRE pin, and SSI_EXT2_CLK is IOMUX ALT3 of the EPITO pin. |

| TEST_MODE                               | TEST_MODE is for Freescale factory use only. This signal is internally connected to an on-chip pull-down device. The user must either float this signal or tie it to GND.                                                                                                                                                                                                                                                                        |

| USB_H1_GPANAIO,<br>USB_OTG_GPANAIO      | These signals are reserved for Freescale manufacturing use only. Users should float these outputs.                                                                                                                                                                                                                                                                                                                                               |

| USB_H1_RREFEXT,<br>USB_OTG_RREFEXT      | These signals determine the reference current for the USB PHY bandgap reference. An external 6.04 k $\Omega$ 1% resistor to GND is required. This resistor should be connected through a short (low impedance connection) and placed away from other noisy regions.                                                                                                                                                                              |

|                                         | If USB_H1 is not used, the H1 RREFEXT resistor may be eliminated and the pin left floating.<br>If USB_OTG is not used, the OTG RREFEXT resistor may be eliminated and the pin left<br>floating.                                                                                                                                                                                                                                                  |

# 4.4.1 GPIO Output Buffer Impedance

Table 24 shows the GPIO output buffer impedance of the i.MX50 processor.

| Parameter S                |        | Test Conditions                                                                                                                                                         |                      | Тур                   |                       |                        |      |

|----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|------------------------|------|

|                            | Symbol |                                                                                                                                                                         | Min                  | OVDD<br>2.775 V       | OVDD<br>1.875V        | Max                    | Unit |

| Output driver<br>impedance | Rpu    | Low drive strength, Ztl = 150 $\Omega$<br>Medium drive strength, Ztl = 75 $\Omega$<br>High drive strength, Ztl = 50 $\Omega$<br>Max drive strength, Ztl = 37.5 $\Omega$ | 80<br>40<br>27<br>20 | 104<br>52<br>35<br>26 | 150<br>75<br>51<br>38 | 250<br>125<br>83<br>62 | Ω    |

| Output driver<br>impedance | Rpd    | Low drive strength, Ztl = 150 $\Omega$<br>Medium drive strength, Ztl = 75 $\Omega$<br>High drive strength, Ztl = 50 $\Omega$<br>Max drive strength, Ztl = 37.5 $\Omega$ | 64<br>32<br>21<br>16 | 88<br>44<br>30<br>22  | 134<br>66<br>44<br>34 | 243<br>122<br>81<br>61 | Ω    |

### Table 24. GPIO Output Buffer Impedance

# 4.4.2 LVIO Output Buffer Impedance

Table 25 shows the LVIO output buffer impedance of the i.MX50 processor.

| Parameter Syn              |        | ool Test Conditions                                                                                                                                                     | Min                  | Тур                   |                       |                        |      |

|----------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|------------------------|------|

|                            | Symbol |                                                                                                                                                                         |                      | OVDD<br>2.775 V       | OVDD<br>1.875V        | Мах                    | Unit |

| Output driver<br>impedance | Rpu    | Low drive strength, Ztl = 150 $\Omega$<br>Medium drive strength, Ztl = 75 $\Omega$<br>High drive strength, Ztl = 50 $\Omega$<br>Max drive strength, Ztl = 37.5 $\Omega$ | 80<br>40<br>27<br>20 | 104<br>52<br>35<br>26 | 150<br>75<br>51<br>38 | 250<br>125<br>83<br>62 | Ω    |

| Output driver<br>impedance | Rpd    | Low drive strength, Ztl = 150 $\Omega$<br>Medium drive strength, Ztl = 75 $\Omega$<br>High drive strength, Ztl = 50 $\Omega$<br>Max drive strength, Ztl = 37.5 $\Omega$ | 64<br>32<br>21<br>16 | 88<br>44<br>30<br>22  | 134<br>66<br>44<br>34 | 243<br>122<br>81<br>61 | Ω    |

### Table 25. LVIO Output Buffer Impedance

# 4.5.8 LPDDR1 I/O AC Parameters

#### Table 34 shows the AC parameters for LPDDR1 I/O.

| Table 34 | . LPDDR1 | I/O AC | Parameters |

|----------|----------|--------|------------|

|----------|----------|--------|------------|

| Parameter                                             | Symbol         | Min      | Max      | Unit |

|-------------------------------------------------------|----------------|----------|----------|------|

| AC input logic high                                   | Vihd(ac)       | 0.8*ovdd | ovdd+0.3 |      |

| AC input logic low                                    | Vild(ac)       | -0.3     | 0.2*ovdd |      |

| AC input differential voltage <sup>1</sup>            | Vid(ac)        | 0.6*ovdd | ovdd+0.6 | V    |

| AC input differential crosspoint voltage <sup>2</sup> | Vix(ac)        | 0.4*ovdd | 0.6*ovdd | v    |

| Output propagation delay high to low                  | <b>t</b> POHLD |          | 2.5      |      |

| Output propagation delay low to high                  | <b>t</b> POLHD |          | 2.5      | ns   |

| Input propagation delay high to low                   | <b>t</b> PIHLD |          | 1.5      |      |

| Input propagation delay low to high                   | <b>t</b> PILHD |          | 1.5      |      |

| Single output slew rate                               | tsr            | 0.3      | 2.5      | V/ns |

<sup>1</sup>Vid(ac) specifies the input differential voltage IVtr-Vcpl required for switching, where Vtr is the "true" input signal and Vcp is the "complementary" input signal. The Minimum value is equal to Vih(ac)-Vil(ac)

<sup>2</sup>The typical value of Vix(ac) is expected to be about  $0.5^*$  ovdd. and Vix(ac) is expected to track variation of ovdd. Vix(ac) indicates the voltage at which differential input signal must cross.

### 4.5.9 LPDDR2 I/O AC Parameters

Table 35 shows the AC parameters for LPDDR2 I/O.

Table 35. LPDDR2 I/O AC Parameters

| Parameter                                                                     | Symbol         | Min       | Мах                 | Unit |

|-------------------------------------------------------------------------------|----------------|-----------|---------------------|------|

| AC input logic high                                                           | Vih(ac)        | Vref+0.22 | ovdd                |      |

| AC input logic low                                                            | Vil(ac)        | OVSS      | Vref-0.22           |      |

| AC differential input high voltage <sup>1</sup>                               | Vidh(ac)       | 0.44      | -                   | v    |

| AC differential input low voltage                                             | Vidhl(ac)      | -         | 0.44                | v    |

| AC input differential cross point voltage (relative to ovdd / 2) <sup>2</sup> | Vix(ac)        | -0.12     | 0.12                |      |

| Over/undershoot peak                                                          | Vpeak          |           | 0.35                | ns   |

| Over/undershoot area (above OVDD or below OVSS)                               | Varea          |           | 0.6 (at 266<br>MHz) | V-ns |

| Output propagation delay high to low                                          | <b>t</b> POHLD |           | 3.5                 |      |

| Output propagation delay low to high                                          | <b>t</b> POLHD |           | 3.5                 | ns   |

| Input propagation delay high to low                                           | <b>t</b> PIHLD |           | 1.5                 |      |

| Input propagation delay low to high                                           | tPILHD         |           | 1.5                 |      |

| Table 37. WDOG_RST_B | Timing Parameters |

|----------------------|-------------------|

|----------------------|-------------------|

| ID  | Parameter                        | Min | Max | Unit              |

|-----|----------------------------------|-----|-----|-------------------|

| CC5 | Duration of WDOG_RST_B Assertion | 1   |     | T <sub>CKIL</sub> |

### NOTE

CKIL is approximately 32 kHz.  $T_{\mbox{CKIL}}$  is one period or approximately 30  $\mu s.$

### 4.6.3 Clock Amplifier Parameters (CKIH)

The input to clock amplifier (CAMP) is internally ac-coupled allowing direct interface to a square wave or sinusoidal frequency source. No external series capacitors are required.

Table 38 shows the electrical parameters of CAMP.

| Table 38. CAMP Electrica | Parameters (CK | (HI) |

|--------------------------|----------------|------|

|--------------------------|----------------|------|

| Parameter                   | Min                       | Тур | Max  | Unit |

|-----------------------------|---------------------------|-----|------|------|

| Input frequency             | 8.0                       | _   | 40.0 | MHz  |

| VIL (for square wave input) | 0                         | _   | 0.3  | V    |

| VIH (for square wave input) | (VCC <sup>1</sup> – 0.25) | _   | 3    | V    |

| Sinusoidal input amplitude  | 0.4 <sup>2</sup>          | _   | VDD  | Vp-р |

| Output duty cycle           | 45                        | 50  | 55   | %    |

<sup>1</sup> VCC is the supply voltage of CAMP.

<sup>2</sup> This value of the sinusoidal input is determined during characterization.

# 4.6.4 **DPLL Electrical Parameters**

Table 39 shows the electrical parameters of digital phase-locked loop (DPLL).

Table 39. DPLL Electrical Parameters

| Parameter                                         | Test Conditions/Remarks         | Min       | Тур | Max      | Unit |

|---------------------------------------------------|---------------------------------|-----------|-----|----------|------|

| Reference clock frequency range <sup>1</sup>      | —                               | 10        |     | 100      | MHz  |

| Reference clock frequency range after pre-divider | —                               | 10        | _   | 40       | MHz  |

| Output clock frequency range (dpdck_2)            | —                               | 300       | _   | 1025     | MHz  |

| Pre-division factor <sup>2</sup>                  | —                               | 1         | _   | 16       | _    |

| Multiplication factor integer part                | —                               | 5         | —   | 15       | —    |

| Multiplication factor numerator <sup>3</sup>      | Should be less than denominator | -67108862 | _   | 67108862 | _    |

| Multiplication factor denominator <sup>2</sup>    | —                               | 1         | —   | 67108863 | —    |

| Output duty cycle                                 | —                               | 48.5      | 50  | 51.5     | %    |

| ID   | Parameter Symbol   |      | Timing<br>T <sup>2</sup> = GPMI Clock Cycle <sup>3</sup> |       | Example Timing for GPMI Clock $\approx 100 \text{MHz}$ T = 10ns |      | Unit |

|------|--------------------|------|----------------------------------------------------------|-------|-----------------------------------------------------------------|------|------|

|      |                    |      | Min.                                                     | Max.  | Min.                                                            | Max. |      |

| NF5  | WE pulse width     | tWP  | DS                                                       | *T    | 1                                                               | 0    | ns   |

| NF6  | ALE setup time     | tALS | (AS+1)*T                                                 | —     | 10                                                              | —    | ns   |

| NF7  | ALE hold time      | tALH | (DH+1)*T                                                 | —     | 20                                                              | —    | ns   |

| NF8  | Data setup time    | tDS  | DS*T                                                     | —     | 10                                                              | —    | ns   |

| NF9  | Data hold time     | tDH  | DH*T                                                     | —     | 10                                                              | —    | ns   |

| NF10 | Write cycle time   | tWC  | (DS+E                                                    | DH)*T | 20                                                              |      | ns   |

| NF11 | WE hold time       | tWH  | DH                                                       | *T    | 10                                                              |      | ns   |

| NF12 | Ready to RE low    | tRR  | (AS+1)*T                                                 | _     | 10                                                              | —    | ns   |

| NF13 | RE pulse width     | tRP  | DS*T                                                     | —     | 10                                                              | —    | ns   |

| NF14 | READ cycle time    | tRC  | (DS+DH)*T                                                | —     | 20                                                              | —    | ns   |

| NF15 | RE high hold time  | tREH | DH*T                                                     |       | 10                                                              | —    | ns   |

| NF16 | Data setup on read | tDSR | N/A                                                      |       | 10                                                              | —    | ns   |

| NF17 | Data hold on read  | tDHR | N/                                                       | A     | 10                                                              | —    | ns   |

Table 40. Asynchronous Mode Timing Parameters<sup>1</sup> (continued)

1 GPMI's Async Mode output timing could be controlled by module's internal register, say HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD.

This AC timing depends on these registers' setting. In the above table, we use AS/DS/DH representing these settings each. <sup>2</sup> T represents for the GPMI clock period.

<sup>3</sup> AS minimum value could be 0, while DS/DH minimum value is 1.

| ID   | Parameter                                      | Symbol            | Tim<br>T = GPMI C          | Unit |    |

|------|------------------------------------------------|-------------------|----------------------------|------|----|

|      |                                                |                   | Min.                       | Max. | -  |

| NF24 | postamble delay                                | t <sub>POST</sub> | POST_DELAY*t <sub>CK</sub> | —    | ns |

| NF25 | CLE and ALE setup time                         | t <sub>CALS</sub> | 0.5*t <sub>CK</sub>        | —    | ns |

| NF26 | CLE and ALE hold time                          | t <sub>CALH</sub> | 0.5*t <sub>CK</sub>        | —    | ns |

| NF27 | Data input to first DQS<br>latching transition | t <sub>DQSS</sub> | t <sub>СК</sub>            | _    | ns |

Table 41. Source Synchronous Mode Timing Parameters<sup>1</sup> (continued)

<sup>1</sup> GPMI's sync mode output timing could be controlled by module's internal register, say HW\_GPMI\_TIMING2\_CE\_DELAY, HW\_GPMI\_TIMING\_PREAMBLE\_DELAY, and HW\_GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers' setting. In the above table, we use CE\_DELAY/PRE\_DELAY/POST\_DELAY representing these settings each.

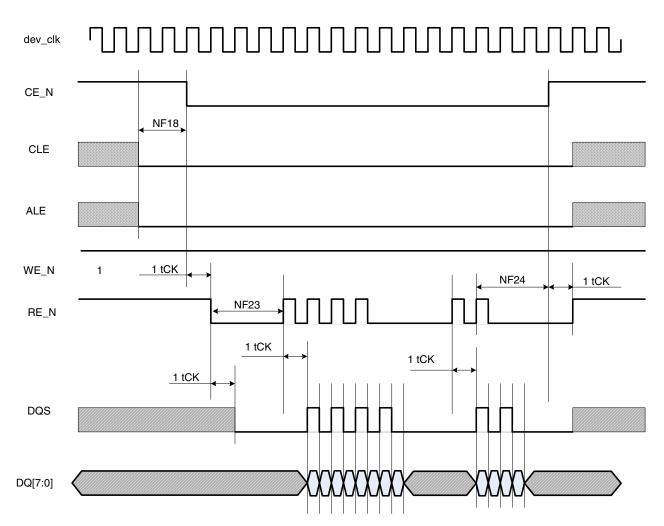

### 4.6.5.3 Samsung Toggle Mode AC Timing

### 4.6.5.3.1 Command and Address Timing

### NOTE

Samsung Toggle Mode command and address timing is the same as ONFI 1.0 compatible Async mode AC timing. Please refer to the above chapter for details.

Figure 16. Samsung Toggle Mode Data Read Timing

| Table 42. Samsung Tog | gle Mode Timing Parameters <sup>1</sup> |

|-----------------------|-----------------------------------------|

|-----------------------|-----------------------------------------|

| ID   | Parameter                     | Symbol           | Tim<br>T = GPMI C        | Unit |    |

|------|-------------------------------|------------------|--------------------------|------|----|

|      |                               |                  | Min.                     | Max. |    |

| NF18 | CE# access time               | t <sub>CE</sub>  | CE_DELAY*t <sub>CK</sub> | —    | ns |

| NF19 | CE# hold time                 | t <sub>CH</sub>  | 0.5 *t <sub>CK</sub>     | —    | ns |

| NF20 | Command/address DQ setup time | t <sub>CAS</sub> | 0.5*t <sub>CK</sub>      | _    | ns |

| NF21 | Command/address DQ hold time  | t <sub>CAH</sub> | 0.5*t <sub>CK</sub>      | _    | ns |

| NF22 | clock period                  | t <sub>CK</sub>  | 7.5                      | —    | ns |

|      | Deversater                               | BCD = 0     |             | BCD = 1  |          | BCD = 2   |           | BCD = 3   |           |

|------|------------------------------------------|-------------|-------------|----------|----------|-----------|-----------|-----------|-----------|

| ID   | Parameter                                | Min         | Мах         | Min      | Max      | Min       | Max       | Min       | Max       |

| WE1  | EIM_BCLK Cycle time <sup>2</sup>         | t           | _           | 2t       | _        | 3t        | —         | 4t        |           |

| WE2  | EIM_BCLK Low Level Width                 | 0.4t        |             | 0.8t     | _        | 1.2t      | —         | 1.6t      |           |

| WE3  | EIM_BCLK High Level<br>Width             | 0.4t        |             | 0.8t     | _        | 1.2t      | _         | 1.6t      | _         |

| WE4  | Clock rise to address valid <sup>3</sup> | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE5  | Clock rise to address invalid            | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE6  | Clock rise to EIM_CSx valid              | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE7  | Clock rise to EIM_CSx invalid            | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE8  | Clock rise to EIM_RW valid               | 0.5t - 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE9  | Clock rise to EIM_RW invalid             | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE10 | Clock rise to EIM_OE valid               | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE11 | Clock rise to EIM_OE invalid             | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE12 | Clock rise to EIM_EBx valid              | 0.5t - 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE13 | Clock rise to EIM_EBx invalid            | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE14 | Clock rise to EIM_LBA valid              | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE15 | Clock rise to EIM_LBA invalid            | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 3t – 1.25 | 3t + 1.75 |

| WE16 | Clock rise to Output Data valid          | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 2t – 1.25 | 2t + 1.75 |

| WE17 | Clock rise to Output Data<br>Invalid     | 0.5t – 1.25 | 0.5t + 1.75 | t – 1.25 | t + 1.75 | 2t – 1.25 | 2t + 1.75 | 2t – 1.25 | 2t + 1.75 |

| WE18 | Input Data setup time to<br>Clock rise   | 2           | _           | 2        | —        | 2         | —         | 2         | —         |

| WE19 | Input Data hold time from<br>Clock rise  | 2.5         |             | 2.5      | —        | 2.5       | —         | 2.5       | —         |

| WE20 | EIM_WAIT setup time to<br>Clock rise     | 2           | —           | 2        | —        | 2         | —         | 2         | —         |

| WE21 | EIM_WAIT hold time from<br>Clock rise    | 2.5         |             | 2.5      | —        | 2.5       | —         | 2.5       | —         |

### Table 43. EIM Bus Timing Parameters <sup>1</sup>

*t* is axi\_clk cycle time. The maximum allowed axi\_clk frequency is 133 MHz, whereas the maximum allowed EIM\_BCLK frequency is 66.5 MHz. As a result, if BCD = 0, axi\_clk must be  $\leq$  66.5 MHz. If BCD = 1, then 133 MHz is allowed for axi\_clk, resulting in a EIM\_BCLK of 66.5 MHz. When the clock branch to EIM is decreased to 66.5 MHz, other buses are impacted which are clocked from this source. See the CCM chapter of the *MCIMX50 Applications Processor Reference Manual* (MCIMX50RM) for a detailed clock tree description.

1

### NOTE

DDR6 and DDR7 can be adjusted by the parameter -DLL\_WR\_DELAY-;

The ideal case is that SDCLK is center aligned to the DRAM\_A[9:0] data valid window;

For this table, HW\_DRAM\_PHY23[14:8] (DLL\_WR\_DELAY) = 0x10;

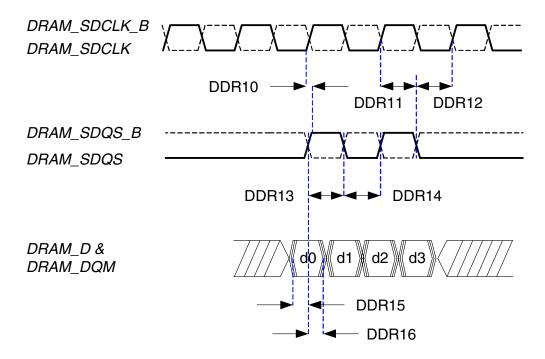

### 4.8.3 DRAM Data Output Timing

The DRAM data output timing is defined for all DDR types: DDR2, LPDDR1, and LPDDR2.

### Figure 30. DRAM Data Output Timing

Table 47. DDR Output AC Timing

| ID                     | Description                                      | Symbol | Min              | Max              | Unit |

|------------------------|--------------------------------------------------|--------|------------------|------------------|------|

| DDR10                  | Positive DQS latching edge to associated CK edge | tDQSS  | -0.3             | 0.3              | ns   |

| DDR11                  | DQS falling edge from CK rising edge—hold time   | tDSH   | 0.5 tCK<br>- 0.3 | 0.5 tCK<br>+ 0.3 | ns   |

| DDR12                  | DQS falling edge to CK rising edge—setup time    | tDSS   | 0.5 tCK<br>- 0.3 | 0.5 tCK<br>+ 0.3 | ns   |

| DDR13                  | DQS output high pulse width                      | tDQSH  | 0.48 tCK         | 0.52 tCK         | ns   |

| DDR14                  | DQS output low pulse width                       | tDQSL  | 0.48 tCK         | 0.52 tCK         | ns   |

| DDR15<br>CK >= 200 MHz | DQ & DQM output setup time relative to DQS       | tDS    | 0.5 tCK<br>- 1.3 | —                | ns   |

| ID    | Description               | Symbol | Min               | Max  | Unit |

|-------|---------------------------|--------|-------------------|------|------|

| DDR21 | DQS to DQ input skew      | tDQSQ  |                   | 0.65 | ns   |

| DDR22 | DQS to DQ input hold time | tQH    | 0.45 tCK<br>-0.85 | _    | ns   |

Table 48. DDR2 Input AC Timing

### NOTE

The timing parameter DDR20(tDQSCK) is not strictly required by this DRAM MC design.

# 4.9 External Peripheral Interfaces

The following sections provide information on external peripheral interfaces.

### 4.9.1 AUDMUX Timing Parameters

The AUDMUX provides programmable interconnect logic for voice, audio and data routing between internal serial interfaces (SSIs) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is hence governed by the SSI module.

# 4.9.2 CSPI and eCSPI Timing Parameters

This section describes the timing parameters of the CSPI and eCSPI modules. The CSPI and eCSPI have separate timing parameters for master and slave modes. The nomenclature used with the CSPI/eCSPI modules and the respective routing of these signals is shown in Table 49.

| Module | I/O Access                                              |

|--------|---------------------------------------------------------|

| eCSPI1 | GPIO, KPP, DISP0_DAT, CSI0_DAT, and EIM_D through IOMUX |

| eCSPI2 | DISP0_DAT, CSI0_DAT, and EIM through IOMUX              |

| CSPI   | DISP0_DAT, EIM_A/D, SD1, and SD2 through IOMUX          |

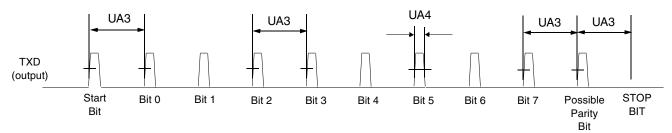

### 4.9.10.3.1 UART IrDA Mode Transmitter

Figure 57 depicts the UART IrDA mode transmit timing with 8 data bit/1 stop bit format. Table 73 lists the transmit timing characteristics.

Figure 57. UART IrDA Mode Transmit Timing Diagram

### Table 73. IrDA Mode Transmit Timing Parameters

| ID  | Parameter                      | Symbol                | Min                                                                       | Мах                                                       | Units |

|-----|--------------------------------|-----------------------|---------------------------------------------------------------------------|-----------------------------------------------------------|-------|

| UA3 | Transmit Bit Time in IrDA mode | t <sub>TIRbit</sub>   | 1/F <sub>baud_rate</sub> <sup>1</sup> – T <sub>ref_clk</sub> <sup>2</sup> | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub>           | _     |

| UA4 | Transmit IR Pulse Duration     | t <sub>TIRpulse</sub> | $(3/16)^{*}(1/F_{baud_rate}) - T_{ref_clk}$                               | (3/16)*(1/F <sub>baud_rate</sub> ) + T <sub>ref_clk</sub> | _     |

<sup>1</sup> F<sub>baud\_rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup>  $T_{ref_clk}$ : The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

### 4.9.10.3.2 UART IrDA Mode Receiver

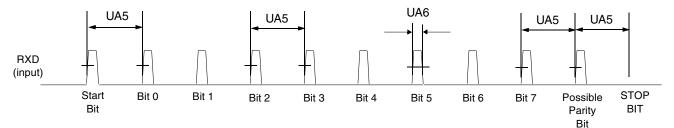

Figure 58 depicts the UART IrDA mode receive timing with 8 data bit/1 stop bit format. Table 74 lists the receive timing characteristics.

Figure 58. UART IrDA Mode Receive Timing Diagram

Table 74. IrDA Mode Receive Timing Parameters

| ID  | Parameter                                  | Symbol                | Min.                                       | Max.                                                      | Units |

|-----|--------------------------------------------|-----------------------|--------------------------------------------|-----------------------------------------------------------|-------|

| UA5 | Receive Bit Time <sup>1</sup> in IrDA mode | t <sub>RIRbit</sub>   | $1/F_{baud_rate}^2 - 1/(16*F_{baud_rate})$ | 1/F <sub>baud_rate</sub> + 1/(16*F <sub>baud_rate</sub> ) | —     |

| UA6 | Receive IR Pulse Duration                  | t <sub>RIRpulse</sub> | 1.41 μs                                    | (5/16)*(1/F <sub>baud_rate</sub> )                        | _     |

<sup>1</sup> The UART receiver can tolerate 1/(16\*F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16\*F<sub>baud\_rate</sub>).

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

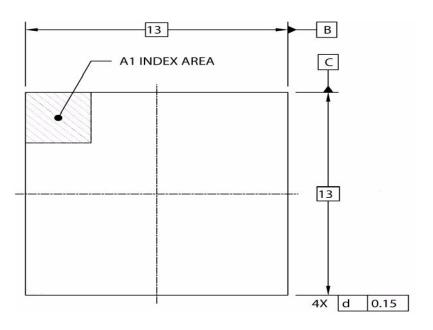

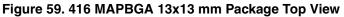

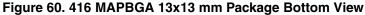

### 5.1.1 Case 416 MAPBGA, 13 x 13 mm, 0.5 mm Pitch Package Views

Figure 59 shows the top view of the 13 x 13 mm package, Figure 60 shows the bottom view (416 soldier balls) of the 13 x 13 mm package, and Figure 61 shows the side view of the 13 x 13 mm package.

ш BOOT\_MODE0 DRAM\_SDQS2 BOOT\_MODE1 DRAM\_SDQS2\_ AB S S S S S S Š S S S 2 S S S S S S S S AB g USB\_OTG\_VDDA25\_ NVCC\_EMI\_DRAM USB\_H1\_VDDA33 USB\_OTG\_DN ۵ TEST\_MODE DRAM\_DQM2 USB\_H1\_DN DISP\_RESET DISP\_BUSY DRAM\_D16 DRAM\_D18 DRAM\_D20 DRAM\_D22 **GND3P0** DISP\_RS SD3\_D0 RESET\_IN GND2P5 GND1P2 GND1P8 SD3\_D2 SD3\_D1 EXTAL VSS AC AC USB\_H1\_VDDA25\_1 USB\_OTG\_VDDA33 NVCC\_EMI\_DRAM USB\_OTG\_DP USB\_H1\_DP DRAM\_D19 DRAM\_D17 DRAM\_D21 DRAM\_D23 DISP\_WR SD3\_CMD DISP\_RD DISP\_CS SD3\_CLK POR\_B VDD3P0 VDD2P5 VDD1P8 SD3\_WP VDD1P2 XTAL VSS VSS VSS AD AD 9 42 13 15 16 18 Ξ 4 17 19 5 N ო 4 ഹ ശ ω თ 20 23 33 24 ~ -

### Table 79. 416 MAPBGA 13x13 mm, 0.5 mm Pitch Ball Map (continued)

### 5.1.3 416 MAPBGA 13 x 13 Power Rails

#### Table 80. 416 MAPBGA 13x13 Ground, Power, Sense, and Reference Contact Signals

| Pin Name      | Ball Number                                                                         | Comments |

|---------------|-------------------------------------------------------------------------------------|----------|

| GND_DCDC      | W5                                                                                  | —        |

| NVCC_EIM      | L7, M7, M8                                                                          | —        |

| NVCC_EMI_DRAM | A21, AA21, AA23, AA24, AC21, AD21, B21, D21, D23, D24, K21, K23, K24, R21, R23, R24 | _        |

| NVCC_EPDC     | M10, N10, P10, R10, U10                                                             | —        |

| NVCC_JTAG     | U9                                                                                  | —        |

| NVCC_KEYPAD   | N8                                                                                  | —        |

| NVCC_LCD      | U11                                                                                 | —        |

| NVCC_MISC     | P8                                                                                  | —        |

| NVCC_NANDF    | V9, V10                                                                             | —        |

| NVCC_RESET    | V8                                                                                  | —        |

| NVCC_SD1      | Т7                                                                                  | —        |

| NVCC_SD2      | U8                                                                                  | _        |

| NVCC_SPI      | R7                                                                                  | —        |

| NVCC_SRTC      | AA1                                                                                                                                                                                                                                                                                                                        | _                                                                                                                  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| NVCC_SSI       | R8                                                                                                                                                                                                                                                                                                                         | _                                                                                                                  |  |  |

| NVCC_UART      | Т8                                                                                                                                                                                                                                                                                                                         | —                                                                                                                  |  |  |

| USB_H1_VDDA25  | AD9                                                                                                                                                                                                                                                                                                                        | Note that on the 416 MAPBGA package,<br>USB_OTG_VDDA25 and USB_H1_VDDA25<br>are shorted together on the substrate. |  |  |

| USB_H1_VDDA33  | AC11                                                                                                                                                                                                                                                                                                                       | Note that on the 416 MAPBGA package,<br>USB_OTG_VDDA33 and USB_H1_VDDA33<br>are shorted together on the substrate. |  |  |

| USB_OTG_VDDA25 | AC9                                                                                                                                                                                                                                                                                                                        | Note that on the 416 MAPBGA package,<br>USB_OTG_VDDA25 and USB_H1_VDDA25<br>are shorted together on the substrate. |  |  |

| USB_OTG_VDDA33 | AD11                                                                                                                                                                                                                                                                                                                       | Note that on the 416 MAPBGA package,<br>USB_OTG_VDDA33 and USB_H1_VDDA33<br>are shorted together on the substrate. |  |  |

| VCC            | H14, H15, H16, H17, J17, K14, K15, K17, L15                                                                                                                                                                                                                                                                                | —                                                                                                                  |  |  |

| VDD_DCDCI      | Y6                                                                                                                                                                                                                                                                                                                         | _                                                                                                                  |  |  |

| VDD_DCDCO      | Y5                                                                                                                                                                                                                                                                                                                         | _                                                                                                                  |  |  |

| VDD1P2         | AD6                                                                                                                                                                                                                                                                                                                        | _                                                                                                                  |  |  |

| VDD1P8         | AD7                                                                                                                                                                                                                                                                                                                        | _                                                                                                                  |  |  |

| VDD2P5         | AD4                                                                                                                                                                                                                                                                                                                        | _                                                                                                                  |  |  |

| VDD3P0         | AD3                                                                                                                                                                                                                                                                                                                        | _                                                                                                                  |  |  |

| VDDA           | P17, R17                                                                                                                                                                                                                                                                                                                   | _                                                                                                                  |  |  |

| VDDAL1         | P15, R15                                                                                                                                                                                                                                                                                                                   | _                                                                                                                  |  |  |

| VDDGP          | G10, G8, G9, H10, H11, H8, H9, J8, K10, K11, K7,<br>K8, L10, L11, L8                                                                                                                                                                                                                                                       | —                                                                                                                  |  |  |

| VDDO25         | N23                                                                                                                                                                                                                                                                                                                        | —                                                                                                                  |  |  |

| VSS            | A1, A18, A24, AA11, AA2, AA9, AC18, AC3, AC4,<br>AC6, AC7, AD1, AD18, AD24, B18, G20, G21,<br>G23, H12, H13, K12, K13, L12, L13, L14, L17,<br>M11, M14, M15, M17, M18, M20, M21, N11, N14,<br>N15, N17, P11, P12, P13, P14, R11, R12, R13,<br>R14, T17, T18, U12, U13, U14, U15, U16, U17,<br>U18, V17, V18, V20, V21, V23 | _                                                                                                                  |  |  |

|                 |                                             | • • • •                                                                                                                                                                                                             |

|-----------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NVCC_RESET      | V8                                          | —                                                                                                                                                                                                                   |

| NVCC_SD1        | Т7                                          | —                                                                                                                                                                                                                   |

| NVCC_SD2        | U8                                          | —                                                                                                                                                                                                                   |

| NVCC_SPI        | R7                                          | —                                                                                                                                                                                                                   |

| NVCC_SRTC       | AA1                                         | —                                                                                                                                                                                                                   |

| NVCC_SSI        | R8                                          |                                                                                                                                                                                                                     |

| NVCC_UART       | Т8                                          |                                                                                                                                                                                                                     |

| POP_EMMC_RST    | A19                                         | This is PoP eMMC 4.4 NAND Reset<br>input pin. This pin does not connect to<br>the i.MX50. If using eMMC 4.4 NAND,<br>this pin can be connected to a GPIO.<br>For non 4.4 eMMC applications, leave<br>floating.      |

| POP_LPDDR2_1.8V | A20, B19, B20, M5, N5                       | This is the 1.8V supply for the PoP LPDDR2. These pins do not connect to the i.MX50.                                                                                                                                |

| POP_LPDDR2_ZQ0  | AA24                                        | This is the PoP LPDDR2 ZQ0 pin. This pin does not connect to the i.MX50. This should be connected on the PCB to a 240 $\Omega$ 1% resistor to ground                                                                |

| POP_LPDDR2_ZQ1  | AA23                                        | This is the PoP LPDDR2 ZQ1 pin. This pin does not connect to the i.MX50. If used, this should be connected on the PCB to a 240 $\Omega$ 1% resistor to ground                                                       |

| POP_NAND_VCC    | D19, D20                                    | This is the 3.3V I/O and memory supply<br>for the PoP eMMC NAND. Note that<br>because the eMMC memory and I/O<br>domains are shorted together, it is not<br>possible to support 1.8 V I/O for the PoP<br>eMMC NAND. |

| USB_VDDA25      | AC9, AD9                                    | Note that on the PoPBGA package,<br>USB_OTG_VDDA25 and<br>USB_H1_VDDA25 are shorted<br>together.                                                                                                                    |

| USB_VDDA33      | AC11, AD11                                  | Note that on the PoPBGA package,<br>USB_OTG_VDDA33 and<br>USB_H1_VDDA33 are shorted<br>together.                                                                                                                    |

| VCC             | H14, H15, H16, H17, J17, K14, K15, K17, L15 | —                                                                                                                                                                                                                   |

| VDD_DCDCI       | Y6                                          | —                                                                                                                                                                                                                   |

| VDD_DCDCO       | Y5                                          | —                                                                                                                                                                                                                   |

| VDD1P2          | AD6                                         | —                                                                                                                                                                                                                   |

| VDD1P8          | AD7                                         | —                                                                                                                                                                                                                   |

Figure 66. 400 MAPBGA 17x17 mm Package Bottom View

|                     | 1                               | -                               | 1                               |                                   | -        | -                                     | 1                           | 1                                  |

|---------------------|---------------------------------|---------------------------------|---------------------------------|-----------------------------------|----------|---------------------------------------|-----------------------------|------------------------------------|

| Pin Name            | 416<br>MAPBGA<br>Ball<br>Number | 416<br>PoPBGA<br>Ball<br>Number | 400<br>MAPBGA<br>Ball<br>Number | Pin Power<br>Domain               | Pad Type | IOMUX<br>MUX<br>CTL<br>After<br>Reset | Direction<br>After<br>Reset | IOMUX<br>PAD CTL<br>After<br>Reset |

| UART2_RTS           | L2                              | C2                              |                                 | NVCC_UART                         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| UART2_RXD           | L1                              | C1                              | L2                              | NVCC_UART                         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| UART2_TXD           | K1                              | B1                              | L1                              | NVCC_UART                         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| UART3_RXD           | L4                              | E4                              | К3                              | NVCC_UART                         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| UART3_TXD           | K4                              | D4                              | J2                              | NVCC_UART                         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| UART4_RXD           | L5                              | D5                              | J3                              | NVCC_UART                         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| UART4_TXD           | K5                              | D6                              | H2                              | NVCC_UART                         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| USB_H1_DN           | AC10                            | AC10                            | W10                             | USB_H1_VDDA25,<br>USB_H1_VDDA33   | ANALOG50 |                                       | _                           | _                                  |

| USB_H1_DP           | AD10                            | AD10                            | Y10                             | USB_H1_VDDA25,<br>USB_H1_VDDA33   | ANALOG50 |                                       | _                           | _                                  |

| USB_H1_GPANAI<br>O  | Y11                             | AA17                            | U10                             | USB_H1_VDDA25,<br>USB_H1_VDDA33   | ANALOG25 |                                       | _                           | _                                  |

| USB_H1_RREFEX<br>T  | AA10                            | AA10                            | U9                              | USB_H1_VDDA25,<br>USB_H1_VDDA33   | ANALOG25 | _                                     | —                           | _                                  |

| USB_H1_VBUS         | Y10                             | AA16                            | V9                              | USB_H1_VDDA25,<br>USB_H1_VDDA33   | ANALOG50 | _                                     | _                           | _                                  |

| USB_OTG_DN          | AC8                             | AC8                             | W8                              | USB_OTG_VDDA25,<br>USB_OTG_VDDA33 | ANALOG50 | _                                     | _                           |                                    |

| USB_OTG_DP          | AD8                             | AD8                             | Y8                              | USB_OTG_VDDA25,<br>USB_OTG_VDDA33 | ANALOG50 |                                       | _                           | _                                  |

| USB_OTG_GPANA<br>IO | ¥7                              | AA14                            | V7                              | USB_OTG_VDDA25,<br>USB_OTG_VDDA33 | ANALOG25 | _                                     | _                           | _                                  |

| USB_OTG_ID          | Y8                              | AA12                            | ¥7                              | USB_OTG_VDDA25,<br>USB_OTG_VDDA33 | ANALOG25 |                                       | _                           | _                                  |

| USB_OTG_RREFE<br>XT | AA8                             | AA8                             | W7                              | USB_OTG_VDDA25,<br>USB_OTG_VDDA33 | ANALOG25 | —                                     | —                           | _                                  |

| USB_OTG_VBUS        | Y9                              | AA13                            | V8                              | USB_OTG_VDDA25,<br>USB_OTG_VDDA33 | ANALOG50 | —                                     | _                           | —                                  |

| VREF                | M23                             | M23                             | K17                             | VDDO25                            | ANALOG   | _                                     | —                           | —                                  |

| WDOG                | G5                              | D9                              | F4                              | NVCC_MISC                         | HVIO     | ALT1                                  | IN                          | —                                  |

| XTAL                | AD5                             | AD5                             | Y6                              | VDD2P5                            | ANALOG   | —                                     | —                           | —                                  |

### Table 85. Alphabetical List of Signal Assignments (continued)

**Revision History**

# 6 Revision History

Table 86 provides a revision history for this data sheet.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 7         | 10/2013 | <ul> <li>Added new part number information for parts with 1 GHz core frequencies:</li> <li>MCIMX508CVK1B</li> <li>MCIMX508CVM1B</li> <li>MCIMX507CVM1B</li> <li>MCIMX507CVK1B</li> <li>Updated sections:</li> <li>Section 1, "Introduction"</li> <li>Table 1, "Ordering Information"</li> <li>Table 11, "i.MX50 Operating Ranges"</li> <li>Table 15, "Maximum Supply Current Consumption—ARM CLK = 1 GHz" (added)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Rev. 6         | 07/2013 | In Table 11, "i.MX50 Operating Ranges," added VCC Stop mode ranges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Rev. 5         | 05/2013 | <ul> <li>In Table 11, "i.MX50 Operating Ranges," changed VCC peripheral supply (LPM) minimum voltage from<br/>0.9 V to 1 V, and changed nominal voltage from 0.95 V to 1.05 V.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Rev. 4         | 01/2013 | <ul> <li>In Table 1, "Ordering Information," on page 7, added new part number information for MCIMX507CVK8B.</li> <li>In Figure 27, "DTACK Read Access," on page 67, updated timing of EIM_DTACK.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Rev. 3         | 10/2012 | <ul> <li>In Table 11, "i.MX50 Operating Ranges," on page 24:</li> <li>—Changed DDR clock rate for reduced performance mode (RPM) of VCC from 100 MHz to 133 MHz</li> <li>—Changed DDR clock rate for high performance mode (HPM) of VCC from 200 MHz to 266 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Rev. 2         | 05/2012 | <ul> <li>In Table 1, "Ordering Information," on page 7, added the following new part numbers: MCIMX508CZK8B, MCIMX503EVM8B, MCIMX502CVK8B, and MCIMX502EVM8B.</li> <li>In Table 1, "Ordering Information," on page 7, added a new column, T<sub>junction</sub>.</li> <li>In Table 3, "Package Feature Comparison," on page 9, added a new row for 416 PoPBGA package.</li> <li>Updated Figure 1, "i.MX50 System Block Diagram," on page 10 by removing "LDOx3" and "DC-DC 1.2V."</li> <li>In Table 5, "Special Signal Considerations," on page 17, updated details for the following signals: DRAM_OPEN/DRAM_OPENFB and DRAM_SDODT0/DRAM_SDODT1</li> <li>In Table 5, "Special Signal Considerations," on page 17, added new rows for the following signals: POP_EMMC_RST, POP_LPDDR2_ZQ0/ZQ1, POP_LPDDR2_1.8V, and POP_NAND_VCC.</li> <li>Added Section 4.1.2.1, "13 x 13 mm MAPBGA Package Thermal Resistance Data."</li> <li>Added Section 4.1.2.2, "13 x 13 mm POPBGA Package Thermal Resistance Data."</li> <li>In Table 11, "i.MX50 Operating Ranges," on page 24, added footnotes for USB_OTG_VDDA25 and USB_OTG_VDDA33.</li> <li>In Table 78, "VBUS Comparators Thresholds," on page 101, changed VBUS input max current to 350 µA.</li> <li>Added Section 5.2, "13 x 13 mm, 0.5 mm Pitch, 416 Pin PoPBGA Package Information."</li> <li>In Table 85, "Alphabetical List of Signal Assignments," on page 124:         <ul> <li>—Added a new column "416 PoPBGA Ball Number"</li> <li>—Changed "USB_H1_VDDA" to "USB_H1_VDDA25, USB_H1_VDDA33"</li> <li>Replace mDDR with LPDDR1 throughout the document.</li> </ul> </li> </ul> |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, and Energy Efficient Solutions logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex are the registered trademarks of ARM Limited. NEON is the trademark of ARM Limited. © 2011–2013 Freescale Semiconductor, Inc.

Document Number: IMX50CEC Rev. 7 10/2013