Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Active                                                     |

| Core Processor                  | ARM® Cortex®-A8                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 800MHz                                                     |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                     |

| RAM Controllers                 | LPDDR, LPDDR2, DDR2                                        |

| Graphics Acceleration           | Yes                                                        |

| Display & Interface Controllers | EPDC, LCD                                                  |

| Ethernet                        | 10/100Mbps (1)                                             |

| SATA                            | -                                                          |

| USB                             | USB 2.0 + PHY (2)                                          |

| Voltage - I/O                   | 1.2V, 1.875V, 2.775V, 3.0V                                 |

| Operating Temperature           | 0°C ~ 70°C (TA)                                            |

| Security Features               | Boot Security, Cryptography, Secure JTAG                   |

| Package / Case                  | 416-LFBGA                                                  |

| Supplier Device Package         | 416-MAPBGA (13x13)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcimx508cvk8b |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### • Pixel Processing Pipeline (ePXP)

The ePXP is a high-performance pixel processor capable of 1 pixel/clock performance for combined operations, such as color-space conversion, alpha blending, gamma mapping, and rotation. The ePXP is enhanced with features specifically for grayscale applications working in conjunction with the electrophoretic display controller to form a full grayscale display solution. In addition, the ePXP supports traditional pixel/frame processing paths for still-image and video processing applications, allowing it to interface with the integrated LCD controller (eLCDIF).

Graphics acceleration

The i.MX50 provides a 2D graphics accelerator with performance up to 200 Mpix/s.

## 1.1.5 Multilevel Memory System

The multilevel memory system of the i.MX50 is based on the L1 instruction and data caches, L2 cache, and internal and external memory. The i.MX50 supports many types of external memory devices, including DDR2, LPDDR2, LPDDR1, NOR Flash, PSRAM, Cellular RAM, NAND Flash (MLC and SLC) and OneNAND<sup>TM</sup>, and managed NAND including eMMC up to rev. 4.4.

## 1.1.6 Smart Speed™ Technology

The i.MX50 device has power management throughout the SOC that enables the rich suite of multimedia features and peripherals to consume minimum power in both active and various low power modes. Smart Speed technology enables the designer to deliver a feature-rich product that requires levels of power that are far less than industry expectations.

## 1.1.7 Interface Flexibility

The i.MX50 supports connection to a variety of interfaces, including an LCD controller for displays, two high-speed USB on-the-go-capable PHYs, multiple expansion card ports (high-speed MMC/SDIO host and others), 10/100 Ethernet controller, and a variety of other popular interfaces (for example, UART,  $I^2C$ , and  $I^2S$  serial audio).

## 1.1.8 Advanced Security

The i.MX50 delivers hardware-enabled security features, such as High-Assurance Boot 4 (HAB4) for signed/authenticated firmware images, basic DRM support with random private keys and AES encryption/decryption, and storage and programmability of on-chip fuses.

## 1.2 Features

The i.MX50 applications processor is based on the ARM Cortex-A8 platform and has the following features:

- MMU, L1 instruction cache, and L1 data cache

- Unified L2 cache

- 800 MHz or 1 GHz target frequency of the core (including NEON, VFPv3, and L1 cache)

i.MX50 Applications Processors for Consumer Products, Rev. 7

- GPU 2D

- SDMA

- USBOH1 (USB OTG and host controller complex)

- FEC Ethernet controller

- MAX AHB crossbar (133 MHz)—This connects the various AHB bus sub-segments in the system and provides decode into the following slaves:

- IP-Bus 1 (66 MHz)—This bus segment contains peripherals accessible by the ARM core and without DMA capability

- IP-Bus 2 (66 MHz)—This bus segment contains peripherals accessible by the ARM core and without DMA capability

- APBH DMA bridge (133 MHz)—The APBH DMA bridge is a master to the MAX for its memory-side DMA operations. The APBH bus is an AMBA APB slave bus providing peripheral access to many of the high-speed IP blocks on the i.MX50.

- IP-Bus 3 (66 MHz)—This third peripheral bus segment contains peripherals accessible by the ARM core and SDMA and as such houses peripherals with DMA capability. The IP-Bus 3 can be accessed by the ARM CPU through IP-Bus 1 and SPBA.

- Quality of service controller (QoSC)—This provides both soft and dynamic arbitration/priority control. The QoSC works in conjunction with the critical display modules such as the eLCDIF and EPDC to provide dynamic priority control, based on real-time metrics.

The i.MX50 makes use of dedicated hardware accelerators to achieve state-of-the-art multimedia performance. The use of hardware accelerators provides both high performance and low power consumption, while freeing up the CPU core for other tasks.

The i.MX50 incorporates the following hardware accelerators:

- GPU2Dv1—2D Graphics accelerator, OpenVG 1.1, 200 Mpix/s performance

- ePXP—enhanced PiXel Processing Pipeline off loading key pixel processing operations required to support both LCD and EPD display applications

The i.MX50 includes the following interfaces to external devices:

#### NOTE

Not all the interfaces are available simultaneously depending on I/O multiplexer configuration.

- Displays:

- EPDC (i.MX508 Only)—Supporting direct-driver TFT backplanes beyond  $2048 \times 1536$  at 106 Hz refresh (or  $4096 \times 4096$  at 20 Hz)

- eLCDIF—Supporting beyond SXGA +  $(1400 \times 1050)$  at 60 Hz resolutions with up to a 32-bit display interface

- On the i.MX508, both displays can be active simultaneously. If both displays are active, the eLCDIF only provides a 16-bit interface due to pin muxing.

- Expansion cards:

- Four SD/MMC card

i.MX50 Applications Processors for Consumer Products, Rev. 7

Table 4. i.MX50 Digital and Analog Modules (continued)

| Block<br>Mnemonic | Block Name                          | Subsystem                             | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDMA              | Smart Direct<br>Memory<br>Access    | Master<br>Connectivity<br>Peripherals | The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by offloading various cores in dynamic data routing. The SDMA features list is as follows:  Powered by a 16-bit instruction-set micro-RISC engine  Multi-channel DMA supports up to 32 time-division multiplexed DMA channels  48 events with total flexibility to trigger any combination of channels  Memory accesses including linear, FIFO, and 2D addressing  Shared peripherals between ARM Cortex-A8 and SDMA  Very fast context-switching with two-level priority-based preemptive multi-tasking  DMA units with auto-flush and prefetch capability  Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)  DMA ports can handle uni-directional and bi-directional flows (copy mode)  Up to 8-word buffer for configurable burst transfers for EMI  Support of byte-swapping and CRC calculations  A library of scripts and API is available |

| SJC               | Secure JTAG<br>Controller           | System<br>Control<br>Peripherals      | The Secure JTAG Controller provides a mechanism for regulating JTAG access, preventing unauthorized JTAG usage while allowing JTAG access for manufacturing tests and software debugging.  The i.MX50 JTAG port provides debug access to several hardware blocks including the ARM processor and the system bus, therefore, it must be accessible for initial laboratory bring-up, manufacturing tests and troubleshooting, and for software debugging by authorized entities. However, if the JTAG port is left unsecured it provides a method for executing unauthorized program code, getting control over secure applications, and running code in privileged modes.  The Secure JTAG controller provides three different security modes that can be selected through an e-fuse configuration to prevent unauthorized JTAG access.                                                                                                                                                                                  |

| SPBA              | Shared<br>Peripheral Bus<br>Arbiter | System<br>Control<br>Peripherals      | SPBA (Shared Peripheral Bus Arbiter) is a two-to-one IP bus interface (IP bus) arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SRTC              | Secure Real<br>Time Clock           | Security<br>Peripherals               | The SRTC incorporates a special System State Retention Register (SSRR) that stores system parameters during system shutdown modes. This register and all SRTC counters are powered by dedicated supply rail NVCC_SRTC. The NVCC_SRTC can be energized separately even if all other supply rails are shut down. This register is helpful for storing warm boot parameters. The SSRR also stores the system security state. In case of a security violation, the SSRR marks the event (security violation indication).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### **Electrical Characteristics**

**Table 5. Special Signal Considerations (continued)**

| Signal Name                  | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_H1_VBUS,<br>USB_OTG_VBUS | These inputs are used by the i.MX50 to detect the presence and level of USB 5 V. If either VBUS input pin is connected to an external USB connector, there is a possibility that a fast 5 V edge rate during a cable attach could trigger the VBUS input ESD protection, which could result in damage to the i.MX50 silicon. To prevent this, the system should use some circuitry to prevent the 5 V edge rate from exceeding 5.25 V / 1 $\mu s$ . Freescale recommends the use of a low pass filter consisting of 100 $\Omega$ resistor in series and a 1 $\mu F$ capacitor close to the i.MX50 pin. In the case when the USB interface is connected on an on-board USB device (for example, 3G modem), the corresponding USB_VBUS pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                                     |

| VREF                         | This pin is the DRAM MC reference voltage input. For LPDDR2 and DDR2, this pin should be connected to $1\!\!\!/$ of NVCC_EMI_DRAM. For LPDDR1, this pin should be left floating. The user may generate VREF using a precision external resistor divider. Use a 1 k $\Omega$ 0.5% resistor to GND and a 1 k $\Omega$ 0.5% resistor to NVCC_EMI_DRAM. Shunt each resistor with a closely-mounted 0.1 $\mu\text{F}$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WDOG_B                       | This output can be used to reset the system PMIC when the i.MX50 processor is locked up. This output is in the NVCC_MISC domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WDOG_RST_B_DEB               | This output may be used to drive out the internal system reset signal to the system reset controller. This is only intended for debug purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XTAL/EXTAL                   | <ul> <li>These pins are the 24 MHz crystal driver as well as the external 24 MHz clock input. If using these pins to directly drive a 24 MHz crystal:</li> <li>The user should tie a 24 MHz fundamental-mode crystal across XTAL and EXTAL.</li> <li>The crystal must be rated for a maximum drive level of 100 μW or higher.</li> <li>The recommended crystal ESR (equivalent series resistance) is 80 Ω or less. If using these pins as a clock input from an external 24 MHz oscillator:</li> <li>The crystal may be eliminated and EXTAL driven directly driven by the external oscillator. The clock signal level on EXTAL must swing from NVCC_SRTC to GND.</li> <li>In this configuration, the XTAL pin must be floated and the COSC_EN bit (bit 12 in the CCR register in the Clock Control Module) must be cleared to put the on-chip oscillator circuit in bypass mode which allows EXTAL to be externally driven.</li> <li>Note there are strict jitter requirements if using an external oscillator in a USB application: &lt; 50 ps peak-to-peak below 1.2 MHz and &lt; 100 ps peak-to-peak above 1.2 MHz for the USB PHY.</li> </ul> |

# 4 Electrical Characteristics

This section provides the device and module-level electrical characteristics of the i.MX50 processor.

#### **NOTE**

These electrical specifications are preliminary. These specifications are not fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications are published after thorough characterization and device qualifications have been completed.

Table 15. Maximum Supply Current Consumption—ARM CLK = 1 GHz

| Condition                                                                           | Supply                                     | Voltage (V) | Current (mA) | Power (mW) |

|-------------------------------------------------------------------------------------|--------------------------------------------|-------------|--------------|------------|

| <ul> <li>Ta = 70°C</li> <li>ARM core in Run mode</li> <li>ARM CLK = 1GHz</li> </ul> | VDDGP                                      | 1.35        | 1000         | 1350       |

|                                                                                     | VCC                                        | 1.275       | 220          | 280.5      |

| • SYS CLK = 266 MHz<br>• AHB CLK = 133 MHz                                          | VDDA/VDDAL1                                | 1.35        | 40           | 54         |

| • DDR CLK = 266 MHz                                                                 | VDD1P2                                     | 1.3         | 15           | 19.5       |

| All voltages operating at maximum levels                                            | VDD1P8                                     | 1.95        | 3            | 5.9        |

| External (MHz) crystal and on-chip oscillator enabled                               | VDD2P5 <sup>1</sup>                        | 2.75        | 2            | 5.5        |

| All modules enabled                                                                 | VDD3P0                                     | 3.3         | 2            | 6.6        |

|                                                                                     | NVCC_EMI_DRAM                              | 1.95        | 8.3          | 16.17      |

|                                                                                     | VDD_DCDCi                                  | 1.95        | 0.021        | 0.041      |

|                                                                                     | USB_OTG_VDDA33 +<br>USB_H1_VDDA33          | 3.6         | 10.8         | 38.8       |

|                                                                                     | VDDO25 + USB_OTG_VDDA25 +<br>USB_H1_VDDA25 | 2.75        | 12.45        | 34.239     |

|                                                                                     | NVCC_RESET                                 | 3.1         | 0.226        | 0.701      |

|                                                                                     | NVCC_SRTC                                  | 1.3         | 0.0035       | 0.0045     |

|                                                                                     | Total                                      | _           | _            | 1812       |

During eFuse programming, the maximum current on VDD2P5 will exceed these values. See Table 13 on page 26 for the maximum VDD2P5 current during eFuse programming.

Table 16. Stop Mode Current and Power Consumption <sup>1</sup>

| Supply      | Voltago (V) | Current (mA)       |                |  |

|-------------|-------------|--------------------|----------------|--|

| Supply      | Voltage (V) | Typical, Ta = 25°C | Max, Ta = 25°C |  |

| VDDGP       | 0.85        | 0.057              | 0.198          |  |

| VCC         | 0.95        | 0.544              | 1.890          |  |

| VDDA/VDDAL1 | 0.95        | 0.071              | 0.247          |  |

The typical power, at Ta = 25°C, will be < 1 mW, including all supplies. Total max power, at Ta=25°C, will not exceed 2.5 mW, including all supplies.

# 4.1.5.1 Conditions for Stop Mode Current and Power Consumption

- ARM core in STOP mode and power gated

- VDDGP, VCC, and VDDA/VDDAL1 voltages at suspend levels

- VDD3P0, VDD2P5, VDD1P8, and VDD1P2 powered off

- USB\_VDDA25 and USB\_VDDA33 powered off

i.MX50 Applications Processors for Consumer Products, Rev. 7

Table 23. HVIO DC Electrical Characteristics (continued)

| DC Electrical Characteristics                                               | Symbol | Test Conditions                                         | MIN                    | ТҮР | MAX         | Units |

|-----------------------------------------------------------------------------|--------|---------------------------------------------------------|------------------------|-----|-------------|-------|

| Pull-up resistor (22 KΩ PU)                                                 | Rpu    | Vi=OVDD/2                                               | 22                     | 29  | 71          | ΚΩ    |

| Pull-up resistor (47 KΩ PU)                                                 | Rpu    | Vi=OVDD/2                                               | 43                     | 59  | 148         | ΚΩ    |

| Pull-up resistor (100 KΩ PU)                                                | Rpu    | Vi=OVDD/2                                               | 46                     | 62  | 156         | ΚΩ    |

| Pull-down resistor (100 KΩ PD)                                              | Rpd    | Vi=OVDD/2                                               | 53                     | 77  | 256         | ΚΩ    |

| Input current (no pull-up/down)                                             | IIN    | VI = 0<br>VI=OVDD                                       | _                      | 2.8 | 470<br>50   | nA    |

| Input current (22 KΩ PU)                                                    | IIN    | VI = 0<br>VI=OVDD                                       | _                      | _   | 153<br>0.05 | μА    |

| Input current (47 KΩ PU)                                                    | IIN    | VI = 0<br>VI=OVDD                                       | _                      |     | 77<br>0.05  | μА    |

| Input current (100 KΩ PU)                                                   | IIN    | VI = 0<br>VI=OVDD                                       | _                      |     | 73<br>0.05  | μА    |

| Input current (100 KΩ PD)                                                   | IIN    | VI = 0<br>VI=OVDD                                       | _                      | _   | 0.47<br>63  | μА    |

| High-level output current, high voltage mode                                | loh_hv | Vol=0.8*OVDD<br>Low Drive<br>Medium Drive<br>High Drive | -5.1<br>-10.2<br>-15.3 | _   | _           | mA    |

| External pull-up / pull-down resistor required to overdrive internal keeper | Rext   | _                                                       | _                      |     | 2.5         | ΚΩ    |

To maintain a valid level, the transitioning edge of the input must sustain a constant slew rate (monotonic) from the current DC level through to the target DC level, VIL or VIH. Monotonic input transition time is from 0.1 ns to 1 s. VIL and VIH do not apply when hysteresis is enabled.

# 4.4 Output Buffer Impedance Characteristics

This section defines the I/O impedance parameters of the i.MX50 processor.

<sup>&</sup>lt;sup>2</sup> Hysteresis of 250 mV is guaranteed over all operating conditions when hysteresis is enabled.

## 4.5 I/O AC Parameters

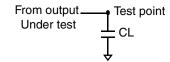

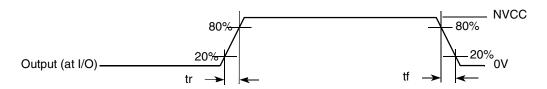

The load circuit and output transition time waveforms are shown in Figure 4 and Figure 5. The AC electrical characteristics for slow and fast I/O are presented in the Table 27 and Table 28, respectively. Note that the fast or slow I/O behavior is determined by the appropriate control bit in the IOMUX control registers.

CL includes package, probe and fixture capacitance

Figure 4. Load Circuit for Output

**Figure 5. Output Transition Time Waveform**

### 4.5.1 GPIO I/O Slow AC Parameters

Table 27 shows the AC parameters for GPIO slow I/O.

Table 27, GPIO I/O Slow AC Parameters

| Parameter                                     | Symbol | Test Condition | Min                    | Тур | Max                     | Unit  |

|-----------------------------------------------|--------|----------------|------------------------|-----|-------------------------|-------|

| Output Pad Transition Times (Max Drive)       | tr, tf | 15 pF<br>35 pF |                        |     | 1.91/1.52<br>3.07/2.65  | ns    |

| Output Pad Transition Times (High Drive)      | tr, tf | 15 pF<br>35 pF |                        |     | 2.22/1.81<br>3.81/3.42  | ns    |

| Output Pad Transition Times (Medium Drive)    | tr, tf | 15 pF<br>35 pF |                        |     | 2.88/2.42<br>5.43/5.02  | ns    |

| Output Pad Transition Times (Low Drive)       | tr, tf | 15 pF<br>35 pF |                        |     | 4.94/4.50<br>10.55/9.70 | ns    |

| Output Pad Slew Rate (Max Drive) <sup>1</sup> | tps    | 15 pF<br>35 pF | 0.5/0.65<br>0.32/0.37  |     |                         | V/ns  |

| Output Pad Slew Rate (High Drive)             | tps    | 15 pF<br>35 pF | 0.43/0.54<br>0.26/0.41 |     |                         | V/ns  |

| Output Pad Slew Rate (Medium Drive)           | tps    | 15 pF<br>35 pF | 0.34/0.41<br>0.18/0.2  |     |                         | V/ns  |

| Output Pad Slew Rate (Low Drive)              | tps    | 15 pF<br>35 pF | 0.20/0.22<br>0.09/0.1  |     |                         | V/ns  |

| Output Pad di/dt (Max Drive)                  | tdit   |                |                        |     | 30                      | mA/ns |

### **Electrical Characteristics**

## 4.5.4 LVIO I/O Fast AC Parameters

Table 30 shows the AC parameters for LVIO fast I/O.

Table 30. LVIO I/O Fast AC Parameters

| Parameter                                     | Symbol | Test Condition | Min                    | Тур | Max                      | Unit  |

|-----------------------------------------------|--------|----------------|------------------------|-----|--------------------------|-------|

| Output Pad Transition Times (Max Drive)       | tr, tf | 15 pF<br>35 pF |                        |     | 1.44/1.27<br>2.78/2.56   | ns    |

| Output Pad Transition Times (High Drive)      | tr, tf | 15 pF<br>35 pF |                        |     | 1.80/1.61<br>3.59/3.34   | ns    |

| Output Pad Transition Times (Medium Drive)    | tr, tf | 15 pF<br>35 pF |                        |     | 2.55/2.28<br>5.32/5.01   | ns    |

| Output Pad Transition Times (Low Drive)       | tr, tf | 15 pF<br>35 pF |                        |     | 4.74/4.59<br>10.59/10.21 | ns    |

| Output Pad Slew Rate (Max Drive) <sup>1</sup> | tps    | 15 pF<br>35 pF | 0.69/0.78<br>0.36/0.39 |     |                          | V/ns  |

| Output Pad Slew Rate (High Drive)             | tps    | 15 pF<br>35 pF | 0.55/0.61<br>0.28/0.30 |     |                          | V/ns  |

| Output Pad Slew Rate (Medium Drive)           | tps    | 15 pF<br>35 pF | 0.39/0.44<br>0.19/0.20 |     |                          | V/ns  |

| Output Pad Slew Rate (Low Drive)              | tps    | 15 pF<br>35 pF | 0.21/0.22<br>0.09/0.10 |     |                          | V/ns  |

| Output pad di/dt (Max drive)                  | tdit   | _              | _                      | _   | 70                       | mA/ns |

| Output pad di/dt (High drive)                 | tdit   | _              | _                      | _   | 54                       | mA/ns |

| Output pad di/dt (Medium drive)               | tdit   | _              | _                      | _   | 35                       | mA/ns |

| Output pad di/dt (Low drive)                  | tdit   | _              | _                      | _   | 18                       | mA/ns |

| Input transition times <sup>2</sup>           | trm    | _              | _                      | _   | 25                       | ns    |

<sup>1</sup> tps is measured between VIL to VIH for rising edge and between VIH to VIL for falling edge.

# 4.5.5 HVIO I/O Low Voltage (1.8 V) AC Parameters

Table 27 shows the AC parameters for HVIO I/O Low Voltage (1.8 V).

Table 31. HVIO I/O Low Voltage (1.8 V) AC Parameters

| Parameter                                  | Symbol | Test Condition | Min | Тур | Max                    | Unit |

|--------------------------------------------|--------|----------------|-----|-----|------------------------|------|

| Output Pad Transition Times (High Drive)   | tr, tf | 15 pF<br>35 pF |     |     | 1.82/1.97<br>3.39/3.57 | ns   |

| Output Pad Transition Times (Medium Drive) | tr, tf | 15 pF<br>35 pF |     |     | 2.48/2.62<br>4.95/5.14 | ns   |

| Output Pad Transition Times (Low Drive)    | tr, tf | 15 pF<br>35 pF |     |     | 4.57/4.77<br>9.60/9.91 | ns   |

i.MX50 Applications Processors for Consumer Products, Rev. 7

<sup>&</sup>lt;sup>2</sup> Hysteresis mode is recommended for inputs with transition time greater than 25 ns.

Table 40. Asynchronous Mode Timing Parameters<sup>1</sup> (continued)

| ID   | Parameter          | Symbol | Timing<br>T <sup>2</sup> = GPMI Clock Cycle <sup>3</sup> |       | Example 1<br>GPMI Clock<br>T = 1 | $\approx 100 \mathrm{MHz}$ | Unit |

|------|--------------------|--------|----------------------------------------------------------|-------|----------------------------------|----------------------------|------|

|      |                    |        | Min.                                                     | Max.  | Min.                             | Max.                       |      |

| NF5  | WE pulse width     | tWP    | DS                                                       | *T    | 1                                | 0                          | ns   |

| NF6  | ALE setup time     | tALS   | (AS+1)*T                                                 | _     | 10                               | _                          | ns   |

| NF7  | ALE hold time      | tALH   | (DH+1)*T                                                 | _     | 20                               | _                          | ns   |

| NF8  | Data setup time    | tDS    | DS*T                                                     | _     | 10                               | _                          | ns   |

| NF9  | Data hold time     | tDH    | DH*T                                                     | _     | 10                               | _                          | ns   |

| NF10 | Write cycle time   | tWC    | (DS+E                                                    | DH)*T | 20                               |                            | ns   |

| NF11 | WE hold time       | tWH    | DH                                                       | l*T   | 10                               |                            | ns   |

| NF12 | Ready to RE low    | tRR    | (AS+1)*T                                                 | _     | 10                               | _                          | ns   |

| NF13 | RE pulse width     | tRP    | DS*T                                                     | _     | 10                               | _                          | ns   |

| NF14 | READ cycle time    | tRC    | (DS+DH)*T                                                | _     | 20                               | _                          | ns   |

| NF15 | RE high hold time  | tREH   | DH*T                                                     |       | 10                               | _                          | ns   |

| NF16 | Data setup on read | tDSR   | N/A                                                      |       | 10                               | _                          | ns   |

| NF17 | Data hold on read  | tDHR   | N/                                                       | 'A    | 10                               | _                          | ns   |

GPMI's Async Mode output timing could be controlled by module's internal register, say HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers' setting. In the above table, we use AS/DS/DH representing these settings each.

$<sup>^{2}\,</sup>$  T represents for the GPMI clock period.

<sup>&</sup>lt;sup>3</sup> AS minimum value could be 0, while DS/DH minimum value is 1.

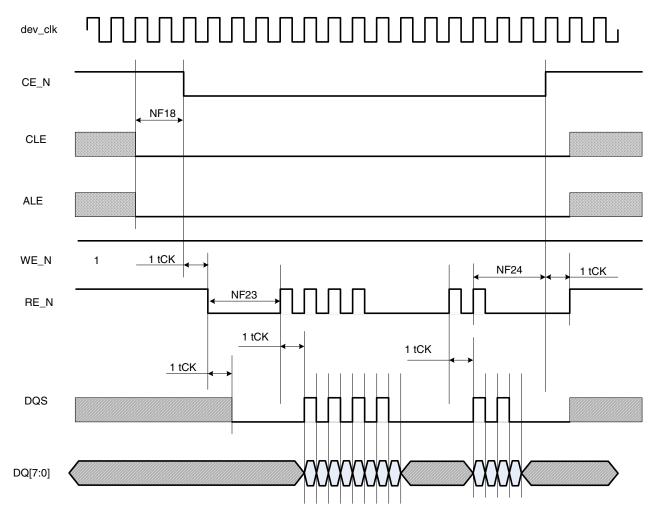

Figure 16. Samsung Toggle Mode Data Read Timing

Table 42. Samsung Toggle Mode Timing Parameters<sup>1</sup>

| ID   | Parameter                     | Symbol           | Timing<br>T = GPMI Clock Cycle |      | Unit |

|------|-------------------------------|------------------|--------------------------------|------|------|

|      |                               |                  | Min.                           | Max. |      |

| NF18 | CE# access time               | t <sub>CE</sub>  | CE_DELAY*t <sub>CK</sub>       | _    | ns   |

| NF19 | CE# hold time                 | t <sub>CH</sub>  | 0.5 *t <sub>CK</sub>           | _    | ns   |

| NF20 | Command/address DQ setup time | t <sub>CAS</sub> | 0.5*t <sub>CK</sub>            | _    | ns   |

| NF21 | Command/address DQ hold time  | t <sub>CAH</sub> | 0.5*t <sub>CK</sub>            | _    | ns   |

| NF22 | clock period                  | t <sub>CK</sub>  | 7.5                            | _    | ns   |

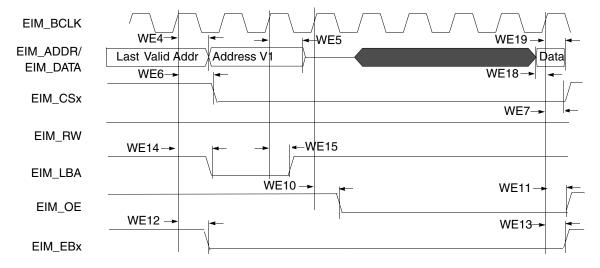

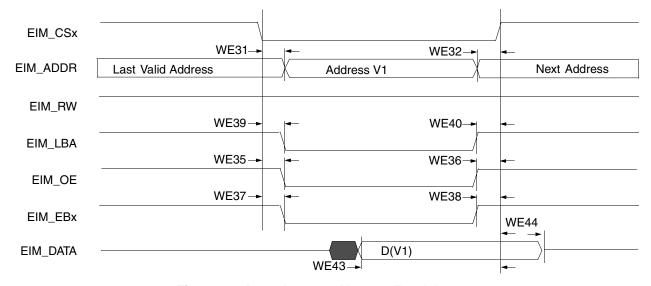

Figure 24. 16-Bit Muxed A/D Mode, Synchronous Read Access, WSC=7, RADVN=1, ADH=1, OEA=2

Figure 25, Figure 26, Figure 27, and Table 44 help to determine timing parameters relative to the chip select (CS) state for asynchronous and DTACK EIM accesses with corresponding EIM bit fields and the timing parameters mentioned above.

Figure 25. Asynchronous Memory Read Access

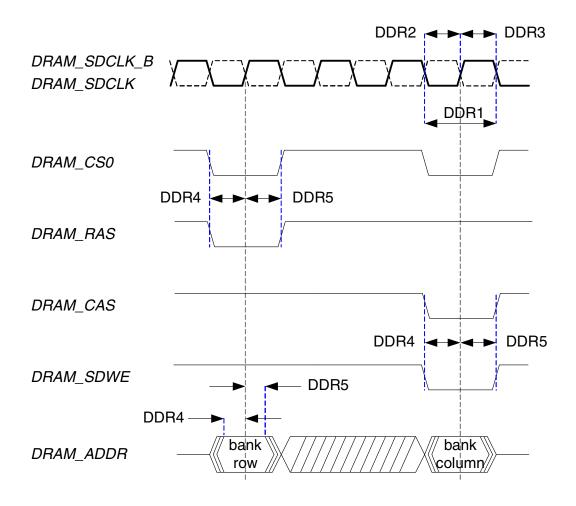

## 4.8.1 DRAM Command & Address Output Timing—DDR2 and LPDDR1

The following diagrams and tables specify the timings related to the address and command pins, which interfaces DDR2 and LPDDR1 memory devices.

Figure 28. DRAM Command/Address Output Timing—DDR2 and LPDDR1

Table 45. EMI Command/Address AC Timing

| ID   | Description                           | Symbol | Min              | Max      | Unit |

|------|---------------------------------------|--------|------------------|----------|------|

| DDR1 | CK cycle time                         | tCK    | 3.75             | _        | ns   |

| DDR2 | CK high level width                   | tCH    | 0.48 tCK         | 0.52 tCK | ns   |

| DDR3 | CK low level width                    | tCL    | 0.48 tCK         | 0.52 tCK | ns   |

| DDR4 | Address and control output setup time | tIS    | 0.5 tCK<br>- 0.3 | _        | ns   |

| DDR5 | Address and control output hold time  | tlH    | 0.5 tCK<br>- 0.3 |          | ns   |

i.MX50 Applications Processors for Consumer Products, Rev. 7

| ID  | Parameters                               | Symbol            | Min | Тур | Max | Unit |

|-----|------------------------------------------|-------------------|-----|-----|-----|------|

| OW1 | Reset Time Low                           | t <sub>RSTL</sub> | 480 | 511 | _1  | μs   |

| OW2 | Presence Detect High                     | t <sub>PDH</sub>  | 15  | _   | 60  | μs   |

| OW3 | Presence Detect Low                      | t <sub>PDL</sub>  | 60  | _   | 240 | μs   |

| OW4 | Reset Time High (includes recovery time) | t <sub>RSTH</sub> | 480 | 512 | _   | μs   |

In order not to mask signaling by other devices on the 1-Wire bus,  $t_{RSTL} + t_{R}$  should always be less than 960  $\mu$ s.

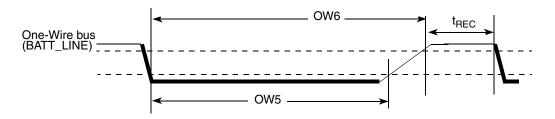

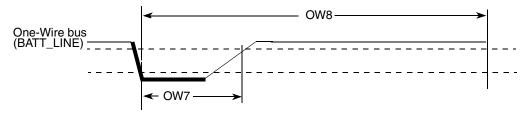

Figure 43 depicts Write 0 Sequence timing, and Table 61 lists the timing parameters.

Figure 43. Write 0 Sequence Timing Diagram

**Table 61. WR0 Sequence Timing Parameters**

| ID  | Parameter              | Symbol            | Min | Тур | Max | Unit |

|-----|------------------------|-------------------|-----|-----|-----|------|

| OW5 | Write 0 Low Time       | t <sub>LOW0</sub> | 60  | 100 | 120 | μs   |

| OW6 | Transmission Time Slot | t <sub>SLOT</sub> | OW5 | 117 | 120 | μs   |

| _   | Recovery time          | t <sub>REC</sub>  | 1   | _   | _   | μs   |

Figure 44 depicts Write 1 Sequence timing, Figure 45 depicts the Read Sequence timing, and Table 62 lists the timing parameters.

Figure 44. Write 1 Sequence Timing Diagram

99

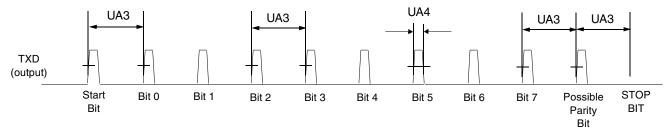

#### 4.9.10.3.1 UART IrDA Mode Transmitter

Figure 57 depicts the UART IrDA mode transmit timing with 8 data bit/1 stop bit format. Table 73 lists the transmit timing characteristics.

Figure 57. UART IrDA Mode Transmit Timing Diagram

**Table 73. IrDA Mode Transmit Timing Parameters**

| ID  | Parameter                      | Symbol                | Min                                                 | Max                                             | Units |

|-----|--------------------------------|-----------------------|-----------------------------------------------------|-------------------------------------------------|-------|

| UA3 | Transmit Bit Time in IrDA mode | t <sub>TIRbit</sub>   | 1/F <sub>baud_rate</sub> 1 - T <sub>ref_clk</sub> 2 | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub> | _     |

| UA4 | Transmit IR Pulse Duration     | t <sub>TIRpulse</sub> | $(3/16)*(1/F_{baud\_rate}) - T_{ref\_clk}$          | $(3/16)*(1/F_{baud\_rate}) + T_{ref\_clk}$      | _     |

<sup>&</sup>lt;sup>1</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

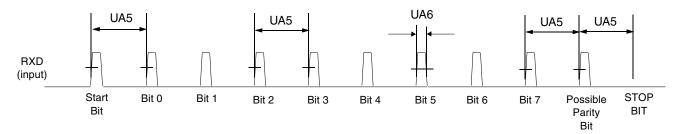

### 4.9.10.3.2 UART IrDA Mode Receiver

Figure 58 depicts the UART IrDA mode receive timing with 8 data bit/1 stop bit format. Table 74 lists the receive timing characteristics.

Figure 58. UART IrDA Mode Receive Timing Diagram

**Table 74. IrDA Mode Receive Timing Parameters**

| ID  | Parameter                                  | Symbol                | Min.                                                                   | Max.                                                      | Units |

|-----|--------------------------------------------|-----------------------|------------------------------------------------------------------------|-----------------------------------------------------------|-------|

| UA5 | Receive Bit Time <sup>1</sup> in IrDA mode | t <sub>RIRbit</sub>   | 1/F <sub>baud_rate</sub> <sup>2</sup> - 1/(16*F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> + 1/(16*F <sub>baud_rate</sub> ) | _     |

| UA6 | Receive IR Pulse Duration                  | t <sub>RIRpulse</sub> | 1.41 μs                                                                | (5/16)*(1/F <sub>baud_rate</sub> )                        | _     |

The UART receiver can tolerate 1/(16\*F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16\*F<sub>baud\_rate</sub>).

<sup>&</sup>lt;sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

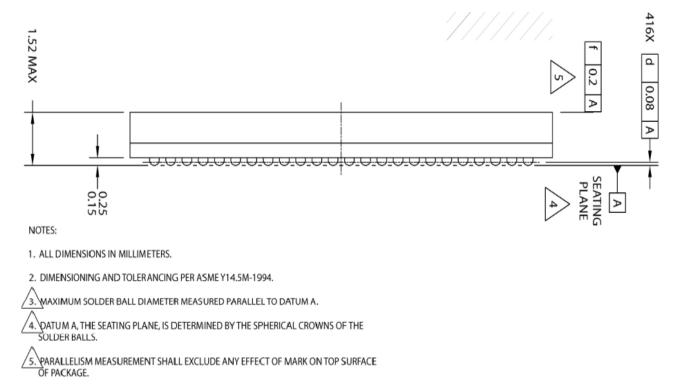

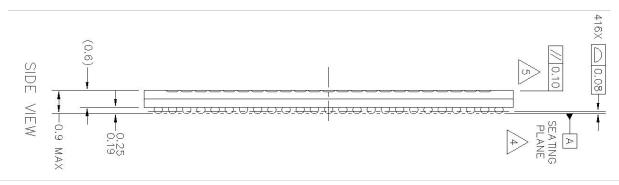

Figure 61. 416 MAPBGA 13x13 mm Package Side View

The following notes apply to Figure 59, Figure 60, and Figure 61:

- Unless otherwise specified dimensions are in millimeters.

- All dimensions and tolerances conform to ASME Y14.5M-1994.

- Parallelism measurement shall exclude any effect of mark on top surface of package.

i.MX50 Applications Processors for Consumer Products, Rev. 7

### **Package Information and Contact Assignments**

Table 79. 416 MAPBGA 13x13 mm, 0.5 mm Pitch Ball Map (continued)

| œ        | SD1_CMD     | SD1_D0        | OZ | SD1_D2   | SD1_D3     | OZ        | NVCC_SPI        | NVCC_SSI        | ON           | NVCC_EPDC      | NSS            | NSS      | NSS      | NSS      | VDDAL1   | ON       | VDDA     | DRAM_SDODT1 | NO     | DRAM_SDCLK_1_B | NVCC_EMI_DRAM | NO | NVCC_EMI_DRAM | NVCC_EMI_DRAM | æ  |

|----------|-------------|---------------|----|----------|------------|-----------|-----------------|-----------------|--------------|----------------|----------------|----------|----------|----------|----------|----------|----------|-------------|--------|----------------|---------------|----|---------------|---------------|----|

| _        | SD2_D0      | SD2_D1        | NC | SD2_CD   | SD2_WP     | NC        | NVCC_SD1        | NVCC_UART       | NC           | NC             | NC             | NC       | NC       | NC       | NC       | NC       | VSS      | VSS         | NC     | DRAM_SDCLK_1   | DRAM_CS0      | NC | DRAM_D6       | DRAM_DQM0     | ⊢  |

| <b>ס</b> | SD2_CLK     | SD2_D5        | NC | SD2_D6   | SD2_D7     | NC        | JTAG_TDO        | NVCC_SD2        | NVCC_JTAG    | NVCC_EPDC      | NVCC_LCD       | NSS      | NSS      | VSS      | NSS      | VSS      | VSS      | NSS         | NC     | DRAM_SDCKE     | DRAM_CS1      | NC | DRAM_D5       | DRAM_D7       | n  |

| >        | SD2_D2      | SD2_D3        | NC | SD2_D4   | SD2_CMD    | NC        | JTAG_MOD        | NVCC_RESET      | NVCC_NANDF   | NVCC_NANDF     | CHGR_DET_B     | DISP_D11 | DISP_D12 | DISP_D13 | DISP_D14 | DISP_D15 | NSS      | NSS         | NC     | NSS            | NSS           | NC | NSS           | DRAM_D4       | >  |

| W        | PMIC_ON_REQ | PMIC_STBY_REQ | OZ | JTAG_TCK | GND_DCDC   | OZ        | ON              | OZ              | OZ           | OZ             | OZ             | ON       | ON       | OZ       | ON       | OZ       | OZ       | OZ          | ON     | DRAM_A0        | DRAM_A1       | ON | DRAM_D2       | DRAM_D3       | M  |

| >        | CKIL        | EOKIL         | OZ | JTAG_TMS | VDD_DCDCO  | VDD_DCDCI | USB_OTG_GPANAIO | USB_OTG_ID      | USB_OTG_VBUS | USB_H1_VBUS    | USB_H1_GPANAIO | DISP_D1  | DISP_D3  | DISP_D5  | DISP_D7  | DISP_D9  | DISP_D10 | SD3_D5      | SD3_D7 | DRAM_A2        | DRAM_A3       | ON | DRAM_D1       | DRAM_D0       | >  |

| АА       | NVCC_SRTC   | NGND_SRTC     | ON | JTAG_TDI | JTAG_TRSTB | CKIH      | GND_KEL         | USB_OTG_RREFEXT | NSS          | USB_H1_RREFEXT | NSS            | DISP_D0  | DISP_D2  | DISP_D4  | DISP_D6  | DISP_D8  | SD3_D3   | SD3_D4      | SD3_D6 | DRAM_A4        | NVCC_EMI_DRAM | NC | NVCC_EMI_DRAM | NVCC_EMI_DRAM | АА |

#### NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

$\stackrel{\frown}{3.}$  maximum solder ball diameter measured parallel to datum a.

DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

PARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SURFACE OF PACKAGE.

ΑD AC AB W U R 0.25 М 23X 0.5 G Ε D ካ3 15 17 1 2 14 16 18 9 11 <sup>1</sup> 10 12 INDEX AREA Ø0.05(M) BOTTOM VIEW

Figure 63. 416 PoPBGA 13 x 13 Package Side View

Figure 64. 416 PoPBGA 13 x 13 mm Package Bottom View

The following notes apply to Figure , Figure 63, and Figure 64:

• Unless otherwise specified dimensions are in millimeters.

i.MX50 Applications Processors for Consumer Products, Rev. 7

### **Package Information and Contact Assignments**

## Table 83. 400 MAPBGA 17 x 17 mm Ball Map (continued)

| -            | æ             | ۵                                                                                   | Z                           | Σ             | 7             | ¥                           |

|--------------|---------------|-------------------------------------------------------------------------------------|-----------------------------|---------------|---------------|-----------------------------|

| SD2_CD       | SD1_CLK       | SD1_D1                                                                              | ECSPI2_MOSI                 | CSPI_SCLK     | UART2_TXD     | UART1_RXD                   |

| SD2_WP       | SD1_D0        | SD1_D3                                                                              | ECSP11_SCLK                 | ECSPI2_SS0    | UART2_RXD     | UART1_RTS                   |

| SD2_CLK      | SD2_D0        | SD1_D2                                                                              | ECSPI1_SS0                  | ECSPI1_MISO   | CSPI_MOSI     | UART3_RXD                   |

| SD2_D3       | SD2_D6        | SD1_CMD                                                                             | ECSPI2_SCLK                 | ECSPI1_MOSI   | ECSPI2_MISO   | CSPI_MISO                   |

| NSS          | NVCC_SRTC     | NVCC_SD2                                                                            | NVCC_SD1                    | NVCC_SPI      | NVCC_UART     | NVCC_SSI                    |

| VDD_DCDCO    | GND_DCDC      | NVCC_RESET                                                                          | VSS                         | NSS           | VDDGP         | VDDGP                       |

| GND_KEL      | VDD_DCDCI     | VSS                                                                                 | VSS                         | VSS           | VSS           | VDDGP                       |

| JTAG_MOD     | JTAG_TCK      | VSS                                                                                 | VSS                         | VSS           | VSS           | VSS                         |

| JTAG_TDO     | JTAG_TMS      | NVCC_JTAG                                                                           | VSS                         | VSS           | VSS           | VDDA                        |

| CHGR_DET_B   | VSS           | NVCC_LCD                                                                            | VSS                         | NCC           | NCC           | NCC                         |

| DISP_D1      | NSS           | NVCC_NANDF                                                                          | NSS                         | NCC           | NCC           | NCC                         |

| DISP_CS      | NSS           | NVCC_NANDF                                                                          | NSS                         | NSS           | NCC           | NCC                         |

| DISP_D13     | NSS           | NSS                                                                                 | NSS                         | NSS           | NSS           | NSS                         |

| DISP_RESET   | NSS           | VSS                                                                                 | NVCC_EMI_DRAM               | NSS           | NSS           | NVCC_EMI_DRAM               |

| SD3_D7       | VSS           | NVCC_EMI_DRAM                                                                       | NVCC_EMI_DRAM NVCC_EMI_DRAM | NSS           | NVCC_EMI_DRAM | NVCC_EMI_DRAM NVCC_EMI_DRAM |

| SD3_D2       | NVCC_EMI_DRAM | NVCC_EMI_DRAM NVCC_EMI_DRAM NVCC_EMI_DRAM NVCC_EMI_DRAM NVCC_EMI_DRAM NVCC_EMI_DRAM | NVCC_EMI_DRAM               | NVCC_EMI_DRAM | NVCC_EMI_DRAM | NVCC_EMI_DRAM               |

| DRAM_A0      | DRAM_A4       | DRAM_CS0                                                                            | DRAM_DQM0                   | DRAM_SDQS0    | VDD025        | VREF                        |

| DRAM_A1      | DRAM_SDCKE    | DRAM_CS1                                                                            | DRAM_D5                     | DRAM_SDQS0_B  | DRAM_SDWE     | DRAM_SDODT0                 |

| DRAM_SDQS2   | DRAM_D1       | DRAM_D3                                                                             | DRAM_D7                     | DRAM_SDBA2    | DRAM_A6       | DRAM_A5                     |

| DRAM_SDQS2_B | DRAM_D0       | DRAM_D2                                                                             | DRAM_D4                     | DRAM_D6       | DRAM_A8       | DRAM_A7                     |

### **Package Information and Contact Assignments**

Table 85. Alphabetical List of Signal Assignments (continued)

| Pin Name      | 416<br>MAPBGA<br>Ball<br>Number | 416<br>PoPBGA<br>Ball<br>Number | 400<br>MAPBGA<br>Ball<br>Number | Pin Power<br>Domain | Pad Type | IOMUX<br>MUX<br>CTL<br>After<br>Reset | Direction<br>After<br>Reset | IOMUX<br>PAD CTL<br>After<br>Reset |

|---------------|---------------------------------|---------------------------------|---------------------------------|---------------------|----------|---------------------------------------|-----------------------------|------------------------------------|

| JTAG_TDI      | AA4                             | AA4                             | U8                              | NVCC_JTAG           | GPIO     | ALT0                                  | IN                          | 47K PU                             |

| JTAG_TDO      | U7                              | V4                              | Т9                              | NVCC_JTAG           | GPIO     | ALT0                                  | OUT-LO                      | Keeper                             |

| JTAG_TMS      | Y4                              | Y4                              | R9                              | NVCC_JTAG           | GPIO     | ALT0                                  | IN                          | 47K PU                             |

| JTAG_TRSTB    | AA5                             | AA5                             | U7                              | NVCC_JTAG           | GPIO     | ALT0                                  | IN                          | 47K PU                             |

| KEY_COL0      | B1                              | A9                              | B1                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| KEY_COL1      | B2                              | A10                             | B2                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| KEY_COL2      | C1                              | B9                              | C1                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| KEY_COL3      | C2                              | B10                             | C2                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| KEY_ROW0      | D1                              | A8                              | D1                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| KEY_ROW1      | D2                              | B8                              | D2                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| KEY_ROW2      | D4                              | D7                              | C3                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| KEY_ROW3      | E4                              | A7                              | D3                              | NVCC_KEYPAD         | HVIO     | ALT1                                  | IN                          | Keeper                             |

| OWIRE         | G7                              | D12                             | E5                              | NVCC_MISC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| PMIC_ON_REQ   | W1                              | W1                              | Y3                              | NVCC_SRTC           | GPIO     | ALT0                                  | OUT-LO                      | _                                  |

| PMIC_STBY_REQ | W2                              | W2                              | Y2                              | NVCC_SRTC           | GPIO     | ALT0                                  | OUT-LO                      | _                                  |

| POR_B         | AD2                             | AD2                             | Y5                              | NVCC_RESET          | LVIO     | ALT0                                  | IN                          | 100K PU                            |

| PWM1          | F5                              | D11                             | E4                              | NVCC_MISC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| PWM2          | F4                              | D10                             | E3                              | NVCC_MISC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| RESET_IN_B    | AC1                             | AC1                             | W3                              | NVCC_RESET          | LVIO     | ALT0                                  | IN                          | 100K PU                            |

| SD1_CLK       | P1                              | M1                              | R1                              | NVCC_SD1            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD1_CMD       | R1                              | N1                              | P4                              | NVCC_SD1            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD1_D0        | R2                              | P2                              | R2                              | NVCC_SD1            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD1_D1        | P2                              | N2                              | P1                              | NVCC_SD1            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD1_D2        | R4                              | M2                              | P3                              | NVCC_SD1            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD1_D3        | R5                              | R4                              | P2                              | NVCC_SD1            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD2_CD        | T4                              | J4                              | T1                              | NVCC_SD2            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD2_CLK       | U1                              | E1                              | Т3                              | NVCC_SD2            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD2_CMD       | V5                              | G1                              | V1                              | NVCC_SD2            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD2_D0        | T1                              | D1                              | R3                              | NVCC_SD2            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| SD2_D1        | T2                              | D2                              | U1                              | NVCC_SD2            | HVIO     | ALT1                                  | IN                          | Keeper                             |

i.MX50 Applications Processors for Consumer Products, Rev. 7

Table 86. i.MX50 Data Sheet Document Revision History (continued)

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 1         | 10/2011 | <ul> <li>Table 5, "Special Signal Considerations," on page 17 changed CHRG_DET_B to CHGR_DET_B.</li> <li>Table 5, "Special Signal Considerations," on page 17 in the CHGR_DET_B signal remarks, added "The maximum current leakage at this pin is 8.5 μA."</li> <li>Table 5, "Special Signal Considerations," on page 17 in the JTAG_MOD remarks, changed "pull-down" to "pull-up, by default" and added "If JTAG port is not needed, the internal pull-up can be disabled in order to reduce supply current to the pin."</li> <li>Table 14, "Maximum Supply Current Consumption—ARM CLK = 800 MHz," on page 27 in the 11<sup>th</sup> row under the Supply column, changed VDDO2P5 to VDDO25.</li> <li>Table 78, "VBUS Comparators Thresholds," on page 101 changed CHRG_DET_B to CHGR_DET_B.</li> <li>Table 5, "Special Signal Considerations," on page 17 for 416 MAPBGA, DRAM_SDCLK_0 pin number was changed to N24 and DRAM_SDCLK_0_B pin number was changed to M24.</li> <li>Table 5, "Special Signal Considerations," on page 17 for 416 MAPBGA, DRAM_SDCLK_1 pin number was changed to T20 and DRAM_SDCLK_1_B pin number was changed to R20.</li> <li>Table 5, "Special Signal Considerations," on page 17 for 416 MAPBGA, DRAM_SDQS0 pin number was changed to P23 and DRAM_SDQS0_B pin number was changed to P24.</li> <li>Table 5, "Special Signal Considerations," on page 17 changed pad type of pin DRAM_CALIBRATION to DRAMCALIB.</li> <li>Table 5, "Special Signal Considerations," on page 17 changed pad type of pins DRAM_SDCLK_0, DRAM_SDCLK_0_B, DRAM_SDCLK_1, DRAM_SDCLK_1_B, DRAM_SDQS0, DRAM_SDQS0_B, DRAM_SDQS1_B, DRAM_SDQS1_B, DRAM_SDQS1_B, DRAM_SDQS2_B, DRAM_SDQS3_B to DRAM_SDQS1_B, DRAM_SDQS3_B, DRAM_SDQS3_B to DRAMCLK.</li> </ul> |

| Rev. 0         | 07/2011 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |