Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Active                                                     |

| Core Processor                  | ARM® Cortex®-A8                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 800MHz                                                     |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                     |

| RAM Controllers                 | LPDDR, LPDDR2, DDR2                                        |

| Graphics Acceleration           | Yes                                                        |

| Display & Interface Controllers | EPDC, LCD                                                  |

| Ethernet                        | 10/100Mbps (1)                                             |

| SATA                            | -                                                          |

| USB                             | USB 2.0 + PHY (2)                                          |

| Voltage - I/O                   | 1.2V, 1.875V, 2.775V, 3.0V                                 |

| Operating Temperature           | 0°C ~ 70°C (TA)                                            |

| Security Features               | Boot Security, Cryptography, Secure JTAG                   |

| Package / Case                  | 400-LFBGA                                                  |

| Supplier Device Package         | 400-LFBGA (17x17)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcimx508cvm8b |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

NEON coprocessor (SIMD Media Processing Architecture) and Vector Floating Point (VFP-Lite) coprocessor supporting VFPv3

The memory system consists of the following components:

- Level 1 cache:

- Instruction (32 Kbyte)

- Data (32 Kbyte)

- Level 2 cache:

- Unified instruction and data (256 Kbyte)

- Level 2 (internal) memory:

- Boot ROM, including HAB (96 Kbyte)

- Internal multimedia/shared, fast access RAM (128 Kbyte)

- External memory interfaces:

- 16/32-bit DDR2-533, LPDDR2-533, or LPDDR1-400 up to a total of 2 GByte

- 8-bit NAND SLC/MLC Flash with up to 100 MHz synchronous clock rate and up to 32-bit hardware ECC for 1 Kbyte block size

- 16/32-bit NOR Flash with a dedicated 16-bit muxed-mode interface. I/O muxing logic selects EIMv2 port as primary muxing at system boot.

- 16-bit PSRAM, Cellular RAM

- Managed NAND, including eMMC up to rev 4.4

The i.MX50 introduces a next generation system bus fabric architecture that aggregates various sub-system buses and masters for access to system peripherals and memories. The various bus-systems and components are as follows:

- 64-bit AXI Fabric (266 MHz)—This bus-fabric is the SoC's central bus aggregation point.

- Provides access to all slave targets in the SoC:

- ROM (ROMCP)

- On-chip RAM (OCRAM)

- External DRAM (DRAM MC)

- External static RAM (EIM)

- Interrupt controller (TZIC)

- Decode into the AHB MAX crossbar second level AHB fabric.

- Provides arbitration to the following masters in the system:

- ARM CPU complex

- Pixel processing pipeline (ePXP)

- Electrophoretic display controller (EPDC)

- eLCDIF LCD display controller

- DCP Crypto engine

- BCH ECC engine

- MAX AHB crossbar

## **Modules List**

Table 4. i.MX50 Digital and Analog Modules (continued)

| Block<br>Mnemonic                              | Block Name                                             | Subsystem                             | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------|--------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSI-1<br>SSI-2                                 | I2S/SSI/AC97<br>Interface                              | Slave<br>Connectivity<br>Peripherals  | The SSI is a full-duplex synchronous interface used on the i.MX50 processor to provide connectivity with off-chip audio peripherals. The SSI interfaces connect internally to the AUDMUX for mapping to external ports. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock/frame sync options. Each SSI has two pairs of 8 x 24 FIFOs and hardware support for an external DMA controller in order to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream, which reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| Temperature Temp Sensor Analog Monitor         |                                                        | Analog                                | The temperature sensor is an internal module to the i.MX50 that monitors the die temperature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface,<br>ver. 2                              | Slave<br>Connectivity<br>Peripherals  | <ul> <li>Each of the UARTv2 modules supports the following serial data transmit/receive protocols and configurations:</li> <li>7 or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd, or none)</li> <li>Programmable bit-rates up to 4 Mbps. This is a higher max baud rate relative to the 1.875 Mbps, which is specified by the TIA/EIA-232-F standard.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> </ul>                                                                                                                                                                                      |

| USB-OH-1                                       | USB 2.0<br>High-Speed<br>OTG-capable<br>and Host ports | Master<br>Connectivity<br>Peripherals | USB-OH-1 supports USB2.0 HS/FS/LS, and contains:  One high-speed OTG-capable module with integrated HS USB PHY  One high-speed Host module with integrated HS USB PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WDOG-1                                         | Watch Dog                                              | Timer<br>Peripherals                  | The Watchdog (WDOG) timer module protects against system failures by providing a method of escaping from unexpected events or programming errors. The WDOG Timer supports two comparison points during each counting period. Each of the comparison points is configurable to invoke an interrupt to the ARM core, and a second point invokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                  |

| XTALOSC                                        | Crystal<br>Oscillator I/F                              | Clocking                              | The XTALOSC module combined with an external 24 MHz crystal with load capacitors implements a crystal oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# 3.1 Special Signal Considerations

Table 5 lists special signal considerations for the i.MX50. The signal names are listed in alphabetical order. The package contact assignments are found in Section 5, "Package Information and Contact Assignments." The signal descriptions are defined in the MCIMX50 Applications Processor Reference Manual (MCIMX50RM).

**Table 5. Special Signal Considerations**

| Signal Name                                                   | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT_MODE0,<br>BOOT_MODE1                                     | These two input pins are sampled out of reset and set the boot mode. For Internal boot, they should be set to 00. For Internal Fuse Only boot, they should be set to 10. For USB downloader, they should be set to 11. The BOOTMODE pins are in the NVCC_RESET domain and include an internal 100K pull-up resistor at start-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BOOT_CONFIG1[7:0],<br>BOOT_CONFIG2[7:0],<br>BOOT_CONFIG3[7:0] | These 24 pins are the GPIO boot override pins and may be driven at power up to select the boot mode. They are sampled 4 x CKIL clock cycles after POR is de-asserted. Consult the "System Boot" chapter of the Reference Manual for more details.  Note that these are not dedicated pins: the BOOT_CONFIG pins appear over 24 pins of the EIM interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BT_LPB_FREQ[1:0]                                              | If the LOW_BATT_GPIO (UART4_TXD) is asserted at power up, the BT_LPB_FREQ[1:0] pins will be sampled to determine the ARM core frequency. Consult the "System Boot" chapter of the Reference Manual for more details.  Note that these are not dedicated pins: BT_LPB_FREQ0 appears on SSI_TXFS and BT_LPB_FREQ1 appears on SSI_TXC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CHGR_DET_B                                                    | This is the USB Charger Detect pin. It is an open drain output pin that expects a 100 K pull-up. This pin is asserted low when a USB charger is detected on the OTG PHY DP and DM. This detection occurs with the application of VBUS. This pin is a raw sensor output and care must be taken to follow the system timings outlined in the USB charger specification Rev 1.1. The maximum current leakage at this pin is $8.5~\mu A$ . This pin can be controlled by software control as well. If not used, this pin should be tied to ground or left floating.                                                                                                                                                                                                                                                                                                                                                                                            |

| СКІН                                                          | This is an input to the CAMPs (Clock Amplifiers), which include on-chip AC-coupling precluding the need for external coupling capacitors. The CAMPs are enabled by default, but the main clocks feeding the on-chip clock tree are sourced from XTAL/EXTAL by default. Optionally, the use of a low jitter external oscillators to feed CKIH (while not required) can be an advantage if low jitter or special frequency clock sources are required by modules sourced by CKIH. See CCM chapter in the MCIMX50 Applications Processor Reference Manual (MCIMX50RM) for details on the respective clock trees.  After initialization, the CAMPs may be disabled if not used by programming the CCR CAMPx_EN field. If disabled, the on-chip CAMP output is low and the input is irrelevant. CKIH is on the NVCC_JTAG power domain, so the input clock amplitude should not exceed NVCC_JTAG.  If unused, the user should tie CKIH to GND for best practice. |

| CKIL/ECKIL                                                    | The user must tie a fundamental mode 32.768 K crystal across ECKIL and CKIL. The target ESR should be 50 K or less. The bias resistor for the amplifier is integrated and approximately 14 M $\Omega$ . The target load capacitance for the crystal is approximately 10 pF. The load capacitors on the board should be slightly less than double this value after taking parasitics into account. While driving in an external 32 KHz signal into ECKIL, CKIL should be left floating so that it biases. A differential amplifier senses these two pins to propagate the clock inside the i.MX508. Care must be taken to minimize external leakages on ECKIL and CKIL. If they are significant to the 14 M $\Omega$ feedback or 1 $\mu$ A, then loss of oscillation margin or cessation of oscillation may result.                                                                                                                                         |

#### **Electrical Characteristics**

**Table 5. Special Signal Considerations (continued)**

| Signal Name                  | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB_H1_VBUS,<br>USB_OTG_VBUS | These inputs are used by the i.MX50 to detect the presence and level of USB 5 V. If either VBUS input pin is connected to an external USB connector, there is a possibility that a fast 5 V edge rate during a cable attach could trigger the VBUS input ESD protection, which could result in damage to the i.MX50 silicon. To prevent this, the system should use some circuitry to prevent the 5 V edge rate from exceeding 5.25 V / 1 $\mu s$ . Freescale recommends the use of a low pass filter consisting of 100 $\Omega$ resistor in series and a 1 $\mu F$ capacitor close to the i.MX50 pin. In the case when the USB interface is connected on an on-board USB device (for example, 3G modem), the corresponding USB_VBUS pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                                     |

| VREF                         | This pin is the DRAM MC reference voltage input. For LPDDR2 and DDR2, this pin should be connected to $1\!\!\!/$ of NVCC_EMI_DRAM. For LPDDR1, this pin should be left floating. The user may generate VREF using a precision external resistor divider. Use a 1 k $\Omega$ 0.5% resistor to GND and a 1 k $\Omega$ 0.5% resistor to NVCC_EMI_DRAM. Shunt each resistor with a closely-mounted 0.1 $\mu\text{F}$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WDOG_B                       | This output can be used to reset the system PMIC when the i.MX50 processor is locked up. This output is in the NVCC_MISC domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WDOG_RST_B_DEB               | This output may be used to drive out the internal system reset signal to the system reset controller. This is only intended for debug purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| XTAL/EXTAL                   | <ul> <li>These pins are the 24 MHz crystal driver as well as the external 24 MHz clock input. If using these pins to directly drive a 24 MHz crystal:</li> <li>The user should tie a 24 MHz fundamental-mode crystal across XTAL and EXTAL.</li> <li>The crystal must be rated for a maximum drive level of 100 μW or higher.</li> <li>The recommended crystal ESR (equivalent series resistance) is 80 Ω or less. If using these pins as a clock input from an external 24 MHz oscillator:</li> <li>The crystal may be eliminated and EXTAL driven directly driven by the external oscillator. The clock signal level on EXTAL must swing from NVCC_SRTC to GND.</li> <li>In this configuration, the XTAL pin must be floated and the COSC_EN bit (bit 12 in the CCR register in the Clock Control Module) must be cleared to put the on-chip oscillator circuit in bypass mode which allows EXTAL to be externally driven.</li> <li>Note there are strict jitter requirements if using an external oscillator in a USB application: &lt; 50 ps peak-to-peak below 1.2 MHz and &lt; 100 ps peak-to-peak above 1.2 MHz for the USB PHY.</li> </ul> |

# 4 Electrical Characteristics

This section provides the device and module-level electrical characteristics of the i.MX50 processor.

## **NOTE**

These electrical specifications are preliminary. These specifications are not fully tested or guaranteed at this early stage of the product life cycle. Finalized specifications are published after thorough characterization and device qualifications have been completed.

#### **Electrical Characteristics**

**Table 7. Absolute Maximum Ratings (continued)**

| Parameter Description                               | Symbol               | Min | Max         | Unit |

|-----------------------------------------------------|----------------------|-----|-------------|------|

| ESD damage immunity:                                | V <sub>esd</sub>     |     |             | V    |

| Human Body Model (HBM)<br>Charge Device Model (CDM) |                      | _   | 2000<br>500 |      |

| Storage temperature range                           | T <sub>STORAGE</sub> | -40 | 125         | °C   |

<sup>1</sup> The term OVDD in this section refers to the associated supply rail of an input or output. The maximum range can be superseded by the DC tables.

## 4.1.2 Thermal Resistance Data

## 4.1.2.1 13 x 13 mm MAPBGA Package Thermal Resistance Data

Table 8 provides thermal resistance data for a 13 x 13 mm MAPBGA package.

Table 8. 13 x 13 mm MAPBGA Package Thermal Resistance Data

| Rating                                                      | Board                   | Symbol          | Value | Unit |

|-------------------------------------------------------------|-------------------------|-----------------|-------|------|

| Junction to Ambient (natural convection) <sup>1, 2</sup>    | Single layer board (1s) | $R_{\theta JA}$ | 51    | °C/W |

| Junction to Ambient (natural convection) <sup>1, 2, 3</sup> | Four layer board (2s2p) | $R_{\theta JA}$ | 28    | °C/W |

| Junction to Ambient (at 200 ft/min) <sup>1, 3</sup>         | Single layer board (1s) | $R_{	hetaJMA}$  | 40    | °C/W |

| Junction to Ambient (at 200 ft/min) <sup>1, 3</sup>         | Four layer board (2s2p) | $R_{	hetaJMA}$  | 24    | °C/W |

| Junction to Board <sup>4</sup>                              | _                       | $R_{\theta JB}$ | 14    | °C/W |

| Junction to Case <sup>5</sup>                               | _                       | $R_{\theta JC}$ | 9     | °C/W |

| Junction to Package Top (natural convection) <sup>6</sup>   | _                       | $\Psi_{JT}$     | 2     | °C/W |

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>&</sup>lt;sup>2</sup> Per JEDEC JESD51-2 with the single layer board horizontal. The thermal test board meets JESD51-9 specification.

<sup>&</sup>lt;sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>&</sup>lt;sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

<sup>&</sup>lt;sup>5</sup> Thermal resistance between the die and the case top surface as measured by using the cold plate method (MIL SPEC-883 Method 1012.1).

<sup>&</sup>lt;sup>6</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

## 4.3.5 Low Voltage I/O (LVIO) DC Parameters

The parameters in Table 22 are guaranteed per the operating ranges in Table 11, unless otherwise noted.

**Table 22. LVIO DC Electrical Characteristics**

| DC Electrical Characteristics            | Symbol | Test Conditions                                                      | MIN                          | Тур          | MAX              | Units |

|------------------------------------------|--------|----------------------------------------------------------------------|------------------------------|--------------|------------------|-------|

| High-level output voltage                | Voh    | Ioh=-1mA<br>Ioh=spec'ed Drive                                        | OVDD-0.15<br>0.8*OVDD        | _            | _                | V     |

| Low-level output voltage                 | Vol    | Iol=1mA<br>Iol=specified Drive                                       | _                            | _            | 0.15<br>0.2*OVDD | V     |

| High-level output current                | l      | Voh=0.8*OVDD<br>Low Drive<br>Medium Drive<br>High Drive<br>Max Drive | -2.1<br>-4.2<br>-6.3<br>-8.4 | _            | _                | mA    |

| Low-level output current                 | l      | Vol=0.2*OVDD<br>Low Drive<br>Medium Drive<br>High Drive<br>Max Drive | 2.1<br>4.2<br>6.3<br>8.4     | _            | _                | mA    |

| High-Level DC input voltage <sup>1</sup> | VIH    | _                                                                    | 0.7*OVDD                     | _            | OVDD             | V     |

| Low-Level DC input voltage               | VIL    | _                                                                    | 0V                           | _            | 0.3*OVDD         | V     |

| Input Hysteresis                         | VHYS   | OVDD=1.875<br>OVDD=2.775                                             | 0.35                         | 0.62<br>1.27 | _                | V     |

| Schmitt trigger VT+ <sup>2</sup>         | VT+    | _                                                                    | 0.5*OVDD                     | _            | _                | V     |

| Schmitt trigger VT-                      | VT-    | _                                                                    | _                            | _            | 0.5*OVDD         | V     |

| Pull-up resistor (22 KΩ PU)              | Rpu    | Vi=OVDD/2                                                            | 20                           | 24           | 28               | ΚΩ    |

| Pull-up resistor (47 KΩ PU)              | Rpu    | Vi=OVDD/2                                                            | 43                           | 51           | 59               | ΚΩ    |

| Pull-up resistor (100 KΩ PU)             | Rpu    | Vi=OVDD/2                                                            | 91                           | 108          | 125              | ΚΩ    |

| Pull-down resistor (100 KΩ PD)           | Rpd    | Vi=OVDD/2                                                            | 91                           | 108          | 126              | ΚΩ    |

| Input current (no pull-up/down)          | IIN    | VI = 0<br>VI=OVDD                                                    | _                            | 1.7          | 250<br>120       | nA    |

| Input current (22 KΩ PU)                 | IIN    | VI = 0<br>VI=OVDD                                                    | _                            | _            | 161<br>0.12      | μА    |

| Input current (47 KΩ PU)                 | IIN    | VI = 0<br>VI=OVDD                                                    | _                            | _            | 76<br>0.12       | μА    |

| Input current (100 KΩ PU)                | IIN    | VI = 0<br>VI=OVDD                                                    | _                            | _            | 36<br>0.12       | μА    |

i.MX50 Applications Processors for Consumer Products, Rev. 7

<sup>&</sup>lt;sup>1</sup> Vin(dc) specifies the allowable dc excursion of each differential input.

<sup>&</sup>lt;sup>2</sup> Vid(dc) specifies the input differential voltage IVtr-Vcpl required for switching, where Vtr is the "pure" input level and Vcp is the "complementary" input level. the minimum value is equal to Vih(dc) - Vil(dc).

<sup>&</sup>lt;sup>3</sup> Typ condition: typ model, 1.8 V, and 25 °C. Max condition: BCS model, 1.9 V, and 105 °C. Min condition: WCS model, 1.7 V, and -20 °C.

## 4.4.3 HVIO Output Buffer Impedance

Table 26 shows the HVIO output buffer impedance of the i.MX50 processor.

## **Table 26. HVIO Output Buffer Impedance**

|                         |                               |                                                                                                                              | М                     | in                    | Ту                    | /p                | M                      | ах                     |      |

|-------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-------------------|------------------------|------------------------|------|

| Parameter               | ameter Symbol Test Conditions |                                                                                                                              | OVDD<br>1.95 V        | OVDD<br>3.3 V         | OVDD<br>1.875 V       | OVDD<br>3.30V     | OVDD<br>1.65 V         | OVDD<br>2.68 V         | Unit |

| Output driver impedance | Rpu                           | Low drive strength, Ztl = 150 $\Omega$<br>Medium drive strength, Ztl = 75 $\Omega$<br>High drive strength, Ztl = 50 $\Omega$ | 113.5<br>56.2<br>37.8 | 103.8<br>51.9<br>35.1 | 130.6<br>66<br>45.9   | 133<br>69.2<br>41 | 219.4<br>109.7<br>73.1 | 212.2<br>111.1<br>71.8 | Ω    |

| Output driver impedance | Rpd                           | Low drive strength, Ztl =1 50 $\Omega$<br>Medium drive strength, Ztl = 75 $\Omega$<br>High drive strength, Ztl = 50 $\Omega$ | 78.5<br>39.7<br>26.8  | 70<br>34.5<br>23      | 113.6<br>56.8<br>38.3 | 102<br>50<br>33.3 | 230.8<br>115.4<br>76.9 | 179.5<br>89.8<br>60.7  | Ω    |

## **NOTE**

Output driver impedance is measured with *long* transmission line of impedance Ztl attached to I/O pad and incident wave launched into transmission line. Rpu/Rpd and Ztl form a voltage divider that defines specific voltage of incident wave relative to OVDD. Output driver impedance is calculated from this voltage divider (see Figure 3).

Table 31. HVIO I/O Low Voltage (1.8 V) AC Parameters (continued)

| Parameter                                      | Symbol | Test Condition | Min                    | Тур | Max | Unit  |

|------------------------------------------------|--------|----------------|------------------------|-----|-----|-------|

| Output Pad Slew Rate (High Drive) <sup>1</sup> | tr, tf | 15 pF<br>35 pF | 0.54/0.50<br>0.29/0.28 |     |     | V/ns  |

| Output Pad Slew Rate (Medium Drive)            | tr, tf | 15 pF<br>35 pF | 0.40/0.38<br>0.20/0.19 |     |     | V/ns  |

| Output Pad Slew Rate (Low Drive)               | tr, tf | 15 pF<br>35 pF | 0.22/0.21<br>0.10/0.10 |     |     | V/ns  |

| Output Pad di/dt (High Drive)                  | tdit   |                |                        |     | 34  | mA/ns |

| Output Pad di/dt (Medium drive)                | tdit   |                |                        |     | 22  | mA/ns |

| Output Pad di/dt (Low drive)                   | tdit   |                |                        |     | 11  | mA/ns |

| Input Transition Times <sup>2</sup>            | trm    |                |                        |     | 25  | ns    |

tps is measured between VIL to VIH for rising edge and between VIH to VIL for falling edge.

# 4.5.6 HVIO I/O High Voltage (3.0 V) AC Parameters

Table 32 shows the AC parameters for HVIO I/O High Voltage (3.0 V).

Table 32. HVIO I/O High Voltage (3.0 V) AC Parameters

| Parameter                                      | Symbol | Test Condition | Min                    | Тур | Max                    | Unit  |

|------------------------------------------------|--------|----------------|------------------------|-----|------------------------|-------|

| Output Pad Transition Times (High Drive)       | tpr    | 15 pF<br>35 pF |                        |     | 2.16/1.79<br>3.75/3.28 | ns    |

| Output Pad Transition Times (Medium Drive)     | tpr    | 15 pF<br>35 pF |                        |     | 2.81/2.40<br>5.06/4.58 | ns    |

| Output Pad Transition Times (Low Drive)        | tpr    | 15 pF<br>35 pF |                        |     | 4.69/4.15<br>8.91/8.51 | ns    |

| Output Pad Slew Rate (High Drive) <sup>1</sup> | tps    | 15 pF<br>35 pF | 0.75/0.90<br>0.43/0.49 |     |                        | V/ns  |

| Output Pad Slew Rate (Medium Drive)            | tps    | 15 pF<br>35 pF | 0.57/0.67<br>0.32/0.35 |     |                        | V/ns  |

| Output Pad Slew Rate (Low Drive)               | tps    | 15 pF<br>35 pF | 0.34/0.39<br>0.18/0.19 |     |                        | V/ns  |

| Output pad di/dt (High drive)                  | tdit   | _              | _                      | _   | 55                     | mA/ns |

| Output pad di/dt (Medium drive)                | tdit   | _              | _                      | _   | 36                     | mA/ns |

| Output pad di/dt (Low drive)                   | tdit   | _              | _                      | _   | 16                     | mA/ns |

| Input transition times <sup>2</sup>            | trm    | _              | _                      | _   | 25                     | ns    |

<sup>1</sup> tps is measured between VIL to VIH for rising edge and between VIH to VIL for falling edge.

i.MX50 Applications Processors for Consumer Products, Rev. 7

<sup>&</sup>lt;sup>2</sup> Hysteresis mode is recommended for inputs with transition time greater than 25 ns.

<sup>&</sup>lt;sup>2</sup> Hysteresis mode is recommended for inputs with transition time greater than 25 ns.

### Table 37. WDOG\_RST\_B Timing Parameters

| ID  | Parameter                        | Min | Max | Unit              |

|-----|----------------------------------|-----|-----|-------------------|

| CC5 | Duration of WDOG_RST_B Assertion | 1   | _   | T <sub>CKIL</sub> |

### **NOTE**

CKIL is approximately 32 kHz.  $T_{\text{CKIL}}$  is one period or approximately 30  $\mu s$ .

# 4.6.3 Clock Amplifier Parameters (CKIH)

The input to clock amplifier (CAMP) is internally ac-coupled allowing direct interface to a square wave or sinusoidal frequency source. No external series capacitors are required.

Table 38 shows the electrical parameters of CAMP.

Table 38. CAMP Electrical Parameters (CKIH)

| Parameter                   | Min                       | Тур | Max  | Unit |

|-----------------------------|---------------------------|-----|------|------|

| Input frequency             | 8.0                       | _   | 40.0 | MHz  |

| VIL (for square wave input) | 0                         | _   | 0.3  | V    |

| VIH (for square wave input) | (VCC <sup>1</sup> - 0.25) | _   | 3    | V    |

| Sinusoidal input amplitude  | 0.4 <sup>2</sup>          | _   | VDD  | Vp-p |

| Output duty cycle           | 45                        | 50  | 55   | %    |

<sup>1</sup> VCC is the supply voltage of CAMP.

## 4.6.4 DPLL Electrical Parameters

Table 39 shows the electrical parameters of digital phase-locked loop (DPLL).

**Table 39. DPLL Electrical Parameters**

| Parameter                                         | Test Conditions/Remarks         | Min       | Тур | Max      | Unit |

|---------------------------------------------------|---------------------------------|-----------|-----|----------|------|

| Reference clock frequency range <sup>1</sup>      | _                               | 10        | _   | 100      | MHz  |

| Reference clock frequency range after pre-divider | _                               | 10        | _   | 40       | MHz  |

| Output clock frequency range (dpdck_2)            | _                               | 300       | _   | 1025     | MHz  |

| Pre-division factor <sup>2</sup>                  | _                               | 1         | _   | 16       | _    |

| Multiplication factor integer part                | _                               | 5         | _   | 15       | _    |

| Multiplication factor numerator <sup>3</sup>      | Should be less than denominator | -67108862 | _   | 67108862 | _    |

| Multiplication factor denominator <sup>2</sup>    | _                               | 1         | _   | 67108863 | _    |

| Output duty cycle                                 | _                               | 48.5      | 50  | 51.5     | %    |

i.MX50 Applications Processors for Consumer Products, Rev. 7

<sup>&</sup>lt;sup>2</sup> This value of the sinusoidal input is determined during characterization.

Table 41. Source Synchronous Mode Timing Parameters<sup>1</sup> (continued)

| ID   | Parameter                                   | Symbol            | Tim<br>T = GPMI C          | Unit |    |

|------|---------------------------------------------|-------------------|----------------------------|------|----|

|      |                                             |                   | Min.                       | Max. |    |

| NF24 | postamble delay                             | t <sub>POST</sub> | POST_DELAY*t <sub>CK</sub> | _    | ns |

| NF25 | CLE and ALE setup time                      | t <sub>CALS</sub> | 0.5*t <sub>CK</sub>        | _    | ns |

| NF26 | CLE and ALE hold time                       | t <sub>CALH</sub> | 0.5*t <sub>CK</sub>        | _    | ns |

| NF27 | Data input to first DQS latching transition | t <sub>DQSS</sub> | t <sub>CK</sub>            | _    | ns |

GPMI's sync mode output timing could be controlled by module's internal register, say HW\_GPMI\_TIMING2\_CE\_DELAY, HW\_GPMI\_TIMING\_PREAMBLE\_DELAY, and HW\_GPMI\_TIMING2\_POST\_DELAY. This AC timing depends on these registers' setting. In the above table, we use CE\_DELAY/PRE\_DELAY/POST\_DELAY representing these settings each.

## 4.6.5.3 Samsung Toggle Mode AC Timing

## 4.6.5.3.1 Command and Address Timing

## **NOTE**

Samsung Toggle Mode command and address timing is the same as ONFI 1.0 compatible Async mode AC timing. Please refer to the above chapter for details.

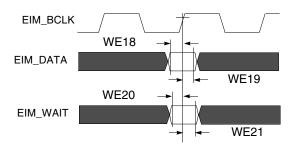

Figure 18. EIM Inputs Timing Diagram

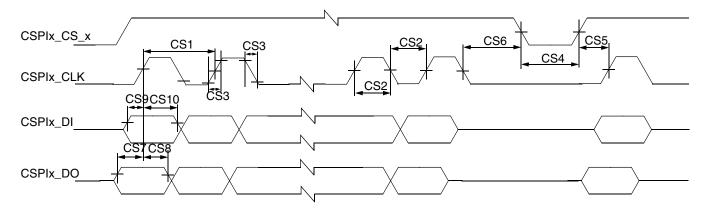

# 4.9.2.2 CSPI Slave Mode Timing

Figure 33 depicts the timing of CSPI in slave mode. Table 51 lists the CSPI slave mode timing characteristics.

Figure 33. CSPI Slave Mode Timing Diagram

**Table 51. CSPI Slave Mode Timing Parameters**

| ID   | Parameter                            | Symbol                 | Min | Max | Unit |

|------|--------------------------------------|------------------------|-----|-----|------|

| CS1  | CSPIx_CLK Cycle Time                 | t <sub>clk</sub>       | 60  | _   | ns   |

| CS2  | CSPIx_CLK High or Low Time           | t <sub>SW</sub>        | 15  | _   | ns   |

| CS3  | CSPIx_CLK Rise or Fall               | t <sub>RISE/FALL</sub> | _   | _   | ns   |

| CS4  | CSPIx_CS_x pulse width               | t <sub>CSLH</sub>      | 30  | _   | ns   |

| CS5  | CSPIx_CS_x Lead Time (CS setup time) | t <sub>SCS</sub>       | 5   | _   | ns   |

| CS6  | CSPIx_CS_x Lag Time (CS hold time)   | t <sub>HCS</sub>       | 5   | _   | ns   |

| CS7  | CSPIx_DO Setup Time                  | t <sub>Smosi</sub>     | 5   | _   | ns   |

| CS8  | CSPIx_DO Hold Time                   | t <sub>Hmosi</sub>     | 5   | _   | ns   |

| CS9  | CSPIx_DI Setup Time                  | t <sub>Smiso</sub>     | 5   | _   | ns   |

| CS10 | CSPIx_DI Hold Time                   | t <sub>Hmiso</sub>     | 5   | _   | ns   |

### **Electrical Characteristics**

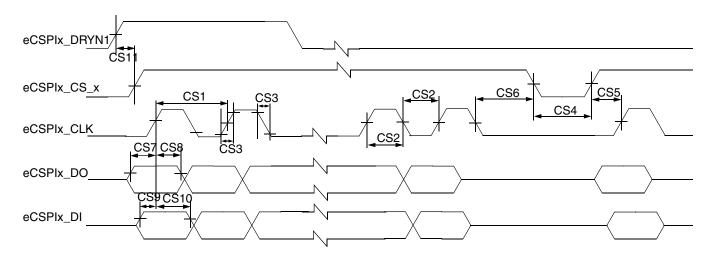

# 4.9.2.3 eCSPI Master Mode Timing

Figure 34 depicts the timing of eCSPI in master mode and Table 52 lists the eCSPI master mode timing characteristics.

Figure 34. eCSPI Master Mode Timing Diagram

**Table 52. eCSPI Master Mode Timing Parameters**

| ID   | Parameter                                                 | Symbol                 | Min      | Max | Unit |

|------|-----------------------------------------------------------|------------------------|----------|-----|------|

| CS1  | eCSPIx_CLK Cycle Time-Read<br>eCSPIx_CLK Cycle Time-Write | t <sub>clk</sub>       | 60<br>15 | _   | ns   |

| CS2  | eCSPIx_CLK High or Low Time                               | t <sub>SW</sub>        | 6        | _   | ns   |

| CS3  | eCSPIx_CLK Rise or Fall                                   | t <sub>RISE/FALL</sub> | _        | _   | ns   |

| CS4  | eCSPIx_CS_x pulse width                                   | t <sub>CSLH</sub>      | 15       | _   | ns   |

| CS5  | eCSPIx_CS_x Lead Time (CS setup time)                     | t <sub>SCS</sub>       | 5        | _   | ns   |

| CS6  | eCSPIx_CS_x Lag Time (CS hold time)                       | t <sub>HCS</sub>       | 5        | _   | ns   |

| CS7  | eCSPIx_DO Setup Time                                      | t <sub>Smosi</sub>     | 5        | _   | ns   |

| CS8  | eCSPIx_DO Hold Time                                       | t <sub>Hmosi</sub>     | 5        | _   | ns   |

| CS9  | eCSPIx_DI Setup Time                                      | t <sub>Smiso</sub>     | 5        | _   | ns   |

| CS10 | eCSPIx_DI Hold Time                                       | t <sub>Hmiso</sub>     | 5        | _   | ns   |

| CS11 | eCSPIx_DRYN Setup Time                                    | t <sub>SDRY</sub>      | 5        | _   | ns   |

#### **Electrical Characteristics**

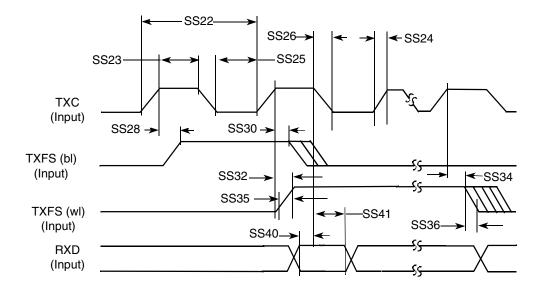

## 4.9.9.4 SSI Receiver Timing with External Clock

Figure 54 depicts the SSI receiver external clock timing and Table 69 lists the timing parameters for the receiver timing with external clock.

Figure 54. SSI Receiver External Clock Timing Diagram

Table 69. SSI Receiver Timing with External Clock

| ID   | Parameter                          | Min  | Max  | Unit |  |  |  |  |  |  |

|------|------------------------------------|------|------|------|--|--|--|--|--|--|

|      | External Clock Operation           |      |      |      |  |  |  |  |  |  |

| SS22 | (Tx/Rx) CK clock period            | 81.4 | _    | ns   |  |  |  |  |  |  |

| SS23 | (Tx/Rx) CK clock high period       | 36   | _    | ns   |  |  |  |  |  |  |

| SS24 | (Tx/Rx) CK clock rise time         | _    | 6.0  | ns   |  |  |  |  |  |  |

| SS25 | (Tx/Rx) CK clock low period        | 36   | _    | ns   |  |  |  |  |  |  |

| SS26 | (Tx/Rx) CK clock fall time         | _    | 6.0  | ns   |  |  |  |  |  |  |

| SS28 | (Rx) CK high to FS (bl) high       | -10  | 15.0 | ns   |  |  |  |  |  |  |

| SS30 | (Rx) CK high to FS (bl) low        | 10   | _    | ns   |  |  |  |  |  |  |

| SS32 | (Rx) CK high to FS (wl) high       | -10  | 15.0 | ns   |  |  |  |  |  |  |

| SS34 | (Rx) CK high to FS (wl) low        | 10   | _    | ns   |  |  |  |  |  |  |

| SS35 | (Tx/Rx) External FS rise time      | _    | 6.0  | ns   |  |  |  |  |  |  |

| SS36 | (Tx/Rx) External FS fall time      | _    | 6.0  | ns   |  |  |  |  |  |  |

| SS40 | SRXD setup time before (Rx) CK low | 10   | _    | ns   |  |  |  |  |  |  |

| SS41 | SRXD hold time after (Rx) CK low   | 2    | _    | ns   |  |  |  |  |  |  |

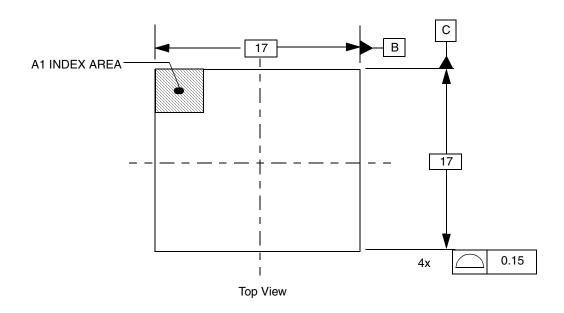

# 5.3.1 400 MAPBGA 17 x 17 mm Package Views

Figure 65 shows the top view of the 17 x 17 mm package, Figure 66 shows the bottom view of the package, and Figure 67 shows the side view of the package.

Figure 65. 400 MAPBGA 17x17 mm Package Top view

## 5.3.3 400 MAPBGA 17 x 17 Power Rails

Table 84. 400 MAPBGA 17x17 Ground, Power, Sense, and Reference Contact Signals

| Pin Name       | Ball Number                                                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC             | A1 Y1 A20 Y20                                                                                                                                                              |

| NVCC_EIM       | F6 F7 F8                                                                                                                                                                   |

| NVCC_EMI_DRAM  | K14 N14 J15 K15 L15 N15 P15 H16 J16 K16 L16 M16 N16 P16 R16                                                                                                                |

| NVCC_EPDC      | F9 F10 F11 F12                                                                                                                                                             |

| NVCC_JTAG      | P9                                                                                                                                                                         |

| NVCC_KEYPAD    | H5                                                                                                                                                                         |

| NVCC_LCD       | P10                                                                                                                                                                        |

| NVCC_MISC      | J5                                                                                                                                                                         |

| NVCC_NANDF     | P11 P12                                                                                                                                                                    |

| NVCC_RESET     | P6                                                                                                                                                                         |

| NVCC_SD1       | N5                                                                                                                                                                         |

| NVCC_SD2       | P5                                                                                                                                                                         |

| NVCC_SPI       | M5                                                                                                                                                                         |

| NVCC_SRTC      | R5                                                                                                                                                                         |

| NVCC_SSI       | K5                                                                                                                                                                         |

| NVCC_UART      | L5                                                                                                                                                                         |

| USB_H1_VDDA25  | Y9                                                                                                                                                                         |

| USB_H1_VDDA33  | W11                                                                                                                                                                        |

| USB_OTG_VDDA25 | W9                                                                                                                                                                         |

| USB_OTG_VDDA33 | Y11                                                                                                                                                                        |

| VCC            | K10 L10 M10 K11 L11 M11 J12 K12 L12                                                                                                                                        |

| VDD1P2         | U6                                                                                                                                                                         |

| VDD1P8         | V6                                                                                                                                                                         |

| VDD2P5         | V5                                                                                                                                                                         |

| VDD3P0         | U5                                                                                                                                                                         |

| VDDA           | K9 J11                                                                                                                                                                     |

| VDDAL1         | J9 J10                                                                                                                                                                     |

| VDDGP          | G6 H6 J6 K6 L6 G7 H7 J7 K7 G8 H8 G9 H9 G10 H10                                                                                                                             |

| VDDO25         | L17                                                                                                                                                                        |

| VSS            | T5 W5 M6 N6 L7 M7 N7 P7 J8 K8 L8 M8 N8 P8 L9 M9 N9 N10 R10 G11 H11 N11 R11 G12 H12 M12 N12 R12 G13 H13 J13 K13 L13 M13 N13 P13 R13 G14 H14 J14 L14 M14 P14 R14 H15 M15 R15 |

i.MX50 Applications Processors for Consumer Products, Rev. 7

Table 84. 400 MAPBGA 17x17 Ground, Power, Sense, and Reference Contact Signals (continued)

| VDD_DCDCI | R7 |

|-----------|----|

| VDD_DCDCO | Т6 |

| GND_DCDC  | R6 |

# 5.4 Signal Assignments

**Table 85. Alphabetical List of Signal Assignments**

| Pin Name   | 416<br>MAPBGA<br>Ball<br>Number | 416<br>PoPBGA<br>Ball<br>Number | 400<br>MAPBGA<br>Ball<br>Number | Pin Power<br>Domain             | Pad Type | IOMUX<br>MUX<br>CTL<br>After<br>Reset | Direction<br>After<br>Reset | IOMUX<br>PAD CTL<br>After<br>Reset |

|------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|----------|---------------------------------------|-----------------------------|------------------------------------|

| BOOT_MODE0 | AB1                             | AB1                             | V3                              | NVCC_RESET                      | LVIO     | ALT0                                  | IN                          | 100K PU                            |

| BOOT_MODE1 | AB2                             | AB2                             | U3                              | NVCC_RESET                      | LVIO     | ALT0                                  | IN                          | 100K PU                            |

| CHGR_DET_B | V11                             | AA15                            | T10                             | USB_H1_VDDA25,<br>USB_H1_VDDA33 | ANALOG25 | _                                     | OUT-OD                      | _                                  |

| CKIH       | AA6                             | AA6                             | V4                              | NVCC_JTAG                       | ANALOG   | _                                     | _                           | _                                  |

| CKIL       | Y1                              | Y1                              | Y4                              | NVCC_SRTC                       | ANALOG   |                                       | _                           | _                                  |

| CSPI_MISO  | M5                              | H2                              | K4                              | NVCC_SPI                        | HVIO     | ALT1                                  | IN                          | Keeper                             |

| CSPI_MOSI  | M2                              | J1                              | L3                              | NVCC_SPI                        | HVIO     | ALT1                                  | IN                          | Keeper                             |

| CSPI_SCLK  | M1                              | H1                              | M1                              | NVCC_SPI                        | HVIO     | ALT1                                  | IN                          | Keeper                             |

| CSPI_SS0   | M4                              | J2                              | J4                              | NVCC_SPI                        | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_BUSY  | AC12                            | AA21                            | U11                             | NVCC_LCD                        | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_CS    | AD14                            | AC21                            | T12                             | NVCC_LCD                        | HVIO     | ALT3                                  | OUT-LO                      | 100K PU                            |

| DISP_D0    | AA12                            | AC17                            | V11                             | NVCC_LCD                        | HVIO     | ALT3                                  | OUT-LO                      | 100K PU                            |

| DISP_D1    | Y12                             | AC16                            | T11                             | NVCC_LCD                        | HVIO     | ALT3                                  | OUT-LO                      | 100K PU                            |

| DISP_D10   | Y17                             | AD22                            | Y16                             | NVCC_NANDF                      | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_D11   | V12                             | AD19                            | W14                             | NVCC_NANDF                      | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_D12   | V13                             | AC22                            | V14                             | NVCC_NANDF                      | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_D13   | V14                             | AC23                            | T13                             | NVCC_NANDF                      | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_D14   | V15                             | AB23                            | U14                             | NVCC_NANDF                      | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_D15   | V16                             | AD21                            | Y15                             | NVCC_NANDF                      | HVIO     | ALT1                                  | IN                          | Keeper                             |

| DISP_D2    | AA13                            | AD15                            | W12                             | NVCC_LCD                        | HVIO     | ALT3                                  | OUT-LO                      | 100K PU                            |

| DISP_D3    | Y13                             | AC15                            | W13                             | NVCC_LCD                        | HVIO     | ALT3                                  | OUT-LO                      | 100K PU                            |

| DISP_D4    | AA14                            | AC24                            | Y13                             | NVCC_LCD                        | HVIO     | ALT3                                  | OUT-LO                      | 100K PU                            |

| DISP_D5    | Y14                             | AB24                            | U13                             | NVCC_LCD                        | HVIO     | ALT3                                  | OUT-LO                      | 100K PU                            |

Table 85. Alphabetical List of Signal Assignments (continued)

| Pin Name           | 416<br>MAPBGA<br>Ball<br>Number | 416<br>PoPBGA<br>Ball<br>Number | 400<br>MAPBGA<br>Ball<br>Number | Pin Power<br>Domain | Pad Type | IOMUX<br>MUX<br>CTL<br>After<br>Reset | Direction<br>After<br>Reset | IOMUX<br>PAD CTL<br>After<br>Reset |

|--------------------|---------------------------------|---------------------------------|---------------------------------|---------------------|----------|---------------------------------------|-----------------------------|------------------------------------|

| DRAM_DQM0          | T24                             | M18                             | N17                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | IN                          | Keeper                             |

| DRAM_DQM1          | J24                             | L18                             | F17                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | IN                          | Keeper                             |

| DRAM_DQM2          | AC24                            | Y16                             | U20                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | IN                          | Keeper                             |

| DRAM_DQM3          | B24                             | G17                             | D20                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | IN                          | Keeper                             |

| DRAM_OPEN          | J18                             | _                               | H18                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_OPENFB        | H18                             | _                               | H17                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | IN                          | Keeper                             |

| DRAM_RAS           | H21                             | _                               | E20                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-HI                      | Keeper                             |

| DRAM_SDBA0         | K18                             | _                               | J20                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDBA1         | L18                             | _                               | H20                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDBA2         | N18                             | _                               | M19                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDCKE         | U20                             | T5                              | R18                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDCLK_0       | N24                             | R5                              | J17                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDCLK_0_<br>B | M24                             | P5                              | J18                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | OUT-HI                      | _                                  |

| DRAM_SDCLK_1       | T20                             | _                               | _                               | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDCLK_1_<br>B | R20                             | _                               | _                               | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | OUT-HI                      | _                                  |

| DRAM_SDODT0        | G18                             | _                               | K18                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDODT1        | R18                             | _                               | _                               | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-LO                      | Keeper                             |

| DRAM_SDQS0         | P23                             | N18                             | M17                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDQS0_B       | P24                             | P18                             | M18                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDQS1         | L23                             | J20                             | G17                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDQS1_B       | L24                             | K18                             | G18                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDQS2         | AB23                            | Y15                             | T19                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDQS2_B       | AB24                            | V15                             | T20                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDQS3         | C23                             | E16                             | C19                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDQS3_B       | C24                             | G16                             | C20                             | NVCC_EMI_DRAM       | DRAMCLK  | ALT0                                  | IN                          | _                                  |

| DRAM_SDWE          | P18                             | _                               | L18                             | NVCC_EMI_DRAM       | DRAM     | ALT0                                  | OUT-HI                      | Keeper                             |

| ECKIL              | Y2                              | Y2                              | W4                              | NVCC_SRTC           | ANALOG   | _                                     | _                           | _                                  |

| ECSPI1_MISO        | N7                              | K4                              | М3                              | NVCC_SPI            | HVIO     | ALT1                                  | IN                          | Keeper                             |

| ECSPI1_MOSI        | N2                              | N4                              | M4                              | NVCC_SPI            | HVIO     | ALT1                                  | IN                          | Keeper                             |

i.MX50 Applications Processors for Consumer Products, Rev. 7

Table 85. Alphabetical List of Signal Assignments (continued)

| Pin Name       | 416<br>MAPBGA<br>Ball<br>Number | 416<br>PoPBGA<br>Ball<br>Number | 400<br>MAPBGA<br>Ball<br>Number | Pin Power<br>Domain | Pad Type | IOMUX<br>MUX<br>CTL<br>After<br>Reset | Direction<br>After<br>Reset | IOMUX<br>PAD CTL<br>After<br>Reset |

|----------------|---------------------------------|---------------------------------|---------------------------------|---------------------|----------|---------------------------------------|-----------------------------|------------------------------------|

| EPDC_PWRCTRL 2 | G14                             | F23                             | E12                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_PWRCTRL 3 | G15                             | L21                             | F15                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_PWRSTAT   | G16                             | F24                             | C12                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCE0     | D13                             | N24                             | B12                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCE1     | E13                             | P24                             | A12                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCE2     | D12                             | H21                             | C11                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCE3     | E12                             | J21                             | E8                              | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCE4     | D11                             | K21                             | D10                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCE5     | E11                             | D18                             | E6                              | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCLK     | A13                             | K24                             | B13                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDCLKN    | B13                             | L24                             | D12                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDLE      | D18                             | M24                             | C15                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDOE      | E18                             | V21                             | C13                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDOED     | D19                             | R23                             | G16                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDOEZ     | E19                             | U21                             | F16                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_SDSHR     | A10                             | H23                             | A8                              | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |

| EPDC_VCOM0     | G17                             | H24                             | B14                             | NVCC_EPDC           | HVIO     | ALT1                                  | IN                          | Keeper                             |