Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

# Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application energies microcontrollars are angineered to

# Details

| Detalls                 |                                                                             |

|-------------------------|-----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                    |

| Applications            | USB Microcontroller                                                         |

| Core Processor          | 8051                                                                        |

| Program Memory Type     | ROMIess                                                                     |

| Controller Series       | CY7C647xx                                                                   |

| RAM Size                | 16K x 8                                                                     |

| Interface               | I <sup>2</sup> C, USB, USART                                                |

| Number of I/O           | 24                                                                          |

| Voltage - Supply        | 3.15V ~ 3.45V                                                               |

| Operating Temperature   | 0°C ~ 70°C                                                                  |

| Mounting Type           | Surface Mount                                                               |

| Package / Case          | 56-BSSOP (0.295", 7.50mm Width)                                             |

| Supplier Device Package | 56-SSOP                                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cy7c64713-56pvxc |

|                         |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

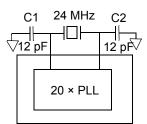

# Figure 1. Crystal Configuration

12-pF capacitor values assumes a trace capacitance of 3 pF per side on a four layer FR4 PCA

# Table 1. Special Function Registers

| x | 8x    | 9x        | Ax           | Bx             | Сх     | Dx    | Ex  | Fx  |

|---|-------|-----------|--------------|----------------|--------|-------|-----|-----|

| 0 | IOA   | IOB       | IOC          | IOD            | SCON1  | PSW   | ACC | В   |

| 1 | SP    | EXIF      | INT2CLR      | IOE            | SBUF1  |       |     |     |

| 2 | DPL0  | MPAGE     | INT4CLR      | OEA            |        |       |     |     |

| 3 | DPH0  |           |              | OEB            |        |       |     |     |

| 4 | DPL1  |           |              | OEC            |        |       |     |     |

| 5 | DPH1  |           |              | OED            |        |       |     |     |

| 6 | DPS   |           |              | OEE            |        |       |     |     |

| 7 | PCON  |           |              |                |        |       |     |     |

| 8 | TCON  | SCON0     | IE           | IP             | T2CON  | EICON | EIE | EIP |

| 9 | TMOD  | SBUF0     |              |                |        |       |     |     |

| A | TL0   | AUTOPTRH1 | EP2468STAT   | EP01STAT       | RCAP2L |       |     |     |

| В | TL1   | AUTOPTRL1 | EP24FIFOFLGS | GPIFTRIG       | RCAP2H |       |     |     |

| С | TH0   | reserved  | EP68FIFOFLGS |                | TL2    |       |     |     |

| D | TH1   | AUTOPTRH2 |              | GPIFSGLDATH    | TH2    |       |     |     |

| E | CKCON | AUTOPTRL2 |              | GPIFSGLDATLX   |        |       |     |     |

| F |       | reserved  | AUTOPTRSETUP | GPIFSGLDATLNOX |        |       |     |     |

# I<sup>2</sup>C Bus

FX1 supports the  $l^2$ C bus as a master only at 100/400 KHz. SCL and SDA pins have open drain outputs and hysteresis inputs. These signals must be pulled up to 3.3 V, even if no  $l^2$ C device is connected.

### **Buses**

All packages: 8 or 16-bit 'FIFO' bidirectional data bus, multiplexed on I/O ports B and D. 128-pin package: adds 16-bit output only 8051 address bus, 8-bit bidirectional data bus.

## **USB Boot Methods**

During the power up sequence, internal logic checks the  $I^2C$  port for the connection of an EEPROM whose first byte is either 0xC0 or 0xC2. If found, it uses the VID/PID/DID values in the EEPROM in place of the internally stored values (0xC0). Alternatively, it boot-loads the EEPROM contents into an internal RAM (0xC2). If no EEPROM is detected, FX1 enumerates using internally stored descriptors. The default ID values for FX1 are VID/PID/DID (0x04B4, 0x6473, 0xAxxx where xxx=Chip revision).<sup>[2]</sup>

### Table 2. Default ID Values for FX1

| Default VID/PID/DID |        |                                                                             |  |  |  |  |  |  |

|---------------------|--------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| Vendor ID           | 0x04B4 | Cypress Semiconductor                                                       |  |  |  |  |  |  |

| Product ID          | 0x6473 | EZ-USB FX1                                                                  |  |  |  |  |  |  |

| Device<br>release   | 0xAnnn | Depends on chip revision (nnn = chip<br>revision where first silicon = 001) |  |  |  |  |  |  |

Notes

2. The I<sup>2</sup>C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.

### Table 3. INT2 USB Interrupts (continued)

|          |               | USB INTE  | RRUPT TABLE FOR INT2                     |

|----------|---------------|-----------|------------------------------------------|

| Priority | INT2VEC Value | Source    | Notes                                    |

| 18       | 44            |           | Reserved                                 |

| 19       | 48            | EP0PING   | EP0 OUT was Pinged and it NAK'd          |

| 20       | 4C            | EP1PING   | EP1 OUT was Pinged and it NAK'd          |

| 21       | 50            | EP2PING   | EP2 OUT was Pinged and it NAK'd          |

| 22       | 54            | EP4PING   | EP4 OUT was Pinged and it NAK'd          |

| 23       | 58            | EP6PING   | EP6 OUT was Pinged and it NAK'd          |

| 24       | 5C            | EP8PING   | EP8 OUT was Pinged and it NAK'd          |

| 25       | 60            | ERRLIMIT  | Bus errors exceeded the programmed limit |

| 26       | 64            |           |                                          |

| 27       | 68            |           | Reserved                                 |

| 28       | 6C            |           | Reserved                                 |

| 29       | 70            | EP2ISOERR | ISO EP2 OUT PID sequence error           |

| 30       | 74            | EP4ISOERR | ISO EP4 OUT PID sequence error           |

| 31       | 78            | EP6ISOERR | ISO EP6 OUT PID sequence error           |

| 32       | 7C            | EP8ISOERR | ISO EP8 OUT PID sequence error           |

# Table 4. Individual FIFO/GPIF Interrupt Sources

| Priority | INT4VEC Value | Source   | Notes                                |

|----------|---------------|----------|--------------------------------------|

| 1        | 80            | EP2PF    | Endpoint 2 Programmable Flag         |

| 2        | 84            | EP4PF    | Endpoint 4 Programmable Flag         |

| 3        | 88            | EP6PF    | Endpoint 6 Programmable Flag         |

| 4        | 8C            | EP8PF    | Endpoint 8 Programmable Flag         |

| 5        | 90            | EP2EF    | Endpoint 2 Empty Flag <sup>[3]</sup> |

| 6        | 94            | EP4EF    | Endpoint 4 Empty Flag                |

| 7        | 98            | EP6EF    | Endpoint 6 Empty Flag                |

| 8        | 9C            | EP8EF    | Endpoint 8 Empty Flag                |

| 9        | A0            | EP2FF    | Endpoint 2 Full Flag                 |

| 10       | A4            | EP4FF    | Endpoint 4 Full Flag                 |

| 11       | A8            | EP6FF    | Endpoint 6 Full Flag                 |

| 12       | AC            | EP8FF    | Endpoint 8 Full Flag                 |

| 13       | B0            | GPIFDONE | GPIF Operation Complete              |

| 14       | B4            | GPIFWF   | GPIF Waveform                        |

If Autovectoring is enabled (AV4EN = 1 in the INTSETUP register), the FX1 substitutes its INT4VEC byte. Therefore, if the high byte ("page") of a jump-table address is preloaded at location 0x0054, the automatically inserted INT4VEC byte at 0x0055 directs the jump to the correct address out of the 14 addresses within the page. When the ISR occurs, the FX1

pushes the program counter onto its stack and then jumps to address 0x0053, where it expects to find a "jump" instruction to the ISR Interrupt service routine.

#### Note

Errata: In Slave FIFO Asynchronous Word Wide mode, if a single word data is transferred from the USB host to EP2, configured as OUT Endpoint (EP) in the first transaction, then the Empty flag behaves incorrectly. This does not happen if the data size is more than one word in the first transaction. For more information, see the "Errata" on page 71.

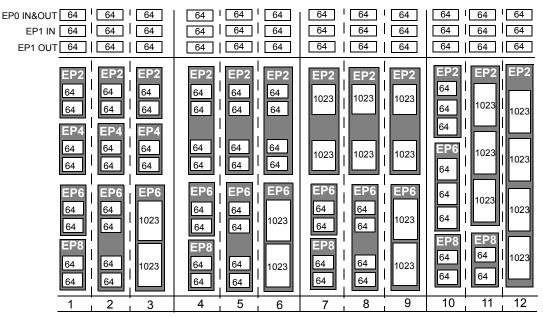

# Figure 6. Endpoint Configuration

### Master/Slave Control Signals

The FX1 endpoint FIFOS are implemented as eight physically distinct 256 × 16 RAM blocks. The 8051/SIE can switch any of the RAM blocks between two domains: the USB (SIE) domain and the 8051-I/O Unit domain. This switching is done instantaneously, giving essentially zero transfer time between "USB FIFOS" and "Slave FIFOS". While they are physically the same memory, no bytes are actually transferred between buffers.

At any time, some RAM blocks fill or empty with USB data under SIE control, while other RAM blocks are available to the 8051 and the I/O control unit. The RAM blocks operate as a single-port in the USB domain, and dual port in the 8051-I/O domain. The blocks are configured as single, double, triple, or quad buffered.

The I/O control unit implements either an internal master (M for master) or external master (S for Slave) interface.

In Master (M) mode, the GPIF internally controls FIFOADR[1..0] to select a FIFO. The RDY pins (two in the 56-pin package, six in the 100-pin and 128-pin packages) are used as flag inputs from an external FIFO or other logic if desired. The GPIF is run from either an internally derived clock or an externally supplied clock (IFCLK), at a rate that transfers data up to 96 Megabytes/s (48 MHz IFCLK with 16-bit interface).

In Slave (S) mode, the FX1 accepts either an internally derived clock or an externally supplied clock (IFCLK with a maximum frequency of 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit, and a Slave FIFO Output Enable signal SLOE enables data of the selected width. External logic must ensure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly

as strobes, rather than a clock qualifier as in the synchronous mode. The signals SLRD, SLWR, SLOE, and PKTEND are gated by the signal SLCS#.

### GPIF and FIFO Clock Rates

An 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz. Alternatively, an externally supplied clock of 5 to 48 MHz feeding the IFCLK pin is used as the interface clock. IFCLK is configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off, if desired. Another bit within the IFCONFIG register inverts the IFCLK signal whether internally or externally sourced.

# GPIF

The GPIF is a flexible 8 or 16-bit parallel interface driven by a user programmable finite state machine. It allows the CY7C64713 to perform local bus mastering, and can implement a wide variety of protocols such as ATA interface, printer parallel port, and Utopia.

The GPIF has six programmable control outputs (CTL), nine address outputs (GPIFADRx), and six general purpose Ready inputs (RDY). The data bus width is 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and determines what state a Ready input (or multiple inputs) must be before proceeding. The GPIF vector is programmed to advance a FIFO to the next data value, advance an address, and so on. A sequence of the GPIF vectors create a single waveform that executes to perform the data move between the FX1 and the external device.

### Six Control OUT Signals

The 100-pin and 128-pin packages bring out all six Control Output pins (CTL0–CTL5). The 8051 programs the GPIF unit to define the CTL waveforms. The 56-pin package brings out three

of these signals: CTL0–CTL2. CTLx waveform edges are programmed to make transitions as fast as once per clock (20.8 ns using a 48 MHz clock).

### Six Ready IN Signals

The 100-pin and 128-pin packages bring out all six Ready inputs (RDY0–RDY5). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching. The 56 pin package brings out two of these signals, RDY0–1.

### Nine GPIF Address OUT Signals

Nine GPIF address lines are available in the 100-pin and 128-pin packages: GPIFADR[8..0]. The GPIF address lines allow indexing through up to a 512 byte block of RAM. If more address lines are needed, I/O port pins are used.

### Long Transfer Mode

In Master mode, the 8051 appropriately sets the GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to 2<sup>32</sup> transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions are complete. The GPIF decrements the value in these registers to represent the current status of the transaction.

### **ECC Generation**

The EZ-USB FX1 can calculate ECCs (Error Correcting Codes) on data that pass across its GPIF or Slave FIFO interfaces. There are two ECC configurations: Two ECCs, each calculated over 256 bytes (SmartMedia<sup>™</sup> Standard); and one ECC calculated over 512 bytes.

The ECC can correct any one-bit error or detect any two-bit error.

**Note** To use the ECC logic, the GPIF or Slave FIFO interface must be configured for byte-wide operation.

### ECC Implementation

The two ECC configurations are selected by the ECCM bit:

### $0.0.0.1 \quad ECCM = 0$

Two 3-byte ECCs, each calculated over a 256-byte block of data. This configuration conforms to the SmartMedia Standard.

Write any value to ECCRESET, then pass data across the GPIF or Slave FIFO interface. The ECC for the first 256 bytes of data is calculated and stored in ECC1. The ECC for the next 256 bytes is stored in ECC2. After the second ECC is calculated, the values in the ECCx registers do not change until the ECCRESET is written again, even if more data is subsequently passed across the interface.

# 0.0.0.2 ECCM = 1

One 3-byte ECC calculated over a 512-byte block of data.

Write any value to ECCRESET, then pass data across the GPIF or Slave FIFO interface. The ECC for the first 512 bytes of data is calculated and stored in ECC1; ECC2 is not used. After the ECC is calculated, the value in ECC1 does not change until the ECCRESET is written again, even if more data is subsequently passed across the interface

## **USB Uploads and Downloads**

The core has the ability to directly edit the data contents of the internal 16 KByte RAM and of the internal 512 byte scratch pad RAM via a vendor specific command. This capability is normally used when 'soft' downloading user code and is available only to and from the internal RAM, only when the 8051 is held in reset. The available RAM spaces are 16 KBytes from 0x0000–0x3FFF (code/data) and 512 bytes from 0xE000–0xE1FF (scratch pad data RAM).<sup>[5]</sup>

### **Autopointer Access**

FX1 provides two identical autopointers. They are similar to the internal 8051 data pointers, but with an additional feature: they can optionally increment after every memory access. This capability is available to and from both internal and external RAM. The autopointers are available in external FX1 registers, under the control of a mode bit (AUTOPTRSETUP.0). Using the external FX1 autopointer access (at 0xE67B–0xE67C) allows the autopointer to access all RAM, internal and external, to the part. Also, the autopointers can point to any FX1 register or endpoint buffer space. When autopointer access to external memory is enabled, the location 0xE67B and 0xE67C in XDATA and the code space cannot be used.

# I<sup>2</sup>C Controller

FX1 has one I<sup>2</sup>C port that is driven by two internal controllers: one that automatically operates at boot time to load VID/PID/DID and configuration information; and another that the 8051, once running, uses to control external I<sup>2</sup>C devices. The I<sup>2</sup>C port operates in master mode only.

### I<sup>2</sup>C Port Pins

The I<sup>2</sup>C pins SCL and SDA must have external 2.2 k $\Omega$  pull up resistors even if no EEPROM is connected to the FX1. External EEPROM device address pins must be configured properly. See Table 7 for configuring the device address pins.

| Bytes | Example EEPROM        | A2  | A1  | A0  |

|-------|-----------------------|-----|-----|-----|

| 16    | 24LC00 <sup>[6]</sup> | N/A | N/A | N/A |

| 128   | 24LC01                | 0   | 0   | 0   |

| 256   | 24LC02                | 0   | 0   | 0   |

| 4K    | 24LC32                | 0   | 0   | 1   |

| 8K    | 24LC64                | 0   | 0   | 1   |

| 16K   | 24LC128               | 0   | 0   | 1   |

#### Notes

5. After the data is downloaded from the host, a 'loader' executes from the internal RAM to transfer downloaded data to the external memory.

6. This EEPROM has no address pins.

61

63

64

61

62

63

62

52

55

58

53

54

55

58

54

55

56

56

44

48

50

51

44

44

50

51

57

54

55

58

58

59

50

51

52

52

52

52

53

54

56

56

57

58

59

50

51

55

51

52

52

52

52

52

54

56

56

50

51

56

51

52

52

52

53

54

54

54

56

54

56

56

57

57

58

58

59

59

59

50

56

50

56

56

57

\* indicates programmable polarity

CY7C64713

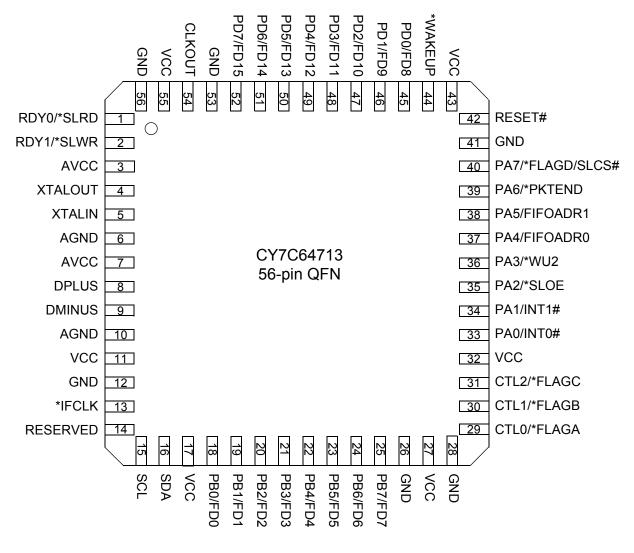

Figure 11. CY7C64713 56-pin QFN Pin Assignment

\* indicates programmable polarity

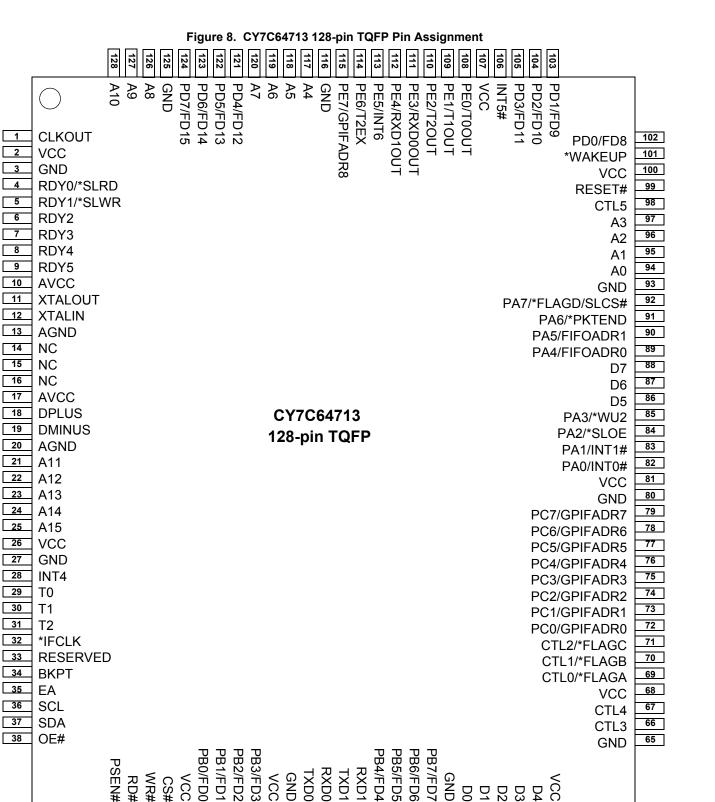

# CY7C64713 Pin Definitions

The FX1 Pin Definitions for CY7C64713 follow.<sup>[7]</sup> Table 8. FX1 Pin Definitions

| 128-pin<br>TQFP | 100-pin<br>TQFP | 56-pin<br>SSOP | 56-pin<br>QFN | Name   | Туре   | Default | Description                                                                                                                                                                                                                               |

|-----------------|-----------------|----------------|---------------|--------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10              | 9               | 10             | 3             | AVCC   | Power  | N/A     | <b>Analog VCC</b> . Connect this pin to 3.3 V power source. This signal provides power to the analog section of the chip.                                                                                                                 |

| 17              | 16              | 14             | 7             | AVCC   | Power  | N/A     | <b>Analog VCC</b> . Connect this pin to 3.3 V power source. This signal provides power to the analog section of the chip.                                                                                                                 |

| 13              | 12              | 13             | 6             | AGND   | Ground | N/A     | Analog Ground. Connect to ground with as short a path as possible.                                                                                                                                                                        |

| 20              | 19              | 17             | 10            | AGND   | Ground | N/A     | Analog Ground. Connect to ground with as short a path as possible.                                                                                                                                                                        |

| 19              | 18              | 16             | 9             | DMINUS | I/O/Z  | Z       | USB D- Signal. Connect to the USB D- signal.                                                                                                                                                                                              |

| 18              | 17              | 15             | 8             | DPLUS  | I/O/Z  | Z       | USB D+ Signal. Connect to the USB D+ signal.                                                                                                                                                                                              |

| 94              |                 |                |               | A0     | Output | L       | 8051 Address Bus. This bus is driven at all times. When the                                                                                                                                                                               |

| 95              |                 |                |               | A1     | Output | L       | 8051 is addressing the internal RAM it reflects the internal address.                                                                                                                                                                     |

| 96              |                 |                |               | A2     | Output | L       |                                                                                                                                                                                                                                           |

| 97              |                 |                |               | A3     | Output | L       |                                                                                                                                                                                                                                           |

| 117             |                 |                |               | A4     | Output | L       |                                                                                                                                                                                                                                           |

| 118             |                 |                |               | A5     | Output | L       |                                                                                                                                                                                                                                           |

| 119             |                 |                |               | A6     | Output | L       |                                                                                                                                                                                                                                           |

| 120             |                 |                |               | A7     | Output | L       |                                                                                                                                                                                                                                           |

| 126             |                 |                |               | A8     | Output | L       |                                                                                                                                                                                                                                           |

| 127             |                 |                |               | A9     | Output | L       |                                                                                                                                                                                                                                           |

| 128             |                 |                |               | A10    | Output | L       |                                                                                                                                                                                                                                           |

| 21              |                 |                |               | A11    | Output | L       |                                                                                                                                                                                                                                           |

| 22              |                 |                |               | A12    | Output | L       |                                                                                                                                                                                                                                           |

| 23              |                 |                |               | A13    | Output | L       |                                                                                                                                                                                                                                           |

| 24              |                 |                |               | A14    | Output | L       |                                                                                                                                                                                                                                           |

| 25              |                 |                |               | A15    | Output | L       |                                                                                                                                                                                                                                           |

| 59              |                 |                |               | D0     | I/O/Z  | Z       | 8051 Data Bus. This bidirectional bus is high impedance when                                                                                                                                                                              |

| 60              |                 |                |               | D1     | I/O/Z  | Z       | inactive, input for bus reads, and output for bus writes. The data bus is used for external 8051 program and data memory. The                                                                                                             |

| 61              |                 |                |               | D2     | I/O/Z  | Z       | data bus is active only for external bus accesses, and is driven                                                                                                                                                                          |

| 62              |                 |                |               | D3     | I/O/Z  | Z       | LOW in suspend.                                                                                                                                                                                                                           |

| 63              |                 |                |               | D4     | I/O/Z  | Z       |                                                                                                                                                                                                                                           |

| 86              |                 |                |               | D5     | I/O/Z  | Z       |                                                                                                                                                                                                                                           |

| 87              |                 |                |               | D6     | I/O/Z  | Z       |                                                                                                                                                                                                                                           |

| 88              |                 |                |               | D7     | I/O/Z  | Z       |                                                                                                                                                                                                                                           |

| 39              |                 |                |               | PSEN#  | Output | Н       | <b>Program Store Enable</b> . This active LOW signal indicates an 8051 code fetch from external memory. It is active for program memory fetches from 0x4000–0xFFFF when the EA pin is LOW, or from 0x0000–0xFFFF when the EA pin is HIGH. |

Note

7. Do not leave unused inputs floating. Tie either HIGH or LOW as appropriate. Pull outputs up or down to ensure signals at power up and in standby. Note that no pins must be driven when the device is powered down.

Table 8. FX1 Pin Definitions (continued)

| 128-pin<br>TQFP | 100-pin<br>TQFP | 56-pin<br>SSOP | 56-pin<br>QFN | Name               | Туре  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|-----------------|----------------|---------------|--------------------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 124             | 98              | 3              | 52            | PD7 or<br>FD[15]   | I/O/Z | I (PD7) | Multiplexed pin whose function is selected by the IFCONFIG[10] and EPxFIFOCFG.0 (wordwide) bits. <b>FD[15]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                   |

| Port E          |                 |                |               |                    |       |         |                                                                                                                                                                                                                                                                                                                                                                                                           |

| 108             | 86              |                |               | PE0 or<br>T0OUT    | I/O/Z | I (PE0) | Multiplexed pin whose function is selected by the PORTECFG.0<br>bit.<br><b>PE0</b> is a bidirectional I/O port pin.<br><b>TOOUT</b> is an active HIGH signal from 8051 Timer-counter0.<br>T0OUT outputs a high level for one CLKOUT clock cycle when<br>Timer0 overflows. If Timer0 is operated in Mode 3 (two separate<br>timer/counters), T0OUT is active when the low byte<br>timer/counter overflows. |

| 109             | 87              |                |               | PE1 or<br>T1OUT    | I/O/Z | I (PE1) | Multiplexed pin whose function is selected by the PORTECFG.1<br>bit.<br><b>PE1</b> is a bidirectional I/O port pin.<br><b>T1OUT</b> is an active HIGH signal from 8051 Timer-counter1.<br>T1OUT outputs a high level for one CLKOUT clock cycle when<br>Timer1 overflows. If Timer1 is operated in Mode 3 (two separate<br>timer/counters), T1OUT is active when the low byte<br>timer/counter overflows. |

| 110             | 88              |                |               | PE2 or<br>T2OUT    | I/O/Z | I (PE2) | Multiplexed pin whose function is selected by the PORTECFG.2<br>bit.<br><b>PE2</b> is a bidirectional I/O port pin.<br><b>T2OUT</b> is the active HIGH output signal from 8051 Timer2.<br>T2OUT is active (HIGH) for one clock cycle when<br>Timer/Counter 2 overflows.                                                                                                                                   |

| 111             | 89              |                |               | PE3 or<br>RXD0OUT  | I/O/Z | I (PE3) | Multiplexed pin whose function is selected by the PORTECFG.3<br>bit.<br><b>PE3</b> is a bidirectional I/O port pin.<br><b>RXD0OUT</b> is an active HIGH signal from 8051 UART0. If<br>RXD0OUT is selected and UART0 is in Mode 0, this pin<br>provides the output data for UART0 only when it is in sync<br>mode. Otherwise it is a 1.                                                                    |

| 112             | 90              |                |               | PE4 or<br>RXD1OUT  | I/O/Z | I (PE4) | Multiplexed pin whose function is selected by the PORTECFG.4<br>bit.<br><b>PE4</b> is a bidirectional I/O port pin.<br><b>RXD10UT</b> is an active HIGH output from 8051 UART1. When<br>the RXD10UT is selected and UART1 is in Mode 0, this pin<br>provides the output data for UART1 only when it is in sync<br>mode. In Modes 1, 2, and 3, this pin is HIGH.                                           |

| 113             | 91              |                |               | PE5 or<br>INT6     | I/O/Z | I (PE5) | Multiplexed pin whose function is selected by the PORTECFG.5<br>bit.<br><b>PE5</b> is a bidirectional I/O port pin.<br><b>INT6</b> is the 8051 INT6 interrupt request input signal. The INT6<br>pin is edge-sensitive, active HIGH.                                                                                                                                                                       |

| 114             | 92              |                |               | PE6 or<br>T2EX     | I/O/Z | I (PE6) | Multiplexed pin whose function is selected by the PORTECFG.6<br>bit.<br><b>PE6</b> is a bidirectional I/O port pin.<br><b>T2EX</b> is an active HIGH input signal to the 8051 Timer2. T2EX<br>reloads timer 2 on its falling edge. T2EX is active only if the<br>EXEN2 bit is set in T2CON.                                                                                                               |

| 115             | 93              |                |               | PE7 or<br>GPIFADR8 | I/O/Z | I (PE7) | Multiplexed pin whose function is selected by the PORTECFG.7<br>bit.<br><b>PE7</b> is a bidirectional I/O port pin.<br><b>GPIFADR8</b> is a GPIF address output pin.                                                                                                                                                                                                                                      |

Table 8. FX1 Pin Definitions (continued)

| 128-pin<br>TQFP | 100-pin<br>TQFP | 56-pin<br>SSOP | 56-pin<br>QFN | Name     | Туре   | Default | Description                                                                                                                                                                                                                                                                               |

|-----------------|-----------------|----------------|---------------|----------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31              | 25              |                |               | Т2       | Input  | N/A     | <b>T2</b> is the active-HIGH T2 input signal to 8051 Timer2, which provides the input to Timer2 when $C/T2 = 1$ . When $C/T2 = 0$ , Timer2 does not use this pin.                                                                                                                         |

| 30              | 24              |                |               | T1       | Input  | N/A     | <b>T1</b> is the active-HIGH T1 signal for 8051 Timer1, which provides the input to Timer1 when C/T1 is 1. When C/T1 is 0, Timer1 does not use this bit.                                                                                                                                  |

| 29              | 23              |                |               | то       | Input  | N/A     | <b>T0</b> is the active-HIGH T0 signal for 8051 Timer0, which provides the input to Timer0 when C/T0 is 1. When C/T0 is 0, Timer0 does not use this bit.                                                                                                                                  |

| 53              | 43              |                |               | RXD1     | Input  | N/A     | <b>RXD1</b> is an active-HIGH input signal for 8051 UART1, which provides data to the UART in all modes.                                                                                                                                                                                  |

| 52              | 42              |                |               | TXD1     | Output | Н       | <b>TXD1</b> is an active-HIGH output pin from 8051 UART1, which provides the output clock in sync mode, and the output data in async mode.                                                                                                                                                |

| 51              | 41              |                |               | RXD0     | Input  | N/A     | <b>RXD0</b> is the active-HIGH RXD0 input to 8051 UART0, which provides data to the UART in all modes.                                                                                                                                                                                    |

| 50              | 40              |                |               | TXD0     | Output | Н       | <b>TXD0</b> is the active-HIGH TXD0 output from 8051 UART0, which provides the output clock in sync mode, and the output data in async mode.                                                                                                                                              |

| 42              |                 |                |               | CS#      | Output | Н       | CS# is the active-LOW chip select for external memory.                                                                                                                                                                                                                                    |

| 41              | 32              |                |               | WR#      | Output | Н       | WR# is the active-LOW write strobe output for external memory.                                                                                                                                                                                                                            |

| 40              | 31              |                |               | RD#      | Output | Н       | <b>RD#</b> is the active-LOW read strobe output for external memory.                                                                                                                                                                                                                      |

| 38              |                 |                |               | OE#      | Output | Н       | OE# is the active LOW output enable for external memory.                                                                                                                                                                                                                                  |

| 33              | 27              | 21             | 14            | Reserved | Input  | N/A     | Reserved. Connect to ground.                                                                                                                                                                                                                                                              |

|                 | •               |                |               |          |        |         |                                                                                                                                                                                                                                                                                           |

| 101             | 79              | 51             | 44            | WAKEUP   | Input  | N/A     | <b>USB Wakeup</b> . If the 8051 is in suspend, asserting this pin starts<br>up the oscillator and interrupts the 8051 to allow it to exit the<br>suspend mode. Holding WAKEUP asserted inhibits the<br>EZ-USB FX1 chip from suspending. This pin has<br>programmable polarity (WAKEUP.4). |

| 36              | 29              | 22             | 15            | SCL      | OD     | Z       | <b>Clock for the I<sup>2</sup>C interface</b> . Connect to VCC with a 2.2K resistor, even if no I <sup>2</sup> C peripheral is attached.                                                                                                                                                  |

| 37              | 30              | 23             | 16            | SDA      | OD     | Z       | <b>Data for I<sup>2</sup>C interface</b> . Connect to VCC with a 2.2K resistor, even if no I <sup>2</sup> C peripheral is attached.                                                                                                                                                       |

|                 |                 | -              |               |          |        |         |                                                                                                                                                                                                                                                                                           |

| 2               | 1               | 6              | 55            | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 26              | 20              | 18             | 11            | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 43              | 33              | 24             | 17            | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 48              | 38              |                |               | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 64              | 49              | 34             | 27            | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 68              | 53              |                |               | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 81              | 66              | 39             | 32            | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 100             | 78              | 50             | 43            | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

| 107             | 85              |                |               | VCC      | Power  | N/A     | VCC. Connect to 3.3 V power source.                                                                                                                                                                                                                                                       |

|                 |                 |                |               |          |        |         |                                                                                                                                                                                                                                                                                           |

| 3               | 2               | 7              | 56            | GND      | Ground | N/A     | Ground.                                                                                                                                                                                                                                                                                   |

| 27              | 21              | 19             | 12            | GND      | Ground | N/A     | Ground.                                                                                                                                                                                                                                                                                   |

|                 |                 |                |               |          |        |         |                                                                                                                                                                                                                                                                                           |

| Hex  | Size | Name                   | Description                     | b7       | b6     | b5     | b4     | b3     | b2     | b1    | b0    | Default  | Access |

|------|------|------------------------|---------------------------------|----------|--------|--------|--------|--------|--------|-------|-------|----------|--------|

| E685 | 1    | USBFRAMEL              | USB Frame<br>count L            | FC7      | FC6    | FC5    | FC4    | FC3    | FC2    | FC1   | FC0   | XXXXXXXX | R      |

| E686 | 1    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

| E687 | 1    | FNADDR                 | USB Function<br>address         | 0        | FA6    | FA5    | FA4    | FA3    | FA2    | FA1   | FA0   | 0xxxxxxx | R      |

| E688 | 2    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

|      |      | ENDPOINTS              |                                 |          |        |        |        |        |        |       |       |          |        |

| E68A | 1    | EP0BCH <sup>[18]</sup> | Endpoint 0<br>Byte Count H      | (BC15)   | (BC14) | (BC13) | (BC12) | (BC11) | (BC10) | (BC9) | (BC8) | XXXXXXXX | RW     |

| E68B | 1    | EP0BCL <sup>[18]</sup> | Endpoint 0<br>Byte Count L      | (BC7)    | BC6    | BC5    | BC4    | BC3    | BC2    | BC1   | BC0   | XXXXXXXX | RW     |

| E68C | 1    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

| E68D | 1    | EP1OUTBC               | Endpoint 1<br>OUT Byte<br>Count | 0        | BC6    | BC5    | BC4    | BC3    | BC2    | BC1   | BC0   | xxxxxxxx | RW     |

| E68E | 1    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

| E68F | 1    | EP1INBC                | Endpoint 1 IN<br>Byte Count     | 0        | BC6    | BC5    | BC4    | BC3    | BC2    | BC1   | BC0   | XXXXXXXX | RW     |

| E690 | 1    | EP2BCH <sup>[18]</sup> | Endpoint 2<br>Byte Count H      | 0        | 0      | 0      | 0      | 0      | BC10   | BC9   | BC8   | XXXXXXXX | RW     |

| E691 | 1    | EP2BCL <sup>[18]</sup> | Endpoint 2<br>Byte Count L      | BC7/SKIP | BC6    | BC5    | BC4    | BC3    | BC2    | BC1   | BC0   | XXXXXXXX | RW     |

| E692 | 2    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

| E694 | 1    | EP4BCH <sup>[18]</sup> | Endpoint 4<br>Byte Count H      | 0        | 0      | 0      | 0      | 0      | 0      | BC9   | BC8   | XXXXXXXX | RW     |

| E695 | 1    | EP4BCL <sup>[18]</sup> | Endpoint 4<br>Byte Count L      | BC7/SKIP | BC6    | BC5    | BC4    | BC3    | BC2    | BC1   | BC0   | XXXXXXXX | RW     |

| E696 | 2    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

| E698 | 1    | EP6BCH <sup>[18]</sup> | Endpoint 6<br>Byte Count H      | 0        | 0      | 0      | 0      | 0      | BC10   | BC9   | BC8   | XXXXXXXX | RW     |

| E699 | 1    | EP6BCL <sup>[18]</sup> | Endpoint 6<br>Byte Count L      | BC7/SKIP | BC6    | BC5    | BC4    | BC3    | BC2    | BC1   | BC0   | XXXXXXXX | RW     |

| E69A | 2    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

| E69C | 1    | EP8BCH <sup>[18]</sup> | Endpoint 8<br>Byte Count H      | 0        | 0      | 0      | 0      | 0      | 0      | BC9   | BC8   | XXXXXXXX | RW     |

| E69D | 1    | EP8BCL <sup>[18]</sup> | Endpoint 8<br>Byte Count L      | BC7/SKIP | BC6    | BC5    | BC4    | BC3    | BC2    | BC1   | BC0   | XXXXXXXX | RW     |

| E69E | 2    | reserved               |                                 |          |        |        |        |        |        |       |       |          |        |

#### Note

18. Read and writes to these register may require synchronization delay, see the section "Synchronization Delay" in the EZ-USB TRM.

| Hex  | Size | Name         | Description                                       | b7        | b6        | b5        | b4        | b3      | b2      | b1      | b0      | Default  | Access |

|------|------|--------------|---------------------------------------------------|-----------|-----------|-----------|-----------|---------|---------|---------|---------|----------|--------|

| E6AE | 1    | EP4FIFOBCL   | Endpoint 4<br>slave FIFO<br>total byte<br>count L | BC7       | BC6       | BC5       | BC4       | BC3     | BC2     | BC1     | BC0     | 0000000  | R      |

| E6AF |      | EP6FIFOBCH   | Endpoint 6<br>slave FIFO<br>total byte<br>count H | 0         | 0         | 0         | 0         | BC11    | BC10    | BC9     | BC8     | 0000000  |        |

| E6B0 | 1    | EP6FIFOBCL   | Endpoint 6<br>slave FIFO<br>total byte<br>count L | BC7       | BC6       | BC5       | BC4       | BC3     | BC2     | BC1     | BC0     | 0000000  | R      |

| E6B1 |      | EP8FIFOBCH   | Endpoint 8<br>slave FIFO<br>total byte<br>count H | 0         | 0         | 0         | 0         | 0       | BC10    | BC9     | BC8     | 0000000  | R      |

| E6B2 | 1    | EP8FIFOBCL   | Endpoint 8<br>slave FIFO<br>total byte<br>count L | BC7       | BC6       | BC5       | BC4       | BC3     | BC2     | BC1     | BC0     | 0000000  | R      |

| E6B3 |      | SUDPTRH      | Setup Data<br>Pointer high<br>address byte        | A15       | A14       | A13       | A12       | A11     | A10     | A9      | A8      | XXXXXXXX | RW     |

| E6B4 | 1    | SUDPTRL      | Setup Data<br>Pointer low<br>address byte         | A7        | A6        | A5        | A4        | A3      | A2      | A1      | 0       | xxxxxxx0 |        |

| E6B5 | 1    | SUDPTRCTL    | Setup Data<br>Pointer Auto<br>Mode                | 0         | 0         | 0         | 0         | 0       | 0       | 0       | SDPAUTO | 00000001 | RW     |

|      | 2    | reserved     |                                                   |           |           |           |           |         |         |         |         |          |        |

| E6B8 | 8    | SETUPDAT     | 8 bytes of<br>setup data                          | D7        | D6        | D5        | D4        | D3      | D2      | D1      | D0      | XXXXXXXX | R      |

|      |      |              | SETUPDAT[0]                                       |           |           |           |           |         |         |         |         |          |        |

|      |      |              | =<br>bmRequestTy<br>pe                            |           |           |           |           |         |         |         |         |          |        |

|      |      |              | SETUPDAT[1]<br>= bmRequest                        |           |           |           |           |         |         |         |         |          |        |

|      |      |              | SETUPDAT[2:<br>3] = wValue                        |           |           |           |           |         |         |         |         |          |        |

|      |      |              | SETUPDAT[4:<br>5] = wIndex                        |           |           |           |           |         |         |         |         |          |        |

|      |      |              | SETUPDAT[6:<br>7] = wLength                       |           |           |           |           |         |         |         |         |          |        |

|      |      | GPIF         |                                                   |           |           |           |           |         |         |         |         |          |        |

| E6C0 | 1    | GPIFWFSELECT | Waveform<br>Selector                              | SINGLEWR1 | SINGLEWR0 | SINGLERD1 | SINGLERD0 | FIFOWR1 | FIFOWR0 | FIFORD1 | FIFORD0 | 11100100 | RW     |

| Hex  | Size | Name                     | Description                                              | b7     | b6       | b5          | b4          | b3      | b2     | b1      | b0      | Default  | Access   |

|------|------|--------------------------|----------------------------------------------------------|--------|----------|-------------|-------------|---------|--------|---------|---------|----------|----------|

| E6C1 |      | GPIFIDLECS               | GPIF Done,<br>GPIF IDLE<br>drive mode                    | DONE   | 0        | 0           | 0           | 0       | 0      | 0       | IDLEDRV | 1000000  | RW       |

| E6C2 | 1    | GPIFIDLECTL              | Inactive Bus,<br>CTL states                              | 0      | 0        | CTL5        | CTL4        | CTL3    | CTL2   | CTL1    | CTL0    | 11111111 | RW       |

| E6C3 |      | GPIFCTLCFG               | CTL Drive<br>Type                                        | TRICTL | 0        | CTL5        | CTL4        | CTL3    | CTL2   | CTL1    | CTL0    | 00000000 | RW       |

| E6C4 |      | GPIFADRH <sup>[19]</sup> | GPIF Address<br>H                                        | 0      | 0        | 0           | 0           | 0       | 0      | 0       | GPIFA8  | 00000000 | RW       |

| E6C5 | 1    | GPIFADRL <sup>[19]</sup> | GPIF Address<br>L                                        | GPIFA7 | GPIFA6   | GPIFA5      | GPIFA4      | GPIFA3  | GPIFA2 | GPIFA1  | GPIFA0  | 00000000 | RW       |

|      |      | FLOWSTATE                |                                                          |        |          |             |             |         |        |         |         |          |          |

| E6C6 | 1    | FLOWSTATE                | Flowstate<br>Enable and<br>Selector                      | FSE    | 0        | 0           | 0           | 0       | FS2    | FS1     | FS0     | 0000000  | brrrrbbb |

| E6C7 | 1    | FLOWLOGIC                | Flowstate<br>Logic                                       | LFUNC1 | LFUNC0   | TERMA2      | TERMA1      | TERMA0  | TERMB2 | TERMB1  | TERMB0  | 00000000 | RW       |

| E6C8 |      | FLOWEQ0CTL               | CTL-Pin<br>States in<br>Flowstate<br>(when<br>Logic = 0) | CTL0E3 | CTL0E2   |             | CTL0E0/CTL4 | CTL3    | CTL2   | CTL1    | CTLO    | 00000000 | RW       |

| E6C9 | 1    | FLOWEQ1CTL               | CTL-Pin<br>States in<br>Flowstate<br>(when<br>Logic = 1) | CTL0E3 | CTL0E2   | CTL0E1/CTL5 | CTL0E0/CTL4 |         | CTL2   | CTL1    | CTLO    | 00000000 | RW       |

| E6CA |      | FLOWHOLDOFF              | Holdoff<br>Configuration                                 |        |          |             | HOPERIOD0   | HOSTATE | HOCTL2 | HOCTL1  | HOCTL0  | 00000000 | RW       |

| E6CB |      | FLOWSTB                  | Flowstate<br>Strobe<br>Configuration                     | SLAVE  | RDYASYNC | CTLTOGL     | SUSTAIN     | 0       | MSTB2  | MSTB1   | MSTB0   | 00100000 | RW       |

| E6CC |      | FLOWSTBEDGE              | Flowstate<br>Rising/Falling<br>Edge<br>Configuration     | 0      | 0        | 0           | 0           | 0       | 0      | FALLING | RISING  | 00000001 |          |

| E6CD |      | FLOWSTBPERIOD            | Master-Strobe<br>Half-Period                             | D7     | D6       | D5          | D4          | D3      | D2     | D1      | D0      | 00000010 | RW       |

| E6CE |      | GPIFTCB3 <sup>[19]</sup> | GPIF<br>Transaction<br>Count Byte 3                      | TC31   | TC30     | TC29        | TC28        | TC27    | TC26   | TC25    | TC24    | 0000000  | RW       |

| E6CF | 1    | GPIFTCB2 <sup>[19]</sup> | GPIF<br>Transaction<br>Count Byte 2                      | TC23   | TC22     | TC21        | TC20        | TC19    | TC18   | TC17    | TC16    | 0000000  | RW       |

Note

19. Read and writes to these register may require synchronization delay, see the section "Synchronization Delay" in the EZ-USB TRM.

| Hex | Size | Name                           | Description                                           | b7    | b6    | b5    | b4    | b3    | b2    | b1   | b0    | Default  | Access |

|-----|------|--------------------------------|-------------------------------------------------------|-------|-------|-------|-------|-------|-------|------|-------|----------|--------|

| BC  | 1    | reserved                       |                                                       |       |       |       |       |       |       |      |       |          |        |

| BD  | 1    | GPIFSGLDATH <sup>[27]</sup>    | GPIF Data H<br>(16-bit mode<br>only)                  | D15   | D14   | D13   | D12   | D11   | D10   | D9   | D8    | xxxxxxxx | RW     |

| BE  | 1    | GPIFSGLDATLX <sup>[27]</sup>   | GPIF Data L<br>w/ Trigger                             | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0    | XXXXXXXX | RW     |

| BF  |      | GPIFSGLDATLNOX <sup>[27]</sup> | GPIF Data L<br>w/ No Trigger                          | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0    | XXXXXXXX | R      |

| C0  | 1    | SCON1 <sup>[27]</sup>          | Serial Port 1<br>Control (bit<br>addressable)         | SM0_1 | SM1_1 | SM2_1 | REN_1 | TB8_1 | RB8_1 | TI_1 | RI_1  | 0000000  | RW     |

| C1  | 1    | SBUF1 <sup>[27]</sup>          | Serial Port 1<br>Data Buffer                          | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0    | 00000000 | RW     |

| C2  | 6    | reserved                       |                                                       |       |       |       |       |       |       |      | 1     |          |        |

| C8  | 1    | T2CON                          | Timer/Counter<br>2 Control (bit<br>addressable)       | TF2   | EXF2  | RCLK  | TCLK  | EXEN2 | TR2   | CT2  | CPRL2 | 00000000 | RW     |

| C9  | 1    | reserved                       |                                                       |       |       |       |       |       |       |      |       |          |        |

| CA  | 1    | RCAP2L                         | Capture for<br>Timer 2,<br>auto-reload,<br>up-counter | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0    | 00000000 | RW     |

| СВ  |      | RCAP2H                         | Capture for<br>Timer 2,<br>auto-reload,<br>up-counter | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0    | 00000000 | RW     |

| CC  | 1    | TL2                            | Timer 2 reload<br>L                                   | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0    | 0000000  | RW     |

| CD  | 1    | TH2                            | Timer 2 reload<br>H                                   | D15   | D14   | D13   | D12   | D11   | D10   | D9   | D8    | 00000000 | RW     |

| CE  | 2    | reserved                       |                                                       |       |       |       |       |       |       |      |       |          |        |

| D0  | 1    | PSW                            | Program<br>Status Word<br>(bit<br>addressable)        | CY    | AC    | F0    | RS1   | RS0   | OV    | F1   | Р     | 00000000 | RW     |

| D1  | 7    | reserved                       |                                                       |       |       |       |       |       |       |      |       |          |        |

| D8  | 1    | EICON <sup>[27]</sup>          | External<br>Interrupt<br>Control                      | SMOD1 | 1     | ERESI | RESI  | INT6  | 0     | 0    | 0     | 0100000  | RW     |

| D9  | 7    | reserved                       |                                                       |       |       |       |       |       |       |      |       |          |        |

| E0  | 1    | ACC                            | Accumulator<br>(bit<br>addressable)                   | D7    | D6    | D5    | D4    | D3    | D2    | D1   | D0    | 00000000 | RW     |

### Note

27. SFRs not part of the standard 8051 architecture.

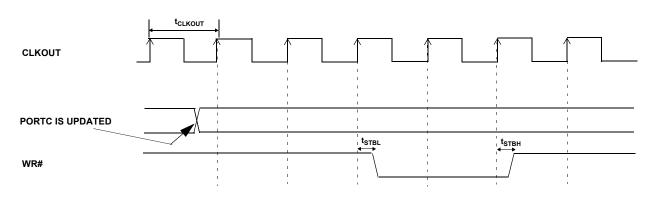

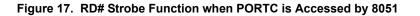

# **PORTC Strobe Feature Timings**

The RD# and WR# are present in the 100 pin version and the 128 pin package. In these 100 pin and 128 pin versions, an 8051 control bit is set to pulse the RD# and WR# pins when the 8051 reads from or writes to the PORTC. This feature is enabled by setting the PORTCSTB bit in CPUCS register.

The RD# and WR# strobes are asserted for two CLKOUT cycles when the PORTC is accessed.

The WR# strobe is asserted two clock cycles after the PORTC is updated and is active for two clock cycles after that as shown in Figure 16.

As for read, the value of the PORTC three clock cycles before the assertion of RD# is the value that the 8051 reads in. The RD# is pulsed for 2 clock cycles after 3 clock cycles from the point when the 8051 has performed a read function on PORTC. In this feature the RD# signal prompts the external logic to prepare the next data byte. Nothing gets sampled internally on assertion of the RD# signal itself. It is just a "prefetch" type signal to get the next data byte prepared. Therefore, using it meets the set up time to the next read.

The purpose of this pulsing of RD# is to let the external peripheral know that the 8051 is done reading PORTC and that the data was latched into the PORTC three CLKOUT cycles prior to asserting the RD# signal. After the RD# is pulsed the external logic may update the data on PORTC.

The timing diagram of the read and write strobing function on accessing PORTC follows. Refer to Figure 13 on page 49 and Figure 14 on page 50 for details on propagation delay of RD# and WR# signals.

### Figure 16. WR# Strobe Function when PORTC is Accessed by 8051

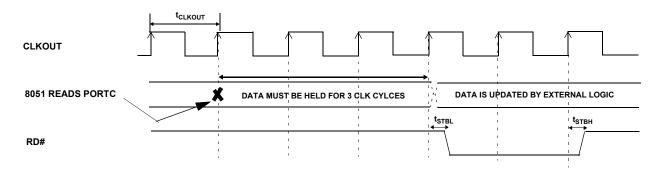

# Slave FIFO Synchronous Read

In the following figure, dashed lines indicate signals with programmable polarity.

# Figure 19. Slave FIFO Synchronous Read Timing Diagram

The following table provides the Slave FIFO Synchronous Read Parameters with Internally Sourced IFCLK. <sup>[36]</sup>

# Table 15. Slave FIFO Synchronous Read Parameters with Internally Sourced IFCLK

| Parameter          | Description                                 | Min   | Max  | Unit |

|--------------------|---------------------------------------------|-------|------|------|

| t <sub>IFCLK</sub> | IFCLK Period                                | 20.83 | -    | ns   |

| t <sub>SRD</sub>   | SLRD to Clock Setup Time                    | 18.7  | -    | ns   |

| t <sub>RDH</sub>   | Clock to SLRD Hold Time                     | 0     | -    | ns   |

| t <sub>OEon</sub>  | SLOE Turn on to FIFO Data Valid             | -     | 10.5 | ns   |

| t <sub>OEoff</sub> | SLOE Turn off to FIFO Data Hold             | -     | 10.5 | ns   |

| t <sub>XFLG</sub>  | Clock to FLAGS Output Propagation Delay     | -     | 9.5  | ns   |

| t <sub>XFD</sub>   | Clock to FIFO Data Output Propagation Delay | -     | 11   | ns   |

The following table provides the Slave FIFO Synchronous Read Parameters with Externally Sourced IFCLK.<sup>[36]</sup>

Table 16. Slave FIFO Synchronous Read Parameters with Externally Sourced IFCLK

| Parameter          | Description                                 | Min   | Max  | Unit |

|--------------------|---------------------------------------------|-------|------|------|

| t <sub>IFCLK</sub> | IFCLK Period                                | 20.83 | 200  | ns   |

| t <sub>SRD</sub>   | SLRD to Clock Setup Time                    | 12.7  | -    | ns   |

| t <sub>RDH</sub>   | Clock to SLRD Hold Time                     | 3.7   | -    | ns   |

| t <sub>OEon</sub>  | SLOE Turn on to FIFO Data Valid             | _     | 10.5 | ns   |

| t <sub>OEoff</sub> | SLOE Turn off to FIFO Data Hold             | -     | 10.5 | ns   |

| t <sub>XFLG</sub>  | Clock to FLAGS Output Propagation Delay     | -     | 13.5 | ns   |

| t <sub>XFD</sub>   | Clock to FIFO Data Output Propagation Delay | -     | 15   | ns   |

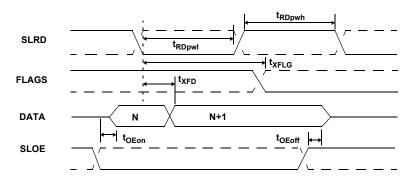

# Slave FIFO Asynchronous Read

In the following figure, dashed lines indicate signals with programmable polarity.

# Figure 20. Slave FIFO Asynchronous Read Timing Diagram

In the following table, the Slave FIFO asynchronous parameter values use internal IFCLK setting at 48 MHz.

# Table 17. Slave FIFO Asynchronous Read Parameters

| Parameter          | Description                                | Min | Max  | Unit |

|--------------------|--------------------------------------------|-----|------|------|

| t <sub>RDpwl</sub> | SLRD Pulse Width LOW                       | 50  | -    | ns   |

| t <sub>RDpwh</sub> | SLRD Pulse Width HIGH                      | 50  | -    | ns   |

| t <sub>XFLG</sub>  | SLRD to FLAGS Output Propagation Delay     | -   | 70   | ns   |

| t <sub>XFD</sub>   | SLRD to FIFO Data Output Propagation Delay | -   | 15   | ns   |

| t <sub>OEon</sub>  | SLOE Turn-on to FIFO Data Valid            | -   | 10.5 | ns   |

| t <sub>OEoff</sub> | SLOE Turn-off to FIFO Data Hold            | _   | 10.5 | ns   |

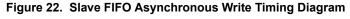

# **Slave FIFO Asynchronous Write**

In the following figure, dashed lines indicate signals with programmable polarity.

In the following table, the Slave FIFO asynchronous parameter values use internal IFCLK setting at 48 MHz.

### Table 20. Slave FIFO Asynchronous Write Parameters with Internally Sourced IFCLK

| Parameter          | Description                            | Min | Max | Unit |

|--------------------|----------------------------------------|-----|-----|------|

| t <sub>WRpwl</sub> | SLWR Pulse LOW                         | 50  | _   | ns   |

| t <sub>WRpwh</sub> | SLWR Pulse HIGH                        | 70  | -   | ns   |

| t <sub>SFD</sub>   | SLWR to FIFO DATA Setup Time           | 10  | -   | ns   |

| t <sub>FDH</sub>   | FIFO DATA to SLWR Hold Time            | 10  | -   | ns   |

| t <sub>XFD</sub>   | SLWR to FLAGS Output Propagation Delay | _   | 70  | ns   |

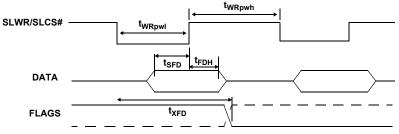

# Slave FIFO Synchronous Packet End Strobe

In the following figure, dashed lines indicate signals with programmable polarity.

# Figure 23. Slave FIFO Synchronous Packet End Strobe Timing Diagram

The following table provides the Slave FIFO Synchronous Packet End Strobe Parameters with Internally Sourced IFCLK. <sup>[38]</sup> **Table 21. Slave FIFO Synchronous Packet End Strobe Parameters with Internally Sourced IFCLK**

| Parameter          | Description                             | Min   | Мах | Unit |

|--------------------|-----------------------------------------|-------|-----|------|

| t <sub>IFCLK</sub> | IFCLK Period                            | 20.83 | _   | ns   |

| t <sub>SPE</sub>   | PKTEND to Clock Setup Time              | 14.6  | -   | ns   |

| t <sub>PEH</sub>   | Clock to PKTEND Hold Time               | 0     | _   | ns   |

| t <sub>XFLG</sub>  | Clock to FLAGS Output Propagation Delay | -     | 9.5 | ns   |

Note 38. IFCLK must not exceed 48 MHz.

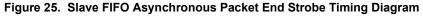

# Slave FIFO Asynchronous Packet End Strobe

In the following figure, dashed lines indicate signals with programmable polarity.

In the following table, the Slave FIFO asynchronous parameter values use internal IFCLK setting at 48 MHz.

# Table 23. Slave FIFO Asynchronous Packet End Strobe Parameters

| Parameter          | Description                              | Min | Мах | Unit |

|--------------------|------------------------------------------|-----|-----|------|

| t <sub>PEpwl</sub> | PKTEND Pulse Width LOW                   | 50  | _   | ns   |

| t <sub>PWpwh</sub> | PKTEND Pulse Width HIGH                  | 50  | _   | ns   |

| t <sub>XFLG</sub>  | PKTEND to FLAGS Output Propagation Delay | _   | 115 | ns   |

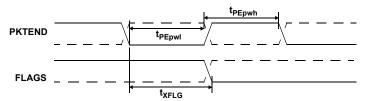

# **Slave FIFO Output Enable**

In the following figure, dashed lines indicate signals with programmable polarity.

# Table 24. Slave FIFO Output Enable Parameters

| Parameter          | Description                     | Max  | Unit |

|--------------------|---------------------------------|------|------|

| t <sub>OEon</sub>  | SLOE Assert to FIFO DATA Output | 10.5 | ns   |

| t <sub>OEoff</sub> | SLOE Deassert to FIFO DATA Hold | 10.5 | ns   |

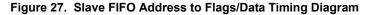

# Slave FIFO Address to Flags/Data

In the following figure, dashed lines indicate signals with programmable polarity.

# Table 25. Slave FIFO Address to Flags/Data Parameters

| Parameter         | Description                                       | Max  | Unit |

|-------------------|---------------------------------------------------|------|------|

| t <sub>XFLG</sub> | FIFOADR[1:0] to FLAGS Output Propagation Delay    | 10.7 | ns   |

| t <sub>XFD</sub>  | FIFOADR[1:0] to FIFODATA Output Propagation Delay | 14.3 | ns   |

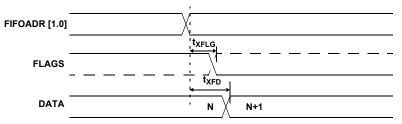

# **Ordering Information**

| Ordering Code    | Package Type               | RAM Size | # Prog I/Os | 8051<br>Address/Data<br>Busses |

|------------------|----------------------------|----------|-------------|--------------------------------|

| CY7C64713-128AXC | 128-pin TQFP - Pb-free     | 16K      | 40          | 16/8 bit                       |

| CY7C64713-100AXC | 100-pin TQFP - Pb-free     | 16K      | 40          | -                              |

| CY7C64713-56PVXC | 56-pin SSOP - Pb-free      | 16K      | 24          | -                              |

| CY7C64713-56LTXC | 56-pin QFN - Pb-free       | 16K      | 24          | -                              |

| CY3674           | EZ-USB FX1 Development Kit | •        |             |                                |

# **Ordering Code Definitions**

# **Document History Page**

| Revision | ECN     | Orig. of                   | Submission | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|----------|---------|----------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|