# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Detans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                        |

| Core Processor             | ARM® Cortex®-M3                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 100MHz                                                                          |

| Connectivity               | Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT |

| Number of I/O              | 70                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                     |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                            |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1767fbd100-551       |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M3 microcontroller

## 3. Applications

- eMetering

- Lighting

- Industrial networking

- Alarm systems

- White goods

- Motor control

## 4. Ordering information

### Table 1.Ordering information

| Type number   | Package  | 'ackage                                                                                     |          |  |  |  |  |

|---------------|----------|---------------------------------------------------------------------------------------------|----------|--|--|--|--|

|               | Name     | Description                                                                                 | Version  |  |  |  |  |

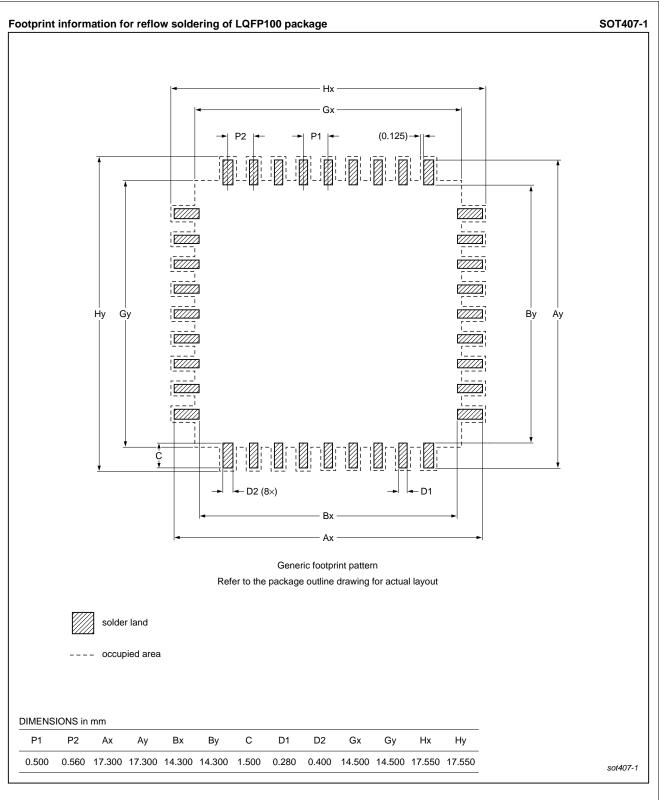

| LPC1769FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm         | SOT407-1 |  |  |  |  |

| LPC1768FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm         | SOT407-1 |  |  |  |  |

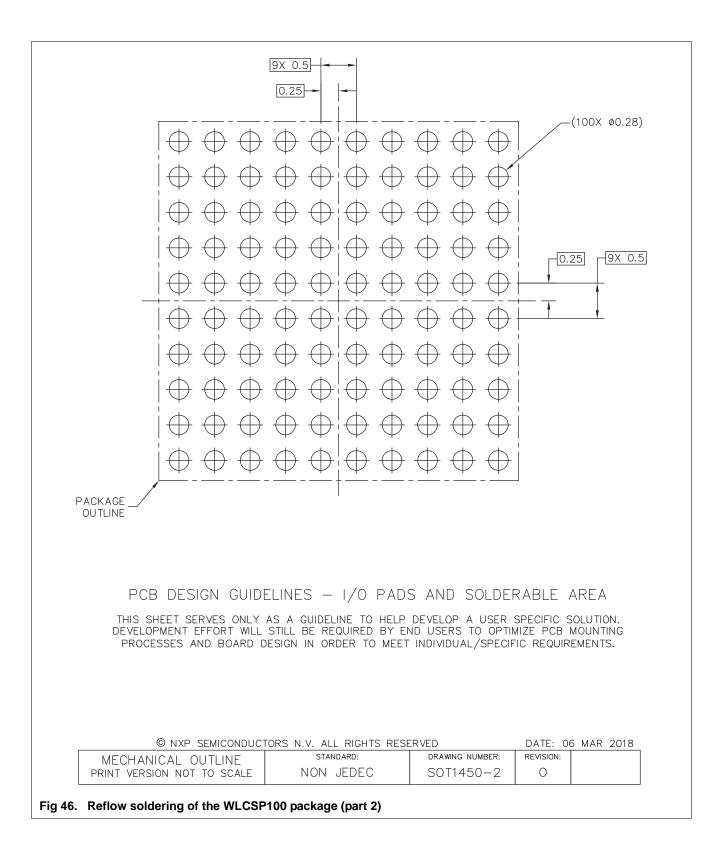

| LPC1768FET100 | TFBGA100 | plastic thin fine-pitch ball grid array package; 100 balls; body $9 \times 9 \times 0.7$ mm | SOT926-1 |  |  |  |  |

| LPC1768UK     | WLCSP100 | wafer level chip-scale package; 100 balls; $5.07 \times 5.07 \times 0.53$ mm                | -        |  |  |  |  |

| LPC1767FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm         | SOT407-1 |  |  |  |  |

| LPC1766FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm         | SOT407-1 |  |  |  |  |

| LPC1765FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm         | SOT407-1 |  |  |  |  |

| LPC1765FET100 | TFBGA100 | plastic thin fine-pitch ball grid array package; 100 balls; body $9 \times 9 \times 0.7$ mm | SOT926-1 |  |  |  |  |

| LPC1764FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm         | SOT407-1 |  |  |  |  |

| LPC1763FBD100 | LQFP100  | plastic low profile quad flat package; 100 leads; body $14 \times 14 \times 1.4$ mm         | SOT407-1 |  |  |  |  |

## 4.1 Ordering options

## Table 2.Ordering options

|               |                             |            | S   | RAM       | in k      | В     |          |                 |     |     |     |      | cy                                          |

|---------------|-----------------------------|------------|-----|-----------|-----------|-------|----------|-----------------|-----|-----|-----|------|---------------------------------------------|

| Type number   | Device order<br>part number | Flash (kB) | CPU | AHB SRAM0 | AHB SRAM1 | Total | Ethernet | USB             | CAN | l²S | DAC | GPIO | Maximum CPU<br>operating frequency<br>(MHz) |

| LPC1769FBD100 | LPC1769FBD100,551           | 512        | 32  | 16        | 16        | 64    | yes      | Device/Host/OTG | 2   | yes | yes | 70   | 120                                         |

| LPC1768FBD100 | LPC1768FBD100/CP32          | 512        | 32  | 16        | 16        | 64    | yes      | Device/Host/OTG | 2   | yes | yes | 70   | 100                                         |

| LPC1768FET100 | LPC1768FET100Z              | 512        | 32  | 16        | 16        | 64    | yes      | Device/Host/OTG | 2   | yes | yes | 70   | 100                                         |

| LPC1768UK     | LPC1768UKZ                  | 512        | 32  | 16        | 16        | 64    | yes      | Device/Host/OTG | 2   | yes | yes | 70   | 100                                         |

| LPC1767FBD100 | LPC1767FBD100,551           | 512        | 32  | 16        | 16        | 64    | yes      | no              | no  | yes | yes | 70   | 100                                         |

| LPC1766FBD100 | LPC1766FBD100,551           | 256        | 32  | 16        | 16        | 64    | yes      | Device/Host/OTG | 2   | yes | yes | 70   | 100                                         |

| LPC1765FBD100 | LPC1765FBD100/3271          | 256        | 32  | 16        | 16        | 64    | no       | Device/Host/OTG | 2   | yes | yes | 70   | 100                                         |

| LPC1765FET100 | LPC1765FET100,551           | 256        | 32  | 16        | 16        | 64    | no       | Device/Host/OTG | 2   | yes | yes | 70   | 100                                         |

| LPC1764FBD100 | LPC1764FBD100,551           | 128        | 16  | 16        | -         | 32    | yes      | Device only     | 2   | no  | no  | 70   | 100                                         |

| LPC1763FBD100 | LPC1763FBD100K              | 256        | 32  | 16        | 16        | 64    | no       | no              | no  | yes | yes | 70   | 100                                         |

4 of 93

32-bit ARM Cortex-M3 microcontroller

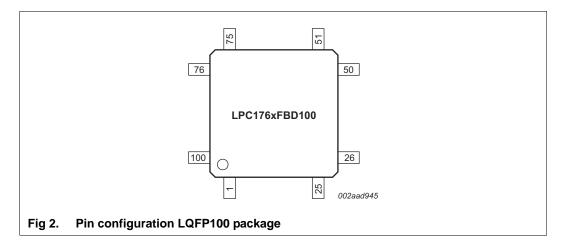

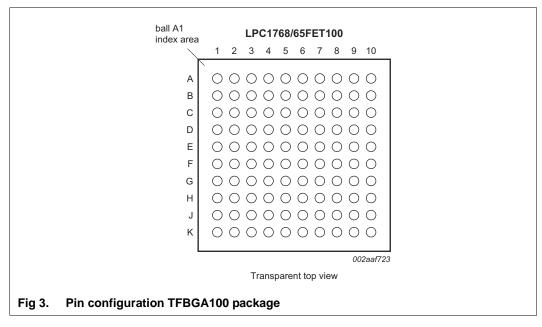

## 7. Pinning information

## 7.1 Pinning

| Table 5. | Pin description . | continued |

|----------|-------------------|-----------|

|----------|-------------------|-----------|

| Symbol Pin/ball           |         |          |          |            | Туре | Description                                                                                                                                                                                                                                   |

|---------------------------|---------|----------|----------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | LQFP100 | TFBGA100 | WLCSP100 |            |      |                                                                                                                                                                                                                                               |

| P1[25]/MCOA1/             | 39      | G5       | F9       | [1]        | I/O  | P1[25] — General purpose digital input/output pin.                                                                                                                                                                                            |

| MAT1[1]                   |         |          |          |            | 0    | <b>MCOA1</b> — Motor control PWM channel 1, output A.                                                                                                                                                                                         |

|                           |         |          |          |            | 0    | <b>MAT1[1]</b> — Match output for Timer 1, channel 1.                                                                                                                                                                                         |

| P1[26]/MCOB1/             | 40      | K6       | E10      | <u>[1]</u> | I/O  | P1[26] — General purpose digital input/output pin.                                                                                                                                                                                            |

| PWM1[6]/CAP0[0]           |         |          |          |            | 0    | <b>MCOB1</b> — Motor control PWM channel 1, output B.                                                                                                                                                                                         |

|                           |         |          |          |            | 0    | <b>PWM1[6]</b> — Pulse Width Modulator 1, channel 6 output.                                                                                                                                                                                   |

|                           |         |          |          |            | I    | CAP0[0] — Capture input for Timer 0, channel 0.                                                                                                                                                                                               |

| P1[27]/CLKOUT             | 43      | K7       | G9       | [1]        | I/O  | P1[27] — General purpose digital input/output pin.                                                                                                                                                                                            |

| /USB_OVRCR/<br>CAP0[1]    |         |          |          |            | 0    | CLKOUT — Clock output pin.                                                                                                                                                                                                                    |

| CAPOII                    |         |          |          |            | I    | USB_OVRCR — USB port Over-Current status. (LPC1769/68/66/65 only).                                                                                                                                                                            |

|                           |         |          |          |            | I    | CAP0[1] — Capture input for Timer 0, channel 1.                                                                                                                                                                                               |

| P1[28]/MCOA2/             | 44      | J7       | G10      | [1]        | I/O  | P1[28] — General purpose digital input/output pin.                                                                                                                                                                                            |

| PCAP1[0]/                 |         |          |          |            | 0    | MCOA2 — Motor control PWM channel 2, output A.                                                                                                                                                                                                |

| MAT0[0]                   |         |          |          |            | 1    | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                                                                                                                 |

|                           |         |          |          |            | 0    | MAT0[0] — Match output for Timer 0, channel 0.                                                                                                                                                                                                |

| P1[29]/MCOB2/             | 45      | G6       | G8       | [1]        | I/O  | P1[29] — General purpose digital input/output pin.                                                                                                                                                                                            |

| PCAP1[1]/                 |         |          |          |            | 0    | MCOB2 — Motor control PWM channel 2, output B.                                                                                                                                                                                                |

| MAT0[1]                   |         |          |          |            | I    | PCAP1[1] — Capture input for PWM1, channel 1.                                                                                                                                                                                                 |

|                           |         |          |          |            | 0    | MAT0[1] — Match output for Timer 0, channel 1.                                                                                                                                                                                                |

| P1[30]/V <sub>BUS</sub> / | 21      | H1       | B8       | [2]        | I/O  | P1[30] — General purpose digital input/output pin.                                                                                                                                                                                            |

| AD0[4]                    |         |          |          |            | I    | V <sub>BUS</sub> — Monitors the presence of USB bus power.<br>(LPC1769/68/66/65/64 only).                                                                                                                                                     |

|                           |         |          |          |            |      | Note: This signal must be HIGH for USB reset to occur.                                                                                                                                                                                        |

|                           |         |          |          |            | I    | AD0[4] — A/D converter 0, input 4.                                                                                                                                                                                                            |

| P1[31]/SCK1/              | 20      | F4       | C7       | [2]        | I/O  | P1[31] — General purpose digital input/output pin.                                                                                                                                                                                            |

| AD0[5]                    |         |          |          |            | I/O  | SCK1 — Serial Clock for SSP1.                                                                                                                                                                                                                 |

|                           |         |          |          |            | I    | AD0[5] — A/D converter 0, input 5.                                                                                                                                                                                                            |

| P2[0] to P2[31]           |         |          |          |            | I/O  | <b>Port 2:</b> Port 2 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 2 pins depends upon the pin function selected via the pin connect block. Pins 14 through 31 of this port are not available. |

| P2[0]/PWM1[1]/            | 75      | B9       | K1       | [1]        | I/O  | P2[0] — General purpose digital input/output pin.                                                                                                                                                                                             |

| TXD1                      |         |          |          |            | 0    | <b>PWM1[1]</b> — Pulse Width Modulator 1, channel 1 output.                                                                                                                                                                                   |

|                           |         |          |          |            | 0    | <b>TXD1</b> — Transmitter output for UART1.                                                                                                                                                                                                   |

| P2[1]/PWM1[2]/            | 74      | B10      | J2       | [1]        | I/O  | P2[1] — General purpose digital input/output pin.                                                                                                                                                                                             |

| RXD1                      |         |          |          |            | 0    | <b>PWM1[2]</b> — Pulse Width Modulator 1, channel 2 output.                                                                                                                                                                                   |

|                           |         |          |          |            | 1    | <b>RXD1</b> — Receiver input for UART1.                                                                                                                                                                                                       |

|                           |         | 1        | 1        | 1          | 1    | -                                                                                                                                                                                                                                             |

| Table 5. | Pin description | continued |

|----------|-----------------|-----------|

|----------|-----------------|-----------|

| Symbol          | Pin/ball |          |          |            | Туре | Description                                                                                                                                                                                                                                                     |  |  |  |

|-----------------|----------|----------|----------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                 | LQFP100  | TFBGA100 | WLCSP100 |            |      |                                                                                                                                                                                                                                                                 |  |  |  |

| P2[11]/EINT1/   | 52       | H8       | J8       | <u>[6]</u> | I/O  | P2[11] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |  |

| I2STX_CLK       |          |          |          |            | I    | EINT1 — External interrupt 1 input.                                                                                                                                                                                                                             |  |  |  |

|                 |          |          |          |            | I/O  | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>I</i> <sup>2</sup> S-bus specification. (LPC1769/68/67/66/65/63 only).                                                         |  |  |  |

| P2[12]/EINT2/   | 51       | K10      | K10      | [6]        | I/O  | P2[12] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |  |

| I2STX_WS        |          |          |          |            | I    | EINT2 — External interrupt 2 input.                                                                                                                                                                                                                             |  |  |  |

|                 |          |          |          |            | I/O  | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification. (LPC1769/68/67/66/65/63 only).                                                                     |  |  |  |

| P2[13]/EINT3/   | 50       | J9       | J9       | [6]        | I/O  | P2[13] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |  |

| I2STX_SDA       |          |          |          |            | I    | EINT3 — External interrupt 3 input.                                                                                                                                                                                                                             |  |  |  |

|                 |          |          |          |            | I/O  | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $PS$ -bus specification. (LPC1769/68/67/66/65/63 only).                                                                         |  |  |  |

| P3[0] to P3[31] |          |          |          |            | I/O  | <b>Port 3:</b> Port 3 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 3 pins depends upon the pin function selected via the pin connect block. Pins 0 through 24, and 27 through 31 of this port are not available. |  |  |  |

| P3[25]/MAT0[0]/ | 27       | H3       | D8       | [1]        | I/O  | P3[25] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |  |

| PWM1[2]         |          |          |          |            | 0    | MAT0[0] — Match output for Timer 0, channel 0.                                                                                                                                                                                                                  |  |  |  |

|                 |          |          |          |            | 0    | PWM1[2] — Pulse Width Modulator 1, output 2.                                                                                                                                                                                                                    |  |  |  |

| P3[26]/STCLK/   | 26       | K1       | A10      | <u>[1]</u> | I/O  | P3[26] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |  |

| MAT0[1]/PWM1[3] |          |          |          |            | I    | <b>STCLK</b> — System tick timer clock input. The maximum STCLK frequency is 1/4 of the Arm processor clock frequency CCLK.                                                                                                                                     |  |  |  |

|                 |          |          |          |            | 0    | <b>MAT0[1]</b> — Match output for Timer 0, channel 1.                                                                                                                                                                                                           |  |  |  |

|                 |          |          |          |            | 0    | <b>PWM1[3]</b> — Pulse Width Modulator 1, output 3.                                                                                                                                                                                                             |  |  |  |

| P4[0] to P4[31] |          |          |          |            | I/O  | <b>Port 4:</b> Port 4 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 4 pins depends upon the pin function selected via the pin connect block. Pins 0 through 27, 30, and 31 of this port are not available.        |  |  |  |

| P4[28]/RX_MCLK/ | 82       | C7       | G1       | [1]        | I/O  | P4[28] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |  |

| MAT2[0]/TXD3    |          |          |          |            | 0    | <b>RX_MCLK</b> — I <sup>2</sup> S receive master clock. (LPC1769/68/67/66/65 only).                                                                                                                                                                             |  |  |  |

|                 |          |          |          |            | 0    | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                                                                                                  |  |  |  |

|                 |          |          |          |            | 0    | TXD3 — Transmitter output for UART3.                                                                                                                                                                                                                            |  |  |  |

| P4[29]/TX_MCLK/ | 85       | E6       | F1       | <u>[1]</u> | I/O  | P4[29] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |  |

| MAT2[1]/RXD3    |          |          |          |            | 0    | <b>TX_MCLK</b> — I <sup>2</sup> S transmit master clock. (LPC1769/68/67/66/65 only).                                                                                                                                                                            |  |  |  |

|                 |          |          |          |            | 0    | MAT2[1] — Match output for Timer 2, channel 1.                                                                                                                                                                                                                  |  |  |  |

|                 |          |          |          |            | 1    | <b>RXD3</b> — Receiver input for UART3.                                                                                                                                                                                                                         |  |  |  |

LPC1769\_68\_67\_66\_65\_64\_63

All information provided in this document is subject to legal disclaimers.

| Symbol | Pin/    | Pin/ball  |           |          | Туре | Description                                                                                                                                                                                         |  |  |

|--------|---------|-----------|-----------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | LQFP100 | TFBGA100  | WLCSP100  |          |      |                                                                                                                                                                                                     |  |  |

| VREFN  | 15      | F1        | A6        |          | I    | ADC negative reference voltage: This should be nominally the same voltage as $V_{SS}$ but should be isolated to minimize noise and error. Level on this pin is used as a reference for ADC and DAC. |  |  |

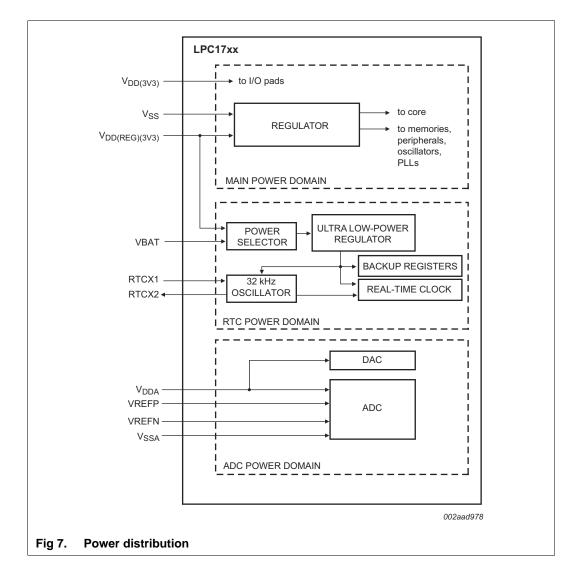

| VBAT   | 19      | G2        | A8        | [10][12] | I    | <b>RTC pin power supply:</b> 3.3 V on this pin supplies the power to the RTC peripheral.                                                                                                            |  |  |

| n.c.   | 13      | D4,<br>E4 | B6,<br>D6 |          | -    | not connected.                                                                                                                                                                                      |  |  |

#### Table 5. Pin description ...continued

[1] 5 V tolerant pad providing digital I/O functions with TTL levels and hysteresis. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

[2] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

- [3] 5 V tolerant pad providing digital I/O with TTL levels and hysteresis and analog output function. When configured as the DAC output, digital section of the pad is disabled. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

- [4] Open-drain 5 V tolerant digital I/O pad, compatible with I<sup>2</sup>C-bus 400 kHz specification. This pad requires an external pull-up to provide output functionality. When power is switched off, this pin connected to the I<sup>2</sup>C-bus is floating and does not disturb the I<sup>2</sup>C lines. Open-drain configuration applies to all functions on this pin.

- [5] Pad provides digital I/O and USB functions. It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only). This pad is not 5 V tolerant.

- [6] 5 V tolerant pad with 10 ns glitch filter providing digital I/O functions with TTL levels and hysteresis. This pin is pulled up to a voltage level of 2.3 V to 2.6 V.

- [7] 5 V tolerant pad with TTL levels and hysteresis. Internal pull-up and pull-down resistors disabled.

- [8] 5 V tolerant pad with TTL levels and hysteresis and internal pull-up resistor.

- [9] 5 V tolerant pad with 20 ns glitch filter providing digital I/O function with TTL levels and hysteresis.

- [10] Pad provides special analog functionality. A 32 kHz crystal oscillator must be used with the RTC.

- [11] When the system oscillator is not used, connect XTAL1 and XTAL2 as follows: XTAL1 can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTAL2 should be left floating.

- [12] When the RTC is not used, connect VBAT to  $V_{DD(REG)(3V3)}$  and leave RTCX1 floating.

## 8.9.1 Features

- Eight DMA channels. Each channel can support an unidirectional transfer.

- 16 DMA request lines.

- Single DMA and burst DMA request signals. Each peripheral connected to the DMA Controller can assert either a burst DMA request or a single DMA request. The DMA burst size is set by programming the DMA Controller.

- Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and peripheral-to-peripheral transfers are supported.

- Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

- Hardware DMA channel priority.

- AHB slave DMA programming interface. The DMA Controller is programmed by writing to the DMA control registers over the AHB slave interface.

- One AHB bus master for transferring data. The interface transfers data when a DMA request goes active.

- 32-bit AHB master bus width.

- Incrementing or non-incrementing addressing for source and destination.

- Programmable DMA burst size. The DMA burst size can be programmed to more efficiently transfer data.

- Internal four-word FIFO per channel.

- Supports 8, 16, and 32-bit wide transactions.

- Big-endian and little-endian support. The DMA Controller defaults to little-endian mode on reset.

- An interrupt to the processor can be generated on a DMA completion or when a DMA error has occurred.

- Raw interrupt status. The DMA error and DMA count raw interrupt status can be read prior to masking.

## 8.10 Fast general purpose parallel I/O

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Separate registers allow setting or clearing any number of outputs simultaneously. The value of the output register may be read back as well as the current state of the port pins.

LPC17xx use accelerated GPIO functions:

- GPIO registers are accessed through the AHB multilayer bus so that the fastest possible I/O timing can be achieved.

- Mask registers allow treating sets of port bits as a group, leaving other bits unchanged.

- All GPIO registers are byte and half-word addressable.

- Entire port value can be written in one instruction.

- Support for Cortex-M3 bit banding.

- Support for use with the GPDMA controller.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- Up to two match registers can be used to generate timed DMA requests.

## 8.22 Pulse width modulator

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC17xx. The Timer is designed to count cycles of the system derived clock and optionally switch pins, generate interrupts or perform other actions when specified timer values occur, based on seven match registers. The PWM function is in addition to these features, and is based on match register events.

The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (PWMMR0) controls the PWM cycle rate, by resetting the count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an PWMMR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the PWMMR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

### 8.22.1 Features

- One PWM block with Counter or Timer operation (may use the peripheral clock or one of the capture inputs as the clock source).

- Seven match registers allow up to 6 single edge controlled or 3 double edge controlled PWM outputs, or a mix of both types. The match registers also allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

32-bit ARM Cortex-M3 microcontroller

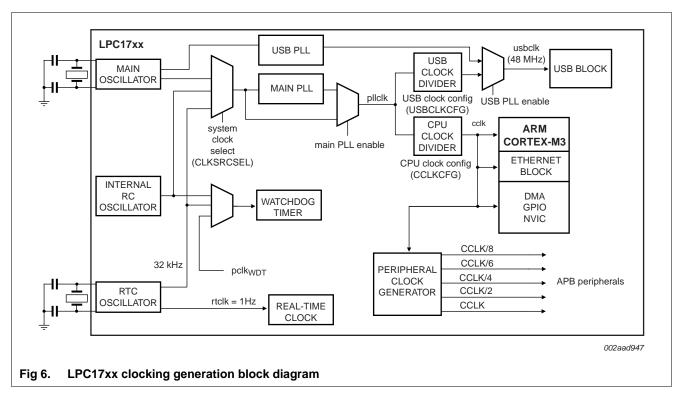

See Figure 6 for an overview of the LPC17xx clock generation.

### 8.29.1.1 Internal RC oscillator

The IRC may be used as the clock source for the WDT, and/or as the clock that drives the PLL and subsequently the CPU. The nominal IRC frequency is 4 MHz. The IRC is trimmed to 1 % accuracy over the entire voltage and temperature range.

Upon power-up or any chip reset, the LPC17xx use the IRC as the clock source. Software may later switch to one of the other available clock sources.

### 8.29.1.2 Main oscillator

The main oscillator can be used as the clock source for the CPU, with or without using the PLL. The main oscillator also provides the clock source for the dedicated USB PLL.

The main oscillator operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the main PLL. The clock selected as the PLL input is PLLCLKIN. The Arm processor clock frequency is referred to as CCLK elsewhere in this document. The frequencies of PLLCLKIN and CCLK are the same value unless the PLL is active and connected. The clock frequency for each peripheral can be selected individually and is referred to as PCLK. Refer to <u>Section 8.29.2</u> for additional information.

## 8.29.1.3 RTC oscillator

The RTC oscillator can be used as the clock source for the RTC block, the main PLL, and/or the CPU.

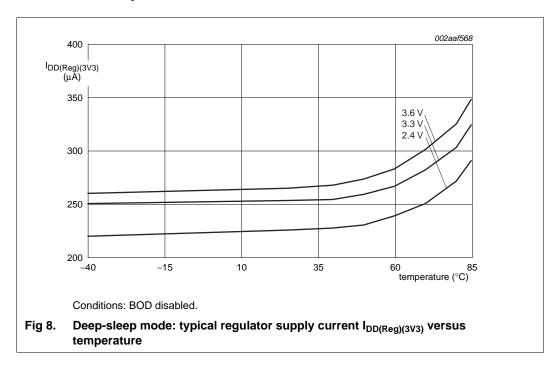

The Deep-sleep mode can be terminated and normal operation resumed by either a Reset or certain specific interrupts that are able to function without clocks. Since all dynamic operation of the chip is suspended, Deep-sleep mode reduces chip power consumption to a very low value. Power to the flash memory is left on in Deep-sleep mode, allowing a very quick wake-up.

On wake-up from Deep-sleep mode, the code execution and peripherals activities will resume after 4 cycles expire if the IRC was used before entering Deep-sleep mode. If the main external oscillator was used, the code execution will resume when 4096 cycles expire. PLL and clock dividers need to be reconfigured accordingly.

### 8.29.6.3 Power-down mode

Power-down mode does everything that Deep-sleep mode does, but also turns off the power to the IRC oscillator and the flash memory. This saves more power but requires waiting for resumption of flash operation before execution of code or data access in the flash memory can be accomplished.

On the wake-up of Power-down mode, if the IRC was used before entering Power-down mode, it will take IRC 60  $\mu$ s to start-up. After this 4 IRC cycles will expire before the code execution can then be resumed if the code was running from SRAM. In the meantime, the flash wake-up timer then counts 4 MHz IRC clock cycles to make the 100  $\mu$ s flash start-up time. When it times out, access to the flash will be allowed. Users need to reconfigure the PLL and clock dividers accordingly.

### 8.29.6.4 Deep power-down mode

The Deep power-down mode can only be entered from the RTC block. In Deep power-down mode, power is shut off to the entire chip with the exception of the RTC module and the RESET pin.

The LPC17xx can wake up from Deep power-down mode via the RESET pin or an alarm match event of the RTC.

### 8.29.6.5 Wake-up interrupt controller

The Wake-up Interrupt Controller (WIC) allows the CPU to automatically wake up from any enabled priority interrupt that can occur while the clocks are stopped in Deep sleep, Power-down, and Deep power-down modes.

The WIC works in connection with the Nested Vectored Interrupt Controller (NVIC). When the CPU enters Deep sleep, Power-down, or Deep power-down mode, the NVIC sends a mask of the current interrupt situation to the WIC. This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately. With this information, the WIC simply notices when one of the interrupts has occurred and then it wakes up the CPU.

The WIC eliminates the need to periodically wake up the CPU and poll the interrupts resulting in additional power savings.

## 8.29.7 Peripheral power control

A Power Control for Peripherals feature allows individual peripherals to be turned off if they are not needed in the application, resulting in additional power savings.

## 8.30 System control

## 8.30.1 Reset

Reset has four sources on the LPC17xx: the RESET pin, the Watchdog reset, power-on reset (POR), and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once the operating voltage attains a usable level, causes the RSTOUT pin to go LOW and starts the wake-up timer (see description in Section 8.29.5). The wake-up timer ensures that reset remains asserted until the external Reset is de-asserted, the oscillator is running, a fixed number of clocks have passed, and the flash controller has completed its initialization. Once reset is de-asserted, or, in case of a BOD-triggered reset, once the voltage rises above the BOD threshold, the RSTOUT pin goes HIGH.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the Boot Block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

#### 32-bit ARM Cortex-M3 microcontroller

- [5] The RTC typically fails when V<sub>i(VBAT)</sub> drops below 1.6 V.

- [6] V<sub>DD(REG)(3V3)</sub> = 3.3 V; T<sub>amb</sub> = 25 °C for all power consumption measurements.

- [7] Applies to LPC1768/67/66/65/64/63.

- [8] Applies to LPC1769 only.

- [9] IRC running at 4 MHz; main oscillator and PLL disabled; PCLK = CCLK/8.

- [10] BOD disabled.

- [11] On pin V<sub>DD(REG)(3V3)</sub>. I<sub>BAT</sub> = 530 nA. V<sub>DD(REG)(3V3)</sub> = 3.0 V; V<sub>BAT</sub> = 3.0 V; T<sub>amb</sub> = 25 °C.

- [12] On pin VBAT; I<sub>DD(REG)(3V3)</sub> = 630 nA; V<sub>DD(REG)(3V3)</sub> = 3.0 V; V<sub>BAT</sub> = 3.0 V; T<sub>amb</sub> = 25 °C.

- [13] On pin VBAT;  $V_{BAT}$  = 3.0 V;  $T_{amb}$  = 25 °C.

- [14] All internal pull-ups disabled. All pins configured as output and driven LOW. V<sub>DD(3V3)</sub> = 3.3 V; T<sub>amb</sub> = 25 °C.

- [15] TCK/SWDCLK pin needs to be externally pulled LOW.

- [16] On pin V<sub>DDA</sub>; V<sub>DDA</sub> = 3.3 V; T<sub>amb</sub> = 25 °C. The ADC is powered if the PDN bit in the AD0CR register is set to 1 and in Power-down mode of the PDN bit is set to 0.

- [17] The ADC is powered if the PDN bit in the AD0CR register is set to 1. See LPC17xx user manual UM10360\_1.

- [18] The ADC is in Power-down mode if the PDN bit in the AD0CR register is set to 0. See LPC17xx user manual UM10360\_1.

- [19]  $V_{i(VREFP)} = 3.3 V$ ;  $T_{amb} = 25 °C$ .

- [20] Including voltage on outputs in 3-state mode.

- [21] V<sub>DD(3V3)</sub> supply voltages must be present.

- [22] 3-state outputs go into 3-state mode in Deep power-down mode.

- [23] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

- [24] To  $V_{\text{SS}}.$

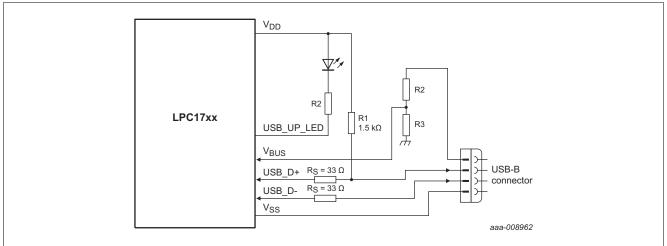

- [25] Includes external resistors of 33  $\Omega\pm$  1 % on D+ and D–.

## **11.1 Power consumption**

32-bit ARM Cortex-M3 microcontroller

32-bit ARM Cortex-M3 microcontroller

## 13. ADC electrical characteristics

### Table 19. ADC characteristics (full resolution)

$V_{DDA} = 2.5 \text{ V to } 3.6 \text{ V}; T_{amb} = -40 \degree \text{C to } +85 \degree \text{C}$  unless otherwise specified; ADC frequency 13 MHz; 12-bit resolution.<sup>[1]</sup>

| Symbol                | Parameter                           | Conditions |            | Min | Тур | Max              | Unit |

|-----------------------|-------------------------------------|------------|------------|-----|-----|------------------|------|

| VIA                   | analog input voltage                |            |            | 0   | -   | V <sub>DDA</sub> | V    |

| C <sub>ia</sub>       | analog input capacitance            |            |            | -   | -   | 15               | pF   |

| E <sub>D</sub>        | differential linearity error        |            | [2][3]     | -   | -   | ±1               | LSB  |

| E <sub>L(adj)</sub>   | integral non-linearity              |            | [4]        | -   | -   | ±3               | LSB  |

| Eo                    | offset error                        |            | [5][6]     | -   | -   | ±2               | LSB  |

| E <sub>G</sub>        | gain error                          |            | [7]        | -   | -   | 0.5              | %    |

| Ε <sub>T</sub>        | absolute error                      |            | [8]        | -   | -   | 4                | LSB  |

| R <sub>vsi</sub>      | voltage source interface resistance |            | <u>[9]</u> | -   | -   | 7.5              | kΩ   |

| f <sub>clk(ADC)</sub> | ADC clock frequency                 |            |            | -   | -   | 13               | MHz  |

| f <sub>c(ADC)</sub>   | ADC conversion frequency            |            | [10]       | -   | -   | 200              | kHz  |

[1]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

- [2] The ADC is monotonic, there are no missing codes.

- [3] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 28.

- [4] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 28</u>.

- [5] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See <u>Figure 28</u>.

- [6] ADCOFFS value (bits 7:4) = 2 in the ADTRM register. See LPC17xx user manual UM10360.

- [7] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See <u>Figure 28</u>.

- [8] The absolute error ( $E_T$ ) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve. See Figure 28.

[10] The conversion frequency corresponds to the number of samples per second.

<sup>[9]</sup> See Figure 29.

32-bit ARM Cortex-M3 microcontroller

| Symbol                | Parameter                    | Conditions                                               |        | Min | Тур  | Max | Unit |

|-----------------------|------------------------------|----------------------------------------------------------|--------|-----|------|-----|------|

| E <sub>D</sub>        | differential linearity error |                                                          | [2][3] | -   | ±1   | -   | LSB  |

| E <sub>L(adj)</sub>   | integral non-linearity       |                                                          | [4]    | -   | ±1.5 | -   | LSB  |

| Eo                    | offset error                 |                                                          | [5]    | -   | ±2   | -   | LSB  |

| E <sub>G</sub>        | gain error                   |                                                          | [6]    | -   | ±2   | -   | LSB  |

| f <sub>clk(ADC)</sub> | ADC clock frequency          | $3.0~V \leq V_{DDA} \leq 3.6~V$                          |        | -   | -    | 33  | MHz  |

|                       |                              | $2.7~\text{V} \leq \text{V}_{\text{DDA}} < 3.0~\text{V}$ |        | -   | -    | 25  | MHz  |

| f <sub>c(ADC)</sub>   | ADC conversion frequency     | $3~V \leq V_{DDA} \leq 3.6~V$                            | [7]    | -   | -    | 500 | kHz  |

|                       |                              | $2.7~V \leq V_{DDA} < 3.0~V$                             | [7]    | -   | -    | 400 | kHz  |

#### Table 20. ADC characteristics (lower resolution)

$T_{amb} = -40 \degree C$  to +85  $\degree C$  unless otherwise specified; 12-bit ADC used as 10-bit resolution ADC.[1]

[1]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

[2] The ADC is monotonic, there are no missing codes.

[3] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 28.

[4] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 28</u>.

[5] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See <u>Figure 28</u>.

[6] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See <u>Figure 28</u>.

[7] The conversion frequency corresponds to the number of samples per second.

### 32-bit ARM Cortex-M3 microcontroller

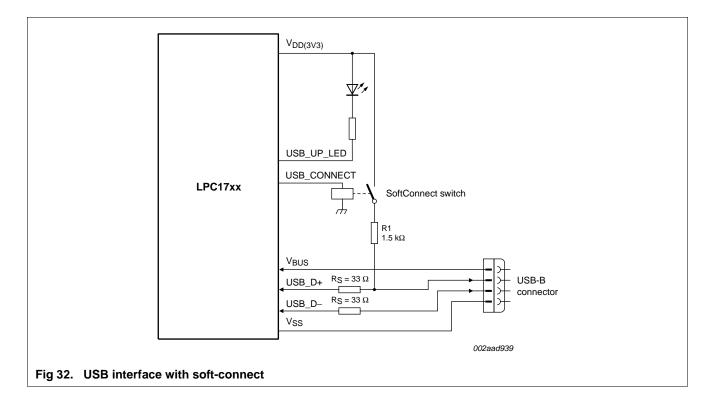

Fig 31. USB interface on a bus-powered device where  $V_{BUS} = 5 V$ ,  $V_{DD}$  not present

32-bit ARM Cortex-M3 microcontroller

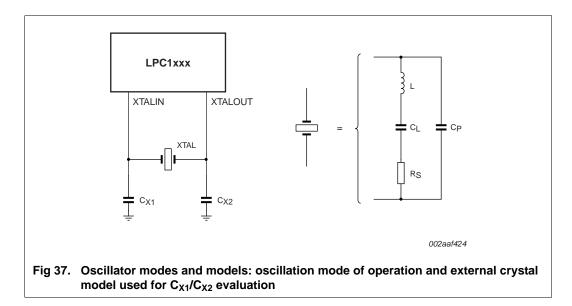

| Table 23. | Recommended values for $C_{X1}/C_{X2}$ in oscillation mode (crystal and external |

|-----------|----------------------------------------------------------------------------------|

|           | components parameters): low frequency mode                                       |

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> /C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------|

| 1 MHz to 5 MHz                                     | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 300 Ω                                             | 39 pF, 39 pF                                                 |

|                                                    | 30 pF                                      | < 300 Ω                                             | 57 pF, 57 pF                                                 |

| 5 MHz to 10 MHz                                    | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 200 Ω                                             | 39 pF, 39 pF                                                 |

|                                                    | 30 pF                                      | < 100 Ω                                             | 57 pF, 57 pF                                                 |

| 10 MHz to 15 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 60 Ω                                              | 39 pF, 39 pF                                                 |

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 80 Ω                                              | 18 pF, 18 pF                                                 |

Table 24. Recommended values for  $C_{X1}/C_{X2}$  in oscillation mode (crystal and external components parameters): high frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 180 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 100 Ω                                             | 39 pF, 39 pF                                                  |

| 20 MHz to 25 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 80 Ω                                              | 39 pF, 39 pF                                                  |

## 15.3 XTAL and RTCX Printed Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input and output pins of the chip. Take care that the load capacitors  $C_{x1}$ ,  $C_{x2}$ , and  $C_{x3}$  in case of third overtone crystal usage have a common ground plane. The external components must also be connected to the ground plain. Loops must be made as small as possible in

32-bit ARM Cortex-M3 microcontroller

## 17. Soldering

Fig 43. Reflow soldering for the LQFP100 package

LPC1769\_68\_67\_66\_65\_64\_63

© NXP Semiconductors N.V. 2018. All rights reserved.

### 32-bit ARM Cortex-M3 microcontroller

#### 32-bit ARM Cortex-M3 microcontroller

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Non-automotive qualified products** — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond

## 22. Contact information

NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

## 21.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP B.V.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

| 11   | Static characteristics                      | 47 |

|------|---------------------------------------------|----|

| 11.1 | Power consumption                           | 50 |

| 11.2 | Peripheral power consumption                | 53 |

| 11.3 | Electrical pin characteristics              | 54 |

| 12   | Dynamic characteristics                     | 56 |

| 12.1 | Flash memory                                | 56 |

| 12.2 | External clock                              | 56 |

| 12.3 | Internal oscillators                        | 57 |

| 12.4 | I/O pins                                    | 57 |

| 12.5 | I <sup>2</sup> C-bus                        | 58 |

| 12.6 | I <sup>2</sup> S-bus interface              | 59 |

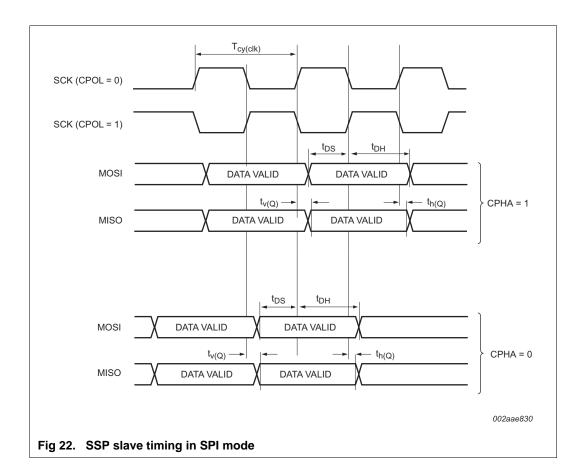

| 12.7 | SSP interface                               | 61 |

| 12.8 | USB interface                               | 63 |

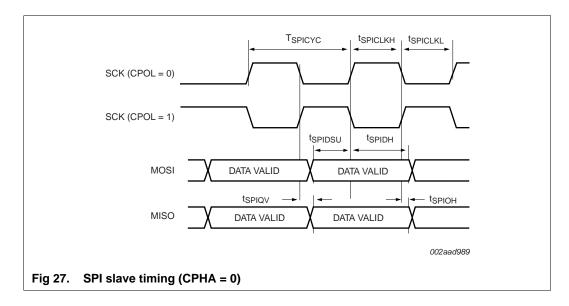

| 12.9 | SPI                                         | 64 |

| 13   | ADC electrical characteristics              | 66 |

| 14   | DAC electrical characteristics              | 69 |

| 15   | Application information                     | 70 |

| 15.1 | Suggested USB interface solutions           | 70 |

| 15.2 | Crystal oscillator XTAL input and component |    |

|      | selection                                   | 73 |

| 15.3 | XTAL and RTCX Printed Circuit Board (PCB)   |    |

|      | layout guidelines                           | 74 |

| 15.4 | Standard I/O pin configuration              | 75 |

| 15.5 | Reset pin configuration                     | 76 |

| 15.6 | ElectroMagnetic Compatibility (EMC)         | 77 |

| 16   | Package outline                             | 78 |

| 17   | Soldering                                   | 81 |

| 18   | Abbreviations                               | 86 |

| 19   | References                                  | 86 |

| 20   | Revision history                            | 87 |

| 21   | Legal information                           | 90 |

| 21.1 | Data sheet status                           | 90 |

| 21.2 | Definitions                                 | 90 |

| 21.3 | Disclaimers                                 | 90 |

| 21.4 | Trademarks                                  | 91 |

| 22   | Contact information                         | 91 |

| 23   | Contents                                    | 92 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP Semiconductors N.V. 2018.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com Date of release: 4 May 2018

Document identifier: LPC1769\_68\_67\_66\_65\_64\_63