# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| D | e | ta | 31 | IS |

|---|---|----|----|----|

|   |   |    |    |    |

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                                           |

| Core Processor             | ARM® Cortex®-M3                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 100MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT    |

| Number of I/O              | 70                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 64K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                               |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-LQFP                                                                           |

| Supplier Device Package    | 100-LQFP (14x14)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1768fbd100-551          |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 5. | Pin description continued |  |

|----------|---------------------------|--|

|----------|---------------------------|--|

| Symbol                      | Pin/ball |          |          | Туре       | Description |                                                                                                                                                                                                                  |

|-----------------------------|----------|----------|----------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | LQFP100  | TFBGA100 | WLCSP100 |            |             |                                                                                                                                                                                                                  |

| P0[4]/                      | 81       | A8       | G2       | <u>[1]</u> | I/O         | P0[4] — General purpose digital input/output pin.                                                                                                                                                                |

| I2SRX_CLK/<br>RD2/CAP2[0]   |          |          |          |            | I/O         | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>PS-bus specification</i> . (LPC1769/68/67/66/65/63 only).                        |

|                             |          |          |          |            | I           | RD2 — CAN2 receiver input. (LPC1769/68/66/65/64 only).                                                                                                                                                           |

|                             |          |          |          |            | I           | CAP2[0] — Capture input for Timer 2, channel 0.                                                                                                                                                                  |

| P0[5]/                      | 80       | D7       | H1       | <u>[1]</u> | I/O         | P0[5] — General purpose digital input/output pin.                                                                                                                                                                |

| I2SRX_WS/<br>TD2/CAP2[1]    |          |          |          |            | I/O         | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification. (LPC1769/68/67/66/65/63 only).                         |

|                             |          |          |          |            | 0           | TD2 — CAN2 transmitter output. (LPC1769/68/66/65/64 only).                                                                                                                                                       |

|                             |          |          |          |            | I           | CAP2[1] — Capture input for Timer 2, channel 1.                                                                                                                                                                  |

| P0[6]/                      | 79       | B8       | G3       | <u>[1]</u> | I/O         | P0[6] — General purpose digital input/output pin.                                                                                                                                                                |

| I2SRX_SDA/<br>SSEL1/MAT2[0] |          |          |          |            | I/O         | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. (LPC1769/68/67/66/65/63 only). |

|                             |          |          |          |            | I/O         | SSEL1 — Slave Select for SSP1.                                                                                                                                                                                   |

|                             |          |          |          |            | 0           | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                                                   |

| P0[7]/                      | 78       | A9       | J1       | <u>[1]</u> | I/O         | P0[7] — General purpose digital input/output pin.                                                                                                                                                                |

| I2STX_CLK/<br>SCK1/MAT2[1]  |          |          |          |            | I/O         | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>PS-bus specification</i> . (LPC1769/68/67/66/65/63 only).                       |

|                             |          |          |          |            | I/O         | SCK1 — Serial Clock for SSP1.                                                                                                                                                                                    |

|                             |          |          |          |            | 0           | MAT2[1] — Match output for Timer 2, channel 1.                                                                                                                                                                   |

| P0[8]/                      | 77       | C8       | H2       | <u>[1]</u> | I/O         | P0[8] — General purpose digital input/output pin.                                                                                                                                                                |

| I2STX_WS/<br>MISO1/MAT2[2]  |          |          |          |            | I/O         | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification. (LPC1769/68/67/66/65/63 only).                      |

|                             |          |          |          |            | I/O         | MISO1 — Master In Slave Out for SSP1.                                                                                                                                                                            |

|                             |          |          |          |            | 0           | MAT2[2] — Match output for Timer 2, channel 2.                                                                                                                                                                   |

| P0[9]/                      | 76       | A10      | H3       | <u>[1]</u> | I/O         | P0[9] — General purpose digital input/output pin.                                                                                                                                                                |

| I2STX_SDA/<br>MOSI1/MAT2[3] |          |          |          |            | I/O         | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $PS$ -bus specification. (LPC1769/68/67/66/65/63 only).                          |

|                             |          |          |          |            | I/O         | MOSI1 — Master Out Slave In for SSP1.                                                                                                                                                                            |

|                             |          |          |          |            | 0           | MAT2[3] — Match output for Timer 2, channel 3.                                                                                                                                                                   |

| P0[10]/TXD2/                | 48       | H7       | H8       | <u>[1]</u> | I/O         | P0[10] — General purpose digital input/output pin.                                                                                                                                                               |

| SDA2/MAT3[0]                |          |          |          |            | 0           | TXD2 — Transmitter output for UART2.                                                                                                                                                                             |

|                             |          |          |          |            | I/O         | <b>SDA2</b> — $I^2C^2$ data input/output (this is not an open-drain pin).                                                                                                                                        |

|                             |          |          |          |            | 0           | MAT3[0] — Match output for Timer 3, channel 0.                                                                                                                                                                   |

LPC1769\_68\_67\_66\_65\_64\_63

All information provided in this document is subject to legal disclaimers.

Table 5.

Pin description ...continued

| Symbol                | Pin/ball |          |          |            | Туре | Description                                                                                                                                                               |  |  |  |

|-----------------------|----------|----------|----------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                       | LQFP100  | TFBGA100 | WLCSP100 |            |      |                                                                                                                                                                           |  |  |  |

| P2[2]/PWM1[3]/        | 73       | D8       | K2       | [1]        | I/O  | P2[2] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

| CTS1/<br>TRACEDATA[3] |          |          |          |            | 0    | PWM1[3] — Pulse Width Modulator 1, channel 3 output.                                                                                                                      |  |  |  |

|                       |          |          |          |            | I    | CTS1 — Clear to Send input for UART1.                                                                                                                                     |  |  |  |

|                       |          |          |          |            | 0    | TRACEDATA[3] — Trace data, bit 3.                                                                                                                                         |  |  |  |

| P2[3]/PWM1[4]/        | 70       | E7       | K3       | [1]        | I/O  | P2[3] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

| DCD1/<br>TRACEDATA[2] |          |          |          |            | 0    | <b>PWM1[4]</b> — Pulse Width Modulator 1, channel 4 output.                                                                                                               |  |  |  |

|                       |          |          |          |            | I    | <b>DCD1</b> — Data Carrier Detect input for UART1.                                                                                                                        |  |  |  |

|                       |          |          |          |            | 0    | TRACEDATA[2] — Trace data, bit 2.                                                                                                                                         |  |  |  |

| P2[4]/PWM1[5]/        | 69       | D9       | J3       | [1]        | I/O  | P2[4] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

| DSR1/<br>TRACEDATA[1] |          |          |          |            | 0    | <b>PWM1[5]</b> — Pulse Width Modulator 1, channel 5 output.                                                                                                               |  |  |  |

|                       |          |          |          |            | I    | DSR1 — Data Set Ready input for UART1.                                                                                                                                    |  |  |  |

|                       |          |          |          |            | 0    | TRACEDATA[1] — Trace data, bit 1.                                                                                                                                         |  |  |  |

| P2[5]/PWM1[6]/        | 68       | D10      | H4       | [1]        | I/O  | P2[5] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

| DTR1/<br>TRACEDATA[0] |          |          |          |            | 0    | <b>PWM1[6]</b> — Pulse Width Modulator 1, channel 6 output.                                                                                                               |  |  |  |

|                       |          |          |          |            | 0    | <b>DTR1</b> — Data Terminal Ready output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal.                                                  |  |  |  |

|                       |          |          |          |            | 0    | TRACEDATA[0] — Trace data, bit 0.                                                                                                                                         |  |  |  |

| P2[6]/PCAP1[0]/       | 67       | E8       | K4       | [1]        | I/O  | P2[6] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

| RI1/TRACECLK          |          |          |          |            | I    | PCAP1[0] — Capture input for PWM1, channel 0.                                                                                                                             |  |  |  |

|                       |          |          |          |            | I    | <b>RI1</b> — Ring Indicator input for UART1.                                                                                                                              |  |  |  |

|                       |          |          |          |            | 0    | TRACECLK — Trace Clock.                                                                                                                                                   |  |  |  |

| P2[7]/RD2/            | 66       | E9       | J4       | [1]        | I/O  | P2[7] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

| RTS1                  |          |          |          |            | I    | RD2 — CAN2 receiver input. (LPC1769/68/66/65/64 only).                                                                                                                    |  |  |  |

|                       |          |          |          |            | 0    | <b>RTS1</b> — Request to Send output for UART1. Can also be configured to be an RS-485/EIA-485 output enable signal.                                                      |  |  |  |

| P2[8]/TD2/            | 65       | E10      | H5       | [1]        | I/O  | P2[8] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

| TXD2                  |          |          |          |            | 0    | TD2 — CAN2 transmitter output. (LPC1769/68/66/65/64 only).                                                                                                                |  |  |  |

|                       |          |          |          |            | 0    | TXD2 — Transmitter output for UART2.                                                                                                                                      |  |  |  |

| P2[9]/                | 64       | F7       | K5       | <u>[1]</u> | I/O  | P2[9] — General purpose digital input/output pin.                                                                                                                         |  |  |  |

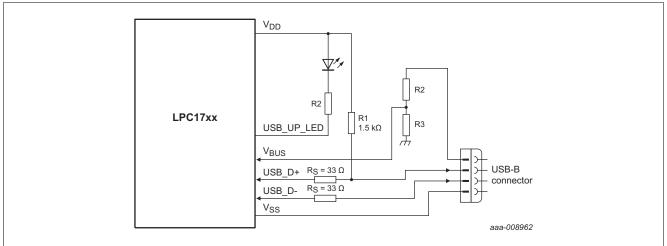

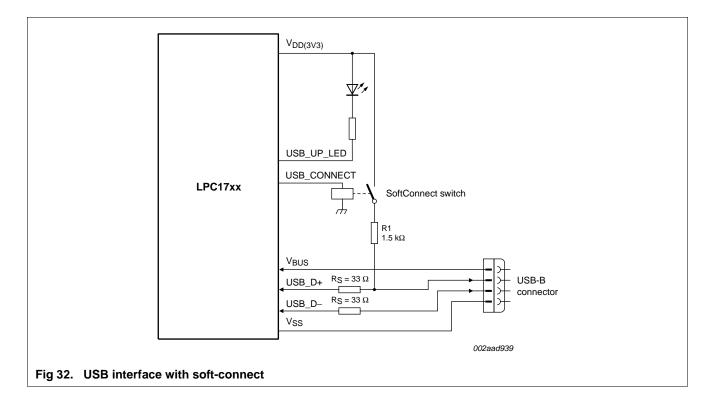

| USB_CONNECT/<br>RXD2  |          |          |          |            | 0    | <b>USB_CONNECT</b> — Signal used to switch an external 1.5 k $\Omega$ resistor under software control. Used with the SoftConnect USB feature. (LPC1769/68/66/65/64 only). |  |  |  |

|                       |          |          |          |            | I    | <b>RXD2</b> — Receiver input for UART2.                                                                                                                                   |  |  |  |

| P2[10]/EINT0/NMI      | 53       | J10      | K9       | [6]        | I/O  | <b>P2[10]</b> — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler.                                            |  |  |  |

|                       |          |          |          |            | I    | EINT0 — External interrupt 0 input.                                                                                                                                       |  |  |  |

|                       |          |          |          |            | I    | NMI — Non-maskable interrupt input.                                                                                                                                       |  |  |  |

# 8.7 Nested Vectored Interrupt Controller (NVIC)

The NVIC is an integral part of the Cortex-M3. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

### 8.7.1 Features

- Controls system exceptions and peripheral interrupts

- In the LPC17xx, the NVIC supports 33 vectored interrupts

- 32 programmable interrupt priority levels, with hardware priority level masking

- Relocatable vector table

- Non-Maskable Interrupt (NMI)

- Software interrupt generation

#### 8.7.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

Any pin on Port 0 and Port 2 (total of 42 pins) regardless of the selected function, can be programmed to generate an interrupt on a rising edge, a falling edge, or both.

## 8.8 Pin connect block

The pin connect block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on-chip peripherals.

Peripherals should be connected to the appropriate pins prior to being activated and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

Most pins can also be configured as open-drain outputs or to have a pull-up, pull-down, or no resistor enabled.

## 8.9 General purpose DMA controller

The GPDMA is an AMBA AHB compliant peripheral allowing selected peripherals to have DMA support.

The GPDMA enables peripheral-to-memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory transactions. The source and destination areas can each be either a memory region or a peripheral, and can be accessed through the AHB master. The GPDMA controller allows data transfers between the USB and Ethernet controllers and the various on-chip SRAM areas. The supported APB peripherals are SSP0/1, all UARTs, the I<sup>2</sup>S-bus interface, the ADC, and the DAC. Two match signals for each timer can be used to trigger DMA transfers.

**Remark:** The Ethernet controller is available on parts LPC1769/68/67/66/64. The USB controller is available on parts LPC1769/68/66/65/64. The I<sup>2</sup>S-bus interface is available on parts LPC1769/68/67/66/65. The DAC is available on parts LPC1769/68/67/66/65/63.

## 8.9.1 Features

- Eight DMA channels. Each channel can support an unidirectional transfer.

- 16 DMA request lines.

- Single DMA and burst DMA request signals. Each peripheral connected to the DMA Controller can assert either a burst DMA request or a single DMA request. The DMA burst size is set by programming the DMA Controller.

- Memory-to-memory, memory-to-peripheral, peripheral-to-memory, and peripheral-to-peripheral transfers are supported.

- Scatter or gather DMA is supported through the use of linked lists. This means that the source and destination areas do not have to occupy contiguous areas of memory.

- Hardware DMA channel priority.

- AHB slave DMA programming interface. The DMA Controller is programmed by writing to the DMA control registers over the AHB slave interface.

- One AHB bus master for transferring data. The interface transfers data when a DMA request goes active.

- 32-bit AHB master bus width.

- Incrementing or non-incrementing addressing for source and destination.

- Programmable DMA burst size. The DMA burst size can be programmed to more efficiently transfer data.

- Internal four-word FIFO per channel.

- Supports 8, 16, and 32-bit wide transactions.

- Big-endian and little-endian support. The DMA Controller defaults to little-endian mode on reset.

- An interrupt to the processor can be generated on a DMA completion or when a DMA error has occurred.

- Raw interrupt status. The DMA error and DMA count raw interrupt status can be read prior to masking.

# 8.10 Fast general purpose parallel I/O

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Separate registers allow setting or clearing any number of outputs simultaneously. The value of the output register may be read back as well as the current state of the port pins.

LPC17xx use accelerated GPIO functions:

- GPIO registers are accessed through the AHB multilayer bus so that the fastest possible I/O timing can be achieved.

- Mask registers allow treating sets of port bits as a group, leaving other bits unchanged.

- All GPIO registers are byte and half-word addressable.

- Entire port value can be written in one instruction.

- Support for Cortex-M3 bit banding.

- Support for use with the GPDMA controller.

- Supports single edge controlled and/or double edge controlled PWM outputs. Single edge controlled PWM outputs all go high at the beginning of each cycle unless the output is a constant low. Double edge controlled PWM outputs can have either edge occur at any position within a cycle. This allows for both positive going and negative going pulses.

- Pulse period and width can be any number of timer counts. This allows complete flexibility in the trade-off between resolution and repetition rate. All PWM outputs will occur at the same repetition rate.

- Double edge controlled PWM outputs can be programmed to be either positive going or negative going pulses.

- Match register updates are synchronized with pulse outputs to prevent generation of erroneous pulses. Software must 'release' new match values before they can become effective.

- May be used as a standard 32-bit timer/counter with a programmable 32-bit prescaler if the PWM mode is not enabled.

### 8.23 Motor control PWM

The motor control PWM is a specialized PWM supporting 3-phase motors and other combinations. Feedback inputs are provided to automatically sense rotor position and use that information to ramp speed up or down. An abort input is also provided that causes the PWM to immediately release all motor drive outputs. At the same time, the motor control PWM is highly configurable for other generalized timing, counting, capture, and compare applications.

# 8.24 Quadrature Encoder Interface (QEI)

A quadrature encoder, also known as a 2-channel incremental encoder, converts angular displacement into two pulse signals. By monitoring both the number of pulses and the relative phase of the two signals, the user can track the position, direction of rotation, and velocity. In addition, a third channel, or index signal, can be used to reset the position counter. The quadrature encoder interface decodes the digital pulses from a quadrature encoder wheel to integrate position over time and determine direction of rotation. In addition, the QEI can capture the velocity of the encoder wheel.

## 8.24.1 Features

- Tracks encoder position.

- Increments/decrements depending on direction.

- Programmable for 2× or 4× position counting.

- Velocity capture using built-in timer.

- Velocity compare function with "less than" interrupt.

- Uses 32-bit registers for position and velocity.

- Three position compare registers with interrupts.

- Index counter for revolution counting.

- Index compare register with interrupts.

- Can combine index and position interrupts to produce an interrupt for whole and partial revolution displacement.

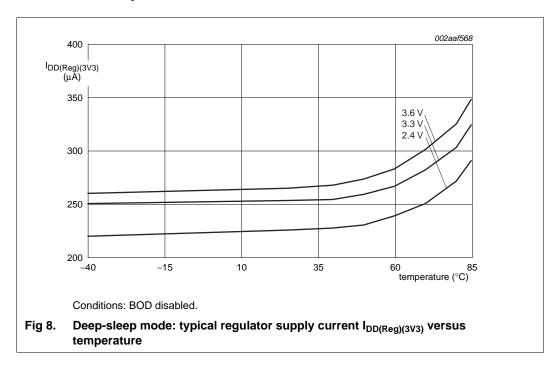

The Deep-sleep mode can be terminated and normal operation resumed by either a Reset or certain specific interrupts that are able to function without clocks. Since all dynamic operation of the chip is suspended, Deep-sleep mode reduces chip power consumption to a very low value. Power to the flash memory is left on in Deep-sleep mode, allowing a very quick wake-up.

On wake-up from Deep-sleep mode, the code execution and peripherals activities will resume after 4 cycles expire if the IRC was used before entering Deep-sleep mode. If the main external oscillator was used, the code execution will resume when 4096 cycles expire. PLL and clock dividers need to be reconfigured accordingly.

#### 8.29.6.3 Power-down mode

Power-down mode does everything that Deep-sleep mode does, but also turns off the power to the IRC oscillator and the flash memory. This saves more power but requires waiting for resumption of flash operation before execution of code or data access in the flash memory can be accomplished.

On the wake-up of Power-down mode, if the IRC was used before entering Power-down mode, it will take IRC 60  $\mu$ s to start-up. After this 4 IRC cycles will expire before the code execution can then be resumed if the code was running from SRAM. In the meantime, the flash wake-up timer then counts 4 MHz IRC clock cycles to make the 100  $\mu$ s flash start-up time. When it times out, access to the flash will be allowed. Users need to reconfigure the PLL and clock dividers accordingly.

#### 8.29.6.4 Deep power-down mode

The Deep power-down mode can only be entered from the RTC block. In Deep power-down mode, power is shut off to the entire chip with the exception of the RTC module and the RESET pin.

The LPC17xx can wake up from Deep power-down mode via the RESET pin or an alarm match event of the RTC.

#### 8.29.6.5 Wake-up interrupt controller

The Wake-up Interrupt Controller (WIC) allows the CPU to automatically wake up from any enabled priority interrupt that can occur while the clocks are stopped in Deep sleep, Power-down, and Deep power-down modes.

The WIC works in connection with the Nested Vectored Interrupt Controller (NVIC). When the CPU enters Deep sleep, Power-down, or Deep power-down mode, the NVIC sends a mask of the current interrupt situation to the WIC. This mask includes all of the interrupts that are both enabled and of sufficient priority to be serviced immediately. With this information, the WIC simply notices when one of the interrupts has occurred and then it wakes up the CPU.

The WIC eliminates the need to periodically wake up the CPU and poll the interrupts resulting in additional power savings.

### 8.29.7 Peripheral power control

A Power Control for Peripherals feature allows individual peripherals to be turned off if they are not needed in the application, resulting in additional power savings.

# 8.30 System control

### 8.30.1 Reset

Reset has four sources on the LPC17xx: the RESET pin, the Watchdog reset, power-on reset (POR), and the BrownOut Detection (BOD) circuit. The RESET pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once the operating voltage attains a usable level, causes the RSTOUT pin to go LOW and starts the wake-up timer (see description in Section 8.29.5). The wake-up timer ensures that reset remains asserted until the external Reset is de-asserted, the oscillator is running, a fixed number of clocks have passed, and the flash controller has completed its initialization. Once reset is de-asserted, or, in case of a BOD-triggered reset, once the voltage rises above the BOD threshold, the RSTOUT pin goes HIGH.

When the internal Reset is removed, the processor begins executing at address 0, which is initially the Reset vector mapped from the Boot Block. At that point, all of the processor and peripheral registers have been initialized to predetermined values.

LPC1769\_68\_67\_66\_65\_64\_63

#### Table 8. Static characteristics ...continued

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol                    | Parameter                                                                   | Conditions                                           | Min     | Typ <u>[1]</u>          | Max                                                       | Unit                    |    |

|---------------------------|-----------------------------------------------------------------------------|------------------------------------------------------|---------|-------------------------|-----------------------------------------------------------|-------------------------|----|

| I <sup>2</sup> C-bus pins | 6 (P0[27] and P0[28])                                                       |                                                      |         |                         |                                                           |                         |    |

| V <sub>IH</sub>           | HIGH-level input<br>voltage                                                 |                                                      |         | 0.7V <sub>DD(3V3)</sub> | -                                                         | -                       | V  |

| V <sub>IL</sub>           | LOW-level input voltage                                                     |                                                      |         | -                       | -                                                         | 0.3V <sub>DD(3V3)</sub> | V  |

| V <sub>hys</sub>          | hysteresis voltage                                                          |                                                      |         | -                       | $\begin{array}{l} 0.05 \times \\ V_{DD(3V3)} \end{array}$ | -                       | V  |

| V <sub>OL</sub>           | LOW-level output voltage                                                    | I <sub>OLS</sub> = 3 mA                              |         | -                       | -                                                         | 0.4                     | V  |

| I <sub>LI</sub>           | input leakage current                                                       | $V_{I} = V_{DD(3V3)}$                                | [24]    | -                       | 2                                                         | 4                       | μA |

|                           |                                                                             | V <sub>I</sub> = 5 V                                 |         | -                       | 10                                                        | 22                      | μA |

| Oscillator pi             | ins                                                                         |                                                      |         |                         |                                                           |                         |    |

| V <sub>i(XTAL1)</sub>     | input voltage on pin<br>XTAL1                                               |                                                      |         | -0.5                    | 1.8                                                       | 1.95                    | V  |

| V <sub>o(XTAL2)</sub>     | output voltage on pin<br>XTAL2                                              |                                                      |         | -0.5                    | 1.8                                                       | 1.95                    | V  |

| V <sub>i(RTCX1)</sub>     | input voltage on pin<br>RTCX1                                               |                                                      |         | -0.5                    | -                                                         | 3.6                     | V  |

| V <sub>o(RTCX2)</sub>     | output voltage on pin<br>RTCX2                                              |                                                      |         | -0.5                    | -                                                         | 3.6                     | V  |

| USB pins (L               | PC1769/68/66/65/64 only)                                                    |                                                      | 1       |                         |                                                           | L                       | 1  |

| I <sub>OZ</sub>           | OFF-state output<br>current                                                 | 0 V < V <sub>I</sub> < 3.3 V                         | [2]     | -                       | -                                                         | ±10                     | μA |

| V <sub>BUS</sub>          | bus supply voltage                                                          |                                                      | [2]     | -                       | -                                                         | 5.25                    | V  |

| V <sub>DI</sub>           | differential input sensitivity voltage                                      | (D+) – (D–)                                          | [2]     | 0.2                     | -                                                         | -                       | V  |

| V <sub>CM</sub>           | differential common<br>mode voltage range                                   | includes V <sub>DI</sub> range                       | [2]     | 0.8                     | -                                                         | 2.5                     | V  |

| V <sub>th(rs)se</sub>     | single-ended receiver<br>switching threshold<br>voltage                     |                                                      | [2]     | 0.8                     | -                                                         | 2.0                     | V  |

| V <sub>OL</sub>           | LOW-level output<br>voltage for<br>low-/full-speed                          | $R_L$ of 1.5 k $\Omega$ to 3.6 V                     | [2]     | -                       | -                                                         | 0.18                    | V  |

| V <sub>OH</sub>           | HIGH-level output<br>voltage (driven) for<br>low-/full-speed                | $R_L$ of 15 k $\Omega$ to GND                        | [2]     | 2.8                     | -                                                         | 3.5                     | V  |

| C <sub>trans</sub>        | transceiver capacitance                                                     | pin to GND                                           | [2]     | -                       | -                                                         | 20                      | pF |

| Z <sub>DRV</sub>          | driver output<br>impedance for driver<br>which is not high-speed<br>capable | with 33 $\Omega$ series resistor; steady state drive | [2][25] | 36                      | -                                                         | 44.1                    | Ω  |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] For USB operation 3.0 V  $\leq$  V\_{DD((3V3)}  $\leq$  3.6 V. Guaranteed by design.

[3]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

[4]  $V_{DDA}$  for DAC specs are from 2.7 V to 3.6 V.

#### 32-bit ARM Cortex-M3 microcontroller

- [5] The RTC typically fails when V<sub>i(VBAT)</sub> drops below 1.6 V.

- [6] V<sub>DD(REG)(3V3)</sub> = 3.3 V; T<sub>amb</sub> = 25 °C for all power consumption measurements.

- [7] Applies to LPC1768/67/66/65/64/63.

- [8] Applies to LPC1769 only.

- [9] IRC running at 4 MHz; main oscillator and PLL disabled; PCLK = CCLK/8.

- [10] BOD disabled.

- [11] On pin V<sub>DD(REG)(3V3)</sub>. I<sub>BAT</sub> = 530 nA. V<sub>DD(REG)(3V3)</sub> = 3.0 V; V<sub>BAT</sub> = 3.0 V; T<sub>amb</sub> = 25 °C.

- [12] On pin VBAT; I<sub>DD(REG)(3V3)</sub> = 630 nA; V<sub>DD(REG)(3V3)</sub> = 3.0 V; V<sub>BAT</sub> = 3.0 V; T<sub>amb</sub> = 25 °C.

- [13] On pin VBAT;  $V_{BAT}$  = 3.0 V;  $T_{amb}$  = 25 °C.

- [14] All internal pull-ups disabled. All pins configured as output and driven LOW. V<sub>DD(3V3)</sub> = 3.3 V; T<sub>amb</sub> = 25 °C.

- [15] TCK/SWDCLK pin needs to be externally pulled LOW.

- [16] On pin V<sub>DDA</sub>; V<sub>DDA</sub> = 3.3 V; T<sub>amb</sub> = 25 °C. The ADC is powered if the PDN bit in the AD0CR register is set to 1 and in Power-down mode of the PDN bit is set to 0.

- [17] The ADC is powered if the PDN bit in the AD0CR register is set to 1. See LPC17xx user manual UM10360\_1.

- [18] The ADC is in Power-down mode if the PDN bit in the AD0CR register is set to 0. See LPC17xx user manual UM10360\_1.

- [19]  $V_{i(VREFP)} = 3.3 V$ ;  $T_{amb} = 25 °C$ .

- [20] Including voltage on outputs in 3-state mode.

- [21] V<sub>DD(3V3)</sub> supply voltages must be present.

- [22] 3-state outputs go into 3-state mode in Deep power-down mode.

- [23] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

- [24] To  $V_{\text{SS}}.$

- [25] Includes external resistors of 33  $\Omega\pm$  1 % on D+ and D–.

### **11.1 Power consumption**

32-bit ARM Cortex-M3 microcontroller

# 13. ADC electrical characteristics

#### Table 19. ADC characteristics (full resolution)

$V_{DDA} = 2.5 \text{ V to } 3.6 \text{ V}; T_{amb} = -40 \degree \text{C to } +85 \degree \text{C}$  unless otherwise specified; ADC frequency 13 MHz; 12-bit resolution.<sup>[1]</sup>

| Symbol                | Parameter                           | Conditions |        | Min | Тур | Max              | Unit |

|-----------------------|-------------------------------------|------------|--------|-----|-----|------------------|------|

| VIA                   | analog input voltage                |            |        | 0   | -   | V <sub>DDA</sub> | V    |

| C <sub>ia</sub>       | analog input capacitance            |            |        | -   | -   | 15               | pF   |

| E <sub>D</sub>        | differential linearity error        |            | [2][3] | -   | -   | ±1               | LSB  |

| E <sub>L(adj)</sub>   | integral non-linearity              |            | [4]    | -   | -   | ±3               | LSB  |

| E <sub>O</sub>        | offset error                        |            | [5][6] | -   | -   | ±2               | LSB  |

| E <sub>G</sub>        | gain error                          |            | [7]    | -   | -   | 0.5              | %    |

| ET                    | absolute error                      |            | [8]    | -   | -   | 4                | LSB  |

| R <sub>vsi</sub>      | voltage source interface resistance |            | [9]    | -   | -   | 7.5              | kΩ   |

| f <sub>clk(ADC)</sub> | ADC clock frequency                 |            |        | -   | -   | 13               | MHz  |

| f <sub>c(ADC)</sub>   | ADC conversion frequency            |            | [10]   | -   | -   | 200              | kHz  |

[1]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

- [2] The ADC is monotonic, there are no missing codes.

- [3] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 28.

- [4] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 28</u>.

- [5] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See <u>Figure 28</u>.

- [6] ADCOFFS value (bits 7:4) = 2 in the ADTRM register. See LPC17xx user manual UM10360.

- [7] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See <u>Figure 28</u>.

- [8] The absolute error ( $E_T$ ) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve. See Figure 28.

[9] See <u>Figure 29</u>.

[10] The conversion frequency corresponds to the number of samples per second.

LPC1769\_68\_67\_66\_65\_64\_63

Fig 31. USB interface on a bus-powered device where  $V_{BUS} = 5 V$ ,  $V_{DD}$  not present

order to keep the noise coupled in via the PCB as small as possible. Also parasitics should stay as small as possible. Values of  $C_{x1}$  and  $C_{x2}$  should be chosen smaller accordingly to the increase in parasitics of the PCB layout.

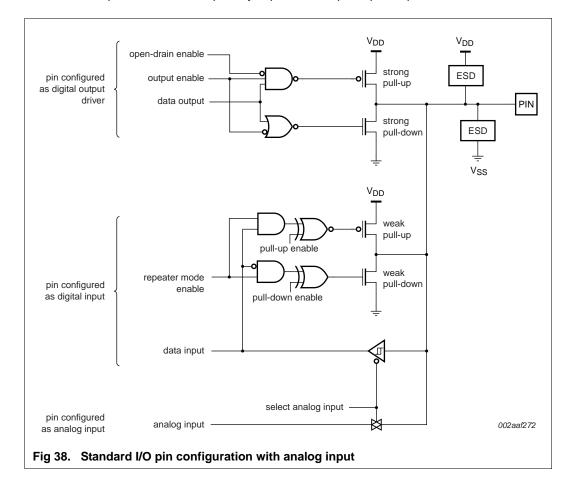

# 15.4 Standard I/O pin configuration

Figure 38 shows the possible pin modes for standard I/O pins with analog input function:

- · Digital output driver: Open-drain mode enabled/disabled

- Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- Digital input: Repeater mode enabled/disabled

- Analog input

The default configuration for standard I/O pins is input with pull-up enabled. The weak MOS devices provide a drive capability equivalent to pull-up and pull-down resistors.

32-bit ARM Cortex-M3 microcontroller

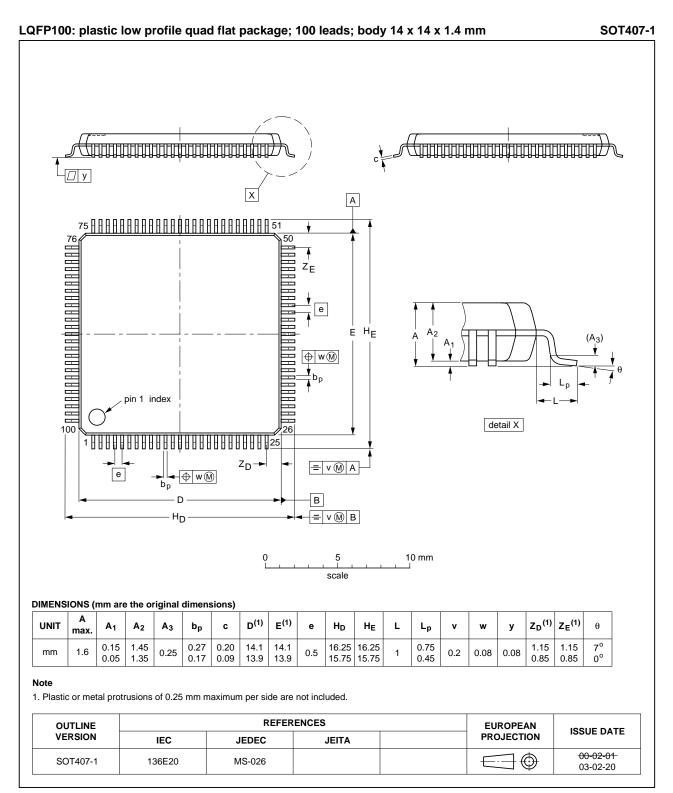

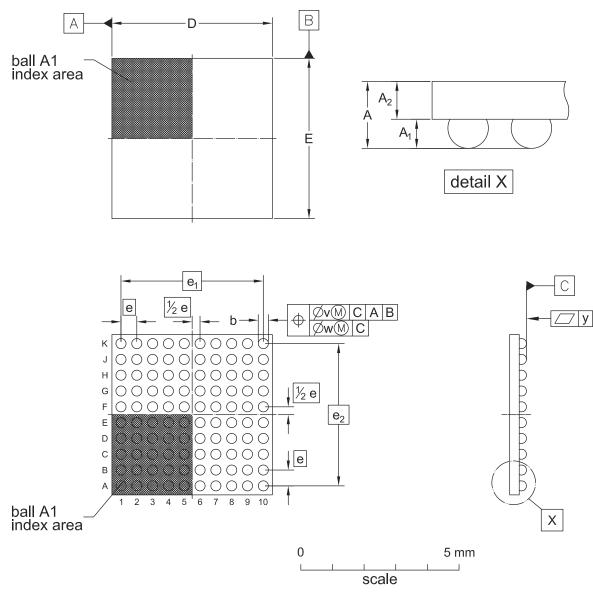

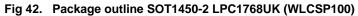

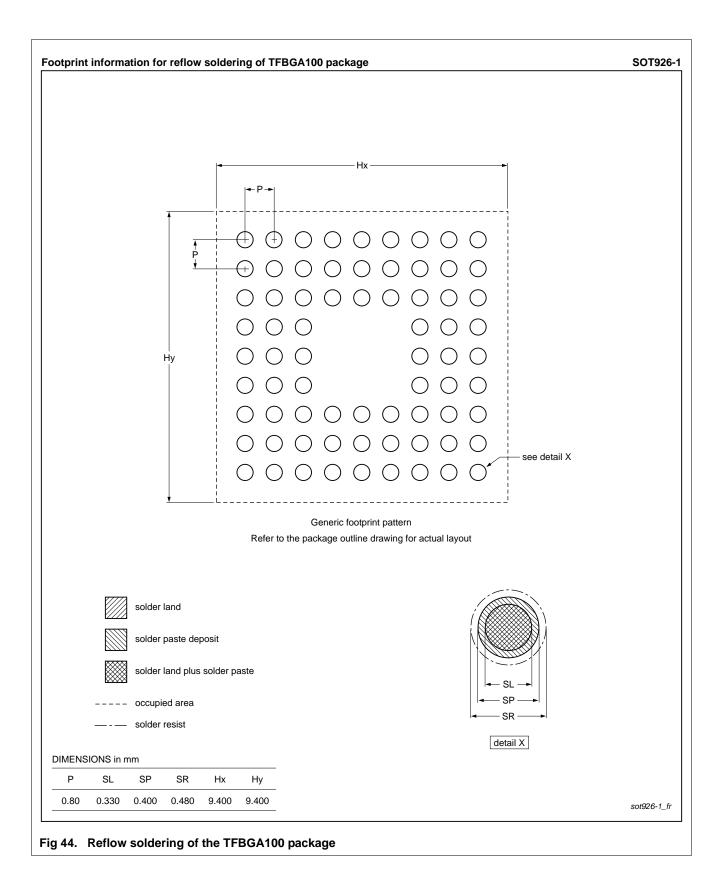

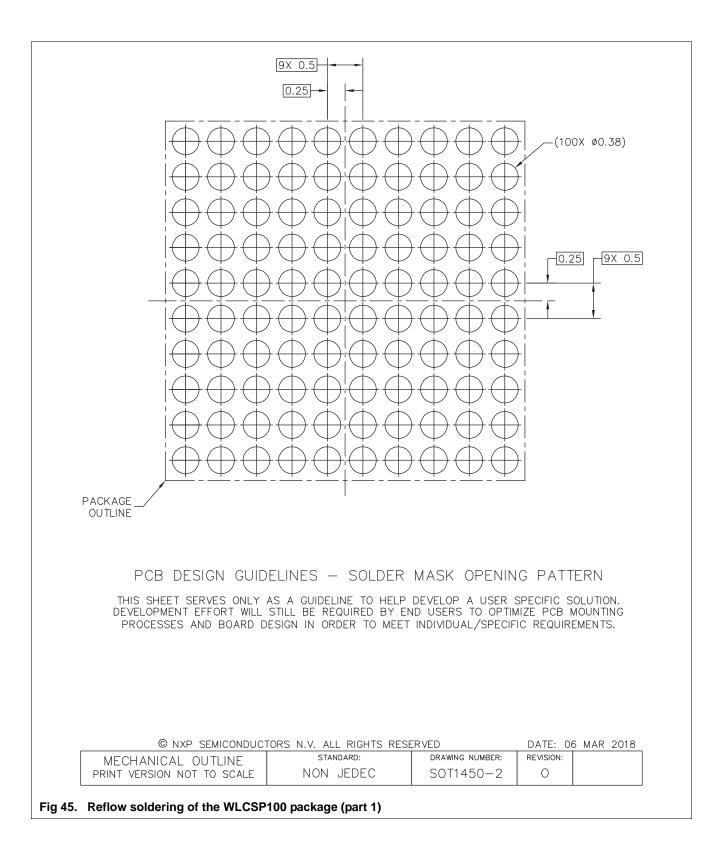

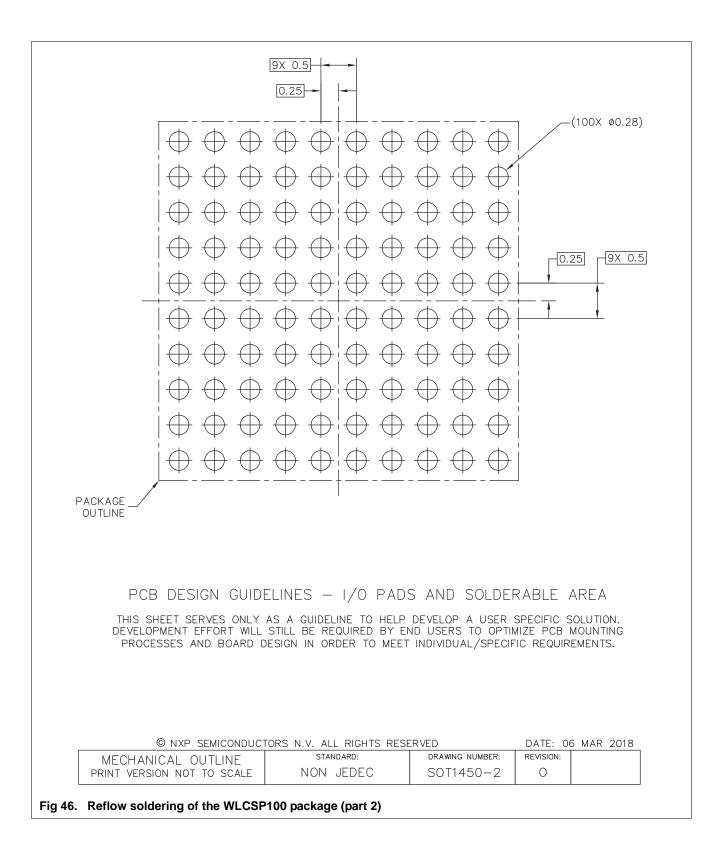

# 16. Package outline

#### Fig 40. Package outline SOT407-1 (LQFP100)

| DIMENSIONS | (mm | are the | original | dimensions | ) |

|------------|-----|---------|----------|------------|---|

|------------|-----|---------|----------|------------|---|

| UNIT |                   | А                    | A <sub>1</sub>       | $A_2$                   | b    | D                    | Е                    | е   | e <sub>1</sub> | e <sub>2</sub> | V    | W    | у    |

|------|-------------------|----------------------|----------------------|-------------------------|------|----------------------|----------------------|-----|----------------|----------------|------|------|------|

| mm   | MAX<br>NOM<br>MIN | 0.57<br>0.53<br>0.49 | 0.26<br>0.23<br>0.20 | 0.325<br>0.300<br>0.275 | 0.32 | 5.10<br>5.07<br>5.04 | 5.10<br>5.07<br>5.04 | 0.5 | 4.5            | 4.5            | 0.15 | 0.05 | 0.03 |

LPC1769\_68\_67\_66\_65\_64\_63

32-bit ARM Cortex-M3 microcontroller

LPC1769\_68\_67\_66\_65\_64\_63

| Document ID                     | Release<br>date                                                                         | Data sheet status                                      | Change<br>notice             | Supersedes                                                       |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|------------------------------------------------------------------|--|--|--|--|

| LPC1769_68_67_66_65_64_63 v.9.2 | 20131021                                                                                | Product data sheet                                     | -                            | LPC1769_68_67_66_65_64 v.9.1                                     |  |  |  |  |

| Modifications:                  |                                                                                         | 8 "Static characteristics                              | 5":                          |                                                                  |  |  |  |  |

|                                 |                                                                                         |                                                        |                              | should be tied to VDD(3V3) if the                                |  |  |  |  |

|                                 |                                                                                         | C and DAC are not us                                   |                              |                                                                  |  |  |  |  |

|                                 | – Ad                                                                                    | ded Table note 4 "VDD                                  | A for DAC spec               | cs are from 2.7 V to 3.6 V."                                     |  |  |  |  |

|                                 | – V <sub>D</sub>                                                                        | <sub>DA</sub> /VREFP spec chang                        | ed from 2.7 V to             | o 2.5 V.                                                         |  |  |  |  |

|                                 | Table                                                                                   | 19 "ADC characteristic                                 | s (full resolution           | ו)":                                                             |  |  |  |  |

|                                 |                                                                                         | ded Table note 1 "VDD<br>C and DAC are not us          |                              | should be tied to VDD(3V3) if the                                |  |  |  |  |

|                                 | – V <sub>D</sub>                                                                        | <sub>DA</sub> changed from 2.7 V                       | to 2.5 V.                    |                                                                  |  |  |  |  |

|                                 |                                                                                         |                                                        | •                            | ion)": Added Table note 1 "VDDA<br>ne ADC and DAC are not used." |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.9.1 | 20130916                                                                                | Product data sheet                                     | -                            | LPC1769_68_67_66_65_64 v.9                                       |  |  |  |  |

| Modifications:                  | Added                                                                                   | Table 7 "Thermal resi                                  | stance".                     |                                                                  |  |  |  |  |

|                                 | Table                                                                                   | 6 "Limiting values":                                   |                              |                                                                  |  |  |  |  |

|                                 | – Up                                                                                    | dated min/max values                                   | for V <sub>DD(3V3)</sub> and | d V <sub>DD(REG)(3V3)</sub> .                                    |  |  |  |  |

|                                 | – Up                                                                                    | dated conditions for V <sub>I</sub>                    |                              |                                                                  |  |  |  |  |

|                                 | <ul> <li>Updated table notes.</li> </ul>                                                |                                                        |                              |                                                                  |  |  |  |  |

|                                 |                                                                                         | 8 "Static characteristics<br>externally pulled LOW.'   |                              | note 15 "TCK/SWDCLK pin needs                                    |  |  |  |  |

|                                 | <ul> <li>Update</li> </ul>                                                              | ed Section 15.1 "Sugg                                  | ested USB inter              | rface solutions".                                                |  |  |  |  |

|                                 | <ul> <li>Addec</li> </ul>                                                               | Section 5 "Marking".                                   |                              |                                                                  |  |  |  |  |

|                                 |                                                                                         | ged title of Figure 31 fro<br>interface with soft-conr |                              | ice on a self-powered device" to                                 |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.9   | 20120810                                                                                | Product data sheet                                     | -                            | LPC1769_68_67_66_65_64 v.8                                       |  |  |  |  |

| Modifications:                  |                                                                                         | ve table note "The pea<br>num current." from Tabl      |                              | ted to 25 times the corresponding lues".                         |  |  |  |  |

|                                 | Chang                                                                                   | ge V <sub>DD(3V3)</sub> to V <sub>DD(REG)</sub>        | (3V3) in Section             | 11.3 "Internal oscillators".                                     |  |  |  |  |

|                                 | <ul> <li>Glitch filter constant changed to 10 ns in Table note 6 in Table 4.</li> </ul> |                                                        |                              |                                                                  |  |  |  |  |

|                                 | <ul> <li>Description of RESET function updated in Table 4.</li> </ul>                   |                                                        |                              |                                                                  |  |  |  |  |

|                                 | <ul> <li>Pull-up</li> </ul>                                                             | o value added for GPIC                                 | ) pins in Table 4            | 4.                                                               |  |  |  |  |

|                                 | <ul> <li>Pin co</li> </ul>                                                              | nfiguration diagram for                                | LQFP100 pacl                 | kage corrected (Figure 2).                                       |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.8   | 20111114                                                                                | Product data sheet                                     | -                            | LPC1769_68_67_66_65_64 v.7                                       |  |  |  |  |

| Modifications:                  | <ul> <li>Pin de</li> </ul>                                                              | escription of USB_UP_I                                 | LED pin update               | d in Table 4.                                                    |  |  |  |  |

|                                 |                                                                                         | d R <sub>i2</sub> labels in Figure 2                   | •                            |                                                                  |  |  |  |  |

|                                 |                                                                                         | PC1765FET100 addec                                     |                              |                                                                  |  |  |  |  |

|                                 |                                                                                         | note 10 updated in Tab                                 |                              |                                                                  |  |  |  |  |

|                                 |                                                                                         | note 1 updated in Table                                |                              |                                                                  |  |  |  |  |

|                                 |                                                                                         | escription of STCLK pin                                | -                            |                                                                  |  |  |  |  |

|                                 |                                                                                         | omagnetic compatibility                                | / data added in              | Section 14.6.                                                    |  |  |  |  |

|                                 | <ul> <li>Sectio</li> </ul>                                                              | n 16 added.                                            |                              |                                                                  |  |  |  |  |

#### Table 27. Revision history ... continued

| Document ID                   | Release<br>date                                                                                                                                                                                                             | Data sheet status                               | Change<br>notice             | Supersedes                                  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------|---------------------------------------------|--|--|--|--|

| LPC1769_68_67_66_65_64_63 v.7 | 20110405                                                                                                                                                                                                                    | Product data sheet                              | -                            | LPC1769_68_67_66_65_64 v.6                  |  |  |  |  |

| Modifications:                |                                                                                                                                                                                                                             | scription of pins P0[29<br>re not 5 V tolerant. | and P0[30] upo               | dated in Table note 5 of Table 4.           |  |  |  |  |

|                               | <ul> <li>Typica</li> </ul>                                                                                                                                                                                                  | I value for Parameter N                         | N <sub>endu</sub> added in T | able 9.                                     |  |  |  |  |

|                               | <ul> <li>Param<br/>Table 7</li> </ul>                                                                                                                                                                                       | <b>y</b> -                                      | ins: typical value           | e corrected $V_{hys} = 0.05 V_{DD(3V3)}$ in |  |  |  |  |

|                               | Condit                                                                                                                                                                                                                      | ion 3.0 V $\leq$ V <sub>DD(3V3)</sub> $\leq$ 3  | 3.6 V added in ⊺             | Table 16.                                   |  |  |  |  |

|                               | <ul> <li>Typical values for parameters I<sub>DD(REG)(3V3)</sub> and I<sub>BAT</sub> with condition Deep<br/>power-down mode corrected in Table 7 and Table note 9, Table note 10, and<br/>Table note 11 updated.</li> </ul> |                                                 |                              |                                             |  |  |  |  |

|                               | <ul> <li>For De</li> </ul>                                                                                                                                                                                                  | ep power-down mode                              | , Figure 9 updat             | ed and Figure 10 added.                     |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.6 | 20100825                                                                                                                                                                                                                    | Product data sheet                              | -                            | LPC1769_68_67_66_65_64 v.5                  |  |  |  |  |

| Modifications:                | <ul> <li>Part Ll</li> </ul>                                                                                                                                                                                                 | PC1768TFBGA added                               | •                            |                                             |  |  |  |  |

|                               | Section                                                                                                                                                                                                                     | n 7.30.2; BOD level co                          | rrected.                     |                                             |  |  |  |  |

|                               | Added                                                                                                                                                                                                                       | Section 10.2.                                   |                              |                                             |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.5 | 20100716                                                                                                                                                                                                                    | Product data sheet                              | -                            | LPC1769_68_67_66_65_64 v.4                  |  |  |  |  |

| LPC1769_68_67_66_65_64 v.4    | 20100201                                                                                                                                                                                                                    | Product data sheet                              | -                            | LPC1768_67_66_65_64 v.3                     |  |  |  |  |

| LPC1768_67_66_65_64 v.3       | 20091119                                                                                                                                                                                                                    | Product data sheet                              | -                            | LPC1768_66_65_64 v.2                        |  |  |  |  |

| LPC1768_66_65_64 v.2          | 20090211                                                                                                                                                                                                                    | Objective data sheet                            | -                            | LPC1768_66_65_64 v.1                        |  |  |  |  |

| LPC1768_66_65_64 v.1          | 20090115                                                                                                                                                                                                                    | Objective data sheet                            | -                            | -                                           |  |  |  |  |

#### Table 27. Revision history ... continued

LPC1769\_68\_67\_66\_65\_64\_63