Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Active                                                                             |

| Core Processor             | ARM® Cortex®-M3                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 100MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT    |

| Number of I/O              | 70                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 64K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                               |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TFBGA                                                                          |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1768fet100-551          |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Two/one 16 kB SRAM blocks with separate access paths for higher throughput. These SRAM blocks may be used for Ethernet, USB, and DMA memory, as well as for general purpose CPU instruction and data storage.

- Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with SSP, I<sup>2</sup>S-bus, UART, Analog-to-Digital and Digital-to-Analog converter peripherals, timer match signals, and for memory-to-memory transfers.

- Multilayer AHB matrix interconnect provides a separate bus for each AHB master. AHB masters include the CPU, General Purpose DMA controller, Ethernet MAC, and the USB interface. This interconnect provides communication with no arbitration delays.

- Split APB bus allows high throughput with few stalls between the CPU and DMA.

- Serial interfaces:

- Ethernet MAC with RMII interface and dedicated DMA controller. (Not available on all parts, see <u>Table 2</u>.)

- USB 2.0 full-speed device/Host/OTG controller with dedicated DMA controller and on-chip PHY for device, Host, and OTG functions. (Not available on all parts, see <u>Table 2</u>.)

- Four UARTs with fractional baud rate generation, internal FIFO, and DMA support. One UART has modem control I/O and RS-485/EIA-485 support, and one UART has IrDA support.

- ◆ CAN 2.0B controller with two channels. (Not available on all parts, see Table 2.)

- SPI controller with synchronous, serial, full duplex communication and programmable data length.

- Two SSP controllers with FIFO and multi-protocol capabilities. The SSP interfaces can be used with the GPDMA controller.

- Three enhanced I<sup>2</sup>C bus interfaces, one with an open-drain output supporting full I<sup>2</sup>C specification and Fast mode plus with data rates of 1 Mbit/s, two with standard port pins. Enhancements include multiple address recognition and monitor mode.

- I<sup>2</sup>S (Inter-IC Sound) interface for digital audio input or output, with fractional rate control. The I<sup>2</sup>S-bus interface can be used with the GPDMA. The I<sup>2</sup>S-bus interface supports 3-wire and 4-wire data transmit and receive as well as master clock input/output. (Not available on all parts, see Table 2.)

- Other peripherals:

- ◆ 70 (100 pin package) General Purpose I/O (GPIO) pins with configurable pull-up/down resistors. All GPIOs support a new, configurable open-drain operating mode. The GPIO block is accessed through the AHB multilayer bus for fast access and located in memory such that it supports Cortex-M3 bit banding and use by the General Purpose DMA Controller.

- ♦ 12-bit Analog-to-Digital Converter (ADC) with input multiplexing among eight pins, conversion rates up to 200 kHz, and multiple result registers. The 12-bit ADC can be used with the GPDMA controller.

- 10-bit Digital-to-Analog Converter (DAC) with dedicated conversion timer and DMA support. (Not available on all parts, see <u>Table 2</u>)

- Four general purpose timers/counters, with a total of eight capture inputs and ten compare outputs. Each timer block has an external count input. Specific timer events can be selected to generate DMA requests.

- One motor control PWM with support for three-phase motor control.

32-bit ARM Cortex-M3 microcontroller

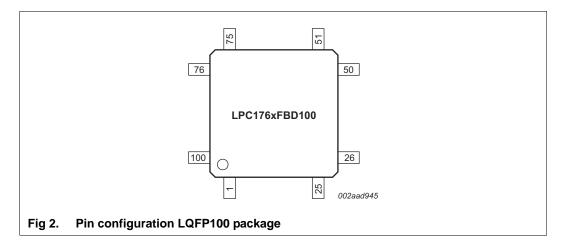

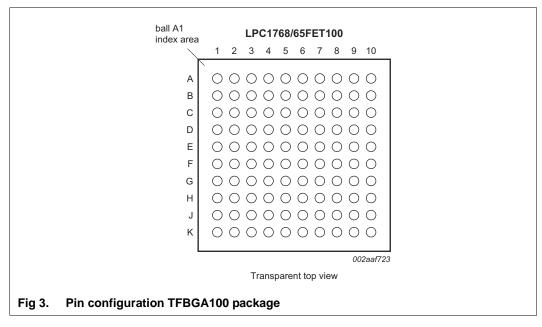

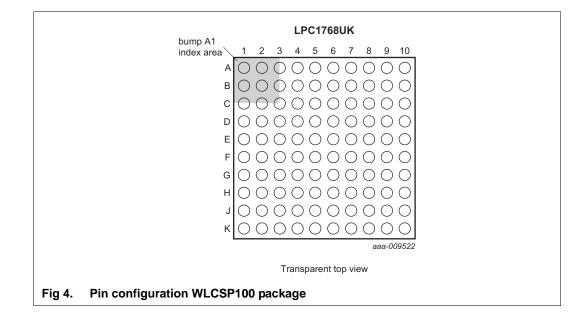

## 7. Pinning information

## 7.1 Pinning

32-bit ARM Cortex-M3 microcontroller

### Table 4. Pin allocation table TFBGA100

| Pin | Symbol                              | Pin | Symbol                              | Pin | Symbol                              | Pin | Symbol                              |

|-----|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|-----|-------------------------------------|

| Row | / A                                 |     |                                     |     |                                     |     |                                     |

| 1   | TDO/SWO                             | 2   | P0[3]/RXD0/AD0[6]                   | 3   | V <sub>DD(3V3)</sub>                | 4   | P1[4]/ENET_TX_EN                    |

| 5   | P1[10]/ENET_RXD1                    | 6   | P1[16]/ENET_MDC                     | 7   | V <sub>DD(REG)(3V3)</sub>           | 8   | P0[4]/I2SRX_CLK/<br>RD2/CAP2[0]     |

| 9   | P0[7]/I2STX_CLK/<br>SCK1/MAT2[1]    | 10  | P0[9]/I2STX_SDA/<br>MOSI1/MAT2[3]   | 11  | -                                   | 12  | -                                   |

| Row | / B                                 |     | +                                   |     | +                                   |     | -                                   |

| 1   | TMS/SWDIO                           | 2   | RTCK                                | 3   | V <sub>SS</sub>                     | 4   | P1[1]/ENET_TXD1                     |

| 5   | P1[9]/ENET_RXD0                     | 6   | P1[17]/<br>ENET_MDIO                | 7   | V <sub>SS</sub>                     | 8   | P0[6]/I2SRX_SDA/<br>SSEL1/MAT2[0]   |

| 9   | P2[0]/PWM1[1]/TXD1                  | 10  | P2[1]/PWM1[2]/RXD1                  | 11  | -                                   | 12  | -                                   |

| Row | ı C                                 |     |                                     |     |                                     |     |                                     |

| 1   | TCK/SWDCLK                          | 2   | TRST                                | 3   | TDI                                 | 4   | P0[2]/TXD0/AD0[7]                   |

| 5   | P1[8]/ENET_CRS                      | 6   | P1[15]/<br>ENET_REF_CLK             | 7   | P4[28]/RX_MCLK/<br>MAT2[0]/TXD3     | 8   | P0[8]/I2STX_WS/<br>MISO1/MAT2[2]    |

| 9   | V <sub>SS</sub>                     | 10  | V <sub>DD(3V3)</sub>                | 11  | -                                   | 12  | -                                   |

| Row | <i>i</i> D                          |     |                                     |     |                                     |     |                                     |

| 1   | P0[24]/AD0[1]/<br>I2SRX_WS/CAP3[1]  | 2   | P0[25]/AD0[2]/<br>I2SRX_SDA/TXD3    | 3   | P0[26]/AD0[3]/<br>AOUT/RXD3         | 4   | n.c.                                |

| 5   | P1[0]/ENET_TXD0                     | 6   | P1[14]/ENET_RX_ER                   | 7   | P0[5]/I2SRX_WS/<br>TD2/CAP2[1]      | 8   | P2[2]/PWM1[3]/<br>CTS1/TRACEDATA[3] |

| 9   | P2[4]/PWM1[5]/<br>DSR1/TRACEDATA[1] | 10  | P2[5]/PWM1[6]/<br>DTR1/TRACEDATA[0] | 11  | -                                   | 12  | -                                   |

| Row | ν E                                 |     | 1                                   |     | 1                                   | 1   | 1                                   |

| 1   | V <sub>SSA</sub>                    | 2   | V <sub>DDA</sub>                    | 3   | VREFP                               | 4   | n.c.                                |

| 5   | P0[23]/AD0[0]/<br>I2SRX_CLK/CAP3[0] | 6   | P4[29]/TX_MCLK/<br>MAT2[1]/RXD3     | 7   | P2[3]/PWM1[4]/<br>DCD1/TRACEDATA[2] | 8   | P2[6]/PCAP1[0]/<br>RI1/TRACECLK     |

LPC1769\_68\_67\_66\_65\_64\_63

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2018. All rights reserved.

| Table 5. | Pin description continued |  |

|----------|---------------------------|--|

|----------|---------------------------|--|

| Symbol                      | Pin/ball |          |          |            | Туре | Description                                                                                                                                                                                                      |  |  |

|-----------------------------|----------|----------|----------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                             | LQFP100  | TFBGA100 | WLCSP100 |            |      |                                                                                                                                                                                                                  |  |  |

| P0[4]/                      | 81       | A8       | G2       | <u>[1]</u> | I/O  | P0[4] — General purpose digital input/output pin.                                                                                                                                                                |  |  |

| I2SRX_CLK/<br>RD2/CAP2[0]   |          |          |          |            | I/O  | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>PS-bus specification</i> . (LPC1769/68/67/66/65/63 only).                        |  |  |

|                             |          |          |          |            | I    | RD2 — CAN2 receiver input. (LPC1769/68/66/65/64 only).                                                                                                                                                           |  |  |

|                             |          |          |          |            | I    | CAP2[0] — Capture input for Timer 2, channel 0.                                                                                                                                                                  |  |  |

| P0[5]/                      | 80       | D7       | H1       | <u>[1]</u> | I/O  | P0[5] — General purpose digital input/output pin.                                                                                                                                                                |  |  |

| I2SRX_WS/<br>TD2/CAP2[1]    |          |          |          |            | I/O  | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $PS$ -bus specification. (LPC1769/68/67/66/65/63 only).                         |  |  |

|                             |          |          |          |            | 0    | TD2 — CAN2 transmitter output. (LPC1769/68/66/65/64 only).                                                                                                                                                       |  |  |

|                             |          |          |          |            | I    | CAP2[1] — Capture input for Timer 2, channel 1.                                                                                                                                                                  |  |  |

| P0[6]/                      | 79       | B8       | G3       | <u>[1]</u> | I/O  | P0[6] — General purpose digital input/output pin.                                                                                                                                                                |  |  |

| I2SRX_SDA/<br>SSEL1/MAT2[0] |          |          |          |            | I/O  | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. (LPC1769/68/67/66/65/63 only). |  |  |

|                             |          |          |          |            | I/O  | SSEL1 — Slave Select for SSP1.                                                                                                                                                                                   |  |  |

|                             |          |          |          |            | 0    | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                                                   |  |  |

| P0[7]/                      | 78       | A9       | J1       | <u>[1]</u> | I/O  | P0[7] — General purpose digital input/output pin.                                                                                                                                                                |  |  |

| I2STX_CLK/<br>SCK1/MAT2[1]  |          |          |          |            | I/O  | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the $l^2S$ -bus specification. (LPC1769/68/67/66/65/63 only).                          |  |  |

|                             |          |          |          |            | I/O  | SCK1 — Serial Clock for SSP1.                                                                                                                                                                                    |  |  |

|                             |          |          |          |            | 0    | MAT2[1] — Match output for Timer 2, channel 1.                                                                                                                                                                   |  |  |

| P0[8]/                      | 77       | C8       | H2       | <u>[1]</u> | I/O  | P0[8] — General purpose digital input/output pin.                                                                                                                                                                |  |  |

| I2STX_WS/<br>MISO1/MAT2[2]  |          |          |          |            | I/O  | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification. (LPC1769/68/67/66/65/63 only).                      |  |  |

|                             |          |          |          |            | I/O  | MISO1 — Master In Slave Out for SSP1.                                                                                                                                                                            |  |  |

|                             |          |          |          |            | 0    | MAT2[2] — Match output for Timer 2, channel 2.                                                                                                                                                                   |  |  |

| P0[9]/                      | 76       | A10      | H3       | <u>[1]</u> | I/O  | P0[9] — General purpose digital input/output pin.                                                                                                                                                                |  |  |

| I2STX_SDA/<br>MOSI1/MAT2[3] |          |          |          |            | I/O  | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $\beta$ S-bus specification. (LPC1769/68/67/66/65/63 only).                      |  |  |

|                             |          |          |          |            | I/O  | MOSI1 — Master Out Slave In for SSP1.                                                                                                                                                                            |  |  |

|                             |          |          |          |            | 0    | MAT2[3] — Match output for Timer 2, channel 3.                                                                                                                                                                   |  |  |

| P0[10]/TXD2/                | 48       | H7       | H8       | [1]        | I/O  | P0[10] — General purpose digital input/output pin.                                                                                                                                                               |  |  |

| SDA2/MAT3[0]                |          |          |          |            | 0    | TXD2 — Transmitter output for UART2.                                                                                                                                                                             |  |  |

|                             |          |          |          |            | I/O  | <b>SDA2</b> — $I^2C^2$ data input/output (this is not an open-drain pin).                                                                                                                                        |  |  |

|                             |          |          |          |            | 0    | MAT3[0] — Match output for Timer 3, channel 0.                                                                                                                                                                   |  |  |

LPC1769\_68\_67\_66\_65\_64\_63

All information provided in this document is subject to legal disclaimers.

| Table 5. | Pin description | continued |

|----------|-----------------|-----------|

|----------|-----------------|-----------|

| Symbol          | Pin/ball |          |          |            | Туре | Description                                                                                                                                                                                                                                                     |  |  |

|-----------------|----------|----------|----------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 | LQFP100  | TFBGA100 | WLCSP100 |            |      |                                                                                                                                                                                                                                                                 |  |  |

| P2[11]/EINT1/   | 52       | H8       | J8       | <u>[6]</u> | I/O  | P2[11] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |

| I2STX_CLK       |          |          |          |            | I    | EINT1 — External interrupt 1 input.                                                                                                                                                                                                                             |  |  |

|                 |          |          |          |            | I/O  | <b>I2STX_CLK</b> — Transmit Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>I</i> <sup>2</sup> S-bus specification. (LPC1769/68/67/66/65/63 only).                                                         |  |  |

| P2[12]/EINT2/   | 51       | K10      | K10      | [6]        | I/O  | P2[12] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |

| I2STX_WS        |          |          |          |            | I    | EINT2 — External interrupt 2 input.                                                                                                                                                                                                                             |  |  |

|                 |          |          |          |            | I/O  | <b>I2STX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification. (LPC1769/68/67/66/65/63 only).                                                                     |  |  |

| P2[13]/EINT3/   | 50       | J9       | J9       | [6]        | I/O  | P2[13] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |

| I2STX_SDA       |          |          |          |            | I    | EINT3 — External interrupt 3 input.                                                                                                                                                                                                                             |  |  |

|                 |          |          |          |            | I/O  | <b>I2STX_SDA</b> — Transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $PS$ -bus specification. (LPC1769/68/67/66/65/63 only).                                                                         |  |  |

| P3[0] to P3[31] |          |          |          |            | I/O  | <b>Port 3:</b> Port 3 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 3 pins depends upon the pin function selected via the pin connect block. Pins 0 through 24, and 27 through 31 of this port are not available. |  |  |

| P3[25]/MAT0[0]/ | 27       | H3       | D8       | [1]        | I/O  | P3[25] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |

| PWM1[2]         |          |          |          |            | 0    | MAT0[0] — Match output for Timer 0, channel 0.                                                                                                                                                                                                                  |  |  |

|                 |          |          |          |            | 0    | PWM1[2] — Pulse Width Modulator 1, output 2.                                                                                                                                                                                                                    |  |  |

| P3[26]/STCLK/   | 26       | K1       | A10      | <u>[1]</u> | I/O  | P3[26] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |

| MAT0[1]/PWM1[3] |          |          |          |            | I    | <b>STCLK</b> — System tick timer clock input. The maximum STCLK frequency is 1/4 of the Arm processor clock frequency CCLK.                                                                                                                                     |  |  |

|                 |          |          |          |            | 0    | <b>MAT0[1]</b> — Match output for Timer 0, channel 1.                                                                                                                                                                                                           |  |  |

|                 |          |          |          |            | 0    | <b>PWM1[3]</b> — Pulse Width Modulator 1, output 3.                                                                                                                                                                                                             |  |  |

| P4[0] to P4[31] |          |          |          |            | I/O  | <b>Port 4:</b> Port 4 is a 32-bit I/O port with individual direction controls for each bit. The operation of port 4 pins depends upon the pin function selected via the pin connect block. Pins 0 through 27, 30, and 31 of this port are not available.        |  |  |

| P4[28]/RX_MCLK/ | 82       | C7       | G1       | <u>[1]</u> | I/O  | P4[28] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |

| MAT2[0]/TXD3    |          |          |          |            | 0    | <b>RX_MCLK</b> — I <sup>2</sup> S receive master clock. (LPC1769/68/67/66/65 only).                                                                                                                                                                             |  |  |

|                 |          |          |          |            | 0    | MAT2[0] — Match output for Timer 2, channel 0.                                                                                                                                                                                                                  |  |  |

|                 |          |          |          |            | 0    | TXD3 — Transmitter output for UART3.                                                                                                                                                                                                                            |  |  |

| P4[29]/TX_MCLK/ | 85       | E6       | F1       | <u>[1]</u> | I/O  | P4[29] — General purpose digital input/output pin.                                                                                                                                                                                                              |  |  |

| MAT2[1]/RXD3    |          |          |          |            | 0    | <b>TX_MCLK</b> — I <sup>2</sup> S transmit master clock. (LPC1769/68/67/66/65 only).                                                                                                                                                                            |  |  |

|                 |          |          |          |            | 0    | MAT2[1] — Match output for Timer 2, channel 1.                                                                                                                                                                                                                  |  |  |

|                 |          |          |          |            | 1    | <b>RXD3</b> — Receiver input for UART3.                                                                                                                                                                                                                         |  |  |

LPC1769\_68\_67\_66\_65\_64\_63

All information provided in this document is subject to legal disclaimers.

## 8.7 Nested Vectored Interrupt Controller (NVIC)

The NVIC is an integral part of the Cortex-M3. The tight coupling to the CPU allows for low interrupt latency and efficient processing of late arriving interrupts.

## 8.7.1 Features

- Controls system exceptions and peripheral interrupts

- In the LPC17xx, the NVIC supports 33 vectored interrupts

- 32 programmable interrupt priority levels, with hardware priority level masking

- Relocatable vector table

- Non-Maskable Interrupt (NMI)

- Software interrupt generation

### 8.7.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but may have several interrupt flags. Individual interrupt flags may also represent more than one interrupt source.

Any pin on Port 0 and Port 2 (total of 42 pins) regardless of the selected function, can be programmed to generate an interrupt on a rising edge, a falling edge, or both.

## 8.8 Pin connect block

The pin connect block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on-chip peripherals.

Peripherals should be connected to the appropriate pins prior to being activated and prior to any related interrupt(s) being enabled. Activity of any enabled peripheral function that is not mapped to a related pin should be considered undefined.

Most pins can also be configured as open-drain outputs or to have a pull-up, pull-down, or no resistor enabled.

## 8.9 General purpose DMA controller

The GPDMA is an AMBA AHB compliant peripheral allowing selected peripherals to have DMA support.

The GPDMA enables peripheral-to-memory, memory-to-peripheral, peripheral-to-peripheral, and memory-to-memory transactions. The source and destination areas can each be either a memory region or a peripheral, and can be accessed through the AHB master. The GPDMA controller allows data transfers between the USB and Ethernet controllers and the various on-chip SRAM areas. The supported APB peripherals are SSP0/1, all UARTs, the I<sup>2</sup>S-bus interface, the ADC, and the DAC. Two match signals for each timer can be used to trigger DMA transfers.

**Remark:** The Ethernet controller is available on parts LPC1769/68/67/66/64. The USB controller is available on parts LPC1769/68/66/65/64. The I<sup>2</sup>S-bus interface is available on parts LPC1769/68/67/66/65. The DAC is available on parts LPC1769/68/67/66/65/63.

## 8.13.1 Features

- Two CAN controllers and buses.

- Data rates to 1 Mbit/s on each bus.

- 32-bit register and RAM access.

- Compatible with CAN specification 2.0B, ISO 11898-1.

- Global Acceptance Filter recognizes standard (11-bit) and extended-frame (29-bit) receive identifiers for all CAN buses.

- Acceptance Filter can provide FullCAN-style automatic reception for selected Standard Identifiers.

- FullCAN messages can generate interrupts.

## 8.14 12-bit ADC

The LPC17xx contain a single 12-bit successive approximation ADC with eight channels and DMA support.

## 8.14.1 Features

- 12-bit successive approximation ADC.

- Input multiplexing among 8 pins.

- Power-down mode.

- Measurement range VREFN to VREFP.

- 12-bit conversion rate: 200 kHz.

- Individual channels can be selected for conversion.

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or Timer Match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

- DMA support.

## 8.15 10-bit DAC

The DAC allows to generate a variable analog output. The maximum output value of the DAC is VREFP.

Remark: The DAC is available on parts LPC1769/68/67/66/65/63. See Table 2.

## 8.15.1 Features

- 10-bit DAC

- Resistor string architecture

- Buffered output

- Power-down mode

- Selectable output drive

- Dedicated conversion timer

- DMA support

- Digital filter with programmable delays for encoder input signals.

- Can accept decoded signal inputs (clk and direction).

- Connected to APB.

## 8.25 Repetitive Interrupt (RI) timer

The repetitive interrupt timer provides a free-running 32-bit counter which is compared to a selectable value, generating an interrupt when a match occurs. Any bits of the timer/compare can be masked such that they do not contribute to the match detection. The repetitive interrupt timer can be used to create an interrupt that repeats at predetermined intervals.

### 8.25.1 Features

- 32-bit counter running from PCLK. Counter can be free-running or be reset by a generated interrupt.

- 32-bit compare value.

- 32-bit compare mask. An interrupt is generated when the counter value equals the compare value, after masking. This allows for combinations not possible with a simple compare.

## 8.26 Arm Cortex-M3 system tick timer

The Arm Cortex-M3 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a 10 ms interval. In the LPC17xx, this timer can be clocked from the internal AHB clock or from a device pin.

## 8.27 Watchdog timer

The purpose of the watchdog is to reset the microcontroller within a reasonable amount of time if it enters an erroneous state. When enabled, the watchdog will generate a system reset if the user program fails to 'feed' (or reload) the watchdog within a predetermined amount of time.

### 8.27.1 Features

- Internally resets chip if not periodically reloaded.

- Debug mode.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect/Incomplete feed sequence causes reset/interrupt if enabled.

- Flag to indicate watchdog reset.

- Programmable 32-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{32} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the Internal RC (IRC) oscillator, the RTC oscillator, or the APB peripheral clock. This gives a wide range of potential timing choices of Watchdog operation under different power reduction

conditions. It also provides the ability to run the WDT from an entirely internal source that is not dependent on an external crystal and its associated components and wiring for increased reliability.

• Includes lock/safe feature.

## 8.28 RTC and backup registers

The RTC is a set of counters for measuring time when system power is on, and optionally when it is off. The RTC on the LPC17xx is designed to have extremely low power consumption, i.e. less than 1  $\mu$ A. The RTC will typically run from the main chip power supply, conserving battery power while the rest of the device is powered up. When operating from a battery, the RTC will continue working down to 2.1 V. Battery power can be provided from a standard 3 V Lithium button cell.

An ultra-low power 32 kHz oscillator will provide a 1 Hz clock to the time counting portion of the RTC, moving most of the power consumption out of the time counting function.

The RTC includes a calibration mechanism to allow fine-tuning the count rate in a way that will provide less than 1 second per day error when operated at a constant voltage and temperature. A clock output function (see <u>Section 8.29.4</u>) makes measuring the oscillator rate easy and accurate.

The RTC contains a small set of backup registers (20 bytes) for holding data while the main part of the LPC17xx is powered off.

The RTC includes an alarm function that can wake up the LPC17xx from all reduced power modes with a time resolution of 1 s.

#### 8.28.1 Features

- Measures the passage of time to maintain a calendar and clock.

- Ultra low power design to support battery powered systems.

- Provides Seconds, Minutes, Hours, Day of Month, Month, Year, Day of Week, and Day of Year.

- Dedicated power supply pin can be connected to a battery or to the main 3.3 V.

- Periodic interrupts can be generated from increments of any field of the time registers.

- Backup registers (20 bytes) powered by VBAT.

- RTC power supply is isolated from the rest of the chip.

## 8.29 Clocking and power control

#### 8.29.1 Crystal oscillators

The LPC17xx include three independent oscillators. These are the main oscillator, the IRC oscillator, and the RTC oscillator. Each oscillator can be used for more than one purpose as required in a particular application. Any of the three clock sources can be chosen by software to drive the main PLL and ultimately the CPU.

Following reset, the LPC17xx will operate from the Internal RC oscillator until switched by software. This allows systems to operate without any external crystal and the bootloader code to operate at a known frequency.

## 8.29.2 Main PLL (PLL0)

The PLL0 accepts an input clock frequency in the range of 32 kHz to 25 MHz. The input frequency is multiplied up to a high frequency, then divided down to provide the actual clock used by the CPU and/or the USB block.

The PLL0 input, in the range of 32 kHz to 25 MHz, may initially be divided down by a value 'N', which may be in the range of 1 to 256. This input division provides a wide range of output frequencies from the same input frequency.

Following the PLL0 input divider is the PLL0 multiplier. This can multiply the input divider output through the use of a Current Controlled Oscillator (CCO) by a value 'M', in the range of 1 through 32768. The resulting frequency must be in the range of 275 MHz to 550 MHz. The multiplier works by dividing the CCO output by the value of M, then using a phase-frequency detector to compare the divided CCO output to the multiplier input. The error value is used to adjust the CCO frequency.

The PLL0 is turned off and bypassed following a chip Reset and by entering Power-down mode. PLL0 is enabled by software only. The program must configure and activate the PLL0, wait for the PLL0 to lock, and then connect to the PLL0 as a clock source.

## 8.29.3 USB PLL (PLL1)

The LPC17xx contain a second, dedicated USB PLL1 to provide clocking for the USB interface.

The PLL1 receives its clock input from the main oscillator only and provides a fixed 48 MHz clock to the USB block only. The PLL1 is disabled and powered off on reset. If the PLL1 is left disabled, the USB clock will be supplied by the 48 MHz clock from the main PLL0.

The PLL1 accepts an input clock frequency in the range of 10 MHz to 25 MHz only. The input frequency is multiplied up the range of 48 MHz for the USB clock using a Current Controlled Oscillators (CCO). It is insured that the PLL1 output has a 50 % duty cycle.

## 8.29.4 RTC clock output

The LPC17xx feature a clock output function intended for synchronizing with external devices and for use during system development to allow checking the internal clocks CCLK, IRC clock, main crystal, RTC clock, and USB clock in the outside world. The RTC clock output allows tuning the RTC frequency without probing the pin, which would distort the results.

#### 8.29.5 Wake-up timer

The LPC17xx begin operation at power-up and when awakened from Power-down mode by using the 4 MHz IRC oscillator as the clock source. This allows chip operation to resume quickly. If the main oscillator or the PLL is needed by the application, software will need to enable these features and wait for them to stabilize before they are used as a clock source.

When the main oscillator is initially activated, the wake-up timer allows software to ensure that the main oscillator is fully functional before the processor uses it as a clock source and starts to execute instructions. This is important at power on, all types of Reset, and

## 11. Static characteristics

#### Table 8.Static characteristics

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

| Symbol                    | Parameter                        | Conditions                                                                                                        |               | Min | Typ[1] | Max              | Unit |

|---------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------|-----|--------|------------------|------|

| Supply pins               |                                  |                                                                                                                   | 1             |     |        |                  |      |

| V <sub>DD(3V3)</sub>      | supply voltage (3.3 V)           | external rail                                                                                                     | [2]           | 2.4 | 3.3    | 3.6              | V    |

| V <sub>DD(REG)(3V3)</sub> | regulator supply voltage (3.3 V) |                                                                                                                   |               | 2.4 | 3.3    | 3.6              | V    |

| V <sub>DDA</sub>          | analog 3.3 V pad supply voltage  |                                                                                                                   | [3][4]        | 2.5 | 3.3    | 3.6              | V    |

| V <sub>i(VBAT)</sub>      | input voltage on pin<br>VBAT     |                                                                                                                   | <u>[5]</u>    | 2.1 | 3.3    | 3.6              | V    |

| V <sub>i(VREFP)</sub>     | input voltage on pin<br>VREFP    |                                                                                                                   | [3]           | 2.5 | 3.3    | V <sub>DDA</sub> | V    |

| I <sub>DD(REG)(3V3)</sub> | regulator supply current (3.3 V) | active mode; code<br>while(1){}<br>executed from flash; all<br>peripherals disabled;<br>PCLK = CCLK/ <sub>8</sub> |               |     |        |                  |      |

|                           |                                  | CCLK = 12 MHz; PLL<br>disabled                                                                                    | <u>[6][7]</u> | -   | 7      | -                | mA   |

|                           |                                  | CCLK = 100 MHz; PLL<br>enabled                                                                                    | <u>[6][7]</u> | -   | 42     | -                | mA   |

|                           |                                  | CCLK = 100 MHz; PLL<br>enabled (LPC1769)                                                                          | <u>[6][8]</u> | -   | 50     | -                | mA   |

|                           |                                  | CCLK = 120 MHz; PLL<br>enabled (LPC1769)                                                                          | [6][8]        | -   | 67     | -                | mA   |

|                           |                                  | sleep mode                                                                                                        | [6][9]        | -   | 2      | -                | mA   |

|                           |                                  | deep sleep mode                                                                                                   | [6][10]       | -   | 240    | -                | μA   |

|                           |                                  | power-down mode                                                                                                   | [6][10]       | -   | 31     | -                | μA   |

|                           |                                  | deep power-down mode;<br>RTC running                                                                              | [11]          | -   | 630    | -                | nA   |

| I <sub>BAT</sub>          | battery supply current           | deep power-down mode;<br>RTC running                                                                              |               |     |        |                  |      |

|                           |                                  | V <sub>DD(REG)(3V3)</sub> present                                                                                 | [12]          | -   | 530    | -                | nA   |

|                           |                                  | V <sub>DD(REG)(3V3)</sub> not<br>present                                                                          | [13]          | -   | 1.1    | -                | μA   |

| I <sub>DD(IO)</sub>       | I/O supply current               | deep sleep mode                                                                                                   | [14][15]      | -   | 40     | -                | nA   |

|                           |                                  | power-down mode                                                                                                   | [14][15]      | -   | 40     | -                | nA   |

|                           |                                  | deep power-down mode                                                                                              | [14]          | -   | 10     | -                | nA   |

#### Table 8. Static characteristics ...continued

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol                    | Parameter                                                                   | Conditions                                           |         | Min                     | Typ <u>[1]</u>            | Max                     | Unit |

|---------------------------|-----------------------------------------------------------------------------|------------------------------------------------------|---------|-------------------------|---------------------------|-------------------------|------|

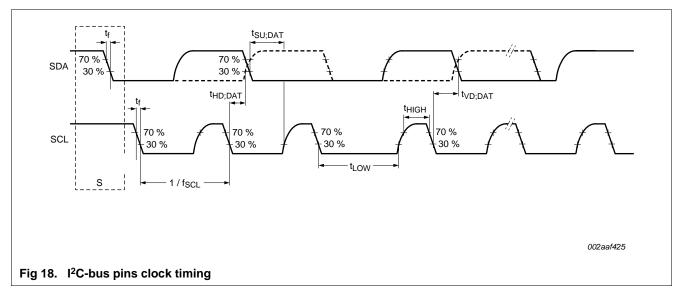

| I <sup>2</sup> C-bus pins | (P0[27] and P0[28])                                                         |                                                      | 1       | ľ                       |                           |                         |      |

| V <sub>IH</sub>           | HIGH-level input voltage                                                    |                                                      |         | 0.7V <sub>DD(3V3)</sub> | -                         | -                       | V    |

| V <sub>IL</sub>           | LOW-level input voltage                                                     |                                                      |         | -                       | -                         | 0.3V <sub>DD(3V3)</sub> | V    |

| V <sub>hys</sub>          | hysteresis voltage                                                          |                                                      |         | -                       | $0.05 \times V_{DD(3V3)}$ | -                       | V    |

| V <sub>OL</sub>           | LOW-level output voltage                                                    | I <sub>OLS</sub> = 3 mA                              |         | -                       | -                         | 0.4                     | V    |

| ILI                       | input leakage current                                                       | $V_{I} = V_{DD(3V3)}$                                | [24]    | -                       | 2                         | 4                       | μA   |

|                           |                                                                             | V <sub>1</sub> = 5 V                                 |         | -                       | 10                        | 22                      | μA   |

| Oscillator pi             |                                                                             | Γ                                                    | 1       | 1                       |                           |                         |      |

| V <sub>i(XTAL1)</sub>     | input voltage on pin<br>XTAL1                                               |                                                      |         | -0.5                    | 1.8                       | 1.95                    | V    |

| V <sub>o(XTAL2)</sub>     | output voltage on pin<br>XTAL2                                              |                                                      |         | -0.5                    | 1.8                       | 1.95                    | V    |

| V <sub>i(RTCX1)</sub>     | input voltage on pin<br>RTCX1                                               |                                                      |         | -0.5                    | -                         | 3.6                     | V    |

| V <sub>o(RTCX2)</sub>     | output voltage on pin<br>RTCX2                                              |                                                      |         | -0.5                    | -                         | 3.6                     | V    |

| USB pins (L               | PC1769/68/66/65/64 only)                                                    | I                                                    |         |                         | 1                         |                         |      |

| I <sub>OZ</sub>           | OFF-state output<br>current                                                 | 0 V < V <sub>I</sub> < 3.3 V                         | [2]     | -                       | -                         | ±10                     | μΑ   |

| V <sub>BUS</sub>          | bus supply voltage                                                          |                                                      | [2]     | -                       | -                         | 5.25                    | V    |

| V <sub>DI</sub>           | differential input sensitivity voltage                                      | (D+) – (D–)                                          | [2]     | 0.2                     | -                         | -                       | V    |

| V <sub>CM</sub>           | differential common<br>mode voltage range                                   | includes V <sub>DI</sub> range                       | [2]     | 0.8                     | -                         | 2.5                     | V    |

| V <sub>th(rs)se</sub>     | single-ended receiver<br>switching threshold<br>voltage                     |                                                      | [2]     | 0.8                     | -                         | 2.0                     | V    |

| V <sub>OL</sub>           | LOW-level output<br>voltage for<br>low-/full-speed                          | $R_L$ of 1.5 k $\Omega$ to 3.6 V                     | [2]     | -                       | -                         | 0.18                    | V    |

| V <sub>OH</sub>           | HIGH-level output<br>voltage (driven) for<br>low-/full-speed                | $R_L$ of 15 k $\Omega$ to GND                        | [2]     | 2.8                     | -                         | 3.5                     | V    |

| C <sub>trans</sub>        | transceiver capacitance                                                     | pin to GND                                           | [2]     | -                       | -                         | 20                      | pF   |

| Z <sub>DRV</sub>          | driver output<br>impedance for driver<br>which is not high-speed<br>capable | with 33 $\Omega$ series resistor; steady state drive | [2][25] | 36                      | -                         | 44.1                    | Ω    |

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] For USB operation 3.0 V  $\leq$  V\_{DD((3V3)}  $\leq$  3.6 V. Guaranteed by design.

[3]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

[4]  $V_{DDA}$  for DAC specs are from 2.7 V to 3.6 V.

32-bit ARM Cortex-M3 microcontroller

## 12.6 I<sup>2</sup>S-bus interface

**Remark:** The I<sup>2</sup>S-bus interface is available on parts LPC1769/68/67/66/65/63. See <u>Table 2</u>.

| Table 15. | Dynamic characteristics: I <sup>2</sup> S-bus interface pins |

|-----------|--------------------------------------------------------------|

|-----------|--------------------------------------------------------------|

$T_{amb} = -40 \degree C$  to +85  $\degree C$ .

| Symbol             | Parameter              | Conditions                      |            | Min                        | Тур | Max                       | Unit |

|--------------------|------------------------|---------------------------------|------------|----------------------------|-----|---------------------------|------|

| common             | to input and output    |                                 |            | -                          |     |                           | _    |

| t <sub>r</sub>     | rise time              |                                 | [1]        | -                          | -   | 35                        | ns   |

| t <sub>f</sub>     | fall time              |                                 | [1]        | -                          | -   | 35                        | ns   |

| t <sub>WH</sub>    | pulse width HIGH       | on pins I2STX_CLK and I2SRX_CLK | <u>[1]</u> | $0.495 \times T_{cy(clk)}$ | -   | -                         | -    |

| t <sub>WL</sub>    | pulse width LOW        | on pins I2STX_CLK and I2SRX_CLK | <u>[1]</u> | -                          | -   | $0.505 	imes T_{cy(clk)}$ | ns   |

| output             |                        |                                 |            |                            |     |                           |      |

| t <sub>v(Q)</sub>  | data output valid time | on pin I2STX_SDA                | [1]        | -                          | -   | 30                        | ns   |

|                    |                        | on pin I2STX_WS                 | [1]        | -                          | -   | 30                        | ns   |

| input              |                        |                                 |            |                            |     |                           |      |

| t <sub>su(D)</sub> | data input set-up time | on pin I2SRX_SDA                | <u>[1]</u> | 3.5                        | -   | -                         | ns   |

| t <sub>h(D)</sub>  | data input hold time   | on pin I2SRX_SDA                | [1]        | 4.0                        | -   | -                         | ns   |

[1] CCLK = 20 MHz; peripheral clock to the I<sup>2</sup>S-bus interface PCLK = <sup>CCLK</sup>/<sub>4</sub>; I<sup>2</sup>S clock cycle time T<sub>cy(clk)</sub> = 1600 ns, corresponds to the SCK signal in the I<sup>2</sup>S-bus specification.

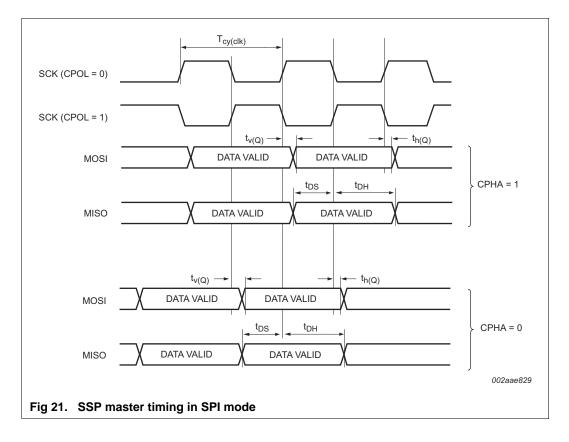

## 12.7 SSP interface

The maximum SSP speed is 33 Mbit/s in master mode or 8 Mbit/s in slave mode. In slave mode, the maximum SSP clock rate must be 1/12 of the SSP PCLK clock rate.

#### Table 16. Dynamic characteristics: SSP pins in SPI mode

$C_L = 30 \text{ pF}$  for all SSP pins;  $T_{amb} = -40 \text{ }^{\circ}C$  to 85  $\text{}^{\circ}C$ ;  $V_{DD(3V3)} = 3.3 \text{ V}$  to 3.6 V; input slew = 1 ns; sampled at 10 % and 90 % of the signal level. Values guaranteed by design.

| Symbol            | Parameter              | Conditions  | Min  | Мах                           | Unit |

|-------------------|------------------------|-------------|------|-------------------------------|------|

| SSP maste         | r                      | ŀ           |      | ŀ                             |      |

| t <sub>DS</sub>   | data set-up time       | in SPI mode | 16.1 | -                             | ns   |

| t <sub>DH</sub>   | data hold time         | in SPI mode | 0    | -                             | ns   |

| t <sub>v(Q)</sub> | data output valid time | in SPI mode | -    | 2.5                           | ns   |

| t <sub>h(Q)</sub> | data output hold time  | in SPI mode | 0    | -                             | ns   |

| SSP slave         |                        |             |      |                               |      |

| t <sub>DS</sub>   | data set-up time       | in SPI mode | 16.1 | -                             | ns   |

| t <sub>DH</sub>   | data hold time         | in SPI mode | 0    | -                             | ns   |

| t <sub>v(Q)</sub> | data output valid time | in SPI mode | -    | 3*T <sub>cy(PCLK)</sub> + 2.5 | ns   |

| t <sub>h(Q)</sub> | data output hold time  | in SPI mode | 0    | -                             | ns   |

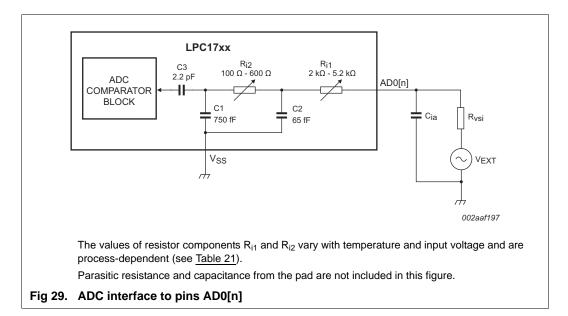

Table 21.

ADC interface components

| Component       | Range                          | Description                                                                                                |

|-----------------|--------------------------------|------------------------------------------------------------------------------------------------------------|

| R <sub>i1</sub> | 2 k $\Omega$ to 5.2 k $\Omega$ | Switch-on resistance for channel selection switch. Varies with temperature, input voltage, and process.    |

| R <sub>i2</sub> | 100 $\Omega$ to 600 $\Omega$   | Switch-on resistance for the comparator input switch. Varies with temperature, input voltage, and process. |

| C1              | 750 fF                         | Parasitic capacitance from the ADC block level.                                                            |

| C2              | 65 fF                          | Parasitic capacitance from the ADC block level.                                                            |

| C3              | 2.2 pF                         | Sampling capacitor.                                                                                        |

# 14. DAC electrical characteristics

Remark: The DAC is available on parts LPC1769/68/67/66/65/63. See Table 2.

#### Table 22. DAC electrical characteristics

$V_{DDA} = 2.7$  V to 3.6 V;  $T_{amb} = -40$  °C to +85 °C unless otherwise specified

| Symbol              | Parameter                    | Conditions |  | Min | Тур  | Max | Unit |  |  |  |

|---------------------|------------------------------|------------|--|-----|------|-----|------|--|--|--|

| E <sub>D</sub>      | differential linearity error |            |  | -   | ±1   | -   | LSB  |  |  |  |

| E <sub>L(adj)</sub> | integral non-linearity       |            |  | -   | ±1.5 | -   | LSB  |  |  |  |

| E <sub>O</sub>      | offset error                 |            |  | -   | 0.6  | -   | %    |  |  |  |

| E <sub>G</sub>      | gain error                   |            |  | -   | 0.6  | -   | %    |  |  |  |

| CL                  | load capacitance             |            |  | -   | 200  | -   | pF   |  |  |  |

| R <sub>L</sub>      | load resistance              |            |  | 1   | -    | -   | kΩ   |  |  |  |

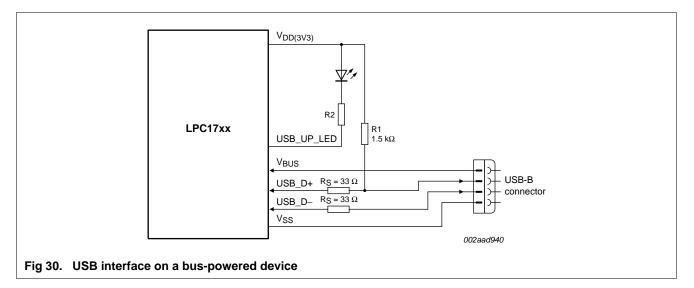

# **15.** Application information

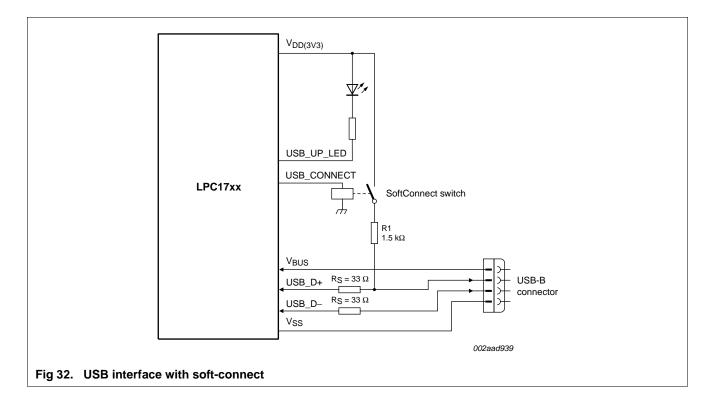

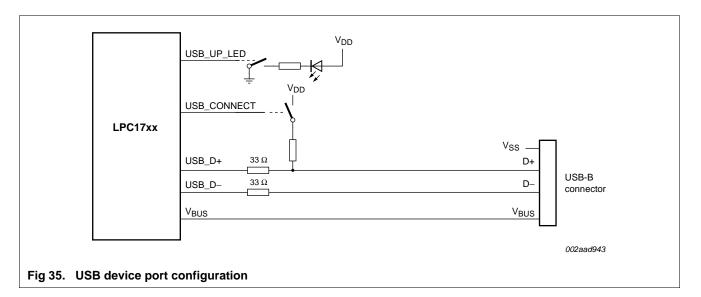

## **15.1 Suggested USB interface solutions**

**Remark:** The USB controller is available as a device/Host/OTG controller on parts LPC1769/68/66/65 and as device-only controller on part LPC1764.

If the LPC1769/68/67/66/65/64/63  $V_{DD}$  is always greater than 0 V while  $V_{BUS} = 5$  V, the  $V_{BUS}$  pin can be connected directly to the  $V_{BUS}$  pin on the USB connector.

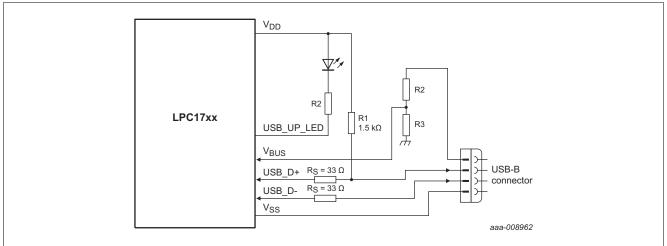

This applies to bus powered devices where the USB cable supplies the system power. For systems where  $V_{DD}$  can be 0 V and  $V_{BUS}$  is directly applied to the  $V_{BUS}$  pin, precautions must be taken to reduce the voltage to below 3.6 V.

The maximum allowable voltage on the V<sub>BUS</sub> pin is 3.6 V. One method is to use a voltage divider to connect the V<sub>BUS</sub> pin to the V<sub>BUS</sub> on the USB connector.

The voltage divider ratio should be such that the  $V_{BUS}$  pin will be greater than  $0.7V_{DD}$  to indicate a logic HIGH while below the 3.6 V allowable maximum voltage.

Use the following operating conditions:

$VBUS_{max} = 5.25 V$

$V_{DD} = 3.6 V$

The voltage divider would need to provide a reduction of 3.6 V/5.25 V or ~0.686 V.

### 32-bit ARM Cortex-M3 microcontroller

Fig 31. USB interface on a bus-powered device where  $V_{BUS} = 5 V$ ,  $V_{DD}$  not present

32-bit ARM Cortex-M3 microcontroller

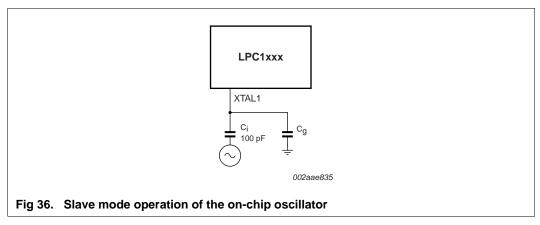

## 15.2 Crystal oscillator XTAL input and component selection

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100 \text{ pF}$ . To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV(RMS) is needed.

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF (<u>Figure 36</u>), with an amplitude between 200 mV(RMS) and 1000 mV(RMS). This corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

External components and models used in oscillation mode are shown in Figure 37 and in Table 23 and Table 24. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (the fundamental frequency is represented by L,  $C_L$  and  $R_S$ ). Capacitance  $C_P$  in Figure 37 represents the parallel package capacitance and should not be larger than 7 pF. Parameters  $F_{OSC}$ ,  $C_L$ ,  $R_S$  and  $C_P$  are supplied by the crystal manufacturer.

## 15.6 ElectroMagnetic Compatibility (EMC)

Radiated emission measurements according to the IEC61967-2 standard using the TEM-cell method are shown for part LPC1768.

# Table 25.ElectroMagnetic Compatibility (EMC) for part LPC1768 (TEM-cell method) $V_{DD} = 3.3 \text{ V}$ ; $T_{amb} = 25 \degree C$ .

| Parameter                | Frequency band         | System of            | lock = |        |         |     | Unit |

|--------------------------|------------------------|----------------------|--------|--------|---------|-----|------|

| 1                        |                        | 12 MHz 24 MHz 48 MHz |        | 72 MHz | 100 MHz |     |      |

| Input clock:             | IRC (4 MHz)            | 1                    |        |        |         |     |      |

| maximum                  | 150 kHz to 30 MHz      | -7                   | -6     | -4     | -7      | -7  | dBμV |

| peak level               | 30 MHz to 150 MHz      | +1                   | +5     | +11    | +16     | +9  | dBμV |

|                          | 150 MHz to 1 GHz       | -2                   | +4     | +11    | +12     | +19 | dBμV |

| IEC level <sup>[1]</sup> | -                      | 0                    | 0      | Ν      | М       | L   | -    |

| Input clock:             | crystal oscillator (12 | MHz)                 |        |        |         |     |      |

| maximum                  | 150 kHz to 30 MHz      | -5                   | -4     | -4     | -7      | -8  | dBμV |

| peak level               | 30 MHz to 150 MHz      | -1                   | +5     | +10    | +15     | +7  | dBμV |

|                          | 150 MHz to 1 GHz       | -1                   | +6     | +11    | +10     | +16 | dBμV |

| IEC level <sup>[1]</sup> | -                      | 0                    | 0      | N      | М       | М   | -    |

[1] IEC levels refer to Appendix D in the IEC61967-2 Specification.

LPC1769\_68\_67\_66\_65\_64\_63

32-bit ARM Cortex-M3 microcontroller

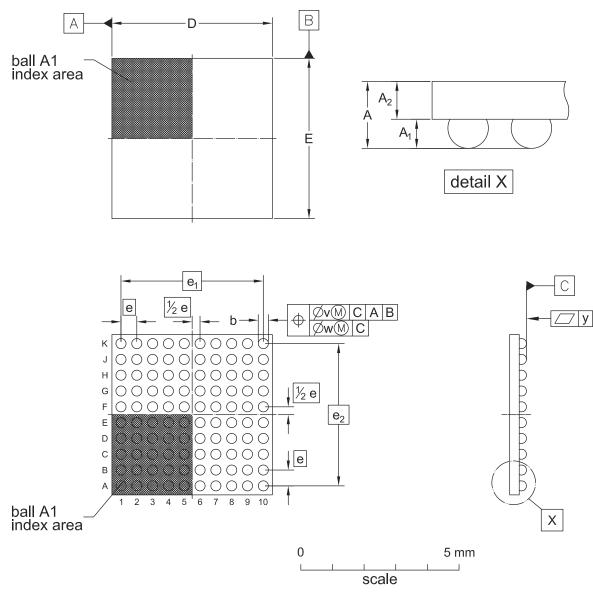

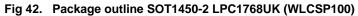

| DIMENSIONS | (mm | are the | original | dimensions | ) |

|------------|-----|---------|----------|------------|---|

|------------|-----|---------|----------|------------|---|

| UNIT |                   | А                    | A <sub>1</sub>       | $A_2$                   | b    | D                    | Е                    | е   | e <sub>1</sub> | e <sub>2</sub> | V    | W    | у    |

|------|-------------------|----------------------|----------------------|-------------------------|------|----------------------|----------------------|-----|----------------|----------------|------|------|------|

| mm   | MAX<br>NOM<br>MIN | 0.57<br>0.53<br>0.49 | 0.26<br>0.23<br>0.20 | 0.325<br>0.300<br>0.275 | 0.32 | 5.10<br>5.07<br>5.04 | 5.10<br>5.07<br>5.04 | 0.5 | 4.5            | 4.5            | 0.15 | 0.05 | 0.03 |

LPC1769\_68\_67\_66\_65\_64\_63