Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | ARM® Cortex®-M3                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                 |

| Speed                      | 100MHz                                                                             |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, Microwire, SPI, SSI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, Motor Control PWM, POR, PWM, WDT    |

| Number of I/O              | 70                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 64K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x12b; D/A 1x10b                                                               |

| Oscillator Type            | Internal                                                                           |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 100-TFBGA                                                                          |

| Supplier Device Package    | 100-TFBGA (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1768fet100z             |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- ◆ Quadrature encoder interface that can monitor one external quadrature encoder.

- One standard PWM/timer block with external count input.

- RTC with a separate power domain and dedicated RTC oscillator. The RTC block includes 20 bytes of battery-powered backup registers.

- WatchDog Timer (WDT). The WDT can be clocked from the internal RC oscillator, the RTC oscillator, or the APB clock.

- Arm Cortex-M3 system tick timer, including an external clock input option.

- Repetitive interrupt timer provides programmable and repeating timed interrupts.

- Each peripheral has its own clock divider for further power savings.

- Standard JTAG debug interface for compatibility with existing tools. Serial Wire Debug and Serial Wire Trace Port options. Boundary Scan Description Language (BSDL) is not available for this device.

- Emulation trace module enables non-intrusive, high-speed real-time tracing of instruction execution.

- Integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep, Deep sleep, Power-down, and Deep power-down modes.

- Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

- Single 3.3 V power supply (2.4 V to 3.6 V).

- Four external interrupt inputs configurable as edge/level sensitive. All pins on Port 0 and Port 2 can be used as edge sensitive interrupt sources.

- Non-maskable Interrupt (NMI) input.

- Clock output function that can reflect the main oscillator clock, IRC clock, RTC clock, CPU clock, and the USB clock.

- The Wake-up Interrupt Controller (WIC) allows the CPU to automatically wake up from any priority interrupt that can occur while the clocks are stopped in deep sleep, Power-down, and Deep power-down modes.

- Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet wake-up interrupt, CAN bus activity, Port 0/2 pin interrupt, and NMI).

- Brownout detect with separate threshold for interrupt and forced reset.

- Power-On Reset (POR).

- Crystal oscillator with an operating range of 1 MHz to 25 MHz.

- 4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a system clock.

- PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator, the internal RC oscillator, or the RTC oscillator.

- USB PLL for added flexibility.

- Code Read Protection (CRP) with different security levels.

- Unique device serial number for identification purposes.

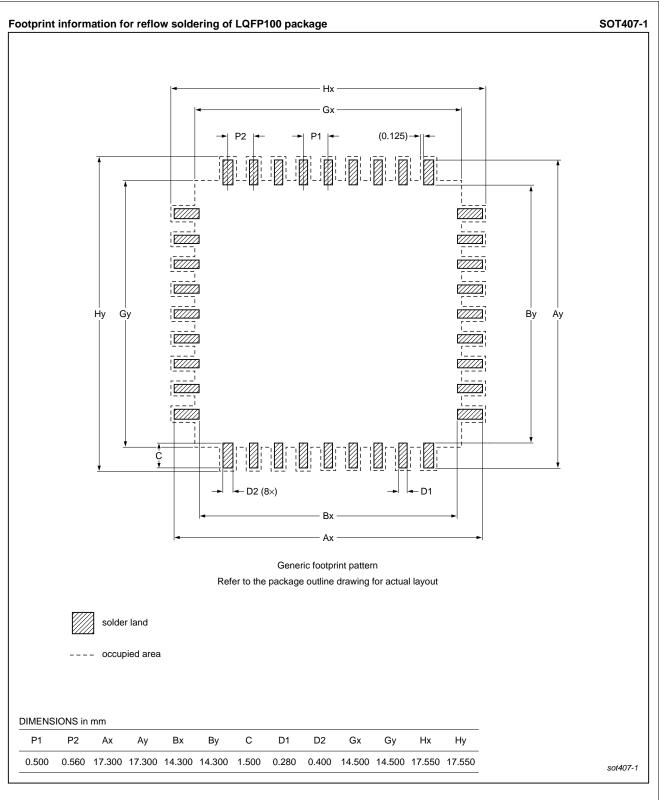

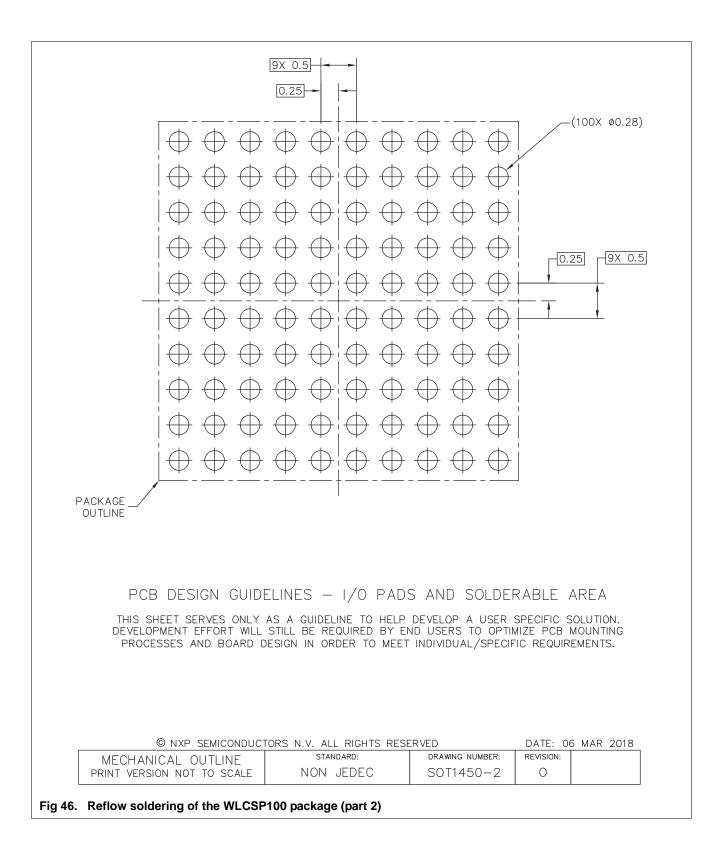

- Available as LQFP100 (14 mm × 14 mm × 1.4 mm), TFBGA100<sup>1</sup> (9 mm × 9 mm × 0.7 mm), and WLCSP100 (5.07 × 5.07 × 0.53 mm) package.

<sup>1.</sup> LPC1768/65 only.

| Pin | Symbol                              | Pin | Symbol                            | Pin | Symbol                       | Pin | Symbol                                |

|-----|-------------------------------------|-----|-----------------------------------|-----|------------------------------|-----|---------------------------------------|

| 9   | P2[7]/RD2/RTS1                      | 10  | P2[8]/TD2/TXD2                    | 11  | -                            | 12  | -                                     |

| Row | / F                                 |     |                                   |     |                              | 1   |                                       |

| 1   | VREFN                               | 2   | RTCX1                             | 3   | RESET                        | 4   | P1[31]/SCK1/<br>AD0[5]                |

| 5   | P1[21]/MCABORT/<br>PWM1[3]/SSEL0    | 6   | P0[18]/DCD1/<br>MOSI0/MOSI        | 7   | P2[9]/USB_CONNECT/<br>RXD2   | 8   | P0[16]/RXD1/<br>SSEL0/SSEL            |

| 9   | P0[17]/CTS1/<br>MISO0/MISO          | 10  | P0[15]/TXD1/<br>SCK0/SCK          | 11  | -                            | 12  | -                                     |

| Row | / G                                 |     | 1                                 |     |                              | 1   |                                       |

| 1   | RTCX2                               | 2   | VBAT                              | 3   | XTAL2                        | 4   | P0[30]/USB_D-                         |

| 5   | P1[25]/MCOA1/<br>MAT1[1]            | 6   | P1[29]/MCOB2/<br>PCAP1[1]/MAT0[1] | 7   | V <sub>SS</sub>              | 8   | P0[21]/RI1/RD1                        |

| 9   | P0[20]/DTR1/SCL1                    | 10  | P0[19]/DSR1/SDA1                  | 11  | -                            | 12  | -                                     |

| Row | / H                                 |     |                                   |     |                              | 1   |                                       |

| 1   | P1[30]/V <sub>BUS</sub> /<br>AD0[4] | 2   | XTAL1                             | 3   | P3[25]/MAT0[0]/<br>PWM1[2]   | 4   | P1[18]/USB_UP_LED/<br>PWM1[1]/CAP1[0] |

| 5   | P1[24]/MCl2/<br>PWM1[5]/MOSI0       | 6   | V <sub>DD(REG)(3V3)</sub>         | 7   | P0[10]/TXD2/<br>SDA2/MAT3[0] | 8   | P2[11]/EINT1/<br>I2STX_CLK            |

| 9   | V <sub>DD(3V3)</sub>                | 10  | P0[22]/RTS1/TD1                   | 11  | -                            | 12  | -                                     |

#### Table 4. Pin allocation table TFBGA100 ... continued

LPC1769\_68\_67\_66\_65\_64\_63

Table 5.

Pin description ...continued

| Symbol                  | Pin/    | /ball    |          |     | Туре | Description                                                                                                                                                                                                      |

|-------------------------|---------|----------|----------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | LQFP100 | TFBGA100 | WLCSP100 |     |      |                                                                                                                                                                                                                  |

| P0[23]/AD0[0]/          | 9       | E5       | D5       | [2] | I/O  | P0[23] — General purpose digital input/output pin.                                                                                                                                                               |

| I2SRX_CLK/<br>CAP3[0]   |         |          |          |     | I    | AD0[0] — A/D converter 0, input 0.                                                                                                                                                                               |

|                         |         |          |          |     | I/O  | <b>I2SRX_CLK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. (LPC1769/68/67/66/65/63 only).   |

|                         |         |          |          |     | I    | CAP3[0] — Capture input for Timer 3, channel 0.                                                                                                                                                                  |

| P0[24]/AD0[1]/          | 8       | D1       | B4       | [2] | I/O  | P0[24] — General purpose digital input/output pin.                                                                                                                                                               |

| I2SRX_WS/<br>CAP3[1]    |         |          |          |     | I    | AD0[1] — A/D converter 0, input 1.                                                                                                                                                                               |

| 0,4 0[1]                |         |          |          |     | I/O  | <b>I2SRX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification. (LPC1769/68/67/66/65/63 only).                       |

|                         |         |          |          |     | I    | CAP3[1] — Capture input for Timer 3, channel 1.                                                                                                                                                                  |

| P0[25]/AD0[2]/          | 7       | D2       | A3       | [2] | I/O  | P0[25] — General purpose digital input/output pin.                                                                                                                                                               |

| I2SRX_SDA/<br>TXD3      |         |          |          |     | I    | AD0[2] — A/D converter 0, input 2.                                                                                                                                                                               |

| 1703                    |         |          |          |     | I/O  | <b>I2SRX_SDA</b> — Receive data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. (LPC1769/68/67/66/65/63 only). |

|                         |         |          |          |     | 0    | TXD3 — Transmitter output for UART3.                                                                                                                                                                             |

| P0[26]/AD0[3]/          | 6       | D3       | C5       | [3] | I/O  | P0[26] — General purpose digital input/output pin.                                                                                                                                                               |

| AOUT/RXD3               |         |          |          |     | I    | AD0[3] — A/D converter 0, input 3.                                                                                                                                                                               |

|                         |         |          |          |     | 0    | AOUT — DAC output (LPC1769/68/67/66/65/63 only).                                                                                                                                                                 |

|                         |         |          |          |     | I    | <b>RXD3</b> — Receiver input for UART3.                                                                                                                                                                          |

| P0[27]/SDA0/<br>USB_SDA | 25      | J2       | C8       | [4] | I/O  | <b>P0[27]</b> — General purpose digital input/output pin. Output is open-drain.                                                                                                                                  |

|                         |         |          |          |     | I/O  | <b>SDA0</b> — I <sup>2</sup> C0 data input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                      |

|                         |         |          |          |     | I/O  | <b>USB_SDA</b> — USB port I <sup>2</sup> C serial data (OTG transceiver, LPC1769/68/66/65 only).                                                                                                                 |

| P0[28]/SCL0/<br>USB_SCL | 24      | J1       | B9       | [4] | I/O  | <b>P0[28]</b> — General purpose digital input/output pin. Output is open-drain.                                                                                                                                  |

|                         |         |          |          |     | I/O  | <b>SCL0</b> — I <sup>2</sup> C0 clock input/output. Open-drain output (for I <sup>2</sup> C-bus compliance).                                                                                                     |

|                         |         |          |          |     | I/O  | <b>USB_SCL</b> — USB port I <sup>2</sup> C serial clock (OTG transceiver, LPC1769/68/66/65 only).                                                                                                                |

| P0[29]/USB_D+           | 29      | J3       | B10      | [5] | I/O  | P0[29] — General purpose digital input/output pin.                                                                                                                                                               |

|                         |         |          |          |     | I/O  | USB_D+ — USB bidirectional D+ line. (LPC1769/68/66/65/64 only).                                                                                                                                                  |

| P0[30]/USB_D-           | 30      | G4       | C9       | [5] | I/O  | P0[30] — General purpose digital input/output pin.                                                                                                                                                               |

|                         |         |          |          |     | I/O  | USB_D- — USB bidirectional D- line. (LPC1769/68/66/65/64 only).                                                                                                                                                  |

The MPU allows separating processing tasks by disallowing access to each other's data, disabling access to memory regions, allowing memory regions to be defined as read-only and detecting unexpected memory accesses that could potentially break the system.

The MPU separates the memory into distinct regions and implements protection by preventing disallowed accesses. The MPU supports up to 8 regions each of which can be divided into 8 subregions. Accesses to memory locations that are not defined in the MPU regions, or not permitted by the region setting, will cause the Memory Management Fault exception to take place.

### 8.6 Memory map

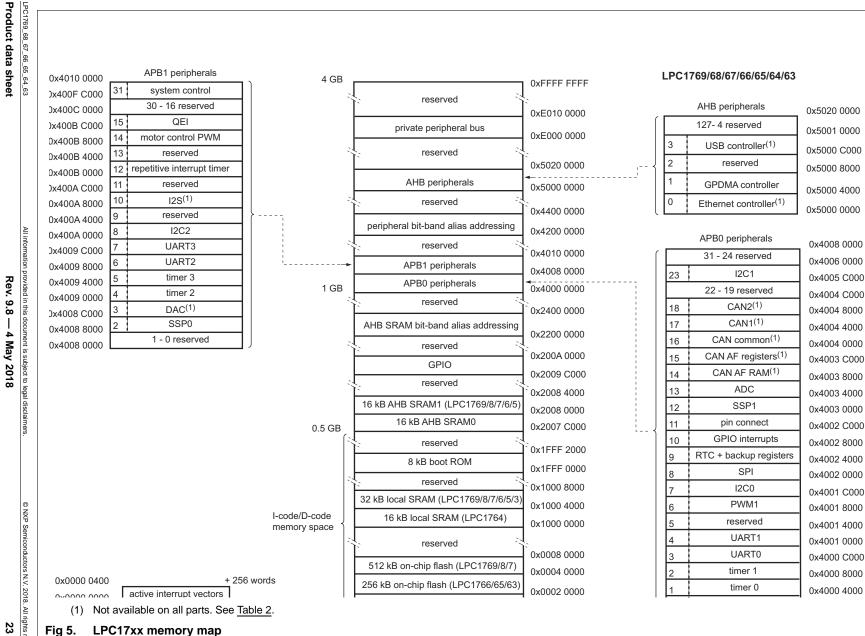

The LPC17xx incorporates several distinct memory regions, shown in the following figures. <u>Figure 5</u> shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The AHB peripheral area is 2 MB in size and is divided to allow for up to 128 peripherals. The APB peripheral area is 1 MB in size and is divided to allow for up to 64 peripherals. Each peripheral of either type is allocated 16 kB of space. This allows simplifying the address decoding for each peripheral.

LPC1769\_68\_67\_66\_65\_64\_63

32-bit ARM Cortex-M3 microcontroller

Rev.

T

23 of 93 èe

- Enhanced Ethernet features:

- Receive filtering.

- Multicast and broadcast frame support for both transmit and receive.

- Optional automatic Frame Check Sequence (FCS) insertion with Cyclic Redundancy Check (CRC) for transmit.

- Selectable automatic transmit frame padding.

- Over-length frame support for both transmit and receive allows any length frames.

- Promiscuous receive mode.

- Automatic collision back-off and frame retransmission.

- Includes power management by clock switching.

- Wake-on-LAN power management support allows system wake-up: using the receive filters or a magic frame detection filter.

- Physical interface:

- Attachment of external PHY chip through standard RMII interface.

- PHY register access is available via the MIIM interface.

### 8.12 USB interface

**Remark:** The USB controller is available as device/Host/OTG controller on parts LPC1769/68/66/65 and as device-only controller on part LPC1764.

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot plugging and dynamic configuration of the devices. All transactions are initiated by the host controller.

The USB interface includes a device, Host, and OTG controller with on-chip PHY for device and Host functions. The OTG switching protocol is supported through the use of an external controller. Details on typical USB interfacing solutions can be found in <u>Section 15.1</u>.

### 8.12.1 USB device controller

The device controller enables 12 Mbit/s data exchange with a USB Host controller. It consists of a register interface, serial interface engine, endpoint buffer memory, and a DMA controller. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. An interrupt is also generated if enabled. When enabled, the DMA controller transfers data between the endpoint buffer and the on-chip SRAM.

#### 8.12.1.1 Features

- Fully compliant with USB 2.0 specification (full speed).

- Supports 32 physical (16 logical) endpoints with a 4 kB endpoint buffer RAM.

- Supports Control, Bulk, Interrupt and Isochronous endpoints.

All information provided in this document is subject to legal disclaimers.

• Scalable realization of endpoints at run time.

## 8.16 UARTs

The LPC17xx each contain four UARTs. In addition to standard transmit and receive data lines, UART1 also provides a full modem control handshake interface and support for RS-485/9-bit mode allowing both software address detection and automatic address detection using 9-bit mode.

The UARTs include a fractional baud rate generator. Standard baud rates such as 115200 Bd can be achieved with any crystal frequency above 2 MHz.

#### 8.16.1 Features

- Maximum UART data bit rate of 6.25 Mbit/s.

- 16 B Receive and Transmit FIFOs.

- Register locations conform to 16C550 industry standard.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, and 14 B.

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- Auto baud capabilities and FIFO control mechanism that enables software flow control implementation.

- UART1 equipped with standard modem interface signals. This module also provides full support for hardware flow control (auto-CTS/RTS).

- Support for RS-485/9-bit/EIA-485 mode (UART1).

- UART3 includes an IrDA mode to support infrared communication.

- All UARTs have DMA support.

## 8.17 SPI serial I/O controller

The LPC17xx contain one SPI controller. SPI is a full duplex serial interface designed to handle multiple masters and slaves connected to a given bus. Only a single master and a single slave can communicate on the interface during a given data transfer. During a data transfer the master always sends 8 bits to 16 bits of data to the slave, and the slave always sends 8 bits to 16 bits of data to the master.

#### 8.17.1 Features

- Maximum SPI data bit rate of 12.5 Mbit/s

- Compliant with SPI specification

- Synchronous, serial, full duplex communication

- Combined SPI master and slave

- Maximum data bit rate of one eighth of the input clock rate

- 8 bits to 16 bits per transfer

## 8.18 SSP serial I/O controller

The LPC17xx contain two SSP controllers. The SSP controller is capable of operation on a SPI, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus during a given

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- Up to two match registers can be used to generate timed DMA requests.

### 8.22 Pulse width modulator

The PWM is based on the standard Timer block and inherits all of its features, although only the PWM function is pinned out on the LPC17xx. The Timer is designed to count cycles of the system derived clock and optionally switch pins, generate interrupts or perform other actions when specified timer values occur, based on seven match registers. The PWM function is in addition to these features, and is based on match register events.

The ability to separately control rising and falling edge locations allows the PWM to be used for more applications. For instance, multi-phase motor control typically requires three non-overlapping PWM outputs with individual control of all three pulse widths and positions.

Two match registers can be used to provide a single edge controlled PWM output. One match register (PWMMR0) controls the PWM cycle rate, by resetting the count upon match. The other match register controls the PWM edge position. Additional single edge controlled PWM outputs require only one match register each, since the repetition rate is the same for all PWM outputs. Multiple single edge controlled PWM outputs will all have a rising edge at the beginning of each PWM cycle, when an PWMMR0 match occurs.

Three match registers can be used to provide a PWM output with both edges controlled. Again, the PWMMR0 match register controls the PWM cycle rate. The other match registers control the two PWM edge positions. Additional double edge controlled PWM outputs require only two match registers each, since the repetition rate is the same for all PWM outputs.

With double edge controlled PWM outputs, specific match registers control the rising and falling edge of the output. This allows both positive going PWM pulses (when the rising edge occurs prior to the falling edge), and negative going PWM pulses (when the falling edge occurs prior to the rising edge).

#### 8.22.1 Features

- One PWM block with Counter or Timer operation (may use the peripheral clock or one of the capture inputs as the clock source).

- Seven match registers allow up to 6 single edge controlled or 3 double edge controlled PWM outputs, or a mix of both types. The match registers also allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

32-bit ARM Cortex-M3 microcontroller

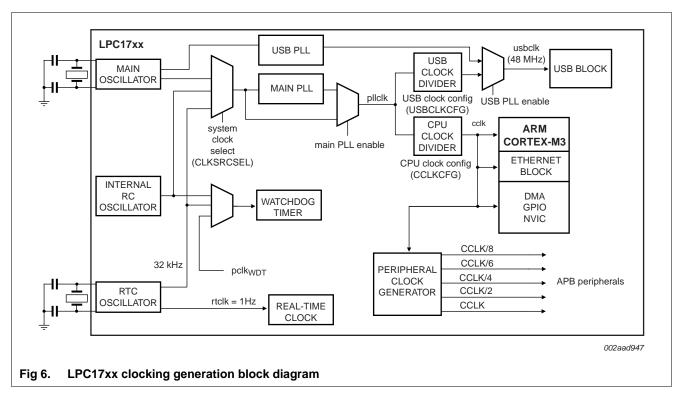

See Figure 6 for an overview of the LPC17xx clock generation.

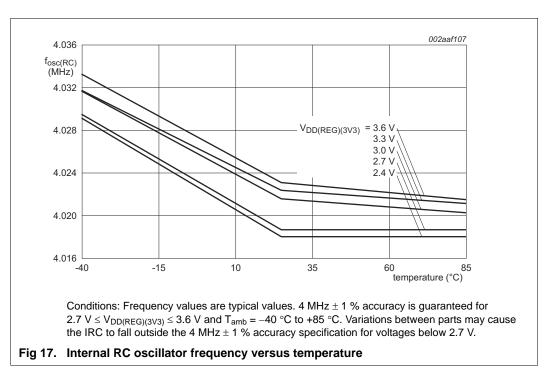

#### 8.29.1.1 Internal RC oscillator

The IRC may be used as the clock source for the WDT, and/or as the clock that drives the PLL and subsequently the CPU. The nominal IRC frequency is 4 MHz. The IRC is trimmed to 1 % accuracy over the entire voltage and temperature range.

Upon power-up or any chip reset, the LPC17xx use the IRC as the clock source. Software may later switch to one of the other available clock sources.

#### 8.29.1.2 Main oscillator

The main oscillator can be used as the clock source for the CPU, with or without using the PLL. The main oscillator also provides the clock source for the dedicated USB PLL.

The main oscillator operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the main PLL. The clock selected as the PLL input is PLLCLKIN. The Arm processor clock frequency is referred to as CCLK elsewhere in this document. The frequencies of PLLCLKIN and CCLK are the same value unless the PLL is active and connected. The clock frequency for each peripheral can be selected individually and is referred to as PCLK. Refer to <u>Section 8.29.2</u> for additional information.

### 8.29.1.3 RTC oscillator

The RTC oscillator can be used as the clock source for the RTC block, the main PLL, and/or the CPU.

### 8.29.8 Power domains

The LPC17xx provide two independent power domains that allow the bulk of the device to have power removed while maintaining operation of the RTC and the backup Registers.

On the LPC17xx, I/O pads are powered by the 3.3 V ( $V_{DD(3V3)}$ ) pins, while the  $V_{DD(REG)(3V3)}$  pin powers the on-chip voltage regulator which in turn provides power to the CPU and most of the peripherals.

Depending on the LPC17xx application, a design can use two power options to manage power consumption.

The first option assumes that power consumption is not a concern and the design ties the  $V_{DD(3V3)}$  and  $V_{DD(REG)(3V3)}$  pins together. This approach requires only one 3.3 V power supply for both pads, the CPU, and peripherals. While this solution is simple, it does not support powering down the I/O pad ring "on the fly" while keeping the CPU and peripherals alive.

The second option uses two power supplies; a 3.3 V supply for the I/O pads ( $V_{DD(3V3)}$ ) and a dedicated 3.3 V supply for the CPU ( $V_{DD(REG)(3V3)}$ ). Having the on-chip voltage regulator powered independently from the I/O pad ring enables shutting down of the I/O pad power supply "on the fly", while the CPU and peripherals stay active.

The VBAT pin supplies power only to the RTC domain. The RTC requires a minimum of power to operate, which can be supplied by an external battery. The device core power  $(V_{DD(REG)(3V3)})$  is used to operate the RTC whenever  $V_{DD(REG)(3V3)}$  is present. Therefore, there is no power drain from the RTC battery when  $V_{DD(REG)(3V3)}$  is available.

LPC1769\_68\_67\_66\_65\_64\_63

#### Table 8. Static characteristics ...continued

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

| Symbol               | Parameter                                  | Conditions                                                                        |                  | Min                           | Typ <u>[1]</u> | Max                     | Unit |

|----------------------|--------------------------------------------|-----------------------------------------------------------------------------------|------------------|-------------------------------|----------------|-------------------------|------|

| I <sub>DD(ADC)</sub> | ADC supply current                         | active mode;                                                                      | [16][17]         | -                             | 1.95           | -                       | mA   |

|                      |                                            | ADC powered                                                                       |                  |                               |                |                         |      |

|                      |                                            | ADC in Power-down mode                                                            | [16][18]         | -                             | <0.2           | -                       | μA   |

|                      |                                            | deep sleep mode                                                                   | [16]             | -                             | 38             | -                       | nA   |

|                      |                                            | power-down mode                                                                   | [16]             | -                             | 38             | -                       | nA   |

|                      |                                            | deep power-down mode                                                              | [16]             | -                             | 24             | -                       | nA   |

| I <sub>I(ADC)</sub>  | ADC input current                          | on pin VREFP                                                                      |                  |                               |                |                         |      |

|                      |                                            | deep sleep mode                                                                   | [19]             | -                             | 100            | -                       | nA   |

|                      |                                            | power-down mode                                                                   | [19]             | -                             | 100            | -                       | nA   |

|                      |                                            | deep power-down<br>mode                                                           | [19]             | -                             | 100            | -                       | nA   |

| Standard po          | rt pins, RESET, RTCK                       |                                                                                   |                  | 1                             | 1              | I                       |      |

| IIL                  | LOW-level input current                    | $V_I = 0 V$ ; on-chip pull-up<br>resistor disabled                                |                  | -                             | 0.5            | 10                      | nA   |

| I <sub>IH</sub>      | HIGH-level input<br>current                | $V_I = V_{DD(3V3)}$ ; on-chip<br>pull-down resistor<br>disabled                   |                  | -                             | 0.5            | 10                      | nA   |

| I <sub>OZ</sub>      | OFF-state output<br>current                | $V_O = 0 V$ ; $V_O = V_{DD(3V3)}$ ;<br>on-chip pull-up/down<br>resistors disabled |                  | -                             | 0.5            | 10                      | nA   |

| VI                   | input voltage                              | pin configured to provide<br>a digital function                                   | [20][21]<br>[22] | 0                             | -              | 5.0                     | V    |

| Vo                   | output voltage                             | output active                                                                     |                  | 0                             | -              | V <sub>DD(3V3)</sub>    | V    |

| V <sub>IH</sub>      | HIGH-level input<br>voltage                |                                                                                   |                  | 0.7V <sub>DD(3V3)</sub>       | -              | -                       | V    |

| V <sub>IL</sub>      | LOW-level input voltage                    |                                                                                   |                  | -                             | -              | 0.3V <sub>DD(3V3)</sub> | V    |

| V <sub>hys</sub>     | hysteresis voltage                         |                                                                                   |                  | 0.4                           | -              | -                       | V    |

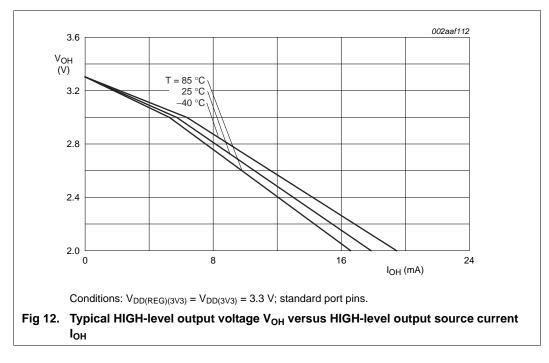

| V <sub>OH</sub>      | HIGH-level output<br>voltage               | $I_{OH} = -4 \text{ mA}$                                                          |                  | V <sub>DD(3V3)</sub> -<br>0.4 | -              | -                       | V    |

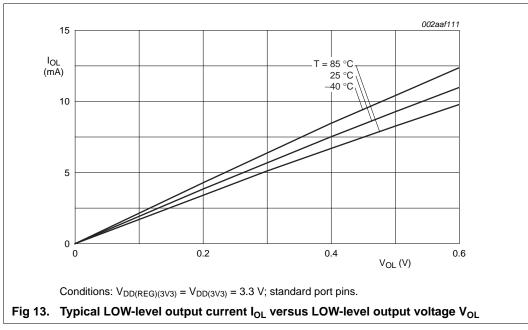

| V <sub>OL</sub>      | LOW-level output voltage                   | I <sub>OL</sub> = 4 mA                                                            |                  | -                             | -              | 0.4                     | V    |

| I <sub>OH</sub>      | HIGH-level output current                  | $V_{OH} = V_{DD(3V3)} - 0.4 V$                                                    |                  | -4                            | -              | -                       | mA   |

| I <sub>OL</sub>      | LOW-level output current                   | V <sub>OL</sub> = 0.4 V                                                           |                  | 4                             | -              | -                       | mA   |

| I <sub>OHS</sub>     | HIGH-level short-circuit<br>output current | V <sub>OH</sub> = 0 V                                                             | [23]             | -                             | -              | -45                     | mA   |

| I <sub>OLS</sub>     | LOW-level short-circuit<br>output current  | $V_{OL} = V_{DD(3V3)}$                                                            | [23]             | -                             | -              | 50                      | mA   |

| I <sub>pd</sub>      | pull-down current                          | V <sub>I</sub> = 5 V                                                              |                  | 10                            | 50             | 150                     | μA   |

| I <sub>pu</sub>      | pull-up current                            | $V_{I} = 0 V$                                                                     |                  | -15                           | -50            | -85                     | μA   |

|                      |                                            | V <sub>DD(3V3)</sub> < V <sub>I</sub> < 5 V                                       |                  | 0                             | 0              | 0                       | μA   |

32-bit ARM Cortex-M3 microcontroller

# 11.3 Electrical pin characteristics

## 12.3 Internal oscillators

#### Table 12. Dynamic characteristic: internal oscillators

```

T_{amb} = -40 \text{ °C to } +85 \text{ °C}; 2.7 \text{ V} \le V_{DD(REG)(3V3)} \le 3.6 \text{ V}.<sup>[1]</sup>

```

| Symbol               | Parameter                        | Conditions | Min  | Typ <u><sup>[2]</sup></u> | Max  | Unit |

|----------------------|----------------------------------|------------|------|---------------------------|------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator frequency | -          | 3.96 | 4.02                      | 4.04 | MHz  |

| f <sub>i(RTC)</sub>  | RTC input frequency              | -          | -    | 32.768                    | -    | kHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

## 12.4 I/O pins

#### Table 13. Dynamic characteristic: I/O pins<sup>[1]</sup>

$T_{amb} = -40 \ ^{\circ}C$  to +85  $\ ^{\circ}C$ ;  $V_{DD(3V3)}$  over specified ranges.

| Symbol         | Parameter | Conditions               | Min | Тур | Max | Unit |

|----------------|-----------|--------------------------|-----|-----|-----|------|

| t <sub>r</sub> | rise time | pin configured as output | 3.0 | -   | 5.0 | ns   |

| t <sub>f</sub> | fall time | pin configured as output | 2.5 | -   | 5.0 | ns   |

[1] Applies to standard I/O pins.

32-bit ARM Cortex-M3 microcontroller

| Symbol                | Parameter                    | Conditions                                               |        | Min | Тур  | Max | Unit |

|-----------------------|------------------------------|----------------------------------------------------------|--------|-----|------|-----|------|

| E <sub>D</sub>        | differential linearity error |                                                          | [2][3] | -   | ±1   | -   | LSB  |

| E <sub>L(adj)</sub>   | integral non-linearity       |                                                          | [4]    | -   | ±1.5 | -   | LSB  |

| Eo                    | offset error                 |                                                          | [5]    | -   | ±2   | -   | LSB  |

| E <sub>G</sub>        | gain error                   |                                                          | [6]    | -   | ±2   | -   | LSB  |

| f <sub>clk(ADC)</sub> | ADC clock frequency          | $3.0~V \leq V_{DDA} \leq 3.6~V$                          |        | -   | -    | 33  | MHz  |

|                       |                              | $2.7~\text{V} \leq \text{V}_{\text{DDA}} < 3.0~\text{V}$ |        | -   | -    | 25  | MHz  |

| f <sub>c(ADC)</sub>   | ADC conversion frequency     | $3~V \leq V_{DDA} \leq 3.6~V$                            | [7]    | -   | -    | 500 | kHz  |

|                       |                              | $2.7~V \leq V_{DDA} < 3.0~V$                             | [7]    | -   | -    | 400 | kHz  |

#### Table 20. ADC characteristics (lower resolution)

$T_{amb} = -40 \degree C$  to +85  $\degree C$  unless otherwise specified; 12-bit ADC used as 10-bit resolution ADC.[1]

[1]  $V_{DDA}$  and VREFP should be tied to  $V_{DD(3V3)}$  if the ADC and DAC are not used.

[2] The ADC is monotonic, there are no missing codes.

[3] The differential linearity error (E<sub>D</sub>) is the difference between the actual step width and the ideal step width. See Figure 28.

[4] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 28</u>.

[5] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See <u>Figure 28</u>.

[6] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See <u>Figure 28</u>.

[7] The conversion frequency corresponds to the number of samples per second.

LPC1769\_68\_67\_66\_65\_64\_63

32-bit ARM Cortex-M3 microcontroller

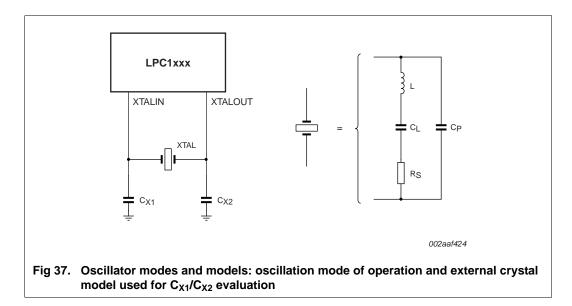

| Table 23. | Recommended values for $C_{X1}/C_{X2}$ in oscillation mode (crystal and external |

|-----------|----------------------------------------------------------------------------------|

|           | components parameters): low frequency mode                                       |

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> /C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------|

| 1 MHz to 5 MHz                                     | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 300 Ω                                             | 39 pF, 39 pF                                                 |

|                                                    | 30 pF                                      | < 300 Ω                                             | 57 pF, 57 pF                                                 |

| 5 MHz to 10 MHz                                    | 10 pF                                      | < 300 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 200 Ω                                             | 39 pF, 39 pF                                                 |

|                                                    | 30 pF                                      | < 100 Ω                                             | 57 pF, 57 pF                                                 |

| 10 MHz to 15 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                 |

|                                                    | 20 pF                                      | < 60 Ω                                              | 39 pF, 39 pF                                                 |

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 80 Ω                                              | 18 pF, 18 pF                                                 |

Table 24. Recommended values for  $C_{X1}/C_{X2}$  in oscillation mode (crystal and external components parameters): high frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load<br>capacitance C <sub>L</sub> | Maximum crystal<br>series resistance R <sub>S</sub> | External load<br>capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------|

| 15 MHz to 20 MHz                                   | 10 pF                                      | < 180 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 100 Ω                                             | 39 pF, 39 pF                                                  |

| 20 MHz to 25 MHz                                   | 10 pF                                      | < 160 Ω                                             | 18 pF, 18 pF                                                  |

|                                                    | 20 pF                                      | < 80 Ω                                              | 39 pF, 39 pF                                                  |

# 15.3 XTAL and RTCX Printed Circuit Board (PCB) layout guidelines

The crystal should be connected on the PCB as close as possible to the oscillator input and output pins of the chip. Take care that the load capacitors  $C_{x1}$ ,  $C_{x2}$ , and  $C_{x3}$  in case of third overtone crystal usage have a common ground plane. The external components must also be connected to the ground plain. Loops must be made as small as possible in

32-bit ARM Cortex-M3 microcontroller

# 17. Soldering

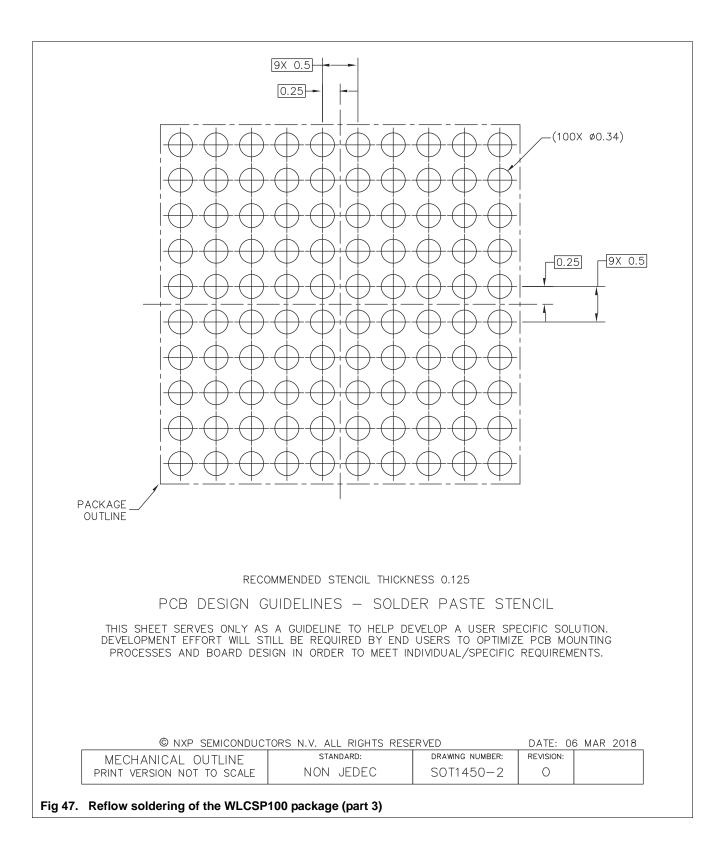

Fig 43. Reflow soldering for the LQFP100 package

LPC1769\_68\_67\_66\_65\_64\_63

© NXP Semiconductors N.V. 2018. All rights reserved.

#### 32-bit ARM Cortex-M3 microcontroller

### 32-bit ARM Cortex-M3 microcontroller

| Document ID                     | Release<br>date                                                                    | Data sheet status                                                                                                               | Change<br>notice             | Supersedes                                                       |  |  |  |  |

|---------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------|--|--|--|--|

| LPC1769_68_67_66_65_64_63 v.9.2 | 20131021                                                                           | Product data sheet                                                                                                              | -                            | LPC1769_68_67_66_65_64 v.9.1                                     |  |  |  |  |

| Modifications:                  |                                                                                    | 8 "Static characteristics                                                                                                       | 5":                          |                                                                  |  |  |  |  |

|                                 |                                                                                    | <ul> <li>Added Table note 3 "VDDA and VREFP should be tied to VDD(3V3) if the</li> </ul>                                        |                              |                                                                  |  |  |  |  |

|                                 |                                                                                    | ADC and DAC are not used."                                                                                                      |                              |                                                                  |  |  |  |  |

|                                 | – Ad                                                                               | <ul> <li>Added Table note 4 "VDDA for DAC specs are from 2.7 V to 3.6 V."</li> </ul>                                            |                              |                                                                  |  |  |  |  |

|                                 | – V <sub>D</sub>                                                                   | <sub>DA</sub> /VREFP spec chang                                                                                                 | ed from 2.7 V to             | o 2.5 V.                                                         |  |  |  |  |

|                                 | Table                                                                              | 19 "ADC characteristic                                                                                                          | s (full resolution           | ו)":                                                             |  |  |  |  |

|                                 |                                                                                    | ded Table note 1 "VDD<br>C and DAC are not us                                                                                   |                              | should be tied to VDD(3V3) if the                                |  |  |  |  |

|                                 | – V <sub>D</sub>                                                                   | <sub>DA</sub> changed from 2.7 V                                                                                                | to 2.5 V.                    |                                                                  |  |  |  |  |

|                                 |                                                                                    |                                                                                                                                 | •                            | ion)": Added Table note 1 "VDDA<br>ne ADC and DAC are not used." |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.9.1 | 20130916                                                                           | Product data sheet                                                                                                              | -                            | LPC1769_68_67_66_65_64 v.9                                       |  |  |  |  |

| Modifications:                  | Added                                                                              | Table 7 "Thermal resi                                                                                                           | stance".                     |                                                                  |  |  |  |  |

|                                 | Table                                                                              | 6 "Limiting values":                                                                                                            |                              |                                                                  |  |  |  |  |

|                                 | – Up                                                                               | dated min/max values                                                                                                            | for V <sub>DD(3V3)</sub> and | d V <sub>DD(REG)(3V3)</sub> .                                    |  |  |  |  |

|                                 | – Up                                                                               | dated conditions for V <sub>I</sub>                                                                                             |                              |                                                                  |  |  |  |  |

|                                 | <ul> <li>Updated table notes.</li> </ul>                                           |                                                                                                                                 |                              |                                                                  |  |  |  |  |

|                                 |                                                                                    | <ul> <li>Table 8 "Static characteristics": Added Table note 15 "TCK/SWDCLK pin nee<br/>to be externally pulled LOW."</li> </ul> |                              |                                                                  |  |  |  |  |

|                                 | <ul> <li>Updated Section 15.1 "Suggested USB interface solutions".</li> </ul>      |                                                                                                                                 |                              |                                                                  |  |  |  |  |

|                                 | <ul> <li>Added Section 5 "Marking".</li> </ul>                                     |                                                                                                                                 |                              |                                                                  |  |  |  |  |

|                                 |                                                                                    | ged title of Figure 31 fro<br>interface with soft-conr                                                                          |                              | ce on a self-powered device" to                                  |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.9   | 20120810                                                                           | Product data sheet                                                                                                              | -                            | LPC1769_68_67_66_65_64 v.8                                       |  |  |  |  |

| Modifications:                  |                                                                                    | ve table note "The pea<br>num current." from Tabl                                                                               |                              | ted to 25 times the corresponding lues".                         |  |  |  |  |

|                                 | <ul> <li>Chang</li> </ul>                                                          | ge V <sub>DD(3V3)</sub> to V <sub>DD(REG)</sub>                                                                                 | (3V3) in Section             | 11.3 "Internal oscillators".                                     |  |  |  |  |

|                                 | <ul> <li>Glitch</li> </ul>                                                         | filter constant changed                                                                                                         | to 10 ns in Tab              | ble note 6 in Table 4.                                           |  |  |  |  |

|                                 | <ul> <li>Descri</li> </ul>                                                         | iption of RESET function                                                                                                        | on updated in Ta             | able 4.                                                          |  |  |  |  |

|                                 | <ul> <li>Pull-up</li> </ul>                                                        | o value added for GPIC                                                                                                          | ) pins in Table 4            | 4.                                                               |  |  |  |  |

|                                 | <ul> <li>Pin co</li> </ul>                                                         | nfiguration diagram for                                                                                                         | LQFP100 pack                 | kage corrected (Figure 2).                                       |  |  |  |  |

| LPC1769_68_67_66_65_64_63 v.8   | 20111114                                                                           | Product data sheet                                                                                                              | -                            | LPC1769_68_67_66_65_64 v.7                                       |  |  |  |  |

| Modifications:                  | <ul> <li>Pin de</li> </ul>                                                         | escription of USB_UP_I                                                                                                          | LED pin update               | d in Table 4.                                                    |  |  |  |  |

|                                 | <ul> <li>R<sub>i1</sub> and R<sub>i2</sub> labels in Figure 27 updated.</li> </ul> |                                                                                                                                 |                              |                                                                  |  |  |  |  |

|                                 | Part LPC1765FET100 added.                                                          |                                                                                                                                 |                              |                                                                  |  |  |  |  |

|                                 |                                                                                    | note 10 updated in Tab                                                                                                          |                              |                                                                  |  |  |  |  |

|                                 |                                                                                    | note 1 updated in Table                                                                                                         |                              |                                                                  |  |  |  |  |

|                                 |                                                                                    | escription of STCLK pin                                                                                                         | -                            |                                                                  |  |  |  |  |

|                                 |                                                                                    | omagnetic compatibility                                                                                                         | / data added in              | Section 14.6.                                                    |  |  |  |  |

|                                 | <ul> <li>Sectio</li> </ul>                                                         | n 16 added.                                                                                                                     |                              |                                                                  |  |  |  |  |

#### Table 27. Revision history ... continued

32-bit ARM Cortex-M3 microcontroller

# 23. Contents

| 1                | General description 1                                                    |

|------------------|--------------------------------------------------------------------------|

| 2                | Features and benefits 1                                                  |

| 3                | Applications 4                                                           |

| 4                | Ordering information 4                                                   |

| 4.1              | Ordering options 4                                                       |

| 5                | Marking 5                                                                |

| 6                | Block diagram 6                                                          |

| 7                | Pinning information 7                                                    |

| 7.1              | Pinning                                                                  |

| 7.2              | Pin description 10                                                       |

| 8                | Functional description 21                                                |

| 8.1              | Architectural overview                                                   |

| 8.2              | ARM Cortex-M3 processor                                                  |

| 8.3<br>8.4       | On-chip flash program memory                                             |

| 8.5              | On-chip SRAM                                                             |

| 8.6              | Memory map                                                               |

| 8.7              | Nested Vectored Interrupt Controller (NVIC) . 24                         |

| 8.7.1            | Features                                                                 |

| 8.7.2            | Interrupt sources 24                                                     |

| 8.8              | Pin connect block                                                        |

| 8.9              | General purpose DMA controller 24                                        |

| 8.9.1            | Features                                                                 |

| 8.10<br>8.10.1   | Fast general purpose parallel I/O    25      Features    26              |

| 8.10.1           | Ethernet                                                                 |

| 8.11.1           | Features                                                                 |

| 8.12             | USB interface                                                            |

| 8.12.1           | USB device controller                                                    |

| 8.12.1.1         | Features                                                                 |

| 8.12.2           | USB host controller 28                                                   |

| 8.12.2.1         | Features                                                                 |

| 8.12.3           | USB OTG controller 28                                                    |

| 8.12.3.1<br>8.13 | Features       28         CAN controller and acceptance filters       28 |

| 8.13.1           | Features                                                                 |

| 8.14             | 12-bit ADC                                                               |

| 8.14.1           | Features                                                                 |

| 8.15             | 10-bit DAC 29                                                            |

| 8.15.1           | Features                                                                 |

| 8.16             | UARTs                                                                    |

| 8.16.1           | Features                                                                 |

| 8.17             | SPI serial I/O controller                                                |

| 8.17.1<br>8.18   | Features    30      SSP serial I/O controller    30                      |

| 8.18.1           | Features                                                                 |

| 5.10.1           |                                                                          |

| 8.19     | I <sup>2</sup> C-bus serial I/O controllers  | 31 |

|----------|----------------------------------------------|----|

| 8.19.1   | Features                                     | 31 |

| 8.20     | I <sup>2</sup> S-bus serial I/O controllers  | 32 |

| 8.20.1   | Features                                     | 32 |

| 8.21     | General purpose 32-bit timers/external event |    |

|          | counters                                     | 32 |

| 8.21.1   | Features                                     | 32 |

| 8.22     | Pulse width modulator                        | 33 |

| 8.22.1   | Features                                     | 33 |

| 8.23     | Motor control PWM                            | 34 |

| 8.24     | Quadrature Encoder Interface (QEI)           | 34 |

| 8.24.1   | Features                                     | 34 |

| 8.25     | Repetitive Interrupt (RI) timer              | 35 |

| 8.25.1   | Features                                     | 35 |

| 8.26     | ARM Cortex-M3 system tick timer              | 35 |

| 8.27     | Watchdog timer                               | 35 |

| 8.27.1   | Features                                     | 35 |

| 8.28     | RTC and backup registers                     | 36 |

| 8.28.1   | Features                                     | 36 |

| 8.29     | Clocking and power control                   | 36 |

| 8.29.1   | Crystal oscillators                          | 36 |

| 8.29.1.1 | Internal RC oscillator                       | 37 |

| 8.29.1.2 | Main oscillator                              | 37 |

| 8.29.1.3 | RTC oscillator                               | 37 |

| 8.29.2   | Main PLL (PLL0)                              | 38 |

| 8.29.3   | USB PLL (PLL1)                               | 38 |

| 8.29.4   | RTC clock output                             | 38 |

| 8.29.5   | Wake-up timer                                | 38 |

| 8.29.6   | Power control                                | 39 |

| 8.29.6.1 | Sleep mode                                   | 39 |

| 8.29.6.2 | Deep-sleep mode                              | 39 |

| 8.29.6.3 | Power-down mode                              | 40 |

| 8.29.6.4 | Deep power-down mode                         | 40 |

| 8.29.6.5 | Wake-up interrupt controller                 | 40 |

| 8.29.7   | Peripheral power control                     | 40 |

| 8.29.8   | Power domains                                | 41 |

| 8.30     | System control                               | 42 |

| 8.30.1   | Reset                                        | 42 |

| 8.30.2   | Brownout detection                           | 43 |

| 8.30.3   | Code security (Code Read Protection - CRP)   | 43 |

| 8.30.4   | APB interface                                | 43 |

| 8.30.5   | AHB multilayer matrix                        | 44 |

| 8.30.6   | External interrupt inputs                    | 44 |

| 8.30.7   | Memory mapping control                       | 44 |

| 8.31     | Emulation and debugging                      | 44 |

| 9        | Limiting values                              | 45 |

|          | Thermal characteristics                      | 46 |

|          |                                              |    |

continued >>