Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 48                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1.5K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-TQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321ar7t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 12.2.1 Voltage Characteristics                              |     |

|-------------------------------------------------------------|-----|

| 12.2.2 Current Characteristics                              |     |

| 12.2.3 Thermal Characteristics                              |     |

| 12.3.1 General Operating Conditions                         |     |

| 12.3.2 Operating Conditions with Low Voltage Detector (LVD) |     |

| 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds          |     |

| 12.3.4 External Voltage Detector (EVD) Thresholds           | 141 |

| 12.4 SUPPLY CURRENT CHARACTERISTICS                         | 142 |

| 12.4.1 CURRENT CONSUMPTION                                  |     |

| 12.4.2 Supply and Clock Managers                            |     |

| 12.4.3 On-Chip Peripherals                                  |     |

| 12.5 CLOCK AND TIMING CHARACTERISTICS                       |     |

| 12.5.1 General Timings                                      |     |

| 12.5.2 External Clock Source                                |     |

| 12.5.4 RC Oscillators                                       |     |

| 12.5.5 PLL Characteristics                                  |     |

| 12.6 MEMORY CHARACTERISTICS                                 | 152 |

| 12.6.1 RAM and Hardware Registers                           | 152 |

| 12.6.2 FLASH Memory                                         |     |

| 12.7 EMC CHARACTERISTICS                                    |     |

| 12.7.1 Functional EMS (Electro Magnetic Susceptibility)     |     |

| 12.7.2 Electro Magnetic Interference (EMI)                  |     |

| 12.7.3 Absolute Maximum Ratings (Electrical Sensitivity)    |     |

| 12.8.1 General Characteristics                              |     |

| 12.8.2 Output Driving Current                               |     |

| 12.9 CONTROL PIN CHARACTERISTICS                            |     |

| 12.9.1 Asynchronous RESET Pin                               | 159 |

| 12.9.2 ICCSEL/VPP Pin                                       |     |

| 12.10TIMER PERIPHERAL CHARACTERISTICS                       | 162 |

| 12.10.1 8-Bit PWM-ART Auto-Reload Timer                     |     |

| 12.10.2 16-Bit Timer                                        |     |

| 12.11COMMUNICATION INTERFACE CHARACTERISTICS                |     |

| 12.11.1 SPI - Serial Peripheral Interface                   |     |

| 12.11.2 I2C - Inter IC Control Interface                    |     |

| 12.12.1 Analog Power Supply and Reference Pins              |     |

| 12.12.2 General PCB Design Guidelines                       |     |

| 12.12.3 ADC Accuracy                                        |     |

| 13 PACKAGE CHARACTERISTICS                                  | 171 |

| 13.1 PACKAGE MECHANICAL DATA                                | 171 |

| 13.2 THERMAL CHARACTERISTICS                                | 173 |

| 13.3 SOLDERING AND GLUEABILITY INFORMATION                  | 174 |

| 14 ST72321 DEVICE CONFIGURATION AND ORDERING INFORMATION    | 175 |

# **Table of Contents**

| 14.1 FLAS  | H OPTION BYTES                                                  | 175 |

|------------|-----------------------------------------------------------------|-----|

| 14.2 DEVI0 | CE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE           | 177 |

| 14.3 DEVE  | LOPMENT TOOLS                                                   | 181 |

|            | Starter kits                                                    |     |

| 14.3.2     |                                                                 |     |

|            | Programming tools                                               |     |

|            | Socket and Emulator Adapter Information                         |     |

|            | PPLICATION NOTES                                                |     |

| 15 KNOWN L | IMITATIONS                                                      | 186 |

|            | LASH AND ROM DEVICES                                            |     |

| 15.1.1     | External RC option                                              | 186 |

|            | Safe Connection of OSC1/OSC2 Pins                               |     |

| 15.1.3     | Reset pin protection with LVD Enabled                           | 186 |

|            | Unexpected Reset Fetch                                          |     |

|            | External interrupt missed                                       |     |

|            | Clearing active interrupts outside interrupt routine            |     |

|            | SCI Wrong Break duration                                        |     |

| 15.1.8     |                                                                 |     |

|            | TIMD set simultaneously with OC interrupt                       |     |

|            |                                                                 |     |

|            |                                                                 |     |

|            | Internal RC Oscillator with LVD                                 |     |

|            | ATIONS SPECIFIC TO REV Q AND REV S FLASH DEVICES                |     |

|            | ADC Accuracy                                                    |     |

|            | ATIONS SPECIFIC TO ROM DEVICES                                  |     |

|            | LVD Operation                                                   |     |

|            | LVD Startup behaviour                                           |     |

|            | AVD not supported                                               |     |

| 15.4.4     |                                                                 |     |

|            | External clock source with PLL                                  |     |

|            | Pull-up not present on PE2      Pull-up not protection with LVD |     |

|            | Safe Connection of OSC1/OSC2 Pins                               |     |

|            | HISTORY                                                         |     |

|            |                                                                 | 152 |

# PIN DESCRIPTION (Cont'd)

For external pin connection guidelines, refer to See "ELECTRICAL CHARACTERISTICS" on page 138. Legend / Abbreviations for Table 2 :

| -                |                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре:            | I = input, O = output, S = supply                                                                                                                                                                   |

| Input level:     | A = Dedicated analog input                                                                                                                                                                          |

| In/Output level: | $\begin{array}{l} C = CMOS \; 0.3 V_{DD} / 0.7 V_{DD} \\ C_T = CMOS \; 0.3 V_{DD} / 0.7 V_{DD} \; \text{with input trigger} \\ T_T = TTL \; 0.8 V / 2 V \; \text{with Schmitt trigger} \end{array}$ |

| Output level:    | HS = 20mA high sink (on N-buffer only)                                                                                                                                                              |

Port and control configuration:

- Input: float = floating, wpu = weak pull-up, int = interrupt <sup>1</sup>), ana = analog

- Output:  $OD = open drain^{2}$ , PP = push-pull

Refer to "I/O PORTS" on page 46 for more details on the software configuration of the I/O ports.

The RESET configuration of each pin is shown in bold. This configuration is valid as long as the device is in reset state.

| F      | Pin n  | 0      |                   |     | Le                      | evel |       |     | Ρ     | ort |     |      | Main               |                          |                        |

|--------|--------|--------|-------------------|-----|-------------------------|------|-------|-----|-------|-----|-----|------|--------------------|--------------------------|------------------------|

| P64    | P44    | P32    | Pin Name          | ype | Type<br>Input<br>Output |      |       | Inp | out   |     | Out | tput | function<br>(after | Alternate function       |                        |

| LQFP64 | LQFP44 | LQFP32 |                   |     |                         |      |       |     | float | ndm | int | ana  | OD                 | РР                       | reset)                 |

| 1      | -      | -      | PE4 (HS)          | I/O | $C_T$                   | HS   | Х     | Х   |       |     | Х   | Х    | Port E4            |                          |                        |

| 2      | -      | -      | PE5 (HS)          | I/O | $C_T$                   | HS   | Х     | Х   |       |     | Х   | Х    | Port E5            |                          |                        |

| 3      | -      | -      | PE6 (HS)          | I/O | $C_T$                   | HS   | Х     | Х   |       |     | Х   | Х    | Port E6            |                          |                        |

| 4      | -      | -      | PE7 (HS)          | I/O | $C_T$                   | HS   | Х     | Х   |       |     | Х   | Х    | Port E7            |                          |                        |

| 5      | 2      | 28     | PB0/PWM3          | I/O | $C_T$                   |      | Χ     | е   | i2    |     | Х   | Х    | Port B0            | PWM Output 3             |                        |

| 6      | 3      | -      | PB1/PWM2          | I/O | $C_T$                   |      | Х     | е   | i2    |     | Х   | Х    | Port B1            | PWM Output 2             |                        |

| 7      | 4      | -      | PB2/PWM1          | I/O | $C_T$                   |      | Х     | е   | i2    |     | Х   | Х    | Port B2            | PWM Output 1             |                        |

| 8      | 5      | 29     | PB3/PWM0          | I/O | $C_T$                   |      | Χ     |     | ei2   |     | Х   | Х    | Port B3            | PWM Output 0             |                        |

| 9      | 6      | 30     | PB4 (HS)/ARTCLK   | I/O | $C_T$                   | HS   | X ei3 |     | X ei3 |     |     | Х    | Х                  | Port B4                  | PWM-ART External Clock |

| 10     | -      | -      | PB5 / ARTIC1      | I/O | $C_T$                   |      | Х     | е   | i3    |     | Х   | Х    | Port B5            | PWM-ART Input Capture 1  |                        |

| 11     | -      | •      | PB6 / ARTIC2      | I/O | $C_T$                   |      | Х     | е   | i3    |     | Х   | Х    | Port B6            | PWM-ART Input Capture 2  |                        |

| 12     | -      | -      | PB7               | I/O | $C_T$                   |      | Χ     |     | ei3   |     | Х   | Х    | Port B7            |                          |                        |

| 13     | 7      | 31     | PD0/AIN0          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D0            | ADC Analog Input 0       |                        |

| 14     | 8      | 32     | PD1/AIN1          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D1            | ADC Analog Input 1       |                        |

| 15     | 9      | -      | PD2/AIN2          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D2            | ADC Analog Input 2       |                        |

| 16     | 10     | -      | PD3/AIN3          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D3            | ADC Analog Input 3       |                        |

| 17     | 11     | •      | PD4/AIN4          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D4            | ADC Analog Input 4       |                        |

| 18     | 12     | -      | PD5/AIN5          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D5            | ADC Analog Input 5       |                        |

| 19     | -      | -      | PD6/AIN6          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D6            | ADC Analog Input 6       |                        |

| 20     | -      | -      | PD7/AIN7          | I/O | $C_T$                   |      | Х     | Х   |       | Х   | Х   | Х    | Port D7            | ADC Analog Input 7       |                        |

| 21     | 13     | 1      | V <sub>AREF</sub> | Ι   |                         |      |       |     |       |     |     |      | Analog R           | eference Voltage for ADC |                        |

| 22     | 14     | 2      | V <sub>SSA</sub>  | S   |                         |      |       |     |       |     |     |      | Analog G           | iround Voltage           |                        |

# Table 2. Device Pin Description

ISTICS for more details.

**۲**۲

3. OSC1 and OSC2 pins connect a crystal/ceramic resonator, or an external source to the on-chip oscillator; see Section 1 DESCRIPTION and Section 12.5 CLOCK AND TIMING CHARACTERISTICS for more details.

4. On the chip, each I/O port may have up to 8 pads:

- ads that are not bonded to external pins are forced by hardware in input pull-up configuration after reset.

The configuration of these pads must be kept at reset state to avoid added current consumption.

- 5. Pull-up always activated on PE2 see limitation Section 15.4.6.

6. It is mandatory to connect all available  $V_{DD}$  and  $V_{REF}$  pins to the supply voltage and all  $V_{SS}$  and  $V_{SSA}$  pins to ground.

# FLASH PROGRAM MEMORY (Cont'd)

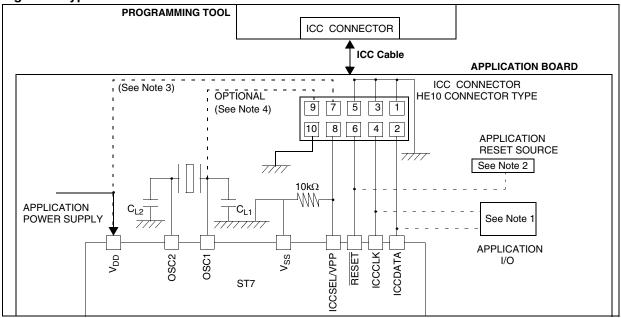

# 4.4 ICC Interface

ICC needs a minimum of 4 and up to 6 pins to be connected to the programming tool (see Figure 6). These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

#### Figure 6. Typical ICC Interface

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input/output serial data pin

- ICCSEL/V<sub>PP</sub>: programming voltage

- OSC1(or OSCIN): main clock input for external source (optional)

- V<sub>DD</sub>: application board power supply (optional, see Figure 6, Note 3)

#### Notes:

1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

2. During the IC<u>C</u> session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

3. The use of Pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

4. Pin 9 has to be connected to the OSC1 or OS-CIN pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

57

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

## 6.4.2 Auxiliary Voltage Detector (AVD)

The Voltage Detector function (AVD) is based on an analog comparison between a V<sub>IT-(AVD)</sub> and V<sub>IT+(AVD)</sub> reference value and the V<sub>DD</sub> main supply or the external EVD pin voltage level (V<sub>EVD</sub>). The V<sub>IT</sub> reference value for falling voltage is lower than the V<sub>IT+</sub> reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

**Caution**: The AVD function is active only if the LVD is enabled through the option byte.

#### 6.4.2.1 Monitoring the V<sub>DD</sub> Main Supply

57/

This mode is selected by clearing the AVDS bit in the SICSR register.

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see section 14.1 on page 175).

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{IT+(AVD)}$  or  $V_{IT-(AVD)}$  threshold (AVDF bit toggles).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 16.

The interrupt on the rising edge is used to inform the application that the  $V_{DD}$  warning state is over.

If the voltage rise time  $t_{\rm rv}$  is less than 256 or 4096 CPU cycles (depending on the reset delay selected by option byte), no AVD interrupt will be generated when  $V_{\rm IT+(AVD)}$  is reached.

If t<sub>rv</sub> is greater than 256 or 4096 cycles then:

- If the AVD interrupt is enabled before the  $V_{IT+(AVD)}$  threshold is reached, then 2 AVD interrupts will be received: the first when the AVDIE bit is set, and the second when the threshold is reached.

- If the AVD interrupt is enabled after the  $V_{\text{IT}+(\text{AVD})}$  threshold is reached then only one AVD interrupt will occur.

Figure 16. Using the AVD to Monitor V<sub>DD</sub> (AVDS bit=0)

# INTERRUPTS (Cont'd)

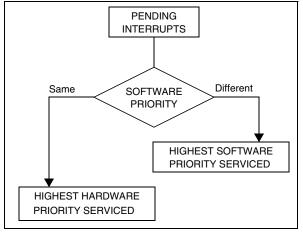

## Servicing Pending Interrupts

As several interrupts can be pending at the same time, the interrupt to be taken into account is determined by the following two-step process:

- the highest software priority interrupt is serviced,

- if several interrupts have the same software priority then the interrupt with the highest hardware priority is serviced first.

Figure 19 describes this decision process.

## Figure 19. Priority Decision Process

When an interrupt request is not serviced immediately, it is latched and then processed when its software priority combined with the hardware priority becomes the highest one.

**Note 1**: The hardware priority is exclusive while the software one is not. This allows the previous process to succeed with only one interrupt.

**Note 2**: TLI, RESET and TRAP can be considered as having the highest software priority in the decision process.

#### **Different Interrupt Vector Sources**

Two interrupt source types are managed by the ST7 interrupt controller: the non-maskable type (RESET, TRAP) and the maskable type (external or from internal peripherals).

### **Non-Maskable Sources**

These sources are processed regardless of the state of the 11 and 10 bits of the CC register (see Figure 18). After stacking the PC, X, A and CC registers (except for RESET), the corresponding vector is loaded in the PC register and the 11 and 10 bits of the CC are set to disable interrupts (level 3). These sources allow the processor to exit HALT mode.

TRAP (Non Maskable Software Interrupt)

This software interrupt is serviced when the TRAP instruction is executed. It will be serviced according to the flowchart in Figure 18.

Caution: TRAP can be interrupted by a TLI.

RESET

The RESET source has the highest priority in the ST7. This means that the first current routine has the highest software priority (level 3) and the highest hardware priority.

See the RESET chapter for more details.

#### **Maskable Sources**

Maskable interrupt vector sources can be serviced if the corresponding interrupt is enabled and if its own interrupt software priority (in ISPRx registers) is higher than the one currently being serviced (I1 and I0 in CC register). If any of these two conditions is false, the interrupt is latched and thus remains pending.

TLI (Top Level Hardware Interrupt)

This hardware interrupt occurs when a specific edge is detected on the dedicated TLI pin. It will be serviced according to the flowchart in Figure 18 as a trap.

**Caution**: A TRAP instruction must not be used in a TLI service routine.

External Interrupts

External interrupts allow the processor to exit from HALT low power mode. External interrupt sensitivity is software selectable through the External Interrupt Control register (EICR).

External interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

If several input pins of a group connected to the same interrupt line are selected simultaneously, these will be logically ORed.

Peripheral Interrupts

Usually the peripheral interrupts cause the MCU to exit from HALT mode except those mentioned in the "Interrupt Mapping" table. A peripheral interrupt occurs when a specific flag is set in the peripheral status registers and if the corresponding enable bit is set in the peripheral control register. The general sequence for clearing an interrupt is based on an access to the status register followed by a read or write to an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (i.e. waiting for being serviced) will therefore be lost if the clear sequence is executed.

57

# POWER SAVING MODES (Cont'd)

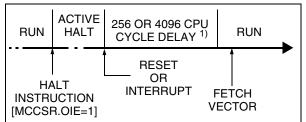

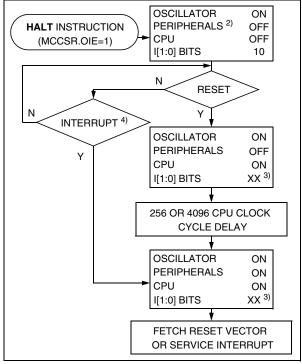

# 8.4 ACTIVE-HALT AND HALT MODES

ACTIVE-HALT and HALT modes are the two lowest power consumption modes of the MCU. They are both entered by executing the 'HALT' instruction. The decision to enter either in ACTIVE-HALT or HALT mode is given by the MCC/RTC interrupt enable flag (OIE bit in MCCSR register).

| MCCSR<br>OIE bit | Power Saving Mode entered when HALT<br>instruction is executed |

|------------------|----------------------------------------------------------------|

| 0                | HALT mode                                                      |

| 1                | ACTIVE-HALT mode                                               |

## 8.4.1 ACTIVE-HALT MODE

ACTIVE-HALT mode is the lowest power consumption mode of the MCU with a real time clock available. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is set (see section 10.2 on page 57 for more details on the MCCSR register).

The MCU can exit ACTIVE-HALT mode on reception of an MCC/RTC interrupt or a RESET. When exiting ACTIVE-HALT mode by means of an interrupt, no 256 or 4096 CPU cycle delay occurs. The CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 27).

When entering ACTIVE-HALT mode, the I[1:0] bits in the CC register are forced to '10b' to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In ACTIVE-HALT mode, only the main oscillator and its associated counter (MCC/RTC) are running to keep a wake-up time base. All other peripherals are not clocked except those which get their clock supply from another clock generator (such as external or auxiliary oscillator).

The safeguard against staying locked in ACTIVE-HALT mode is provided by the oscillator interrupt.

**Note:** As soon as the interrupt capability of one of the oscillators is selected (MCCSR.OIE bit set), entering ACTIVE-HALT mode while the Watchdog is active does not generate a RESET.

This means that the device cannot spend more than a defined delay in this power saving mode.

**CAUTION:** When exiting ACTIVE-HALT mode following an MCC/RTC interrupt, OIE bit of MCCSR register must not be cleared before  $t_{DELAY}$  after the interrupt occurs ( $t_{DELAY}$  = 256 or 4096  $t_{CPU}$  de-

57

lay depending on option byte). Otherwise, the ST7 enters HALT mode for the remaining  $t_{\mbox{\scriptsize DELAY}}$  period.

#### Figure 26. ACTIVE-HALT Timing Overview

#### Figure 27. ACTIVE-HALT Mode Flow-chart

#### Notes:

1. This delay occurs only if the MCU exits ACTIVE-HALT mode by means of a RESET.

2. Peripheral clocked with an external clock source can still be active.

3. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and restored when the CC register is popped.

4. Only the MCC/RTC interrupt can exit the MCU from ACTIVE-HALT mode.

# MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

#### 10.2.5 Low Power Modes

| Mode            | Description                                                                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT            | No effect on MCC/RTC peripheral.<br>MCC/RTC interrupt cause the device to exit<br>from WAIT mode.                                                       |

| ACTIVE-<br>HALT | No effect on MCC/RTC counter (OIE bit is<br>set), the registers are frozen.<br>MCC/RTC interrupt cause the device to exit<br>from ACTIVE-HALT mode.     |

| HALT            | MCC/RTC counter and registers are frozen.<br>MCC/RTC operation resumes when the<br>MCU is woken up by an interrupt with "exit<br>from HALT" capability. |

# 10.2.6 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event          | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------|---------------|--------------------------|----------------------|----------------------|

| Time base overflow event | OIF           | OIE                      | Yes                  | No <sup>1)</sup>     |

### Note:

The MCC/RTC interrupt wakes up the MCU from ACTIVE-HALT mode, not from HALT mode.

# 10.2.7 Register Description MCC CONTROL/STATUS REGISTER (MCCSR) Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| мсо | CP1 | CP0 | SMS | TB1 | TB0 | OIE | OIF |

|     |     |     |     |     |     |     |     |

Bit 7 = MCO Main clock out selection

This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.

- 0: MCO alternate function disabled (I/O pin free for general-purpose I/O)

- 1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

**Note**: To reduce power consumption, the MCO function is not active in ACTIVE-HALT mode.

## Bit 6:5 = **CP[1:0]** CPU clock prescaler

These bits select the CPU clock prescaler which is applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC2</sub> / 2         | 0   | 0   |

| f <sub>OSC2</sub> / 4         | 0   | 1   |

| f <sub>OSC2</sub> / 8         | 1   | 0   |

| f <sub>OSC2</sub> / 16        | 1   | 1   |

#### Bit 4 = **SMS** *Slow mode select*

This bit is set and cleared by software. 0: Normal mode.  $f_{CPU} = f_{OSC2}$ 1: Slow mode.  $f_{CPU}$  is given by CP1, CP0 See Section 8.2 SLOW MODE and Section 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) for more details.

# Bit 3:2 = **TB[1:0]** *Time base control*

These bits select the programmable divider time base. They are set and cleared by software.

| Counter   | Time                    | TB1                     | TB0 |     |

|-----------|-------------------------|-------------------------|-----|-----|

| Prescaler | f <sub>OSC2</sub> =4MHz | f <sub>OSC2</sub> =8MHz | 101 | 100 |

| 16000     | 4ms                     | 2ms                     | 0   | 0   |

| 32000     | 8ms                     | 4ms                     | 0   | 1   |

| 80000     | 20ms                    | 10ms                    | 1   | 0   |

| 200000    | 50ms                    | 25ms                    | 1   | 1   |

A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real time clock.

Bit 1 = **OIE** Oscillator interrupt enable

This bit set and cleared by software.

0: Oscillator interrupt disabled

1: Oscillator interrupt enabled

This interrupt can be used to exit from ACTIVE-HALT mode.

When this bit is set, calling the ST7 software HALT instruction enters the ACTIVE-HALT power saving mode.

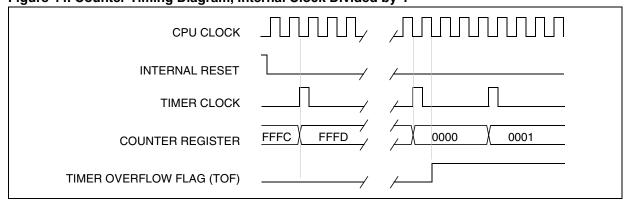

#### **16-BIT TIMER** (Cont'd)

| rigule 45. Counter Thinking Diagram, m | ternar olock brvaca by 2                        |

|----------------------------------------|-------------------------------------------------|

| CPU CLOCK                              |                                                 |

| INTERNAL RESET                         |                                                 |

| TIMER CLOCK                            |                                                 |

| –<br>COUNTER REGISTER –                | \ FFFD\ FFFE\ FFFF\ 0000 \ 0001 \ 0002 \ 0003 \ |

| TIMER OVERFLOW FLAG (TOF)              |                                                 |

# Figure 44. Counter Timing Diagram, Internal Clock Divided by 4

Figure 42 Counter Timing Diagram Internal Clock Divided by 2

## Figure 45. Counter Timing Diagram, Internal Clock Divided By 8

| CPU CLOCK                 |                |

|---------------------------|----------------|

| INTERNAL RESET            | 1              |

| TIMER CLOCK               |                |

| COUNTER REGISTER          | FFFC FFFD 0000 |

| TIMER OVERFLOW FLAG (TOF) |                |

Note: The MCU is in reset state when the internal reset signal is high, when it is low the MCU is running.

# SERIAL PERIPHERAL INTERFACE (Cont'd)

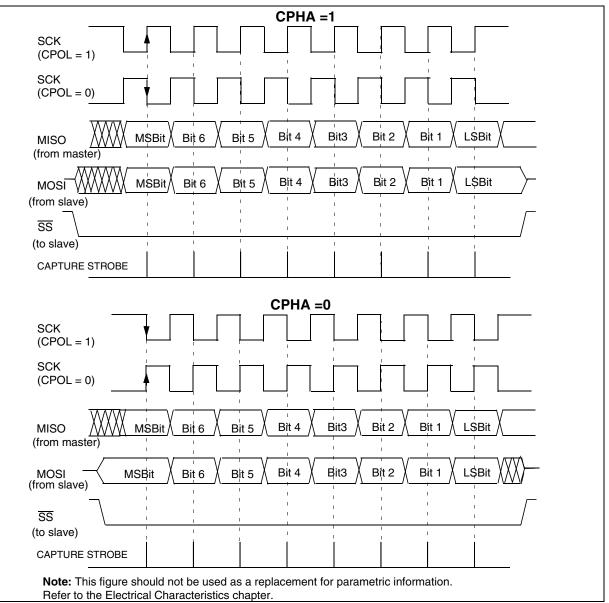

#### 10.5.4 Clock Phase and Clock Polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 57).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge

Figure 57, shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin, the MOSI pin are directly connected between the master and the slave device.

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

# Figure 57. Data Clock Timing Diagram

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

# 10.6.7 Register Description

#### STATUS REGISTER (SCISR) Read Only

Reset Value: 1100 0000 (C0h)

| 7    |    |      |      |    |    |    | 0  |

|------|----|------|------|----|----|----|----|

| TDRE | тс | RDRF | IDLE | OR | NF | FE | PE |

#### Bit 7 = **TDRE** *Transmit data register empty.*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register

1: Data is transferred to the shift register

**Note:** Data is not transferred to the shift register unless the TDRE bit is cleared.

#### Bit 6 = **TC** *Transmission complete.*

This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = **RDRF** *Received data ready flag.*

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detect.*

This bit is set by hardware when a Idle Line is detected. An interrupt is generated if the ILIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Idle Line is detected

1: Idle Line is detected

**Note:** The IDLE bit is not set again until the RDRF bit has been set itself (that is, a new idle line occurs).

#### Bit 3 = **OR** Overrun error.

This bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register while RDRF = 1. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error is detected

**Note:** When this bit is set RDR register content is not lost but the shift register is overwritten.

#### Bit 2 = NF Noise flag.

This bit is set by hardware when noise is detected on a received frame. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No noise is detected

1: Noise is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = **FE** Framing error.

This bit is set by hardware when a de-synchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error is detected

1: Framing error or break character is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it will be transferred and only the OR bit will be set.

#### Bit 0 = **PE** Parity error.

This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register. 0: No parity error

1: Parity error

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

## Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever

TDRE=1 in the SCISR register

Bit 6 = TCIE *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

## Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

#### Bit 4 = **ILIE** *Idle line interrupt enable.*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

#### Bit 3 = **TE** *Transmitter enable*.

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

#### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**CAUTION:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

#### Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

## Bit 1 = **RWU** Receiver wake-up.

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in Active mode

- 1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wake-up by idle line detection.

#### Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

#### **10.8.3 Functional Description**

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{AREF}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the alloted time.

## 10.8.3.1 A/D Converter Configuration

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the «I/O ports» chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

- Select the CS[3:0] bits to assign the analog channel to convert.

#### 10.8.3.2 Starting the Conversion

In the ADCCSR register:

Set the ADON bit to enable the A/D converter and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH or a write to any bit of the ADCCSR register resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRL register

- 3. Read the ADCDRH register. This clears EOC automatically.

**Note:** The data is not latched, so both the low and the high data register must be read before the next conversion is complete, so it is recommended to disable interrupts while reading the conversion result.

To read only 8 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read the ADCDRH register. This clears EOC automatically.

#### 10.8.3.3 Changing the conversion channel

The application can change channels during conversion. When software modifies the CH[3:0] bits in the ADCCSR register, the current conversion is stopped, the EOC bit is cleared, and the A/D converter starts converting the newly selected channel.

#### 10.8.4 Low Power Modes

**Note:** The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed and between single shot conversions.

| Mode | Description                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on A/D Converter                                                                                                                                                                |

|      | A/D Converter disabled.                                                                                                                                                                   |

| HALT | After wakeup from Halt mode, the A/D<br>Converter requires a stabilization time<br>t <sub>STAB</sub> (see Electrical Characteristics)<br>before accurate conversions can be<br>performed. |

#### 10.8.5 Interrupts

None.

# INSTRUCTION SET OVERVIEW (Cont'd)

# 11.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two submodes:

#### Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

## Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table 27. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressingModesAddressingAddressingAddressing

| Long and Short<br>Instructions | Function                                           |

|--------------------------------|----------------------------------------------------|

| LD                             | Load                                               |

| CP                             | Compare                                            |

| AND, OR, XOR                   | Logical Operations                                 |

| ADC, ADD, SUB, SBC             | Arithmetic Additions/Sub-<br>stractions operations |

| BCP                            | Bit Compare                                        |

| Short Instructions Only    | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| TNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations       |

| SWAP                       | Swap Nibbles                      |

| CALL, JP                   | Call or Jump subroutine           |

#### 11.1.7 Relative mode (Direct, Indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Available Relative<br>Direct/Indirect<br>Instructions | Function         |

|-------------------------------------------------------|------------------|

| JRxx                                                  | Conditional Jump |

| CALLR                                                 | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset is following the opcode.

#### Relative (Indirect)

The offset is defined in memory, which address follows the opcode.

| Mnemo | Description            | Function/Example    | Dst     | Src     | 1 | н | 10 | Ν | Z | С |

|-------|------------------------|---------------------|---------|---------|---|---|----|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |   |   |    |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |   |   |    | Ν | Ζ |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A |   | 0 |    |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |   |   |    | Ν | Ζ | С |

| NOP   | No Operation           |                     |         |         |   |   |    |   |   |   |

| OR    | OR operation           | A = A + M           | А       | М       |   |   |    | Ν | Ζ |   |

| POP   | Day from the Ote of    | pop reg             | reg     | М       |   |   |    |   |   |   |

| POP   | Pop from the Stack     | pop CC              | CC      | М       | 1 | Н | 10 | Ν | Ζ | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |   |   |    |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |   |   |    |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |   |   |    |   |   |   |

| RIM   | Enable Interrupts      | l1:0 = 10 (level 0) |         |         | 1 |   | 0  |   |   |   |

| RLC   | Rotate left true C     | C <= A <= C         | reg, M  |         |   |   |    | Ν | Ζ | С |

| RRC   | Rotate right true C    | C => A => C         | reg, M  |         |   |   |    | Ν | Ζ | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |   |   |    |   |   |   |

| SBC   | Substract with Carry   | A = A - M - C       | А       | М       |   |   |    | Ν | Ζ | С |

| SCF   | Set carry flag         | C = 1               |         |         |   |   |    |   |   | 1 |

| SIM   | Disable Interrupts     | 11:0 = 11 (level 3) |         |         | 1 |   | 1  |   |   |   |

| SLA   | Shift left Arithmetic  | C <= A <= 0         | reg, M  |         |   |   |    | Ν | Z | С |

| SLL   | Shift left Logic       | C <= A <= 0         | reg, M  |         |   |   |    | Ν | Ζ | С |

| SRL   | Shift right Logic      | 0 => A => C         | reg, M  |         |   |   |    | 0 | Ζ | С |

| SRA   | Shift right Arithmetic | A7 => A => C        | reg, M  |         |   |   |    | Ν | Z | С |

| SUB   | Substraction           | A = A - M           | А       | М       |   |   |    | Ν | Ζ | С |

| SWAP  | SWAP nibbles           | A7-A4 <=> A3-A0     | reg, M  |         |   |   |    | Ν | Ζ |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |   |   |    | Ν | Ζ |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         | 1 |   | 1  |   |   |   |

| WFI   | Wait for Interrupt     |                     |         |         | 1 |   | 0  |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | А       | М       |   |   |    | Ν | Ζ |   |

# INSTRUCTION SET OVERVIEW (Cont'd)

57

# **12.5 CLOCK AND TIMING CHARACTERISTICS**

#### Subject to general operating conditions for $V_{DD}$ , $f_{CPU}$ , and $T_A$ .

## 12.5.1 General Timings

| Symbol               | Parameter                                                                                                              | Conditions             | Min  | <b>Typ</b> <sup>1)</sup> | Max  | Unit             |

|----------------------|------------------------------------------------------------------------------------------------------------------------|------------------------|------|--------------------------|------|------------------|

| +                    | t <sub>c(INST)</sub> Instruction cycle time                                                                            |                        | 2    | 3                        | 12   | t <sub>CPU</sub> |

| <sup>t</sup> c(INST) |                                                                                                                        | f <sub>CPU</sub> =8MHz | 250  | 375                      | 1500 | ns               |

| +                    | $t_{v(IT)}  \begin{array}{l} \text{Interrupt reaction time}^{\ 2)} \\ t_{v(IT)} = \Delta t_{c(INST)} + 10 \end{array}$ |                        | 10   |                          | 22   | t <sub>CPU</sub> |

|                      |                                                                                                                        | f <sub>CPU</sub> =8MHz | 1.25 |                          | 2.75 | μS               |

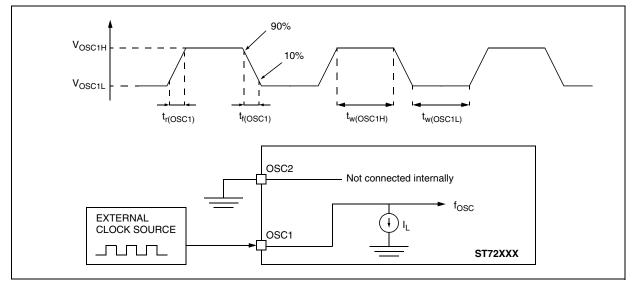

#### 12.5.2 External Clock Source

| Symbol                                         | Parameter                            | Conditions                     | Min                             | Тур | Max                             | Unit |

|------------------------------------------------|--------------------------------------|--------------------------------|---------------------------------|-----|---------------------------------|------|

| V <sub>OSC1H</sub>                             | OSC1 input pin high level voltage    |                                | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     | V <sub>DD</sub>                 | V    |

| V <sub>OSC1L</sub>                             | OSC1 input pin low level voltage     |                                | V <sub>SS</sub>                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | v    |

| t <sub>w(OSC1H)</sub><br>t <sub>w(OSC1L)</sub> | OSC1 high or low time <sup>3)</sup>  | see Figure 76                  | 5                               |     |                                 | ns   |

| t <sub>r(OSC1)</sub><br>t <sub>f(OSC1)</sub>   | OSC1 rise or fall time <sup>3)</sup> |                                |                                 |     | 15                              | 115  |

| ١L                                             | OSC1 Input leakage current           | $V_{SS} \le V_{IN} \le V_{DD}$ |                                 |     | ±1                              | μA   |

# Figure 76. Typical Application with an External Clock Source

#### Notes:

1. Data based on typical application software.

2. Time measured between interrupt event and interrupt vector fetch.  $\Delta t_{c(INST)}$  is the number of  $t_{CPU}$  cycles needed to finish the current instruction execution.

3. Data based on design simulation and/or technology characteristics, not tested in production.

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

# 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as

close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                                                                                                                                                               | Parameter                                      | Conditions                |               | Min | Max    | Unit       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------|---------------|-----|--------|------------|

| f <sub>OSC</sub> Oscillator Frequency <sup>1)</sup>                                                                                                                  | LP: Low powe                                   | r oscillator              | 1             | 2   |        |            |

|                                                                                                                                                                      | MP: Medium p                                   | ower oscillator           | >2            | 4   | MHz    |            |

|                                                                                                                                                                      | MS: Medium speed oscillator                    |                           | >4            | 8   | IVITIZ |            |

|                                                                                                                                                                      |                                                | HS: High speed oscillator |               | >8  | 16     |            |

| R <sub>F</sub>                                                                                                                                                       | Feedback resistor <sup>2)</sup>                |                           |               | 20  | 40     | kΩ         |

|                                                                                                                                                                      | Decommended load conseitence ver               | R <sub>S</sub> =200Ω      | LP oscillator | 22  | 56     |            |

| C <sub>L1</sub><br>C <sub>L2</sub><br>Recommended load capacitance ver-<br>sus equivalent serial resistance of the<br>crystal or ceramic resonator (R <sub>S</sub> ) |                                                | R <sub>S</sub> =200Ω      | MP oscillator | 22  | 46     | <b>"</b> Г |

|                                                                                                                                                                      |                                                | R <sub>S</sub> =200Ω      | MS oscillator | 18  | 33     | pF         |

|                                                                                                                                                                      | crystal or ceramic resonator (R <sub>S</sub> ) | R <sub>S</sub> =100Ω      | HS oscillator | 15  | 33     |            |

| Symbol         | Parameter            |                                                         | Тур                                                              | Max                     | Unit                     |    |

|----------------|----------------------|---------------------------------------------------------|------------------------------------------------------------------|-------------------------|--------------------------|----|

| i <sub>2</sub> | OSC2 driving current | V <sub>DD</sub> =5V<br>V <sub>IN</sub> =V <sub>SS</sub> | LP oscillator<br>MP oscillator<br>MS oscillator<br>HS oscillator | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μA |

#### Notes:

57/

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

# **12.9 CONTROL PIN CHARACTERISTICS**

# 12.9.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                  | Parameter                                        | Conditions                        |                       | Min                              | Тур | Max                              | Unit |

|-------------------------|--------------------------------------------------|-----------------------------------|-----------------------|----------------------------------|-----|----------------------------------|------|

| V <sub>IL</sub>         | Input low level voltage 1)                       |                                   |                       |                                  |     | $0.16 \mathrm{xV}_{\mathrm{DD}}$ | V    |

| V <sub>IH</sub>         | Input high level voltage <sup>1)</sup>           |                                   |                       | $0.85 \mathrm{xV}_{\mathrm{DD}}$ |     |                                  | v    |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis <sup>2)</sup> |                                   |                       |                                  | 2.5 |                                  | V    |

| V <sub>OL</sub>         | Output low level voltage 3)                      | V <sub>DD</sub> =5V               | I <sub>IO</sub> =+2mA |                                  | 0.2 | 0.5                              | v    |

| I <sub>IO</sub>         | Input current on RESET pin                       |                                   |                       |                                  | 2   |                                  | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor                 |                                   |                       | 20                               | 30  | 120                              | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration                   | Stretch applied on external pulse |                       | 0                                |     | 42 <sup>6)</sup>                 | μs   |

|                         |                                                  | Internal reset sources            |                       | 20                               | 30  | 42 <sup>6)</sup>                 | μs   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)                |                                   |                       | 2.5                              |     |                                  | μs   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>5)</sup>           |                                   |                       |                                  | 200 |                                  | ns   |

#### Notes:

57/

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

3. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overrightarrow{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(\text{RSTL})in}$  can be ignored.

5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

6. Data guaranteed by design, not tested in production.

# 12.12 10-BIT ADC CHARACTERISTICS

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                               | Conditions                            | Min       | Тур     | Max                                  | Unit               |

|-------------------|-----------------------------------------------------------------------------------------|---------------------------------------|-----------|---------|--------------------------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                     |                                       | 0.4       |         | 2                                    | MHz                |

| V <sub>AREF</sub> | Analog reference voltage                                                                | $0.7^*V_{DD} \le V_{AREF} \le V_{DD}$ | 3.8       |         | V <sub>DD</sub><br>V <sub>AREF</sub> | V                  |

| V <sub>AIN</sub>  | Conversion voltage range 1)                                                             |                                       | $V_{SSA}$ |         |                                      |                    |

| R <sub>AIN</sub>  | External input impedance                                                                |                                       |           |         | see                                  | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                      |                                       |           |         | Figure 96<br>and                     | pF                 |

| f <sub>AIN</sub>  | Variation freq. of analog input signal                                                  |                                       |           |         | Figure 97                            | Hz                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                      |                                       |           | 12      |                                      | pF                 |

| t <sub>ADC</sub>  | Conversion time (Sample+Hold)<br>f <sub>CPU</sub> =8MHz, SPEED=0 f <sub>ADC</sub> =2MHz |                                       | 7.5       |         |                                      | μS                 |

| t <sub>ADC</sub>  | - No of sample capacitor loading cycles<br>- No. of Hold conversion cycles              |                                       |           | 4<br>11 |                                      | 1/f <sub>ADC</sub> |

#### Notes:

57/

1. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

2. Injecting negative current on any of the analog input pins significantly reduces the accuracy of any conversion being performed on any analog input. Analog pins can be protected against negative injection by adding a Schottky diode (pin to ground). Injecting negative current on digital input pins degrades ADC accuracy especially if performed on a pin close to the analog input pins. Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 12.8 does not affect the ADC accuracy.