Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                     |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 48                                                                      |

| Program Memory Size        | 60KB (60K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321ar9t6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

-

\_

| 8.4     | ACTIVE-HALT AND HALT MODES                                                                                                                                                          | . 43                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|         | 8.4.1 ACTIVE-HALT MODE                                                                                                                                                              | . 43                                                                 |

|         | 8.4.2 HALT MODE                                                                                                                                                                     | . 44                                                                 |

| 9 I/O P | ORTS                                                                                                                                                                                | . 46                                                                 |

| 9.1     | INTRODUCTION                                                                                                                                                                        | . 46                                                                 |

| 9.2     | FUNCTIONAL DESCRIPTION                                                                                                                                                              | . 46                                                                 |

|         | 9.2.1 Input Modes                                                                                                                                                                   | . 46                                                                 |

|         | 9.2.2 Output Modes                                                                                                                                                                  | . 46                                                                 |

|         | 9.2.3 Alternate Functions                                                                                                                                                           | . 46                                                                 |

| 9.3     | I/O PORT IMPLEMENTATION                                                                                                                                                             | . 49                                                                 |

| 9.4     | LOW POWER MODES                                                                                                                                                                     | . 49                                                                 |

|         | INTERRUPTS                                                                                                                                                                          |                                                                      |

| 5.5     |                                                                                                                                                                                     |                                                                      |

| 10.01   | 9.5.1 I/O Port Implementation                                                                                                                                                       |                                                                      |

|         |                                                                                                                                                                                     |                                                                      |

| 10.1    | WATCHDOG TIMER (WDG)                                                                                                                                                                |                                                                      |

|         | 10.1.1 Introduction                                                                                                                                                                 |                                                                      |

|         | 10.1.2 Main Features                                                                                                                                                                |                                                                      |

|         | 10.1.3 Functional Description                                                                                                                                                       |                                                                      |

|         | 10.1.4 How to Program the Watchdog Timeout                                                                                                                                          |                                                                      |

|         | 10.1.5 Low Power Modes                                                                                                                                                              |                                                                      |

|         | 10.1.6 Hardware Watchdog Option                                                                                                                                                     |                                                                      |

|         | 10.1.7 Using Halt Mode with the WDG (WDGHALT option)                                                                                                                                |                                                                      |

|         | 10.1.8 Interrupts                                                                                                                                                                   |                                                                      |

| 10.0    | 10.1.9 Register Description                                                                                                                                                         |                                                                      |

| 10.2    | 2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) .                                                                                                                 |                                                                      |

|         | 10.2.1 Programmable CPU Clock Prescaler                                                                                                                                             |                                                                      |

|         | 10.2.2 Clock-out Capability                                                                                                                                                         |                                                                      |

|         | 10.2.3 Real Time Clock Timer (RTC)                                                                                                                                                  |                                                                      |

|         | 10.2.4 Beeper                                                                                                                                                                       |                                                                      |

|         | 10.2.5 Low Power Modes                                                                                                                                                              |                                                                      |

|         | 10.2.6 Interrupts                                                                                                                                                                   |                                                                      |

| 10.0    | 10.2.7 Register Description                                                                                                                                                         |                                                                      |

| 10.3    | 3 PWM AUTO-RELOAD TIMER (ART)                                                                                                                                                       |                                                                      |

|         | 10.3.1 Introduction                                                                                                                                                                 |                                                                      |

|         | 10.3.2 Functional Description                                                                                                                                                       |                                                                      |

| 10      | 10.3.3 Register Description                                                                                                                                                         |                                                                      |

| 10.4    | 16-BIT TIMER                                                                                                                                                                        |                                                                      |

|         | 10.4.1 Introduction                                                                                                                                                                 | 60                                                                   |

|         |                                                                                                                                                                                     |                                                                      |

|         | 10.4.2 Main Features                                                                                                                                                                | . 69                                                                 |

|         | 10.4.2 Main Features10.4.3 Functional Description                                                                                                                                   | . 69<br>. 69                                                         |

|         | 10.4.2 Main Features10.4.3 Functional Description10.4.4 Low Power Modes                                                                                                             | . 69<br>. 69<br>. 81                                                 |

|         | 10.4.2 Main Features10.4.3 Functional Description10.4.4 Low Power Modes10.4.5 Interrupts                                                                                            | . 69<br>. 69<br>. 81<br>. 81                                         |

|         | 10.4.2Main Features10.4.3Functional Description10.4.4Low Power Modes10.4.5Interrupts10.4.6Summary of Timer Modes                                                                    | . 69<br>. 69<br>. 81<br>. 81<br>. 81                                 |

|         | 10.4.2Main Features10.4.3Functional Description10.4.4Low Power Modes10.4.5Interrupts10.4.6Summary of Timer Modes10.4.7Register Description                                          | . 69<br>. 69<br>. 81<br>. 81<br>. 81<br>. 81                         |

| 10.5    | 10.4.2 Main Features10.4.3 Functional Description10.4.4 Low Power Modes10.4.5 Interrupts10.4.6 Summary of Timer Modes10.4.7 Register Description5 SERIAL PERIPHERAL INTERFACE (SPI) | . 69<br>. 69<br>. 81<br>. 81<br>. 81<br>. 82<br>. 88                 |

| 10.5    | 10.4.2Main Features10.4.3Functional Description10.4.4Low Power Modes10.4.5Interrupts10.4.6Summary of Timer Modes10.4.7Register Description                                          | . 69<br>. 69<br>. 81<br>. 81<br>. 81<br>. 81<br>. 82<br>. 88<br>. 88 |

# PIN DESCRIPTION (Cont'd)

For external pin connection guidelines, refer to See "ELECTRICAL CHARACTERISTICS" on page 138. Legend / Abbreviations for Table 2 :

| -                |                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре:            | I = input, O = output, S = supply                                                                                                                                                                   |

| Input level:     | A = Dedicated analog input                                                                                                                                                                          |

| In/Output level: | $\begin{array}{l} C = CMOS \; 0.3 V_{DD} / 0.7 V_{DD} \\ C_T = CMOS \; 0.3 V_{DD} / 0.7 V_{DD} \; \text{with input trigger} \\ T_T = TTL \; 0.8 V / 2 V \; \text{with Schmitt trigger} \end{array}$ |

| Output level:    | HS = 20mA high sink (on N-buffer only)                                                                                                                                                              |

Port and control configuration:

- Input: float = floating, wpu = weak pull-up, int = interrupt <sup>1</sup>), ana = analog

- Output:  $OD = open drain^{2}$ , PP = push-pull

Refer to "I/O PORTS" on page 46 for more details on the software configuration of the I/O ports.

The RESET configuration of each pin is shown in bold. This configuration is valid as long as the device is in reset state.

| F      | Pin n  | 0      |                   |      | Le    | evel   |       |     | Ρ   | ort |     |      | Main               |                          |

|--------|--------|--------|-------------------|------|-------|--------|-------|-----|-----|-----|-----|------|--------------------|--------------------------|

| P64    | P44    | P32    | Pin Name          | Type | ut    | out    |       | Inp | out |     | Out | tput | function<br>(after | Alternate function       |

| LQFP64 | LQFP44 | LQFP32 |                   |      | Input | Output | float | ndm | int | ana | OD  | РР   | reset)             |                          |

| 1      | -      | -      | PE4 (HS)          | I/O  | $C_T$ | HS     | Х     | Х   |     |     | Х   | Х    | Port E4            |                          |

| 2      | -      | -      | PE5 (HS)          | I/O  | $C_T$ | HS     | Х     | Х   |     |     | Х   | Х    | Port E5            |                          |

| 3      | -      | -      | PE6 (HS)          | I/O  | $C_T$ | HS     | Х     | Х   |     |     | Х   | Х    | Port E6            |                          |

| 4      | -      | -      | PE7 (HS)          | I/O  | $C_T$ | HS     | Х     | Х   |     |     | Х   | Х    | Port E7            |                          |

| 5      | 2      | 28     | PB0/PWM3          | I/O  | $C_T$ |        | Χ     | е   | i2  |     | Х   | Х    | Port B0            | PWM Output 3             |

| 6      | 3      | -      | PB1/PWM2          | I/O  | $C_T$ |        | Х     | е   | i2  |     | Х   | Х    | Port B1            | PWM Output 2             |

| 7      | 4      | -      | PB2/PWM1          | I/O  | $C_T$ |        | Χ     | е   | i2  |     | Х   | Х    | Port B2            | PWM Output 1             |

| 8      | 5      | 29     | PB3/PWM0          | I/O  | $C_T$ |        | Χ     |     | ei2 |     | Х   | Х    | Port B3            | PWM Output 0             |

| 9      | 6      | 30     | PB4 (HS)/ARTCLK   | I/O  | $C_T$ | HS     | Χ     | е   | i3  |     | Х   | Х    | Port B4            | PWM-ART External Clock   |

| 10     | -      | -      | PB5 / ARTIC1      | I/O  | $C_T$ |        | Х     | е   | i3  |     | Х   | Х    | Port B5            | PWM-ART Input Capture 1  |

| 11     | -      | •      | PB6 / ARTIC2      | I/O  | $C_T$ |        | Х     | е   | i3  |     | Х   | Х    | Port B6            | PWM-ART Input Capture 2  |

| 12     | -      | -      | PB7               | I/O  | $C_T$ |        | Χ     |     | ei3 |     | Х   | Х    | Port B7            |                          |

| 13     | 7      | 31     | PD0/AIN0          | I/O  | $C_T$ |        | Χ     | Х   |     | Х   | Х   | Х    | Port D0            | ADC Analog Input 0       |

| 14     | 8      | 32     | PD1/AIN1          | I/O  | $C_T$ |        | Χ     | Х   |     | Х   | Х   | Х    | Port D1            | ADC Analog Input 1       |

| 15     | 9      | -      | PD2/AIN2          | I/O  | $C_T$ |        | Х     | Х   |     | Х   | Х   | Х    | Port D2            | ADC Analog Input 2       |

| 16     | 10     | -      | PD3/AIN3          | I/O  | $C_T$ |        | Χ     | Х   |     | Х   | Х   | Х    | Port D3            | ADC Analog Input 3       |

| 17     | 11     | •      | PD4/AIN4          | I/O  | $C_T$ |        | Х     | Х   |     | Х   | Х   | Х    | Port D4            | ADC Analog Input 4       |

| 18     | 12     | -      | PD5/AIN5          | I/O  | $C_T$ |        | Х     | Х   |     | Х   | Х   | Х    | Port D5            | ADC Analog Input 5       |

| 19     | -      | -      | PD6/AIN6          | I/O  | $C_T$ |        | Х     | Х   |     | Х   | Х   | Х    | Port D6            | ADC Analog Input 6       |

| 20     | -      | -      | PD7/AIN7          | I/O  | $C_T$ |        | Х     | Х   |     | Х   | Х   | Х    | Port D7            | ADC Analog Input 7       |

| 21     | 13     | 1      | V <sub>AREF</sub> | Ι    |       |        |       |     |     |     |     |      | Analog R           | eference Voltage for ADC |

| 22     | 14     | 2      | V <sub>SSA</sub>  | S    |       |        |       |     |     |     |     |      | Analog G           | iround Voltage           |

# Table 2. Device Pin Description

| F      | Pin n  | 0      |                          |      | Le      | evel   |       |     | Р   | ort |     |      | Main                                                                                                                                                                                                                                                                                               |                                                         |  |  |

|--------|--------|--------|--------------------------|------|---------|--------|-------|-----|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| P64    | P44    | P32    | Pin Name                 | Type | ut      | put    |       | Inp | out |     | Out | tput | function<br>(after                                                                                                                                                                                                                                                                                 | Alternate function                                      |  |  |

| LQFP64 | LQFP44 | LQFP32 |                          |      | Input   | Output | float | ndm | int | ana | OD  | д    | reset)                                                                                                                                                                                                                                                                                             |                                                         |  |  |

| 45     | -      | -      | PA2                      | I/O  | $C_T$   |        | Χ     | e   | i0  |     | Х   | Х    | Port A2                                                                                                                                                                                                                                                                                            |                                                         |  |  |

| 46     | 31     | 16     | PA3 (HS)                 | I/O  | $C_T$   | HS     | Χ     |     | ei0 |     | Х   | Х    | Port A3                                                                                                                                                                                                                                                                                            |                                                         |  |  |

| 47     | 32     | -      | V <sub>DD_1</sub>        | S    |         |        |       |     |     |     |     |      | Digital Ma                                                                                                                                                                                                                                                                                         | ain Supply Voltage                                      |  |  |

| 48     | 33     | -      | V <sub>SS_1</sub>        | S    |         |        |       |     |     |     |     |      | Digital G                                                                                                                                                                                                                                                                                          | round Voltage                                           |  |  |

| 49     | 34     | 17     | PA4 (HS)                 | I/O  | $C_{T}$ | HS     | Х     | Х   |     |     | Х   | Х    | Port A4                                                                                                                                                                                                                                                                                            |                                                         |  |  |

| 50     | 35     | -      | PA5 (HS)                 | I/O  | $C_T$   | HS     | Χ     | Х   |     |     | Х   | Х    | Port A5                                                                                                                                                                                                                                                                                            |                                                         |  |  |

| 51     | 36     | 18     | PA6 (HS)/SDAI            | I/O  | $C_{T}$ | HS     | Х     |     |     |     | Т   |      | Port A6                                                                                                                                                                                                                                                                                            | I <sup>2</sup> C Data <sup>1)</sup>                     |  |  |

| 52     | 37     | 19     | PA7 (HS)/SCLI            | I/O  | $C_{T}$ | HS     | Χ     |     |     |     | Т   |      | Port A7                                                                                                                                                                                                                                                                                            | I <sup>2</sup> C Clock <sup>1)</sup>                    |  |  |

| 53     | 38     | 20     | V <sub>PP</sub> / ICCSEL | I    |         |        |       |     |     |     |     |      | Must be tied low. In flash programming mode, this pin acts as the programming voltage input $V_{PP}$ . See Section 12.9.2 for more details. High voltage must not be applied to ROM devices                                                                                                        |                                                         |  |  |

| 54     | 39     | 21     | RESET                    | I/O  | $C_{T}$ |        |       |     |     |     |     |      | Top priority non maskable interrupt.                                                                                                                                                                                                                                                               |                                                         |  |  |

| 55     | -      | -      | EVD                      |      |         |        |       |     |     |     |     |      | External voltage detector                                                                                                                                                                                                                                                                          |                                                         |  |  |

| 56     | -      | -      | TLI                      | I    | $C_{T}$ |        |       |     | Х   |     |     |      | Top level                                                                                                                                                                                                                                                                                          | Top level interrupt input pin                           |  |  |

| 57     | 40     | 22     | V <sub>SS_2</sub>        | S    |         |        |       |     |     |     |     |      | Digital G                                                                                                                                                                                                                                                                                          | round Voltage                                           |  |  |

| 58     | 41     | 23     | OSC2 <sup>3)</sup>       | I/O  |         |        |       |     |     |     |     |      | Resonato                                                                                                                                                                                                                                                                                           | or oscillator inverter output                           |  |  |

| 59     | 42     | 24     | OSC1 <sup>3)</sup>       | I    |         |        |       |     |     |     |     |      |                                                                                                                                                                                                                                                                                                    | clock input or Resonator os-<br>verter input            |  |  |

| 60     | 43     | 25     | V <sub>DD_2</sub>        | S    |         |        |       |     |     |     |     |      | Digital Ma                                                                                                                                                                                                                                                                                         | ain Supply Voltage                                      |  |  |

| 61     | 44     | 26     | PE0/TDO                  | I/O  | $C_T$   |        | Χ     | Х   |     |     | Х   | Х    | Port E0                                                                                                                                                                                                                                                                                            | SCI Transmit Data Out                                   |  |  |

| 62     | 1      | 27     | PE1/RDI                  | I/O  | $C_{T}$ |        | Х     | Х   |     |     | Х   | Х    | Port E1                                                                                                                                                                                                                                                                                            | SCI Receive Data In                                     |  |  |

|        |        |        | PE2 (Flash device)       |      |         |        |       | x   |     |     |     |      | always in                                                                                                                                                                                                                                                                                          | In Flash devices this port is<br>put with weak pull-up. |  |  |

| 63     | -      | -      | PE2 (ROM device)         | I/O  | CT      |        | x     |     |     |     | x   | x    | Port E2<br><b>Caution:</b> In ROM devices, no weak<br>pull-up present on this port.<br>In LQFP44 this pin is not connected to<br>an internal pull-up like other unbond-<br>ed pins (See note 4). It is recommend-<br>ed to configure it as output push pull<br>to avoid added current consumption. |                                                         |  |  |

| 64     | -      | -      | PE3                      | I/O  | $C_T$   |        | Χ     | Х   |     |     | Х   | Х    | Port E3                                                                                                                                                                                                                                                                                            |                                                         |  |  |

#### Notes:

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. In the open drain output column, "T" defines a true open drain I/O (P-Buffer and protection diode to  $V_{DD}$  are not implemented). See See "I/O PORTS" on page 46. and Section 12.8 I/O PORT PIN CHARACTER-

# INTERRUPTS (Cont'd)

# Table 9. Nested Interrupts Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------------|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|                   |                   | е     | i1    | е     | i0    | M     | 00    | Т     | LI    |

| 0024h             | ISPR0             | l1_3  | 10_3  | l1_2  | 10_2  | 11_1  | 10_1  |       |       |

|                   | Reset Value       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

|                   |                   | S     | PI    |       |       | е     | i3    | ei2   |       |

| 0025h             | ISPR1             | l1_7  | 10_7  | l1_6  | 10_6  | l1_5  | 10_5  | l1_4  | 10_4  |

|                   | Reset Value       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

|                   |                   | A۱    | /D    | S     | CI    | TIME  | ER B  | TIME  | ER A  |

| 0026h             | ISPR2             | 11_11 | 10_11 | l1_10 | l0_10 | l1_9  | 10_9  | l1_8  | 10_8  |

|                   | Reset Value       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

|                   |                   |       |       |       |       | PWN   | IART  | 12    | C     |

| 0027h             | ISPR3             |       |       |       |       | 11_13 | l0_13 | l1_12 | 10_12 |

|                   | Reset Value       | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     |

| 0028h             | EICR              | IS11  | IS10  | IPB   | IS21  | IS20  | IPA   | TLIS  | TLIE  |

| 002011            | Reset Value       | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

# **ON-CHIP PERIPHERALS** (Cont'd)

# INPUT CAPTURE CONTROL / STATUS REGISTER (ARTICCSR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |     |     |      |      |     | 0   |

|---|---|-----|-----|------|------|-----|-----|

| 0 | 0 | CS2 | CS1 | CIE2 | CIE1 | CF2 | CF1 |

Bit 7:6 = Reserved, always read as 0.

#### Bit 5:4 = CS[2:1] Capture Sensitivity

These bits are set and cleared by software. They determine the trigger event polarity on the corresponding input capture channel.

0: Falling edge triggers capture on channel x.

1: Rising edge triggers capture on channel x.

Bit 3:2 = **CIE[2:1]** Capture Interrupt Enable

These bits are set and cleared by software. They enable or disable the Input capture channel interrupts independently.

0: Input capture channel x interrupt disabled.

1: Input capture channel x interrupt enabled.

# Bit 1:0 = CF[2:1] Capture Flag

These bits are set by hardware and cleared by software reading the corresponding ARTICRx register. Each CFx bit indicates that an input capture x has occurred.

0: No input capture on channel x.

1: An input capture has occurred on channel x.

# **INPUT CAPTURE REGISTERS (ARTICRx)**

Read only

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| IC7 | IC6 | IC5 | IC4 | IC3 | IC2 | IC1 | IC0 |

Bit 7:0 = IC[7:0] Input Capture Data

These read only bits are set and cleared by hardware. An ARTICRx register contains the 8-bit auto-reload counter value transferred by the input capture channel x event.

## **16-BIT TIMER** (Cont'd)

# 10.4.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are two output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC*i*E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

#### Procedure:

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 1).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OCiR register and CR register:

OCF*i* bit is set.

57/

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC} i \text{R} = \frac{\Delta t * f_{\text{CPU}}}{\text{PRESC}}$$

Where:

- $\Delta t$  = Output compare period (in seconds)

- f<sub>CPU</sub> = CPU clock frequency (in hertz)

- PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 1)

If the timer clock is an external clock, the formula is:

$$\Delta \text{ OC}i\text{R} = \Delta t * f_{\text{EXT}}$$

Where:

$\Delta t$  = Output compare period (in seconds)

$f_{EXT}$  = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

- 1. Reading the SR register while the OCF*i* bit is set.

- 2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCF*i* bit from being set between the time it is read and the write to the OC*i*R register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

# SERIAL COMMUNICATIONS INTERFACE (Cont'd)

# **10.6.4.9 Clock Deviation Causes**

The causes which contribute to the total deviation are:

- D<sub>TRA</sub>: Deviation due to transmitter error (Local oscillator error of the transmitter or the transmitter is transmitting at a different baud rate).

- D<sub>QUANT</sub>: Error due to the baud rate quantization of the receiver.

- D<sub>REC</sub>: Deviation of the local oscillator of the receiver: This deviation can occur during the reception of one complete SCI message assuming that the deviation has been compensated at the beginning of the message.

- D<sub>TCL</sub>: Deviation due to the transmission line (generally due to the transceivers)

All the deviations of the system should be added and compared to the SCI clock tolerance:

$\mathsf{D}_{\mathsf{TRA}} + \mathsf{D}_{\mathsf{QUANT}} + \mathsf{D}_{\mathsf{REC}} + \mathsf{D}_{\mathsf{TCL}} < 3.75\%$

## 10.6.4.10 Noise Error Causes

See also description of Noise error in Section 0.1.4.3.

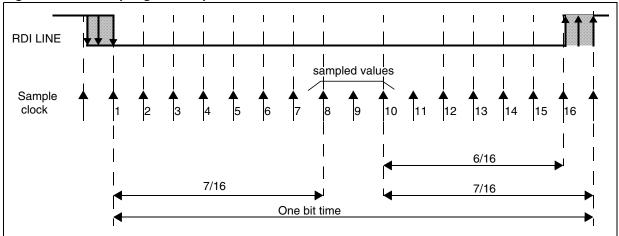

#### Start bit

The noise flag (NF) is set during start bit reception if one of the following conditions occurs:

- 1. A valid falling edge is not detected. A falling edge is considered to be valid if the 3 consecutive samples before the falling edge occurs are detected as '1' and, after the falling edge occurs, during the sampling of the 16 samples, if one of the samples numbered 3, 5 or 7 is detected as a "1".

- 2. During sampling of the 16 samples, if one of the samples numbered 8, 9 or 10 is detected as a "1".

Therefore, a valid Start Bit must satisfy both the above conditions to prevent the Noise Flag getting set.

#### Data Bits

The noise flag (NF) is set during normal data bit reception if the following condition occurs:

During the sampling of 16 samples, if all three samples numbered 8, 9 and 10 are not the same. The majority of the 8th, 9th and 10th samples is considered as the bit value.

Therefore, a valid Data Bit must have samples 8, 9 and 10 at the same value to prevent the Noise Flag getting set.

#### Figure 63. Bit Sampling in Reception Mode

57

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

# Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever

TDRE=1 in the SCISR register

Bit 6 = TCIE *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

# Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

#### Bit 4 = **ILIE** *Idle line interrupt enable.*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

#### Bit 3 = **TE** *Transmitter enable*.

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

#### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**CAUTION:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

#### Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

# Bit 1 = **RWU** Receiver wake-up.

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in Active mode

- 1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wake-up by idle line detection.

#### Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

# I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C STATUS REGISTER 1 (SR1)

Read Only

Reset Value: 0000 0000 (00h)

| 7   |       |     |      |     |      |      | 0  |

|-----|-------|-----|------|-----|------|------|----|

| EVF | ADD10 | TRA | BUSY | BTF | ADSL | M/SL | SB |

#### Bit 7 = **EVF** Event flag.

This bit is set by hardware as soon as an event occurs. It is cleared by software reading SR2 register in case of error event or as described in Figure 66. It is also cleared by hardware when the interface is disabled (PE=0).

#### 0: No event

- 1: One of the following events has occurred:

- BTF=1 (Byte received or transmitted)

- ADSL=1 (Address matched in Slave mode while ACK=1)

- SB=1 (Start condition generated in Master mode)

- AF=1 (No acknowledge received after byte transmission)

- STOPF=1 (Stop condition detected in Slave mode)

- ARLO=1 (Arbitration lost in Master mode)

- BERR=1 (Bus error, misplaced Start or Stop condition detected)

- ADD10=1 (Master has sent header byte)

- Address byte successfully transmitted in Master mode.

Bit 6 = **ADD10** *10-bit addressing in Master mode.* This bit is set by hardware when the master has sent the first byte in 10-bit address mode. It is cleared by software reading SR2 register followed by a write in the DR register of the second address byte. It is also cleared by hardware when the peripheral is disabled (PE=0).

0: No ADD10 event occurred.

1: Master has sent first address byte (header)

#### Bit 5 = TRA Transmitter/Receiver.

When BTF is set, TRA=1 if a data byte has been transmitted. It is cleared automatically when BTF is cleared. It is also cleared by hardware after detection of Stop condition (STOPF=1), loss of bus arbitration (ARLO=1) or when the interface is disabled (PE=0).

0: Data byte received (if BTF=1)

#### 1: Data byte transmitted

#### Bit 4 = **BUSY** Bus busy.

This bit is set by hardware on detection of a Start condition and cleared by hardware on detection of a Stop condition. It indicates a communication in progress on the bus. The BUSY flag of the I2CSR1 register is cleared if a Bus Error occurs.

0: No communication on the bus

1: Communication ongoing on the bus Note:

- The BUSY flag is NOT updated when the interface is disabled (PE=0). This can have consequences when operating in Multimaster mode; i.e. a second active I<sup>2</sup>C master commencing a transfer with an unset BUSY bit can cause a conflict resulting in lost data. A software workaround consists of checking that the I<sup>2</sup>C is not busy before enabling the I<sup>2</sup>C Multimaster cell.

#### Bit 3 = **BTF** Byte transfer finished.

This bit is set by hardware as soon as a byte is correctly received or transmitted with interrupt generation if ITE=1. It is cleared by software reading SR1 register followed by a read or write of DR register. It is also cleared by hardware when the interface is disabled (PE=0).

- Following a byte transmission, this bit is set after reception of the acknowledge clock pulse. In case an address byte is sent, this bit is set only after the EV6 event (See Figure 66). BTF is cleared by reading SR1 register followed by writing the next byte in DR register.

- Following a byte reception, this bit is set after transmission of the acknowledge clock pulse if ACK=1. BTF is cleared by reading SR1 register followed by reading the byte from DR register.

The SCL line is held low while BTF=1.

- 0: Byte transfer not done

- 1: Byte transfer succeeded

Bit 2 = **ADSL** Address matched (Slave mode). This bit is set by hardware as soon as the received slave address matched with the OAR register content or a general call is recognized. An interrupt is generated if ITE=1. It is cleared by software reading SR1 register or by hardware when the interface is disabled (PE=0).

The SCL line is held low while ADSL=1.

- 0: Address mismatched or not received

- 1: Received address matched

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### Bit 1 = M/SL Master/Slave.

This bit is set by hardware as soon as the interface is in Master mode (writing START=1). It is cleared by hardware after detecting a Stop condition on the bus or a loss of arbitration (ARLO=1). It is also cleared when the interface is disabled (PE=0). 0: Slave mode

U. Slave mode

1: Master mode

#### Bit 0 = SB Start bit (Master mode).

This bit is set by hardware as soon as the Start condition is generated (following a write START=1). An interrupt is generated if ITE=1. It is cleared by software reading SR1 register followed by writing the address byte in DR register. It is also cleared by hardware when the interface is disabled (PE=0).

0: No Start condition

1: Start condition generated

# I<sup>2</sup>C STATUS REGISTER 2 (SR2)

# Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |    |       |      |      | 0    |

|---|---|---|----|-------|------|------|------|

| 0 | 0 | 0 | AF | STOPF | ARLO | BERR | GCAL |

Bit 7:5 = Reserved. Forced to 0 by hardware.

#### Bit 4 = **AF** Acknowledge failure.

This bit is set by hardware when no acknowledge is returned. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while AF=1 but by other flags (SB or BTF) that are set at the same time.

- 0: No acknowledge failure

- 1: Acknowledge failure

Note:

When an AF event occurs, the SCL line is not held low; however, the SDA line can remain low if the last bits transmitted are all 0. It is then necessary to release both lines by software.

#### Bit 3 = **STOPF** *Stop detection (Slave mode).*

This bit is set by hardware when a Stop condition is detected on the bus after an acknowledge (if ACK=1). An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0). The SCL line is not held low while STOPF=1.

0: No Stop condition detected

1: Stop condition detected

## Bit 2 = **ARLO** Arbitration lost.

This bit is set by hardware when the interface loses the arbitration of the bus to another master. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

After an ARLO event the interface switches back automatically to Slave mode (M/SL=0).

The SCL line is not held low while ARLO=1.

0: No arbitration lost detected

1: Arbitration lost detected

Note:

- In a Multimaster environment, when the interface is configured in Master Receive mode it does not perform arbitration during the reception of the Acknowledge Bit. Mishandling of the ARLO bit from the I2CSR2 register may occur when a second master simultaneously requests the same data from the same slave and the I<sup>2</sup>C master does not acknowledge the data. The ARLO bit is then left at 0 instead of being set.

#### Bit 1 = **BERR** Bus error.

This bit is set by hardware when the interface detects a misplaced Start or Stop condition. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while BERR=1.

0: No misplaced Start or Stop condition 1: Misplaced Start or Stop condition Note:

If a Bus Error occurs, a Stop or a repeated Start condition should be generated by the Master to re-synchronize communication, get the transmission acknowledged and the bus released for further communication

Bit 0 = GCAL General Call (Slave mode).

This bit is set by hardware when a general call address is detected on the bus while ENGC=1. It is cleared by hardware detecting a Stop condition (STOPF=1) or when the interface is disabled (PE=0).

0: No general call address detected on bus 1: general call address detected on bus

# **11 INSTRUCTION SET**

# **11.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

Table 26. CPU Addressing Mode Overview

so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |          | Syntax              | Destination | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |

|-----------|----------|----------|---------------------|-------------|------------------------------|------------------------|-------------------|

| Inherent  |          |          | nop                 |             |                              |                        | + 0               |

| Immediate |          |          | ld A,#\$55          |             |                              |                        | + 1               |

| Short     | Direct   |          | ld A,\$10           | 00FF        |                              |                        | + 1               |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF    |                              |                        | + 2               |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF        |                              |                        | + 0               |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE       |                              |                        | + 1               |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF    |                              |                        | + 2               |

| Short     | Indirect |          | ld A,[\$10]         | 00FF        | 00FF                         | byte                   | + 2               |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF    | 00FF                         | word                   | + 2               |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE       | 00FF                         | byte                   | + 2               |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF    | 00FF                         | word                   | + 2               |

| Relative  | Direct   |          | jrne loop           | PC+/-127    |                              |                        | + 1               |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127    | 00FF                         | byte                   | + 2               |

| Bit       | Direct   |          | bset \$10,#7        | 00FF        |                              |                        | + 1               |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF        | 00FF                         | byte                   | + 2               |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF        |                              |                        | + 2               |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF        | 00FF                         | byte                   | + 3               |

# **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                    | Ratings                                             | Maximum value                  | Unit    |  |

|-------------------------------------------|-----------------------------------------------------|--------------------------------|---------|--|

| V <sub>DD</sub> - V <sub>SS</sub>         | Supply voltage                                      | 6.5                            |         |  |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming Voltage                                 | 13                             | v       |  |

| V <sub>IN</sub> <sup>1) &amp; 2)</sup>    | Input Voltage on true open drain pin                | V <sub>SS</sub> -0.3 to 6.5    | v       |  |

| VIN /                                     | Input voltage on any other pin                      | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 |         |  |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins     | 50                             | mV      |  |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins   | 50                             | IIIV    |  |

| V <sub>ESD(HBM)</sub>                     | Electro-static discharge voltage (Human Body Model) | see section 12.7.3 on page 155 |         |  |

| V <sub>ESD(MM)</sub>                      | Electro-static discharge voltage (Machine Model)    | 366 Section 12.7.5 on pa       | age 155 |  |

#### **12.2.2 Current Characteristics**

| Symbol                                       | Ratings                                                                | Maximum value | Unit |

|----------------------------------------------|------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                             | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup>  | 150           | mA   |

| I <sub>VSS</sub>                             | Total current out of $V_{SS}$ ground lines (sink) <sup>3)</sup>        | 150           |      |

|                                              | Output current sunk by any standard I/O and control pin                | 25            |      |

| I <sub>IO</sub>                              | Output current sunk by any high sink I/O pin                           | 50            |      |

|                                              | Output current source by any I/Os and control pin                      | - 25          |      |

|                                              | Injected current on V <sub>PP</sub> pin                                | ± 5           |      |

|                                              | Injected current on RESET pin                                          | ± 5           | mA   |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 4)</sup> | Injected current on OSC1 and OSC2 pins                                 | ± 5           |      |

|                                              | Injected current on PB0 (Flash devices only)                           | + 5           |      |

|                                              | Injected current on any other pin 5) & 6)                              | ± 5           |      |

| ΣI <sub>INJ(PIN)</sub> <sup>2)</sup>         | Total injected current (sum of all I/O and control pins) <sup>5)</sup> | ± 25          |      |

#### Notes:

1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7k $\Omega$  for RESET, 10k $\Omega$  for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

3. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "ADC Accuracy" on page 170.

For best reliability, it is recommended to avoid negative injection of more than 1.6mA.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

6. True open drain I/O port pins do not accept positive injection.

# SUPPLY CURRENT CHARACTERISTICS (Cont'd)

# 12.4.3 On-Chip Peripherals

Measured on LQFP64 generic board  $T_A = 25^{\circ}C f_{CPU} = 4MHz$ .

| Symbol               | Parameter                                        | Conditions            | Тур | Unit |

|----------------------|--------------------------------------------------|-----------------------|-----|------|

| I <sub>DD(TIM)</sub> | 16-bit Timer supply current <sup>1)</sup>        | V <sub>DD</sub> =5.0V | 50  | μA   |

| I <sub>DD(ART)</sub> | ART PWM supply current <sup>2)</sup>             | V <sub>DD</sub> =5.0V | 75  | μA   |

| I <sub>DD(SPI)</sub> | SPI supply current <sup>3)</sup>                 | V <sub>DD</sub> =5.0V | 400 | μA   |

| I <sub>DD(SCI)</sub> | SCI supply current <sup>4)</sup>                 | V <sub>DD</sub> =5.0V | 400 | μA   |

| I <sub>DD(I2C)</sub> | I2C supply current <sup>5)</sup>                 | V <sub>DD</sub> =5.0V | 175 | μA   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>6)</sup> | V <sub>DD</sub> =5.0V | 400 | μΑ   |

#### Notes:

- Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer counter running at f<sub>CPU</sub>/4) and timer counter stopped (only TIMD bit set). Data valid for one timer.

- 2. Data based on a differential I<sub>DD</sub> measurement between reset configuration (timer stopped) and timer counter enabled (only TCE bit set).

- 3. Data based on a differential I<sub>DD</sub> measurement between reset configuration (SPI disabled) and a permanent SPI master communication at maximum speed (data sent equal to 55h). This measurement includes the pad toggling consumption.

- 4. Data based on a differential I<sub>DD</sub> measurement between SCI low power state (SCID=1) and a permanent SCI data transmit sequence.

- 5. Data based on a differential I<sub>DD</sub> measurement between reset configuration (I2C disabled) and a permanent I2C master communication at 100kHz (data sent equal to 55h). This measurement include the pad toggling consumption (27kOhm external pull-up on clock and data lines).

- 6. Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions.

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

# 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as

close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol          | Parameter                                      | Cor                  | nditions        | Min | Max | Unit       |

|-----------------|------------------------------------------------|----------------------|-----------------|-----|-----|------------|

| fosc            |                                                | LP: Low powe         | r oscillator    | 1   | 2   |            |

|                 | Oscillator Frequency <sup>1)</sup>             | MP: Medium p         | ower oscillator | >2  | 4   | MHz        |

|                 | Oscillator Frequency                           | MS: Medium s         | peed oscillator | >4  | 8   | MHZ        |

|                 |                                                | HS: High spee        | d oscillator    | >8  | 16  |            |

| R <sub>F</sub>  | Feedback resistor <sup>2)</sup>                |                      |                 | 20  | 40  | kΩ         |

|                 | Decommended load conseitence ver               | R <sub>S</sub> =200Ω | LP oscillator   | 22  | 56  |            |

| C <sub>L1</sub> | Recommended load capacitance ver-              | R <sub>S</sub> =200Ω | MP oscillator   | 22  | 46  | <b>"</b> Г |

| C <sub>L2</sub> | sus equivalent serial resistance of the        | R <sub>S</sub> =200Ω | MS oscillator   | 18  | 33  | pF         |

|                 | crystal or ceramic resonator (R <sub>S</sub> ) | R <sub>S</sub> =100Ω | HS oscillator   | 15  | 33  |            |

| Symbol         | Parameter            |                                                         | Conditions                                                       | Тур                     | Max                      | Unit |

|----------------|----------------------|---------------------------------------------------------|------------------------------------------------------------------|-------------------------|--------------------------|------|

| i <sub>2</sub> | OSC2 driving current | V <sub>DD</sub> =5V<br>V <sub>IN</sub> =V <sub>SS</sub> | LP oscillator<br>MP oscillator<br>MS oscillator<br>HS oscillator | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μA   |

#### Notes:

57/

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

# EMC CHARACTERISTICS (Cont'd)

## 12.7.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbol           | Parameter  | Conditions                                                          | Monitored       | Max vs. [f | osc/f <sub>CPU</sub> ] <sup>1</sup> | Unit |  |

|------------------|------------|---------------------------------------------------------------------|-----------------|------------|-------------------------------------|------|--|

| Symbol           | Farameter  | Conditions                                                          | Frequency Band  | 8/4MHz     | 16/8MHz                             |      |  |

|                  |            |                                                                     | 0.1MHz to 30MHz | 15         | 20                                  |      |  |

| S <sub>EMI</sub> | Peak level | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C,<br>LQFP64 10x10 package | 30MHz to 130MHz | 20         | 27                                  | dBμV |  |

|                  | reak level | conforming to SAE J 1752/3                                          | 130MHz to 1GHz  | 7          | 12                                  |      |  |

|                  |            | ······································                              | SAE EMI Level   | 2.5        | 3                                   | -    |  |

|                  | Peak level | 60K ROM Devices:                                                    | 0.1MHz to 30MHz | 15         | 20                                  | dBµV |  |

| c                |            | $V_{DD}=5V, T_{A}=+25^{\circ}C,$                                    | 30MHz to 130MHz | 20         | 27                                  |      |  |

| S <sub>EMI</sub> | reak level | LQFP64 package                                                      | 130MHz to 1GHz  | 7          | 12                                  |      |  |

|                  |            | conforming to SAE J 1752/3                                          | SAE EMI Level   | 2.5        | 3                                   | -    |  |

|                  |            | 8/16/32K ROM devices:                                               | 0.1MHz to 30MHz | 17         | 21                                  |      |  |

| c                | Peak level | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C,                         | 30MHz to 130MHz | 24         | 30                                  | dBμV |  |

| S <sub>EMI</sub> | rear ievei | LQFP44 10x10 package                                                | 130MHz to 1GHz  | 18         | 23                                  |      |  |

|                  |            | conforming to SAE J 1752/3                                          | SAE EMI Level   | 3          | 3.5                                 | -    |  |

Notes:

1. Data based on characterization results, not tested in production.

2. Refer to Application Note AN1709 for data on other package types.

# EMC CHARACTERISTICS (Cont'd)

# 12.7.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### 12.7.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

#### **Absolute Maximum Ratings**

| Symbol                | Ratings                                                | Conditions            | Maximum value <sup>1)</sup> | Unit |

|-----------------------|--------------------------------------------------------|-----------------------|-----------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model) | T <sub>A</sub> =+25°C | 2000                        | V    |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)       | T <sub>A</sub> =+25°C | 200                         | v    |

#### Notes:

57

1. Data based on characterization results, not tested in production.

#### 12.7.3.2 Static Latch-Up

LU: 2 complementary static tests are required on 6 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard.

#### **Electrical Sensitivities**

| Symbol | Parameter             | Conditions                                      | Class <sup>1)</sup> |

|--------|-----------------------|-------------------------------------------------|---------------------|

| LU     | Static latch-up class | T <sub>A</sub> =+125°C<br>conforming to JESD 78 | II level A          |

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

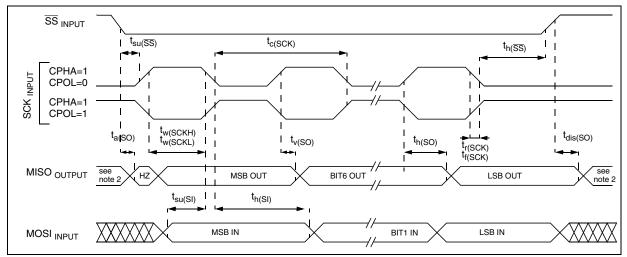

# Figure 93. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

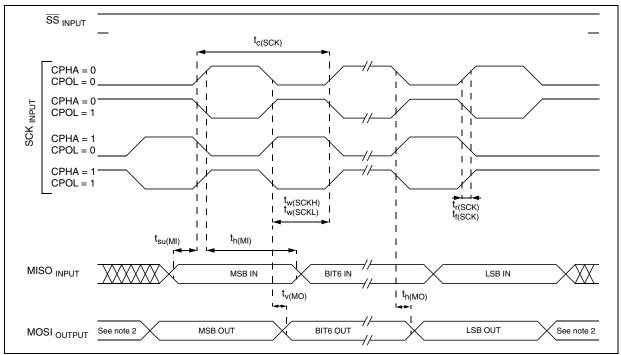

# Figure 94. SPI Master Timing Diagram 1)

#### Notes:

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

# 12.12 10-BIT ADC CHARACTERISTICS

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                               | Conditions                            | Min       | Тур     | Max               | Unit               |

|-------------------|-----------------------------------------------------------------------------------------|---------------------------------------|-----------|---------|-------------------|--------------------|

| f <sub>ADC</sub>  | ADC clock frequency                                                                     |                                       | 0.4       |         | 2                 | MHz                |

| V <sub>AREF</sub> | Analog reference voltage                                                                | $0.7^*V_{DD} \le V_{AREF} \le V_{DD}$ | 3.8       |         | V <sub>DD</sub>   | V                  |

| V <sub>AIN</sub>  | Conversion voltage range 1)                                                             |                                       | $V_{SSA}$ |         | V <sub>AREF</sub> | v                  |

| R <sub>AIN</sub>  | External input impedance                                                                |                                       |           |         | see               | kΩ                 |

| C <sub>AIN</sub>  | External capacitor on analog input                                                      |                                       |           |         | Figure 96<br>and  | pF                 |

| f <sub>AIN</sub>  | Variation freq. of analog input signal                                                  |                                       |           |         | Figure 97         | Hz                 |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                                      |                                       |           | 12      |                   | pF                 |

| t <sub>ADC</sub>  | Conversion time (Sample+Hold)<br>f <sub>CPU</sub> =8MHz, SPEED=0 f <sub>ADC</sub> =2MHz |                                       |           | 7.5     |                   | μS                 |

| t <sub>ADC</sub>  | - No of sample capacitor loading cycles<br>- No. of Hold conversion cycles              |                                       |           | 4<br>11 |                   | 1/f <sub>ADC</sub> |

#### Notes:

57/

1. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.