# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 32                                                                   |

| Program Memory Size        | 48KB (48K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1.5K x 8                                                             |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 44-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321j7t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents

-

\_

| 8.4     | ACTIVE-HALT AND HALT MODES                                                                                                                                                          | . 43                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|         | 8.4.1 ACTIVE-HALT MODE                                                                                                                                                              | . 43                                                                 |

|         | 8.4.2 HALT MODE                                                                                                                                                                     | . 44                                                                 |

| 9 I/O P | ORTS                                                                                                                                                                                | . 46                                                                 |

| 9.1     | INTRODUCTION                                                                                                                                                                        | . 46                                                                 |

| 9.2     | FUNCTIONAL DESCRIPTION                                                                                                                                                              | . 46                                                                 |

|         | 9.2.1 Input Modes                                                                                                                                                                   | . 46                                                                 |

|         | 9.2.2 Output Modes                                                                                                                                                                  | . 46                                                                 |

|         | 9.2.3 Alternate Functions                                                                                                                                                           | . 46                                                                 |

| 9.3     | I/O PORT IMPLEMENTATION                                                                                                                                                             | . 49                                                                 |

| 9.4     | LOW POWER MODES                                                                                                                                                                     | . 49                                                                 |

|         | INTERRUPTS                                                                                                                                                                          |                                                                      |

| 5.5     |                                                                                                                                                                                     |                                                                      |

| 10.01   | 9.5.1 I/O Port Implementation                                                                                                                                                       |                                                                      |

|         |                                                                                                                                                                                     |                                                                      |

| 10.1    | WATCHDOG TIMER (WDG)                                                                                                                                                                |                                                                      |

|         | 10.1.1 Introduction                                                                                                                                                                 |                                                                      |

|         | 10.1.2 Main Features                                                                                                                                                                |                                                                      |

|         | 10.1.3 Functional Description                                                                                                                                                       |                                                                      |

|         | 10.1.4 How to Program the Watchdog Timeout                                                                                                                                          |                                                                      |

|         | 10.1.5 Low Power Modes                                                                                                                                                              |                                                                      |

|         | 10.1.6 Hardware Watchdog Option                                                                                                                                                     |                                                                      |

|         | 10.1.7 Using Halt Mode with the WDG (WDGHALT option)                                                                                                                                |                                                                      |

|         | 10.1.8 Interrupts                                                                                                                                                                   |                                                                      |

| 10.0    | 10.1.9 Register Description                                                                                                                                                         |                                                                      |

| 10.2    | 2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) .                                                                                                                 |                                                                      |

|         | 10.2.1 Programmable CPU Clock Prescaler                                                                                                                                             |                                                                      |

|         | 10.2.2 Clock-out Capability                                                                                                                                                         |                                                                      |

|         | 10.2.3 Real Time Clock Timer (RTC)                                                                                                                                                  |                                                                      |

|         | 10.2.4 Beeper                                                                                                                                                                       |                                                                      |

|         | 10.2.5 Low Power Modes                                                                                                                                                              |                                                                      |

|         | 10.2.6 Interrupts                                                                                                                                                                   |                                                                      |

| 10.0    | 10.2.7 Register Description                                                                                                                                                         |                                                                      |

| 10.3    | 3 PWM AUTO-RELOAD TIMER (ART)                                                                                                                                                       |                                                                      |

|         | 10.3.1 Introduction                                                                                                                                                                 |                                                                      |

|         | 10.3.2 Functional Description                                                                                                                                                       |                                                                      |

| 10      | 10.3.3 Register Description                                                                                                                                                         |                                                                      |

| 10.4    | 16-BIT TIMER                                                                                                                                                                        |                                                                      |

|         | 10.4.1 Introduction                                                                                                                                                                 | 60                                                                   |

|         |                                                                                                                                                                                     |                                                                      |

|         | 10.4.2 Main Features                                                                                                                                                                | . 69                                                                 |

|         | 10.4.2 Main Features10.4.3 Functional Description                                                                                                                                   | . 69<br>. 69                                                         |

|         | 10.4.2 Main Features10.4.3 Functional Description10.4.4 Low Power Modes                                                                                                             | . 69<br>. 69<br>. 81                                                 |

|         | 10.4.2 Main Features10.4.3 Functional Description10.4.4 Low Power Modes10.4.5 Interrupts                                                                                            | . 69<br>. 69<br>. 81<br>. 81                                         |

|         | 10.4.2Main Features10.4.3Functional Description10.4.4Low Power Modes10.4.5Interrupts10.4.6Summary of Timer Modes                                                                    | . 69<br>. 69<br>. 81<br>. 81<br>. 81                                 |

|         | 10.4.2Main Features10.4.3Functional Description10.4.4Low Power Modes10.4.5Interrupts10.4.6Summary of Timer Modes10.4.7Register Description                                          | . 69<br>. 69<br>. 81<br>. 81<br>. 81<br>. 81                         |

| 10.5    | 10.4.2 Main Features10.4.3 Functional Description10.4.4 Low Power Modes10.4.5 Interrupts10.4.6 Summary of Timer Modes10.4.7 Register Description5 SERIAL PERIPHERAL INTERFACE (SPI) | . 69<br>. 69<br>. 81<br>. 81<br>. 81<br>. 82<br>. 88                 |

| 10.5    | 10.4.2Main Features10.4.3Functional Description10.4.4Low Power Modes10.4.5Interrupts10.4.6Summary of Timer Modes10.4.7Register Description                                          | . 69<br>. 69<br>. 81<br>. 81<br>. 81<br>. 81<br>. 82<br>. 88<br>. 88 |

| F      | Pin n° |        |                          |      | Le      | evel   |       |     | Р   | ort |     |      | Main                                                                                                                                                                                                                                                                                               |                                              |  |

|--------|--------|--------|--------------------------|------|---------|--------|-------|-----|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| P64    | P44    | P32    | Pin Name                 | Type | ut      | put    |       | Inp | out |     | Out | tput | function<br>(after                                                                                                                                                                                                                                                                                 | Alternate function                           |  |

| LQFP64 | LQFP44 | LQFP32 |                          |      | Input   | Output | float | ndm | int | ana | OD  | д    | reset)                                                                                                                                                                                                                                                                                             |                                              |  |

| 45     | -      | -      | PA2                      | I/O  | $C_T$   |        | Χ     | e   | i0  |     | Х   | Х    | Port A2                                                                                                                                                                                                                                                                                            |                                              |  |

| 46     | 31     | 16     | PA3 (HS)                 | I/O  | $C_T$   | HS     | Χ     |     | ei0 |     | Х   | Х    | Port A3                                                                                                                                                                                                                                                                                            |                                              |  |

| 47     | 32     | -      | V <sub>DD_1</sub>        | S    |         |        |       |     |     |     |     |      | Digital Ma                                                                                                                                                                                                                                                                                         | ain Supply Voltage                           |  |

| 48     | 33     | -      | V <sub>SS_1</sub>        | S    |         |        |       |     |     |     |     |      | Digital G                                                                                                                                                                                                                                                                                          | round Voltage                                |  |

| 49     | 34     | 17     | PA4 (HS)                 | I/O  | $C_{T}$ | HS     | Х     | Х   |     |     | Х   | Х    | Port A4                                                                                                                                                                                                                                                                                            |                                              |  |

| 50     | 35     | -      | PA5 (HS)                 | I/O  | $C_T$   | HS     | Χ     | Х   |     |     | Х   | Х    | Port A5                                                                                                                                                                                                                                                                                            |                                              |  |

| 51     | 36     | 18     | PA6 (HS)/SDAI            | I/O  | $C_{T}$ | HS     | Х     |     |     |     | Т   |      | Port A6                                                                                                                                                                                                                                                                                            | I <sup>2</sup> C Data <sup>1)</sup>          |  |

| 52     | 37     | 19     | PA7 (HS)/SCLI            | I/O  | $C_{T}$ | HS     | Χ     |     |     |     | Т   |      | Port A7                                                                                                                                                                                                                                                                                            | I <sup>2</sup> C Clock <sup>1)</sup>         |  |

| 53     | 38     | 20     | V <sub>PP</sub> / ICCSEL | I    |         |        |       |     |     |     |     |      | Must be tied low. In flash program-<br>ming mode, this pin acts as the pro-<br>gramming voltage input $V_{PP}$ . See<br>Section 12.9.2 for more details. High<br>voltage must not be applied to ROM<br>devices                                                                                     |                                              |  |

| 54     | 39     | 21     | RESET                    | I/O  | $C_{T}$ |        |       |     |     |     |     |      | Top priority non maskable interrupt.                                                                                                                                                                                                                                                               |                                              |  |

| 55     | -      | -      | EVD                      |      |         |        |       |     |     |     |     |      | External voltage detector                                                                                                                                                                                                                                                                          |                                              |  |

| 56     | -      | -      | TLI                      | I    | $C_{T}$ |        |       |     | Х   |     |     |      | Top level                                                                                                                                                                                                                                                                                          | interrupt input pin                          |  |

| 57     | 40     | 22     | V <sub>SS_2</sub>        | S    |         |        |       |     |     |     |     |      | Digital G                                                                                                                                                                                                                                                                                          | round Voltage                                |  |

| 58     | 41     | 23     | OSC2 <sup>3)</sup>       | I/O  |         |        |       |     |     |     |     |      | Resonato                                                                                                                                                                                                                                                                                           | or oscillator inverter output                |  |

| 59     | 42     | 24     | OSC1 <sup>3)</sup>       | I    |         |        |       |     |     |     |     |      |                                                                                                                                                                                                                                                                                                    | clock input or Resonator os-<br>verter input |  |

| 60     | 43     | 25     | V <sub>DD_2</sub>        | S    |         |        |       |     |     |     |     |      | Digital Ma                                                                                                                                                                                                                                                                                         | ain Supply Voltage                           |  |

| 61     | 44     | 26     | PE0/TDO                  | I/O  | $C_T$   |        | Χ     | Х   |     |     | Х   | Х    | Port E0                                                                                                                                                                                                                                                                                            | SCI Transmit Data Out                        |  |

| 62     | 1      | 27     | PE1/RDI                  | I/O  | $C_{T}$ |        | Х     | Х   |     |     | Х   | Х    | Port E1                                                                                                                                                                                                                                                                                            | SCI Receive Data In                          |  |

|        |        |        | PE2 (Flash device)       |      |         |        |       | x   |     |     |     |      | Port E2<br>Caution: In Flash devices this port is<br>always input with weak pull-up.                                                                                                                                                                                                               |                                              |  |

| 63     | -      | -      | PE2 (ROM device)         | I/O  | CT      |        | x     |     |     |     | x   | x    | Port E2<br><b>Caution:</b> In ROM devices, no weak<br>pull-up present on this port.<br>In LQFP44 this pin is not connected to<br>an internal pull-up like other unbond-<br>ed pins (See note 4). It is recommend-<br>ed to configure it as output push pull<br>to avoid added current consumption. |                                              |  |

| 64     | -      | -      | PE3                      | I/O  | $C_T$   |        | Χ     | Х   |     |     | Х   | Х    | Port E3                                                                                                                                                                                                                                                                                            |                                              |  |

#### Notes:

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is pull-up interrupt input, else the configuration is floating interrupt input.

2. In the open drain output column, "T" defines a true open drain I/O (P-Buffer and protection diode to  $V_{DD}$  are not implemented). See See "I/O PORTS" on page 46. and Section 12.8 I/O PORT PIN CHARACTER-

ISTICS for more details.

**۲**۲

3. OSC1 and OSC2 pins connect a crystal/ceramic resonator, or an external source to the on-chip oscillator; see Section 1 DESCRIPTION and Section 12.5 CLOCK AND TIMING CHARACTERISTICS for more details.

4. On the chip, each I/O port may have up to 8 pads:

- ads that are not bonded to external pins are forced by hardware in input pull-up configuration after reset.

The configuration of these pads must be kept at reset state to avoid added current consumption.

- 5. Pull-up always activated on PE2 see limitation Section 15.4.6.

6. It is mandatory to connect all available  $V_{DD}$  and  $V_{REF}$  pins to the supply voltage and all  $V_{SS}$  and  $V_{SSA}$  pins to ground.

| Address                                                                                                                             | Block    | Register<br>Label                                                                                                                                                        | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Reset<br>Status                                                                                        | Remarks                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 002Ah                                                                                                                               | WATCHDOG | WDGCR                                                                                                                                                                    | Watchdog Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7Fh                                                                                                    | R/W                                                                                                                                                                                                                               |  |  |

| 002Bh                                                                                                                               |          | SICSR                                                                                                                                                                    | System Integrity Control/Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 000x 000x b                                                                                            | R/W                                                                                                                                                                                                                               |  |  |

| 002Ch<br>002Dh                                                                                                                      | MCC      | MCCSR<br>MCCBCR                                                                                                                                                          | Main Clock Control / Status Register<br>Main Clock Controller: Beep Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00h<br>00h                                                                                             | R/W<br>R/W                                                                                                                                                                                                                        |  |  |

| 002Eh<br>to<br>0030h                                                                                                                |          | Reserved Area (3 Bytes)                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |                                                                                                                                                                                                                                   |  |  |

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h<br>0037h<br>0038h<br>0039h<br>003Ah<br>003Bh<br>003Ch<br>003Ch<br>003Eh<br>003Fh | TIMER A  | TACR2<br>TACR1<br>TACSR<br>TAIC1HR<br>TAIC1LR<br>TAOC1HR<br>TAOC1LR<br>TACHR<br>TACHR<br>TACLR<br>TAACHR<br>TAACLR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAOC2HR<br>TAOC2LR | Timer A Control Register 2<br>Timer A Control Register 1<br>Timer A Control/Status Register<br>Timer A Input Capture 1 High Register<br>Timer A Input Capture 1 Low Register<br>Timer A Output Compare 1 High Register<br>Timer A Output Compare 1 Low Register<br>Timer A Counter High Register<br>Timer A Counter High Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter Low Register<br>Timer A Input Capture 2 High Register<br>Timer A Input Capture 2 Low Register<br>Timer A Output Compare 2 Low Register  | 00h<br>00h<br>xxxx x0xx b<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>Read Only<br>Read Only |  |  |

| 0040h                                                                                                                               |          |                                                                                                                                                                          | Reserved Area (1 Byte)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                        |                                                                                                                                                                                                                                   |  |  |

| 0041h<br>0042h<br>0043h<br>0045h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Eh<br>004Fh | TIMER B  | TBCR2<br>TBCR1<br>TBCSR<br>TBIC1LR<br>TBIC1LR<br>TBOC1LR<br>TBOC1LR<br>TBCLR<br>TBCLR<br>TBACLR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR                   | Timer B Control Register 2<br>Timer B Control Register 1<br>Timer B Control/Status Register<br>Timer B Input Capture 1 High Register<br>Timer B Input Capture 1 Low Register<br>Timer B Output Compare 1 High Register<br>Timer B Output Compare 1 Low Register<br>Timer B Counter High Register<br>Timer B Counter High Register<br>Timer B Alternate Counter High Register<br>Timer B Alternate Counter High Register<br>Timer B Input Capture 2 High Register<br>Timer B Input Capture 2 Low Register<br>Timer B Output Compare 2 Low Register | 00h<br>00h<br>xxxx x0xx b<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>80h<br>00h        | R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>Read Only<br>Read Only |  |  |

| 0050h<br>0051h<br>0052h<br>0053h<br>0054h<br>0055h<br>0056h<br>0057h                                                                | SCI      | SCISR<br>SCIDR<br>SCIBRR<br>SCICR1<br>SCICR2<br>SCIERPR<br>SCIETPR                                                                                                       | SCI Status Register<br>SCI Data Register<br>SCI Baud Rate Register<br>SCI Control Register 1<br>SCI Control Register 2<br>SCI Extended Receive Prescaler Register<br>Reserved area<br>SCI Extended Transmit Prescaler Register                                                                                                                                                                                                                                                                                                                    | C0h<br>xxh<br>00h<br>x000 0000b<br>00h<br>00h<br><br>00h                                               | Read Only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W                                                                                                                                                                                      |  |  |

57

# 4 FLASH PROGRAM MEMORY

#### 4.1 Introduction

The ST7 dual voltage High Density Flash (HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external  $V_{PP}$  supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) or IAP (In-Application Programming).

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

#### 4.2 Main Features

- Three Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application Programming) In this mode, all sectors except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

#### 4.3 Structure

The Flash memory is organised in sectors and can be used for both code and data storage.

Depending on the overall Flash memory size in the microcontroller device, there are up to three user

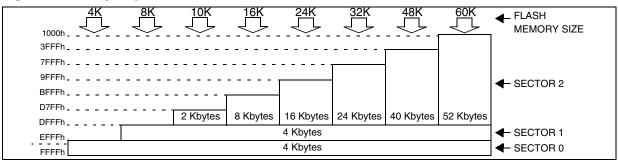

Figure 5. Memory Map and Sector Address

sectors (see Table 4). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

The first two sectors have a fixed size of 4 Kbytes (see Figure 5). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

| Table 4. Sectors available in Flash devices | Table 4. | Sectors | available | in Flash | devices |

|---------------------------------------------|----------|---------|-----------|----------|---------|

|---------------------------------------------|----------|---------|-----------|----------|---------|

| Flash Size (bytes) | Available Sectors |

|--------------------|-------------------|

| 4K                 | Sector 0          |

| 8K                 | Sectors 0,1       |

| > 8K               | Sectors 0,1, 2    |

#### 4.3.1 Read-out Protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory. Even if no protection can be considered as to-tally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In flash devices, this protection is removed by reprogramming the option. In this case, the entire program memory is first automatically erased and the device can be reprogrammed.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

**Note:** In flash devices, the LVD is not supported if read-out protection is enabled.

#### SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 6.4.4 Register Description

#### SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

#### Read/Write

Reset Value: 000x 000x (00h)

| 7   |     |     |     |   |   |   | 0   |

|-----|-----|-----|-----|---|---|---|-----|

| AVD | AVD | AVD | LVD | 0 | 0 | 0 | WDG |

| S   | IE  | F   | RF  | 0 | 0 | 0 | RF  |

#### Bit 7 = **AVDS** Voltage Detection selection

This bit is set and cleared by software. Voltage Detection is available only if the LVD is enabled by option byte.

0: Voltage detection on V<sub>DD</sub> supply

1: Voltage detection on EVD pin

Bit 6 = **AVDIE** Voltage Detector interrupt enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag changes (toggles). The pending interrupt information is automatically cleared when software enters the AVD interrupt routine.

0: AVD interrupt disabled

1: AVD interrupt enabled

#### Bit 5 = AVDF Voltage Detector flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit changes value. Refer to Figure 16 and to Section 6.4.2.1 for additional details.

0: V<sub>DD</sub> or V<sub>EVD</sub> over V<sub>IT+(AVD)</sub> threshold 1: V<sub>DD</sub> or V<sub>EVD</sub> under V<sub>IT-(AVD)</sub> threshold

#### Bit 4 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (writing zero). See WDGRF flag description for more details. When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

Bits 31 = Reserved, must be kept cleared.

#### Bit 0 = **WDGRF** *Watchdog reset flag*

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (writing zero) or an LVD Reset (to ensure a stable cleared state of the WDGRF flag when CPU starts).

Combined with the LVDRF flag information, the flag description is given by the following table.

| <b>RESET Sources</b> | LVDRF | WDGRF |

|----------------------|-------|-------|

| External RESET pin   | 0     | 0     |

| Watchdog             | 0     | 1     |

| LVD                  | 1     | Х     |

#### Application notes

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

**CAUTION:** When the LVD is not activated with the associated option byte, the WDGRF flag can not be used in the application.

# INTERRUPTS (Cont'd)

#### 7.3 INTERRUPTS AND LOW POWER MODES

All interrupts allow the processor to exit the WAIT low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the HALT modes (see column "Exit from HALT" in "Interrupt Mapping" table). When several pending interrupts are present while exiting HALT mode, the first one serviced can only be an interrupt with exit from HALT mode capability and it is selected through the same decision process shown in Figure 19.

**Note:** If an interrupt, that is not able to Exit from HALT mode, is pending with the highest priority when exiting HALT mode, this interrupt is serviced after the first one serviced.

#### 7.4 CONCURRENT & NESTED MANAGEMENT

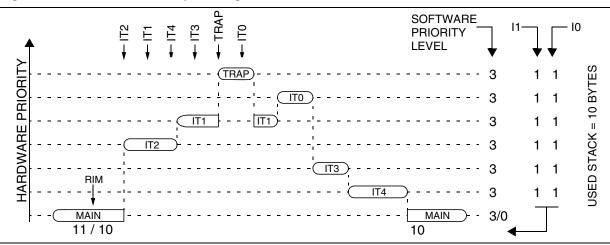

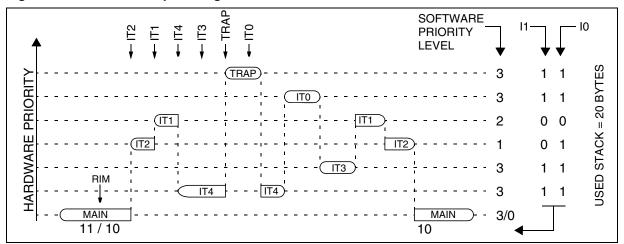

The following Figure 20 and Figure 21 show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in Figure 21. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0, TLI. The software priority is given for each interrupt.

**Warning**: A stack overflow may occur without notifying the software of the failure.

**47**

#### Figure 20. Concurrent Interrupt Management

Figure 21. Nested Interrupt Management

# 7.7 EXTERNAL INTERRUPT CONTROL REGISTER (EICR)

# Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |      |      |     |      | 0    |

|------|------|-----|------|------|-----|------|------|

| IS11 | IS10 | IPB | IS21 | IS20 | IPA | TLIS | TLIE |

Bit 7:6 = **IS1[1:0]** *ei2* and *ei3* sensitivity

The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the following external interrupts: - ei2 (port B3..0)

| IS11 | IS10 | External Interr             | upt Sensitivity             |  |  |  |

|------|------|-----------------------------|-----------------------------|--|--|--|

| 1011 | 1010 | IPB bit =0                  | IPB bit =1                  |  |  |  |

| 0    | 0    | Falling edge &<br>low level | Rising edge<br>& high level |  |  |  |

| 0    | 1    | Rising edge only            | Falling edge only           |  |  |  |

| 1    | 0    | Falling edge only           | Rising edge only            |  |  |  |

| 1    | 1    | Rising and falling edge     |                             |  |  |  |

# - ei3 (port B7..4)

| IS11 | IS10 | External Interrupt Sensitivity |  |

|------|------|--------------------------------|--|

| 0    | 0    | Falling edge & low level       |  |

| 0    | 1    | Rising edge only               |  |

| 1    | 0    | Falling edge only              |  |

| 1    | 1    | Rising and falling edge        |  |

These 2 bits can be written only when 11 and 10 of the CC register are both set to 1 (level 3).

# Bit 5 = **IPB** Interrupt polarity for port B

This bit is used to invert the sensitivity of the port B [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3).

- 0: No sensitivity inversion

- 1: Sensitivity inversion

5/

# Bit 4:3 = **IS2[1:0]** *ei0* and *ei1* sensitivity

The interrupt sensitivity, defined using the IS2[1:0] bits, is applied to the following external interrupts:

- ei0 (port A3..0)

| IS21      | IS20 | External Interr             | upt Sensitivity             |  |  |  |

|-----------|------|-----------------------------|-----------------------------|--|--|--|

| 1521 1520 |      | IPA bit =0                  | IPA bit =1                  |  |  |  |

| 0         | 0    | Falling edge &<br>low level | Rising edge<br>& high level |  |  |  |

| 0         | 1    | Rising edge only            | Falling edge only           |  |  |  |

| 1         | 0    | Falling edge only           | Rising edge only            |  |  |  |

| 1         | 1    | Rising and falling edge     |                             |  |  |  |

#### - ei1 (port F2..0)

| IS21 | IS20 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

# Bit 2 = IPA Interrupt polarity for port A

This bit is used to invert the sensitivity of the port A [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3).

0: No sensitivity inversion

1: Sensitivity inversion

#### Bit 1 = **TLIS** *TLI* sensitivity

This bit allows to toggle the TLI edge sensitivity. It can be set and cleared by software only when TLIE bit is cleared.

- 0: Falling edge

- 1: Rising edge

#### Bit 0 = TLIE TLI enable

This bit allows to enable or disable the TLI capability on the dedicated pin. It is set and cleared by software.

0: TLI disabled

1: TLI enabled

**Note**: a parasitic interrupt can be generated when clearing the TLIE bit.

# **8 POWER SAVING MODES**

# **8.1 INTRODUCTION**

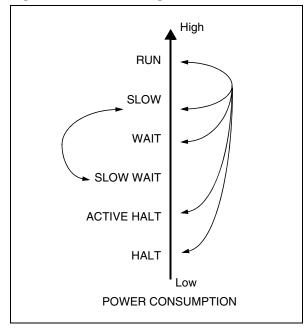

To give a large measure of flexibility to the application in terms of power consumption, four main power saving modes are implemented in the ST7 (see Figure 23): SLOW, WAIT (SLOW WAIT), AC-TIVE HALT and HALT.

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 ( $f_{OSC2}$ ).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

Figure 23. Power Saving Mode Transitions

#### 8.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

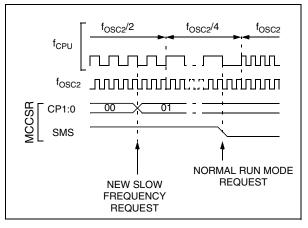

SLOW mode is controlled by three bits in the MCCSR register: the SMS bit which enables or disables Slow mode and two CPx bits which select the internal slow frequency ( $f_{CPU}$ ).

In this mode, the master clock frequency ( $f_{OSC2}$ ) can be divided by 2, 4, 8 or 16. The CPU and peripherals are clocked at this lower frequency ( $f_{CPU}$ ).

**Note**: SLOW-WAIT mode is activated when entering the WAIT mode while the device is already in SLOW mode.

#### Figure 24. SLOW Mode Clock Transitions

# WATCHDOG TIMER (Cont'd)

#### Figure 34. Exact Timeout Duration (t<sub>min</sub> and t<sub>max</sub>)

#### WHERE:

$t_{min0} = (LSB + 128) \times 64 \times t_{OSC2}$  $t_{max0} = 16384 \times t_{OSC2}$  $t_{OSC2} = 125ns \text{ if } f_{OSC2} = 8 \text{ MHz}$

CNT = Value of T[5:0] bits in the WDGCR register (6 bits) MSB and LSB are values from the table below depending on the timebase selected by the TB[1:0] bits in the MCCSR register

| TB1 Bit<br>(MCCSR Reg.) | TB0 Bit<br>(MCCSR Reg.) | Selected MCCSR<br>Timebase | MSB | LSB |

|-------------------------|-------------------------|----------------------------|-----|-----|

| 0                       | 0                       | 2ms                        | 4   | 59  |

| 0                       | 1                       | 4ms                        | 8   | 53  |

| 1                       | 0                       | 10ms                       | 20  | 35  |

| 1                       | 1                       | 25ms                       | 49  | 54  |

To calculate the minimum Watchdog Timeout (t<sub>min</sub>):

**IF** CNT <  $\left[\frac{MSB}{4}\right]$  **THEN**  $t_{min} = t_{min0} + 16384 \times CNT \times t_{osc2}$

**ELSE**

$$t_{min} = t_{min0} + \left[ 16384 \times \left( CNT - \left[ \frac{4CNT}{MSB} \right] \right) + (192 + LSB) \times 64 \times \left[ \frac{4CNT}{MSB} \right] \right] \times t_{osc2}$$

To calculate the maximum Watchdog Timeout (t<sub>max</sub>):

$$\begin{split} \textbf{IF} \ \textbf{CNT} \leq & \left[\frac{\textbf{MSB}}{4}\right] \quad \textbf{THEN} \ t_{max} = t_{max0} + 16384 \times \textbf{CNT} \times t_{osc2} \\ & \textbf{ELSE} \ t_{max} = t_{max0} + \left[16384 \times \left(\textbf{CNT} - \left[\frac{4\textbf{CNT}}{\textbf{MSB}}\right]\right) + (192 + \textbf{LSB}) \times 64 \times \left[\frac{4\textbf{CNT}}{\textbf{MSB}}\right]\right] \times t_{osc2} \end{split}$$

**Note:** In the above formulae, division results must be rounded down to the next integer value. **Example:**

With 2ms timeout selected in MCCSR register

| meout (ms)<br>t <sub>min</sub> | Timeout (ms)<br>t <sub>max</sub> |

|--------------------------------|----------------------------------|

| 1.496                          | 2.048                            |

| 128                            | 128.552                          |

|                                | t <sub>min</sub><br>1.496        |

# **ON-CHIP PERIPHERALS** (Cont'd)

#### **10.3.2 Functional Description**

#### Counter

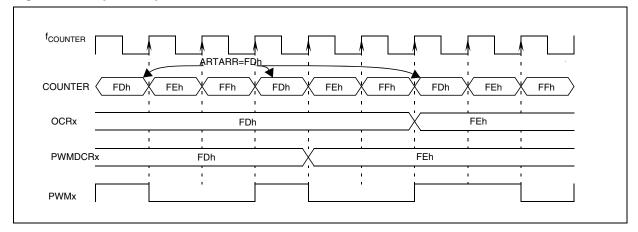

The free running 8-bit counter is fed by the output of the prescaler, and is incremented on every rising edge of the clock signal.

It is possible to read or write the contents of the counter on the fly by reading or writing the Counter Access register (ARTCAR).

When a counter overflow occurs, the counter is automatically reloaded with the contents of the ARTARR register (the prescaler is not affected).

#### Counter clock and prescaler

The counter clock frequency is given by:

$$f_{COUNTEB} = f_{INPLIT} / 2^{CC[2:0]}$$

The timer counter's input clock ( $f_{INPUT}$ ) feeds the 7-bit programmable prescaler, which selects one of the 8 available taps of the prescaler, as defined by CC[2:0] bits in the Control/Status Register (ARTCSR). Thus the division factor of the prescaler can be set to  $2^n$  (where n = 0, 1,...7).

This  $f_{INPUT}$  frequency source is selected through the EXCL bit of the ARTCSR register and can be either the  $f_{CPL}$  or an external input frequency  $f_{FXT}$ .

The clock input to the counter is enabled by the TCE (Timer Counter Enable) bit in the ARTCSR register. When TCE is reset, the counter is stopped and the prescaler and counter contents are frozen. When TCE is set, the counter runs at the rate of the selected clock source.

#### **Counter and Prescaler Initialization**

After RESET, the counter and the prescaler are cleared and  $f_{INPUT} = f_{CPU}$ .

The counter can be initialized by:

- Writing to the ARTARR register and then setting the FCRL (Force Counter Re-Load) and the TCE (Timer Counter Enable) bits in the ARTCSR register.

- Writing to the ARTCAR counter access register,

In both cases the 7-bit prescaler is also cleared, whereupon counting will start from a known value.

Direct access to the prescaler is not possible.

#### **Output compare control**

The timer compare function is based on four different comparisons with the counter (one for each PWMx output). Each comparison is made between the counter value and an output compare register (OCRx) value. This OCRx register can not be accessed directly, it is loaded from the duty cycle register (PWMDCRx) at each overflow of the counter.

This double buffering method avoids glitch generation when changing the duty cycle on the fly.

#### Figure 37. Output compare control

57/

#### **ON-CHIP PERIPHERALS** (Cont'd)

#### Input capture function

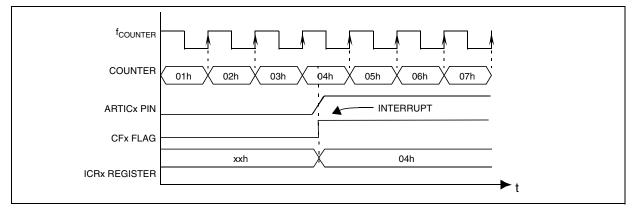

This mode allows the measurement of external signal pulse widths through ARTICRx registers.

Each input capture can generate an interrupt independently on a selected input signal transition. This event is flagged by a set of the corresponding CFx bits of the Input Capture Control/Status register (ARTICCSR).

These input capture interrupts are enabled through the CIEx bits of the ARTICCSR register.

The active transition (falling or rising edge) is software programmable through the CSx bits of the ARTICCSR register.

The read only input capture registers (ARTICRx) are used to latch the auto-reload counter value when a transition is detected on the ARTICx pin (CFx bit set in ARTICCSR register). After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

**Note**: After a capture detection, data transfer in the ARTICRx register is inhibited until it is read (clearing the CFx bit).

The timer interrupt remains pending while the CFx flag is set when the interrupt is enabled (CIEx bit set). This means, the ARTICRx register has to be read at each capture event to clear the CFx flag.

The timing resolution is given by auto-reload counter cycle time (1/f<sub>COUNTER</sub>).

**Note:** During HALT mode, if both input capture and external clock are enabled, the ARTICRx register value is not guaranteed if the input capture pin and the external clock change simultaneously.

#### Figure 41. Input Capture Timing Diagram

#### External interrupt capability

This mode allows the Input capture capabilities to be used as external interrupt sources. The interrupts are generated on the edge of the ARTICx signal.

The edge sensitivity of the external interrupts is programmable (CSx bit of ARTICCSR register) and they are independently enabled through CIEx bits of the ARTICCSR register. After fetching the interrupt vector, the CFx flags can be read to identify the interrupt source.

During HALT mode, the external interrupts can be used to wake up the micro (if the CIEx bit is set).

#### **16-BIT TIMER** (Cont'd)

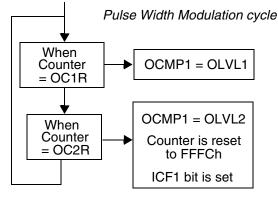

#### 10.4.3.6 Pulse Width Modulation Mode

Pulse Width Modulation (PWM) mode enables the generation of a signal with a frequency and pulse length determined by the value of the OC1R and OC2R registers.

Pulse Width Modulation mode uses the complete Output Compare 1 function plus the OC2R register, and so this functionality can not be used when PWM mode is activated.

In PWM mode, double buffering is implemented on the output compare registers. Any new values written in the OC1R and OC2R registers are taken into account only at the end of the PWM period (OC2) to avoid spikes on the PWM output pin (OCMP1).

#### Procedure

To use Pulse Width Modulation mode:

- 1. Load the OC2R register with the value corresponding to the period of the signal using the formula in the opposite column.

- 2. Load the OC1R register with the value corresponding to the period of the pulse if (OLVL1 = 0 and OLVL2 = 1) using the formula in the opposite column.

- 3. Select the following in the CR1 register:

- Using the OLVL1 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC1R register.

- Using the OLVL2 bit, select the level to be applied to the OCMP1 pin after a successful comparison with the OC2R register.

- 4. Select the following in the CR2 register:

- Set OC1E bit: the OCMP1 pin is then dedicated to the output compare 1 function.

- Set the PWM bit.

- Select the timer clock (CC[1:0]) (see Table 1).

If OLVL1 = 1 and OLVL2 = 0 the length of the positive pulse is the difference between the OC2R and OC1R registers.

If OLVL1 = OLVL2 a continuous signal will be seen on the OCMP1 pin.

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$OCIR Value = \frac{t \cdot f_{CPU}}{PRESC} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>CPU</sub> = CPU clock frequency (in hertz)

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 1)

If the timer clock is an external clock the formula is:

$$OC_{iR} = t * f_{EXT} - 5$$

Where:

t = Signal or pulse period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

The Output Compare 2 event causes the counter to be initialized to FFFCh (See Figure 11)

#### Notes:

- 1. After a write instruction to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- 2. The OCF1 and OCF2 bits cannot be set by hardware in PWM mode therefore the Output Compare interrupt is inhibited.

- 3. The ICF1 bit is set by hardware when the counter reaches the OC2R value and can produce a timer interrupt if the ICIE bit is set and the I bit is cleared.

- 4. In PWM mode the ICAP1 pin can not be used to perform input capture because it is disconnected to the timer. The ICAP2 pin can be used to perform input capture (ICF2 can be set and IC2R can be loaded) but the user must take care that the counter is reset each period and ICF1 can also generates interrupt if ICIE is set.

- 5. When the Pulse Width Modulation (PWM) and One Pulse mode (OPM) bits are both set, the PWM mode is the only active one.

# SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 10.5.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the MCU is woken up by<br>an interrupt with "exit from HALT mode" ca-<br>pability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the device. |

# 10.5.6.1 Using the SPI to wakeup the MCU from Halt mode

In slave configuration, the SPI is able to wakeup the ST7 device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware. **Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. So if Slave selection is configured as external (see Section 10.5.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

#### 10.5.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Transfer<br>Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode Fault<br>Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 1 (SCICR1)

#### Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

#### Bit 7 = **R8** Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = **T8** Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software.

0: SCI enabled

1: SCI prescaler and outputs disabled

Bit  $4 = \mathbf{M}$  Word length. This bit determines the word length. It is set or cleared by software.

0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line 1: Address Mark

#### Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled 1: Parity control enabled

1. Failty control enabled

#### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

#### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software.

0: Parity error interrupt disabled

1: Parity error interrupt enabled.

# I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C CLOCK CONTROL REGISTER (CCR)

Read / Write Reset Value: 0000 0000 (00h)

| 7     |     |     |     |     |     |     | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| FM/SM | CC6 | CC5 | CC4 | CC3 | CC2 | CC1 | CC0 |

# Bit 7 = **FM/SM** Fast/Standard $l^2C$ mode.

This bit is set and cleared by software. It is not cleared when the interface is disabled (PE=0). 0: Standard  $I^2C$  mode

1: Fast I<sup>2</sup>C mode

Bit 6:0 = CC[6:0] 7-bit clock divider.

These bits select the speed of the bus ( $F_{SCL}$ ) depending on the I<sup>2</sup>C mode. They are not cleared when the interface is disabled (PE=0).

Refer to the Electrical Characteristics section for the table of values.

Note: The programmed  $\mathrm{F}_{\mathrm{SCL}}$  assumes no load on SCL and SDA lines.

# I<sup>2</sup>C DATA REGISTER (DR)

#### Read / Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Bit 7:0 = **D**[7:0] 8-bit Data Register.

These bits contain the byte to be received or transmitted on the bus.

- Transmitter mode: Byte transmission start automatically when the software writes in the DR register.

- Receiver mode: the first data byte is received automatically in the DR register using the least significant bit of the address.

Then, the following data bytes are received one by one after reading the DR register.

# INSTRUCTION SET OVERVIEW (Cont'd)

| Mnemo | Description               | Function/Example    | Dst    | Src | 11 | н | 10 | Ν | z | С |

|-------|---------------------------|---------------------|--------|-----|----|---|----|---|---|---|

| ADC   | Add with Carry            | A = A + M + C       | А      | М   |    | Н |    | Ν | Ζ | С |

| ADD   | Addition                  | A=A+M               | А      | М   |    | Н |    | Ν | Ζ | С |

| AND   | Logical And               | A = A . M           | А      | М   |    |   |    | Ν | Z |   |

| BCP   | Bit compare A, Memory     | tst (A . M)         | А      | М   |    |   |    | Ν | Ζ |   |

| BRES  | Bit Reset                 | bres Byte, #3       | М      |     |    |   |    |   |   |   |

| BSET  | Bit Set                   | bset Byte, #3       | М      |     |    |   |    |   |   |   |

| BTJF  | Jump if bit is false (0)  | btjf Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| BTJT  | Jump if bit is true (1)   | btjt Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| CALL  | Call subroutine           |                     |        |     |    |   |    |   |   |   |

| CALLR | Call subroutine relative  |                     |        |     |    |   |    |   |   |   |

| CLR   | Clear                     |                     | reg, M |     |    |   |    | 0 | 1 |   |

| СР    | Arithmetic Compare        | tst(Reg - M)        | reg    | М   |    |   |    | Ν | Ζ | С |

| CPL   | One Complement            | A = FFH-A           | reg, M |     |    |   |    | Ν | Ζ | 1 |

| DEC   | Decrement                 | dec Y               | reg, M |     |    |   |    | Ν | Ζ |   |

| HALT  | Halt                      |                     |        |     | 1  |   | 0  |   |   |   |

| IRET  | Interrupt routine return  | Pop CC, A, X, PC    |        |     | 11 | Н | 10 | Ν | Ζ | С |

| INC   | Increment                 | inc X               | reg, M |     |    |   |    | Ν | Ζ |   |

| JP    | Absolute Jump             | jp [TBL.w]          |        |     |    |   |    |   |   |   |

| JRA   | Jump relative always      |                     |        |     |    |   |    |   |   |   |

| JRT   | Jump relative             |                     |        |     |    |   |    |   |   |   |

| JRF   | Never jump                | jrf *               |        |     |    |   |    |   |   |   |

| JRIH  | Jump if ext. INT pin = 1  | (ext. INT pin high) |        |     |    |   |    |   |   |   |

| JRIL  | Jump if ext. INT pin = 0  | (ext. INT pin low)  |        |     |    |   |    |   |   |   |

| JRH   | Jump if H = 1             | H = 1 ?             |        |     |    |   |    |   |   |   |

| JRNH  | Jump if H = 0             | H = 0 ?             |        |     |    |   |    |   |   |   |

| JRM   | Jump if I1:0 = 11         | 11:0 = 11 ?         |        |     |    |   |    |   |   |   |

| JRNM  | Jump if I1:0 <> 11        | 1:0 <> 11 ?         |        |     |    |   |    |   |   |   |

| JRMI  | Jump if N = 1 (minus)     | N = 1 ?             |        |     |    |   |    |   |   |   |

| JRPL  | Jump if N = 0 (plus)      | N = 0 ?             |        |     |    |   |    |   |   |   |

| JREQ  | Jump if Z = 1 (equal)     | Z = 1 ?             |        |     |    |   |    |   |   |   |

| JRNE  | Jump if Z = 0 (not equal) | Z = 0 ?             |        |     |    |   |    |   |   |   |

| JRC   | Jump if C = 1             | C = 1 ?             |        |     |    |   |    |   |   |   |

| JRNC  | Jump if $C = 0$           | C = 0 ?             |        |     |    |   |    |   |   |   |

| JRULT | Jump if C = 1             | Unsigned <          |        |     |    |   |    |   |   |   |

| JRUGE | Jump if C = 0             | Jmp if unsigned >=  |        |     |    |   |    |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$     | Unsigned >          |        |     |    |   |    |   |   |   |

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# 12.8.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                        | Parameter                                                                                                              |                 | Conditions                                                      | Min                                          | Max        | Unit |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------|----------------------------------------------|------------|------|

|                               | Output low level voltage for a standard I/O pin                                                                        |                 | I <sub>IO</sub> =+5mA                                           |                                              | 1.2        |      |

| 1)                            | when 8 pins are sunk at same time (see Figure 83)                                                                      |                 | I <sub>IO</sub> =+2mA                                           |                                              | 0.5        |      |

| V <sub>OL</sub> <sup>1)</sup> | Output low level voltage for a high sink I/O pin<br>when 4 pins are sunk at same time<br>(see Figure 84 and Figure 86) | <u>2</u>        | $I_{IO}$ =+20mA, $T_A \le 85^{\circ}C$<br>$T_A \ge 85^{\circ}C$ |                                              | 1.3<br>1.5 | v    |

|                               |                                                                                                                        | V <sub>DD</sub> | I <sub>IO</sub> =+8mA                                           |                                              | 0.6        |      |

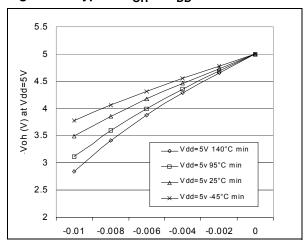

|                               | Output high level voltage for an I/O pin when 4 pins are sourced at same time                                          | ]               | $I_{IO}$ =-5mA, $T_A \le 85^{\circ}C$<br>$T_A \ge 85^{\circ}C$  | V <sub>DD</sub> -1.4<br>V <sub>DD</sub> -1.6 |            |      |

|                               | (see Figure 85 and Figure 88)                                                                                          |                 | I <sub>IO</sub> =-2mA                                           | V <sub>DD</sub> -0.7                         |            | 1    |

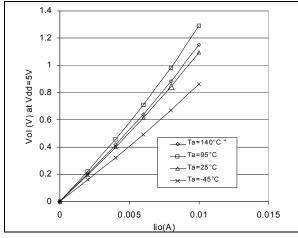

# Figure 83. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (standard)

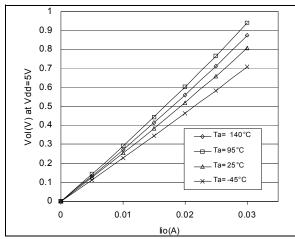

# Figure 84. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink)