Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                   |

| Number of I/O              | 48                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321r6t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| -      | CRIPTION                                                                   |    |

|--------|----------------------------------------------------------------------------|----|

|        | DESCRIPTION                                                                |    |

|        | ISTER & MEMORY MAP                                                         |    |

| -      | SH PROGRAM MEMORY                                                          | -  |

|        |                                                                            |    |

| 4.2    | MAIN FEATURES                                                              | 18 |

| 4.3    | STRUCTURE                                                                  | 18 |

|        | 4.3.1 Read-out Protection                                                  | 18 |

|        |                                                                            |    |

| 4.5    | ICP (IN-CIRCUIT PROGRAMMING)                                               | 20 |

| 4.6    | IAP (IN-APPLICATION PROGRAMMING)                                           | 20 |

| 4.7    | RELATED DOCUMENTATION                                                      | 20 |

|        | 4.7.1 Register Description                                                 | 20 |

| 5 CEN  | TRAL PROCESSING UNIT                                                       | 21 |

| 5.1    | INTRODUCTION                                                               | 21 |

| 5.2    | MAIN FEATURES                                                              | 21 |

| 5.3    | CPU REGISTERS                                                              | 21 |

| 6 SUP  | PLY, RESET AND CLOCK MANAGEMENT                                            | 24 |

|        | PHASE LOCKED LOOP                                                          |    |

| 6.2    | MULTI-OSCILLATOR (MO)                                                      | 25 |

|        | RESET SEQUENCE MANAGER (RSM)                                               |    |

|        | 6.3.1 Introduction                                                         |    |

|        | 6.3.2 Asynchronous External RESET pin                                      |    |

|        | 6.3.3 External Power-On RESET                                              | 27 |

|        | 6.3.4 Internal Low Voltage Detector (LVD) RESET                            |    |

|        | 6.3.5 Internal Watchdog RESET                                              |    |

| 6.4    | SYSTEM INTEGRITY MANAGEMENT (SI)                                           |    |

|        | 6.4.1 Low Voltage Detector (LVD)                                           |    |

|        | 6.4.2 Auxiliary Voltage Detector (AVD)                                     |    |

|        | <ul><li>6.4.3 Low Power Modes</li><li>6.4.4 Register Description</li></ul> |    |

| 7 INTE | RRUPTS                                                                     |    |

|        |                                                                            |    |

|        | MASKING AND PROCESSING FLOW                                                |    |

|        | INTERRUPTS AND LOW POWER MODES                                             |    |

|        | CONCURRENT & NESTED MANAGEMENT                                             |    |

|        |                                                                            |    |

|        |                                                                            |    |

| 7.6    |                                                                            |    |

|        | 7.6.1 I/O Port Interrupt Sensitivity                                       |    |

|        |                                                                            |    |

|        | /ER SAVING MODES       INTRODUCTION                                        |    |

|        |                                                                            |    |

|        | SLOW MODE                                                                  |    |

| 8.3    | WAIT MODE                                                                  | 42 |

# **Table of Contents**

|             | General Description                        |       |

|-------------|--------------------------------------------|-------|

|             | Clock Phase and Clock Polarity             |       |

|             | Error Flags                                |       |

|             | Interrupts                                 |       |

|             | Register Description                       |       |

|             |                                            |       |

|             | Introduction                               |       |

|             | Main Features                              |       |

| 10.6.3      | General Description                        | 99    |

| 10.6.4      | Functional Description                     | . 101 |

| 10.6.5      | Low Power Modes                            | . 108 |

|             | Interrupts                                 |       |

|             |                                            |       |

|             | S INTERFACE (I2C)                          |       |

|             |                                            |       |

|             | Main Features                              |       |

|             | General Description                        |       |

|             | Functional Description     Low Power Modes |       |

|             | Interrupts                                 |       |

|             | Register Description                       |       |

|             | A/D CONVERTER (ADC)                        |       |

|             |                                            |       |

|             | Main Features                              |       |

|             | Functional Description                     |       |

| 10.8.4      | Low Power Modes                            | . 129 |

|             | Interrupts                                 |       |

|             | Register Description                       |       |

|             | DN SET                                     |       |

|             | DRESSING MODES                             |       |

|             | Inherent                                   |       |

|             |                                            |       |

|             |                                            |       |

|             | Indexed (No Offset, Short, Long)           |       |

|             | Indirect Indexed (Short, Long)             |       |

|             | Relative mode (Direct, Indirect)           |       |

|             | ICTION GROUPS                              |       |

|             | L CHARACTERISTICS                          |       |

|             | ETER CONDITIONS                            |       |

| 12.1.1      | Minimum and Maximum values                 | . 138 |

|             | Typical values                             |       |

|             | Typical curves                             |       |

| 12.1.4      | Loading capacitor                          | . 138 |

|             | Pin input voltage                          |       |

| 12.2 ABSOLI | UTE MAXIMUM RATINGS                        | . 139 |

# **2 PIN DESCRIPTION**

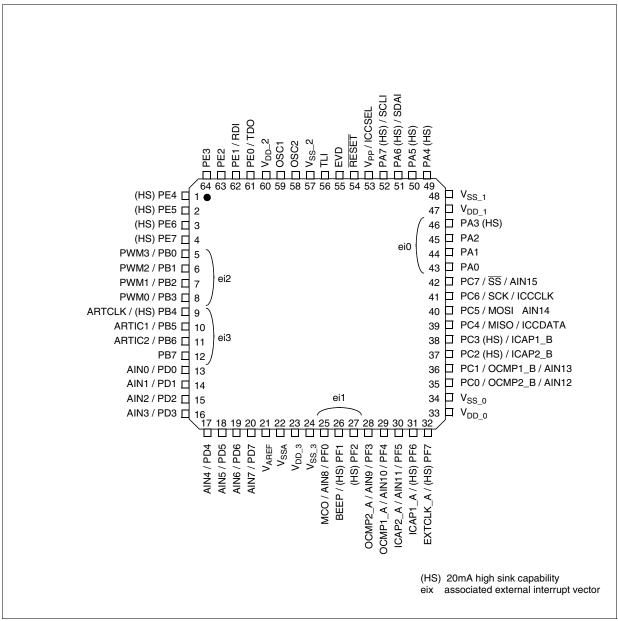

#### Figure 2. 64-Pin LQFP 14x14 and 10x10 Package Pinout

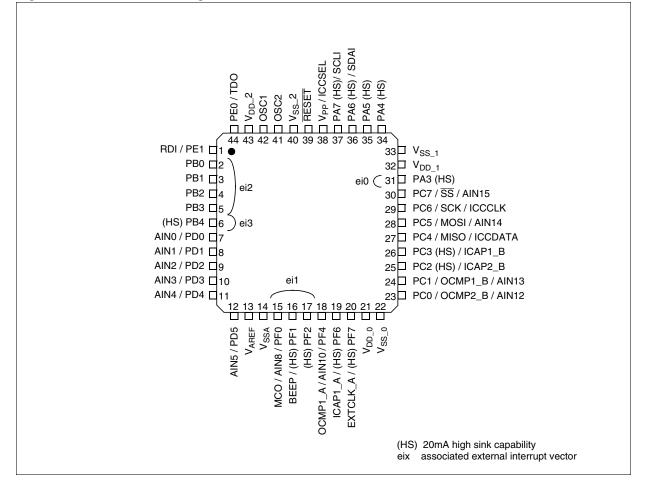

Figure 3. 44-Pin LQFP Package Pinout

57/

ISTICS for more details.

**۲**۲

3. OSC1 and OSC2 pins connect a crystal/ceramic resonator, or an external source to the on-chip oscillator; see Section 1 DESCRIPTION and Section 12.5 CLOCK AND TIMING CHARACTERISTICS for more details.

4. On the chip, each I/O port may have up to 8 pads:

- ads that are not bonded to external pins are forced by hardware in input pull-up configuration after reset.

The configuration of these pads must be kept at reset state to avoid added current consumption.

- 5. Pull-up always activated on PE2 see limitation Section 15.4.6.

6. It is mandatory to connect all available  $V_{DD}$  and  $V_{REF}$  pins to the supply voltage and all  $V_{SS}$  and  $V_{SSA}$  pins to ground.

# FLASH PROGRAM MEMORY (Cont'd)

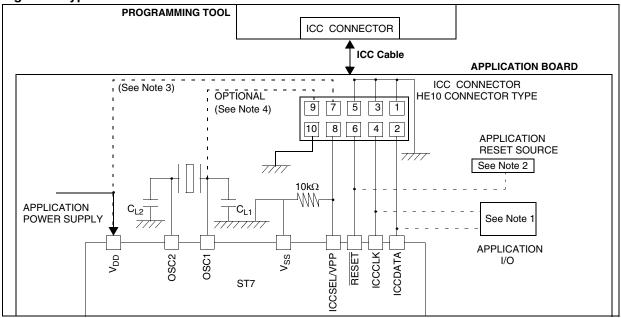

### 4.4 ICC Interface

ICC needs a minimum of 4 and up to 6 pins to be connected to the programming tool (see Figure 6). These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

#### Figure 6. Typical ICC Interface

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input/output serial data pin

- ICCSEL/V<sub>PP</sub>: programming voltage

- OSC1(or OSCIN): main clock input for external source (optional)

- V<sub>DD</sub>: application board power supply (optional, see Figure 6, Note 3)

#### Notes:

1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

2. During the IC<u>C</u> session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

3. The use of Pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

4. Pin 9 has to be connected to the OSC1 or OS-CIN pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

57

# CENTRAL PROCESSING UNIT (Cont'd)

Stack Pointer (SP)

Read/Write

57

Reset Value: 01 FFh

| 15  |     |     |     |     |     |     | 8   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| 7   |     |     |     |     |     |     | 0   |

| SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

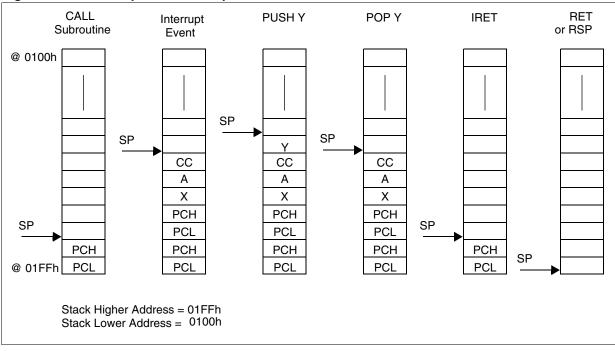

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 2).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

#### Figure 9. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 2.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

#### 6.2 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by three different source types coming from the multi-oscillator block:

- an external source

- 4 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 5. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. The product behaviour must therefore be considered undefined when the OSC pins are left unconnected.

#### **External Clock Source**

57/

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

#### Crystal/Ceramic Oscillators

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 4 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to section 14.1 on page 175 for more details on the frequency ranges). In this mode of the multi-oscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

|                            | Hardware Configuration                 |

|----------------------------|----------------------------------------|

| External Clock             | ST7<br>OSC1 OSC2<br>EXTERNAL<br>SOURCE |

| Crystal/Ceramic Resonators | CAPACITORS                             |

| Internal RC Oscillator     | OSC1 OSC2                              |

#### Table 5. ST7 Clock Sources

# 9 I/O PORTS

#### 9.1 INTRODUCTION

The I/O ports offer different functional modes: – transfer of data through digital inputs and outputs

- and for specific pins:

- external interrupt generation

- alternate signal input/output for the on-chip peripherals.

An I/O port contains up to 8 pins. Each pin can be programmed independently as digital input (with or without interrupt generation) or digital output.

#### 9.2 FUNCTIONAL DESCRIPTION

Each port has two main registers:

- Data Register (DR)

- Data Direction Register (DDR)

- and one optional register:

- Option Register (OR)

Each I/O pin may be programmed using the corresponding register bits in the DDR and OR registers: Bit X corresponding to pin X of the port. The same correspondence is used for the DR register.

The following description takes into account the OR register, (for specific ports which do not provide this register refer to the I/O Port Implementation section). The generic I/O block diagram is shown in Figure 1

#### 9.2.1 Input Modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

#### Notes:

1. Writing the DR register modifies the latch value but does not affect the pin status.

2. When switching from input to output mode, the DR register has to be written first to drive the correct level on the pin as soon as the port is configured as an output.

3. Do not use read/modify/write instructions (BSET or BRES) to modify the DR register as this might corrupt the DR content for I/Os configured as input.

#### **External interrupt function**

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU. Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several input pins are selected simultaneously as interrupt sources, these are first detected according to the sensitivity bits in the EICR register and then logically ORed.

The external interrupts are hardware interrupts, which means that the request latch (not accessible directly by the application) is automatically cleared when the corresponding interrupt vector is fetched. To clear an unwanted pending interrupt by software, the sensitivity bits in the EICR register must be modified.

#### 9.2.2 Output Modes

The output configuration is selected by setting the corresponding DDR register bit. In this case, writing the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output push-pull and open-drain.

DR register value and output pin status:

| DR | Push-pull       | Open-drain |

|----|-----------------|------------|

| 0  | V <sub>SS</sub> | Vss        |

| 1  | V <sub>DD</sub> | Floating   |

#### 9.2.3 Alternate Functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming.

When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin must be configured in input mode. In this case, the pin state is also digitally readable by addressing the DR register.

**Note**: Input pull-up configuration can cause unexpected value at the input of the alternate peripheral input. When an on-chip peripheral use a pin as input and output, this pin has to be configured in input floating mode.

# **10 ON-CHIP PERIPHERALS**

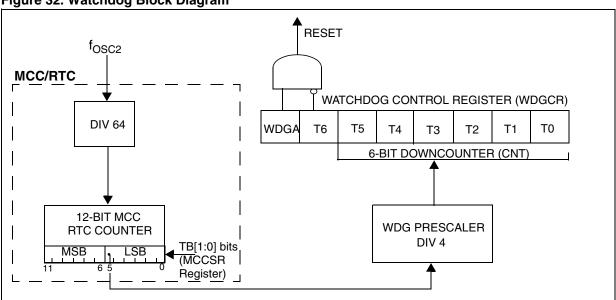

### 10.1 WATCHDOG TIMER (WDG)

#### 10.1.1 Introduction

The Watchdog timer is used to detect the occurrence of a software fault, usually generated by external interference or by unforeseen logical conditions, which causes the application program to abandon its normal sequence. The Watchdog circuit generates an MCU reset on expiry of a programmed time period, unless the program refreshes the counter's contents before the T6 bit becomes cleared.

#### 10.1.2 Main Features

- Programmable free-running downcounter

- Programmable reset

- Reset (if watchdog activated) when the T6 bit reaches zero

- HALT Optional reset on instruction (configurable by option byte)

- Hardware Watchdog selectable by option byte

### 10.1.3 Functional Description

The counter value stored in the Watchdog Control register (WDGCR bits T[6:0]), is decremented every 16384 f<sub>OSC2</sub> cycles (approx.), and the length of the timeout period can be programmed by the user in 64 increments.

If the watchdog is activated (the WDGA bit is set) and when the 7-bit timer (bits T[6:0]) rolls over from 40h to 3Fh (T6 becomes cleared), it initiates a reset cycle pulling the reset pin low for typically 30µs.

The application program must write in the WDGCR register at regular intervals during normal operation to prevent an MCU reset. This downcounter is free-running: it counts down even if the watchdog is disabled. The value to be stored in the WDGCR register must be between FFh and C0h:

- The WDGA bit is set (watchdog enabled)

- The T6 bit is set to prevent generating an immediate reset

- The T[5:0] bits contain the number of increments which represents the time delay before the watchdog produces a reset (see Figure 2. Approximate Timeout Duration). The timing varies between a minimum and a maximum value due to the unknown status of the prescaler when writing to the WDGCR register (see Figure 3).

Following a reset, the watchdog is disabled. Once activated it cannot be disabled, except by a reset.

The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction will generate a Reset.

### Figure 32. Watchdog Block Diagram

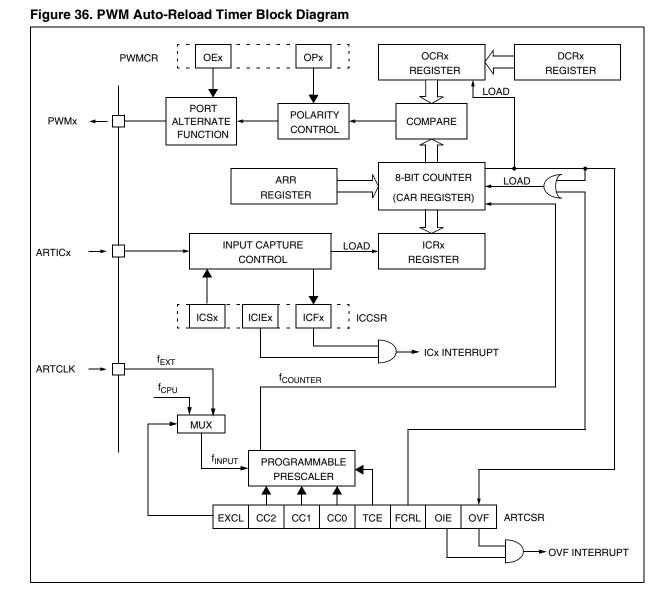

#### **10.3 PWM AUTO-RELOAD TIMER (ART)**

#### 10.3.1 Introduction

The Pulse Width Modulated Auto-Reload Timer on-chip peripheral consists of an 8-bit auto reload counter with compare/capture capabilities and of a 7-bit prescaler clock source.

These resources allow five possible operating modes:

- Generation of up to 4 independent PWM signals

- Output compare and Time base interrupt

- Up to two input capture functions

- External event detector

- Up to two external interrupt sources

The three first modes can be used together with a single counter frequency.

The timer can be used to wake up the MCU from WAIT and HALT modes.

60/193

### **ON-CHIP PERIPHERALS** (Cont'd)

#### PWM CONTROL REGISTER (PWMCR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| OE3 | OE2 | OE1 | OE0 | OP3 | OP2 | OP1 | OP0 |

#### Bit 7:4 = **OE[3:0]** *PWM Output Enable*

These bits are set and cleared by software. They enable or disable the PWM output channels independently acting on the corresponding I/O pin. 0: PWM output disabled.

1: PWM output enabled.

#### Bit 3:0 = OP[3:0] PWM Output Polarity

These bits are set and cleared by software. They independently select the polarity of the four PWM output signals.

| PWMx ou         | OPx |   |

|-----------------|-----|---|

| Counter <= OCRx |     |   |

| 1               | 0   | 0 |

| 0               | 1   | 1 |

**Note**: When an OPx bit is modified, the PWMx output signal polarity is immediately reversed.

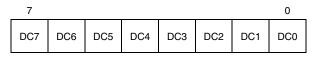

#### **DUTY CYCLE REGISTERS (PWMDCRx)**

Read/Write

Reset Value: 0000 0000 (00h)

# Bit 7:0 = DC[7:0] Duty Cycle Data

These bits are set and cleared by software.

A PWMDCRx register is associated with the OCRx register of each PWM channel to determine the second edge location of the PWM signal (the first edge location is common to all channels and given by the ARTARR register). These PWMDCR registers allow the duty cycle to be set independently for each PWM channel.

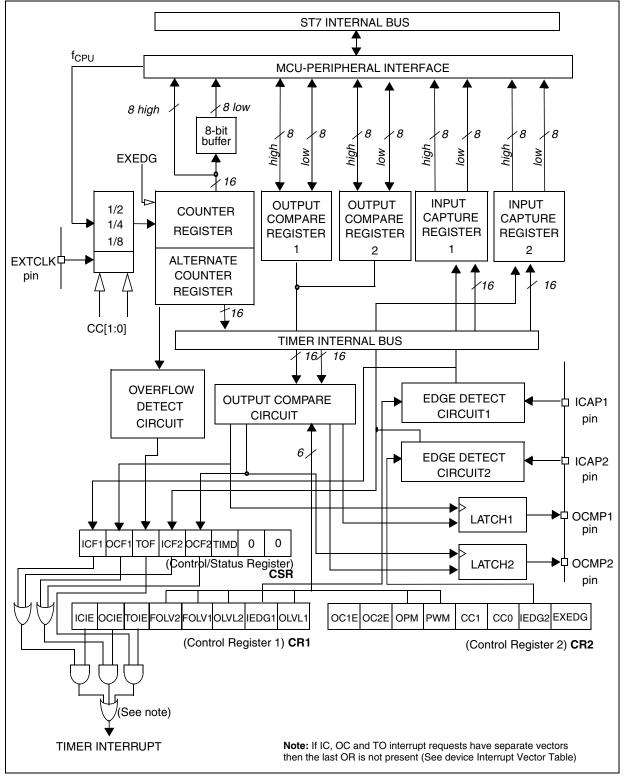

### 16-BIT TIMER (Cont'd)

#### Figure 42. Timer Block Diagram

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.6.4.3 Receiver

The SCI can receive data words of either 8 or 9 bits. When the M bit is set, word length is 9 bits and the MSB is stored in the R8 bit in the SCICR1 register.

#### Character reception

During a SCI reception, data shifts in least significant bit first through the RDI pin. In this mode, the SCIDR register consists or a buffer (RDR) between the internal bus and the received shift register (see Figure 1.).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIERPR registers.

- Set the RE bit, this enables the receiver which begins searching for a start bit.

When a character is received:

- The RDRF bit is set. It indicates that the content of the shift register is transferred to the RDR.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

- The error flags can be set if a frame error, noise or an overrun error has been detected during reception.

Clearing the RDRF bit is performed by the following software sequence done by:

- 1. An access to the SCISR register

- 2. A read to the SCIDR register.

The RDRF bit must be cleared before the end of the reception of the next character to avoid an overrun error.

#### **Break Character**

When a break character is received, the SCI handles it as a framing error.

#### **Idle Character**

When a idle frame is detected, there is the same procedure as a data received character plus an interrupt if the ILIE bit is set and the I bit is cleared in the CCR register.

#### **Overrun Error**

5/

An overrun error occurs when a character is received when RDRF has not been reset. Data can not be transferred from the shift register to the RDR register as long as the RDRF bit is not cleared.

When an overrun error occurs:

- The OR bit is set.

- The RDR content is not lost.

- The shift register is overwritten.

- An interrupt is generated if the RIE bit is set and the I bit is cleared in the CCR register.

The OR bit is reset by an access to the SCISR register followed by a SCIDR register read operation.

#### Noise Error

Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise. Normal data bits are considered valid if three consecutive samples (8th, 9th, 10th) have the same bit value, otherwise the NF flag is set. In the case of start bit detection, the NF flag is set on the basis of an algorithm combining both valid edge detection and three samples (8th, 9th, 10th). Therefore, to prevent the NF flag getting set during start bit reception, there should be a valid edge detection as well as three valid samples.

When noise is detected in a frame:

- The NF flag is set at the rising edge of the RDRF bit.

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The NF flag is reset by a SCISR register read operation followed by a SCIDR register read operation.

During reception, if a false start bit is detected (e.g. 8th, 9th, 10th samples are 011,101,110), the frame is discarded and the receiving sequence is not started for this frame. There is no RDRF bit set for this frame and the NF flag is set internally (not accessible to the user). This NF flag is accessible along with the RDRF bit when a next valid frame is received.

**Note:** If the application Start Bit is not long enough to match the above requirements, then the NF Flag may get set due to the short Start Bit. In this case, the NF flag may be ignored by the application software when the first valid byte is received.

See also Section 0.1.4.10.

# SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever

TDRE=1 in the SCISR register

Bit 6 = TCIE *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

#### Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

#### Bit 4 = **ILIE** *Idle line interrupt enable.*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

#### Bit 3 = **TE** *Transmitter enable*.

This bit enables the transmitter. It is set and cleared by software.

0: Transmitter is disabled

1: Transmitter is enabled

#### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**CAUTION:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

#### Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

#### Bit 1 = **RWU** Receiver wake-up.

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in Active mode

- 1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wake-up by idle line detection.

#### Bit 0 = **SBK** Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter sends a BREAK word at the end of the current word.

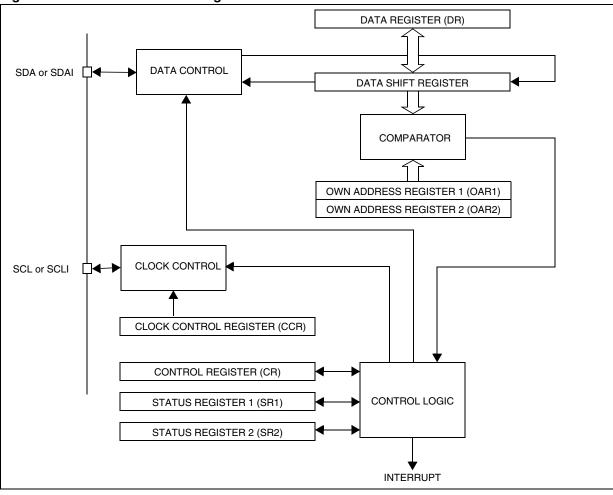

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

Acknowledge may be enabled and disabled by software.

The I<sup>2</sup>C interface address and/or general call address can be selected by software.

The speed of the  $I^2C$  interface may be selected between Standard (up to 100KHz) and Fast  $I^2C$  (up to 400KHz).

#### **SDA/SCL Line Control**

Transmitter mode: the interface holds the clock line low before transmission to wait for the microcontroller to write the byte in the Data Register.

Receiver mode: the interface holds the clock line low after reception to wait for the microcontroller to read the byte in the Data Register. The SCL frequency ( $F_{scl}$ ) is controlled by a programmable clock divider which depends on the I<sup>2</sup>C bus mode.

When the  $I^2C$  cell is enabled, the SDA and SCL ports must be configured as floating inputs. In this case, the value of the external pull-up resistor used depends on the application.

When the I<sup>2</sup>C cell is disabled, the SDA and SCL ports revert to being standard I/O port pins.

# Figure 65. I<sup>2</sup>C Interface Block Diagram

# I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C OWN ADDRESS REGISTER (OAR1)

Read / Write Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ADD7 | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

#### 7-bit Addressing Mode

Bit 7:1 = ADD[7:1] Interface address.

These bits define the  $l^2C$  bus address of the interface. They are not cleared when the interface is disabled (PE=0).

#### Bit 0 = ADD0 Address direction bit.

This bit is don't care, the interface acknowledges either 0 or 1. It is not cleared when the interface is disabled (PE=0).

Note: Address 01h is always ignored.

#### **10-bit Addressing Mode**

Bit 7:0 = **ADD**[7:0] Interface address.

These are the least significant bits of the  $I^2C$  bus address of the interface. They are not cleared when the interface is disabled (PE=0).

### I<sup>2</sup>C OWN ADDRESS REGISTER (OAR2)

Read / Write

Reset Value: 0100 0000 (40h)

| 7   |     |   |   |   |      |      | 0 |

|-----|-----|---|---|---|------|------|---|

| FR1 | FR0 | 0 | 0 | 0 | ADD9 | ADD8 | 0 |

#### Bit 7:6 = **FR[1:0]** *Frequency bits.*

These bits are set by software only when the interface is disabled (PE=0). To configure the interface to  $I^2C$  specified delays select the value corresponding to the microcontroller frequency  $F_{CPU}$ .

| f <sub>CPU</sub> | FR1 | FR0 |

|------------------|-----|-----|

| < 6 MHz          | 0   | 0   |

| 6 to 8 MHz       | 0   | 1   |

Bit 5:3 = Reserved

Bit 2:1 = ADD[9:8] Interface address.

These are the most significant bits of the  $I^2C$  bus address of the interface (10-bit mode only). They are not cleared when the interface is disabled (PE=0).

Bit 0 = Reserved.

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

The following table gives the values to be written in the I2CCCR register to obtain the required  $I^2C$  SCL line frequency.

#### Table 28. SCL Frequency Table

|                  |                         |                             |                          | I2CCCF                      | R Value                 |              |                  |                             |

|------------------|-------------------------|-----------------------------|--------------------------|-----------------------------|-------------------------|--------------|------------------|-----------------------------|

| f <sub>SCL</sub> |                         |                             | f <sub>CPU</sub> =8 MHz. |                             |                         |              |                  |                             |

| (kHz)            | V <sub>DD</sub> = 4.1 V |                             | V <sub>DD</sub> = 5 V    |                             | V <sub>DD</sub> = 4.1 V |              | $V_{DD} = 5 V$   |                             |

|                  | $R_P=3.3k\Omega$        | <b>R<sub>P</sub>=4.7k</b> Ω | $R_P=3.3k\Omega$         | <b>R<sub>P</sub>=4.7k</b> Ω | $R_P=3.3k\Omega$        | $R_P$ =4.7kΩ | $R_P=3.3k\Omega$ | <b>R<sub>P</sub>=4.7k</b> Ω |

| 400              | NA                      | NA                          | NA                       | NA                          | 83h                     | 83           | 83h              | 83h                         |

| 300              | NA                      | NA                          | NA                       | NA                          | 85h                     | 85h          | 85h              | 85h                         |

| 200              | 83h                     | 83h                         | 83h                      | 83h                         | 8Ah                     | 89h          | 8Ah              | 8Ah                         |

| 100              | 10h                     | 10h                         | 10h                      | 10h                         | 24h                     | 23h          | 24h              | 23h                         |

| 50               | 24h                     | 24h                         | 24h                      | 24h                         | 4Ch                     | 4Ch          | 4Ch              | 4Ch                         |

| 20               | 5Fh                     | 5Fh                         | 5Fh                      | 5Fh                         | FFh                     | FFh          | FFh              | FFh                         |

#### Legend:

$R_P$  = External pull-up resistance  $f_{SCL}$  = I<sup>2</sup>C speed NA = Not achievable

#### Note:

– For speeds around 200 kHz, achieved speed can have  $\pm 5\%$  tolerance

– For other speed ranges, achieved speed can have  $\pm 2\%$  tolerance

The above variations depend on the accuracy of the external components used.

### ADC CHARACTERISTICS (Cont'd)

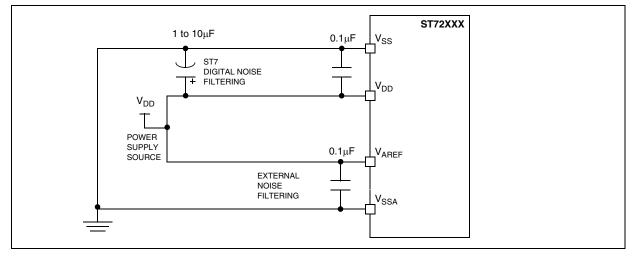

# 12.12.1 Analog Power Supply and Reference Pins

Depending on the MCU pin count, the package may feature separate V<sub>AREF</sub> and V<sub>SSA</sub> analog power supply pins. These pins supply power to the A/D converter cell and function as the high and low reference voltages for the conversion.

Separation of the digital and analog power pins allow board designers to improve A/D performance. Conversion accuracy can be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines (see Section 12.12.2 General PCB Design Guidelines).

#### 12.12.2 General PCB Design Guidelines

To obtain best results, some general design and layout rules should be followed when designing the application PCB to shield the noise-sensitive, analog physical interface from noise-generating CMOS logic signals.

Use separate digital and analog planes. The analog ground plane should be connected to the digital ground plane via a single point on the PCB.

- Filter power to the analog power planes. It is recommended to connect capacitors, with good high frequency characteristics, between the power and ground lines, placing 0.1µF and optionally, if needed 10pF capacitors as close as possible to the ST7 power supply pins and a 1 to 10µF capacitor close to the power source (see Figure 99).

- The analog and digital power supplies should be connected in a star network. Do not use a resistor, as V<sub>AREF</sub> is used as a reference voltage by the A/D converter and any resistance would cause a voltage drop and a loss of accuracy.

- Properly place components and route the signal traces on the PCB to shield the analog inputs. Analog signals paths should run over the analog ground plane and be as short as possible. Isolate analog signals from digital signals that may switch while the analog inputs are being sampled by the A/D converter. Do not toggle digital outputs on the same I/O port as the A/D input being converted.

#### Figure 99. Power Supply Filtering

47/

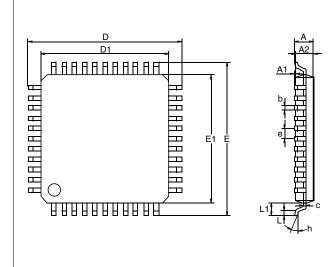

# PACKAGE MECHANICAL DATA (Cont'd)

# Figure 103. 44-Pin Low Profile Quad Flat Package

| Dim  |                | mm    |      | inches <sup>1)</sup> |        |        |  |  |

|------|----------------|-------|------|----------------------|--------|--------|--|--|

| Dim. | Min            | Тур   | Max  | Min                  | Тур    | Max    |  |  |

| Α    |                |       | 1.60 |                      |        | 0.0630 |  |  |

| A1   | 0.05           |       | 0.15 | 0.0020               |        | 0.0059 |  |  |

| A2   | 1.35           | 1.40  | 1.45 | 0.0531               | 0.0551 | 0.0571 |  |  |

| b    | 0.30           | 0.37  | 0.45 | 0.0118               | 0.0146 | 0.0177 |  |  |

| С    | 0.09           |       | 0.20 | 0.0035               |        | 0.0079 |  |  |

| D    |                | 12.00 |      |                      | 0.4724 |        |  |  |

| D1   |                | 10.00 |      |                      | 0.3937 |        |  |  |

| Е    |                | 12.00 |      |                      | 0.4724 |        |  |  |

| E1   |                | 10.00 |      |                      | 0.3937 |        |  |  |

| е    |                | 0.80  |      |                      | 0.0315 |        |  |  |

| θ    | 0°             | 3.5°  | 7°   | 0°                   | 3.5°   | 7°     |  |  |

| L    | 0.45           | 0.60  | 0.75 | 0.0177               | 0.0236 | 0.0295 |  |  |

| L1   |                | 1.00  |      |                      | 0.0394 |        |  |  |

|      | Number of Pins |       |      |                      |        |        |  |  |

| Ν    | 44             |       |      |                      |        |        |  |  |

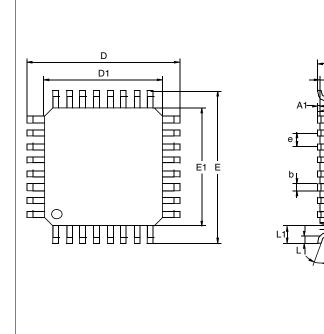

#### Figure 104. 32-Pin Low Profile Quad Flat Package

| Dim. |                | mm   |      | inches <sup>1)</sup> |        |        |  |  |

|------|----------------|------|------|----------------------|--------|--------|--|--|

| Dim. | Min            | Тур  | Max  | Min                  | Тур    | Max    |  |  |

| Α    |                |      | 1.60 |                      |        | 0.0630 |  |  |

| A1   | 0.05           |      | 0.15 | 0.0020               |        | 0.0059 |  |  |

| A2   | 1.35           | 1.40 | 1.45 | 0.0531               | 0.0551 | 0.0571 |  |  |

| b    | 0.30           | 0.37 | 0.45 | 0.0118               | 0.0146 | 0.0177 |  |  |

| С    | 0.09           |      | 0.20 | 0.0035               |        | 0.0079 |  |  |

| D    |                | 9.00 |      |                      | 0.3543 |        |  |  |

| D1   |                | 7.00 |      |                      | 0.2756 |        |  |  |

| Е    |                | 9.00 |      |                      | 0.3543 |        |  |  |

| E1   |                | 7.00 |      |                      | 0.2756 |        |  |  |

| е    |                | 0.80 |      |                      | 0.0315 |        |  |  |

| θ    | 0°             | 3.5° | 7°   | 0°                   | 3.5°   | 7°     |  |  |

| L    | 0.45           | 0.60 | 0.75 | 0.0177               | 0.0236 | 0.0295 |  |  |

| L1   |                | 1.00 |      |                      | 0.0394 |        |  |  |

|      | Number of Pins |      |      |                      |        |        |  |  |

| Ν    | 32             |      |      |                      |        |        |  |  |