# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I²C, SCI, SPI                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321r9tctr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **5 CENTRAL PROCESSING UNIT**

### **5.1 INTRODUCTION**

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

### **5.2 MAIN FEATURES**

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

### **5.3 CPU REGISTERS**

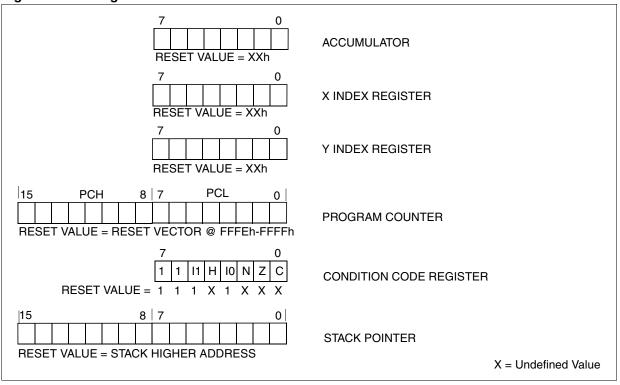

The six CPU registers shown in Figure 1 are not present in the memory mapping and are accessed by specific instructions.

### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

### Index Registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

### Program Counter (PC)

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

Figure 8. CPU Registers

5/

### INTERRUPTS (Cont'd)

### 7.5 INTERRUPT REGISTER DESCRIPTION

### **CPU CC REGISTER INTERRUPT BITS**

Read/Write

5/

Reset Value: 111x 1010 (xAh)

| 7 |   |    |   |    |   |   | 0 |

|---|---|----|---|----|---|---|---|

| 1 | 1 | 11 | н | 10 | Ν | Z | С |

Bit 5, 3 = 11, 10 Software Interrupt Priority

These two bits indicate the current interrupt software priority.

| Interrupt Software Priority    | Level | l1 | 10 |

|--------------------------------|-------|----|----|

| Level 0 (main)                 | Low   | 1  | 0  |

| Level 1                        |       | 0  | 1  |

| Level 2                        | ▼     | 0  | 0  |

| Level 3 (= interrupt disable*) | High  | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (ISPRx).

They can be also set/cleared by software with the RIM, SIM, HALT, WFI, IRET and PUSH/POP instructions (see "Interrupt Dedicated Instruction Set" table).

\*Note: TLI, TRAP and RESET events can interrupt a level 3 program.

### INTERRUPT SOFTWARE PRIORITY REGIS-TERS (ISPRX)

Read/Write (bit 7:4 of **ISPR3** are read only) Reset Value: 1111 1111 (FFh)

| _     | 7     |       |       |       |       |       |       | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| ISPR0 | l1_3  | 10_3  | l1_2  | 10_2  | 11_1  | 10_1  | l1_0  | 10_0  |

| ISPR1 | 11_7  | 10_7  | l1_6  | 10_6  | l1_5  | I0_5  | 11_4  | 10_4  |

| ISPR2 | 11_11 | 10_11 | 11_10 | 10_10 | l1_9  | 10_9  | l1_8  | 10_8  |

| ISPR3 | 1     | 1     | 1     | 1     | 11_13 | 10_13 | 11_12 | 10_12 |

These four registers contain the interrupt software priority of each interrupt vector.

Each interrupt vector (except RESET and TRAP) has corresponding bits in these registers where its own software priority is stored. This correspondance is shown in the following table.

| Vector address | ISPRx bits           |

|----------------|----------------------|

| FFFBh-FFFAh    | I1_0 and I0_0 bits*  |

| FFF9h-FFF8h    | I1_1 and I0_1 bits   |

|                |                      |

| FFE1h-FFE0h    | I1_13 and I0_13 bits |

Each I1\_x and I0\_x bit value in the ISPRx registers has the same meaning as the I1 and I0 bits in the CC register.

Level 0 can not be written (I1\_x=1, I0\_x=0). In this case, the previously stored value is kept. (example: previous=CFh, write=64h, result=44h)

The TLI, RESET, and TRAP vectors have no software priorities. When one is serviced, the I1 and I0 bits of the CC register are both set.

\*Note: Bits in the ISPRx registers which correspond to the TLI can be read and written but they are not significant in the interrupt process management.

**Caution**: If the  $I1_x$  and  $I0_x$  bits are modified while the interrupt x is executed the following behaviour has to be considered: If the interrupt x is still pending (new interrupt or flag not cleared) and the new software priority is higher than the previous one, the interrupt x is re-entered. Otherwise, the software priority stays unchanged up to the next interrupt request (after the IRET of the interrupt x).

### INTERRUPTS (Cont'd)

### **Table 8. Interrupt Mapping**

| N° | Source<br>Block | Description                               | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT <sup>3)</sup> | Address<br>Vector |

|----|-----------------|-------------------------------------------|-------------------|-------------------|------------------------------------|-------------------|

|    | RESET           | Reset                                     | N/A               |                   | yes                                | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                        | IN/A              |                   | no                                 | FFFCh-FFFDh       |

| 0  | TLI             | External top level interrupt              | EICR              |                   | yes                                | FFFAh-FFFBh       |

| 1  | MCC/RTC         | Main clock controller time base interrupt | MCCSR             | Higher            | yes                                | FFF8h-FFF9h       |

| 2  | ei0             | External interrupt port A30               |                   | Priority          | yes                                | FFF6h-FFF7h       |

| 3  | ei1             | External interrupt port F20               | N/A               |                   | yes                                | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt port B30               | - IN/A            |                   | yes                                | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt port B74               |                   | 1                 | yes                                | FFF0h-FFF1h       |

| 6  |                 | Not used                                  |                   |                   |                                    | FFEEh-FFEFh       |

| 7  | SPI             | SPI peripheral interrupts                 | SPICSR            |                   | yes <sup>1</sup>                   | FFECh-FFEDh       |

| 8  | TIMER A         | TIMER A peripheral interrupts             | TASR              | ★                 | no                                 | FFEAh-FFEBh       |

| 9  | TIMER B         | TIMER B peripheral interrupts             | TBSR              |                   | no                                 | FFE8h-FFE9h       |

| 10 | SCI             | SCI Peripheral interrupts                 | SCISR             | Lower             | no                                 | FFE6h-FFE7h       |

| 11 | AVD             | Auxiliary Voltage detector interrupt      | SICSR             | Priority          | no                                 | FFE4h-FFE5h       |

| 12 | I2C             | I2C Peripheral interrupts                 | (see periph)      |                   | no                                 | FFE2h-FFE3h       |

| 13 | PWM ART         | PWM ART interrupt                         | ARTCSR            |                   | yes <sup>2</sup>                   | FFE0h-FFE1h       |

### Notes:

- 1. Exit from HALT possible when SPI is in slave mode.

- 2. Exit from HALT possible when PWM ART is in external clock mode.

- 3. Only a RESET or MCC/RTC interrupt can be used to wake-up from Active Halt mode.

### 7.6 EXTERNAL INTERRUPTS

### 7.6.1 I/O Port Interrupt Sensitivity

The external interrupt sensitivity is controlled by the IPA, IPB and ISxx bits of the EICR register (Figure 22). This control allows to have up to 4 fully independent external interrupt source sensitivities.

Each external interrupt source can be generated on four (or five) different events on the pin:

- Falling edge

- Rising edge

57/

Falling and rising edge

- Falling edge and low level

- Rising edge and high level (only for ei0 and ei2)

To guarantee correct functionality, the sensitivity bits in the EICR register can be modified only when the I1 and I0 bits of the CC register are both set to 1 (level 3). This means that interrupts must be disabled before changing sensitivity.

The pending interrupts are cleared by writing a different value in the ISx[1:0], IPA or IPB bits of the EICR.

### 9 I/O PORTS

### 9.1 INTRODUCTION

The I/O ports offer different functional modes: – transfer of data through digital inputs and outputs

- and for specific pins:

- external interrupt generation

- alternate signal input/output for the on-chip peripherals.

An I/O port contains up to 8 pins. Each pin can be programmed independently as digital input (with or without interrupt generation) or digital output.

### 9.2 FUNCTIONAL DESCRIPTION

Each port has two main registers:

- Data Register (DR)

- Data Direction Register (DDR)

- and one optional register:

- Option Register (OR)

Each I/O pin may be programmed using the corresponding register bits in the DDR and OR registers: Bit X corresponding to pin X of the port. The same correspondence is used for the DR register.

The following description takes into account the OR register, (for specific ports which do not provide this register refer to the I/O Port Implementation section). The generic I/O block diagram is shown in Figure 1

### 9.2.1 Input Modes

The input configuration is selected by clearing the corresponding DDR register bit.

In this case, reading the DR register returns the digital value applied to the external I/O pin.

Different input modes can be selected by software through the OR register.

#### Notes:

1. Writing the DR register modifies the latch value but does not affect the pin status.

2. When switching from input to output mode, the DR register has to be written first to drive the correct level on the pin as soon as the port is configured as an output.

3. Do not use read/modify/write instructions (BSET or BRES) to modify the DR register as this might corrupt the DR content for I/Os configured as input.

### **External interrupt function**

When an I/O is configured as Input with Interrupt, an event on this I/O can generate an external interrupt request to the CPU. Each pin can independently generate an interrupt request. The interrupt sensitivity is independently programmable using the sensitivity bits in the EICR register.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several input pins are selected simultaneously as interrupt sources, these are first detected according to the sensitivity bits in the EICR register and then logically ORed.

The external interrupts are hardware interrupts, which means that the request latch (not accessible directly by the application) is automatically cleared when the corresponding interrupt vector is fetched. To clear an unwanted pending interrupt by software, the sensitivity bits in the EICR register must be modified.

### 9.2.2 Output Modes

The output configuration is selected by setting the corresponding DDR register bit. In this case, writing the DR register applies this digital value to the I/O pin through the latch. Then reading the DR register returns the previously stored value.

Two different output modes can be selected by software through the OR register: Output push-pull and open-drain.

DR register value and output pin status:

| DR | Push-pull       | Open-drain |

|----|-----------------|------------|

| 0  | V <sub>SS</sub> | Vss        |

| 1  | V <sub>DD</sub> | Floating   |

### 9.2.3 Alternate Functions

When an on-chip peripheral is configured to use a pin, the alternate function is automatically selected. This alternate function takes priority over the standard I/O programming.

When the signal is coming from an on-chip peripheral, the I/O pin is automatically configured in output mode (push-pull or open drain according to the peripheral).

When the signal is going to an on-chip peripheral, the I/O pin must be configured in input mode. In this case, the pin state is also digitally readable by addressing the DR register.

**Note:** Input pull-up configuration can cause unexpected value at the input of the alternate peripheral input. When an on-chip peripheral use a pin as input and output, this pin has to be configured in input floating mode.

### **ON-CHIP PERIPHERALS** (Cont'd)

57

### **Output compare and Time base interrupt**

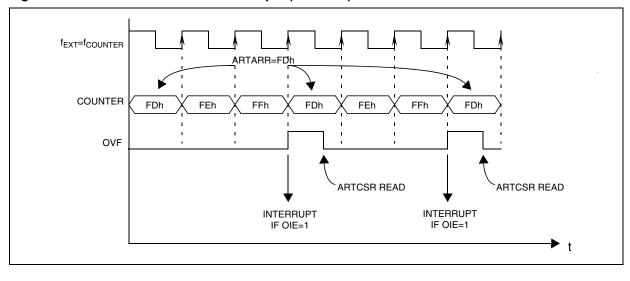

On overflow, the OVF flag of the ARTCSR register is set and an overflow interrupt request is generated if the overflow interrupt enable bit, OIE, in the ARTCSR register, is set. The OVF flag must be reset by the user software. This interrupt can be used as a time base in the application.

### External clock and event detector mode

Using the  $f_{EXT}$  external prescaler input clock, the auto-reload timer can be used as an external clock event detector. In this mode, the ARTARR register is used to select the  $n_{EVENT}$  number of events to be counted before setting the OVF flag.

### n<sub>EVENT</sub> = 256 - ARTARR

**Caution:** The external clock function is not available in HALT mode. If HALT mode is used in the application, prior to executing the HALT instruction, the counter must be disabled by clearing the TCE bit in the ARTCSR register to avoid spurious counter increments.

#### Figure 40. External Event Detector Example (3 counts)

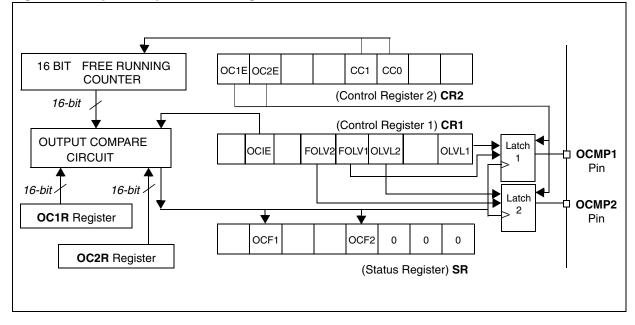

### 16-BIT TIMER (Cont'd)

### Notes:

- 1. After a processor write cycle to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- If the OC*i*E bit is not set, the OCMP*i* pin is a general I/O port and the OLVL*i* bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- 3. In both internal and external clock modes, OCFi and OCMPi are set while the counter value equals the OCiR register value (see Figure 8 for an example with  $f_{CPU}/2$  and Figure 9 for an example with  $f_{CPU}/4$ ). This behavior is the same in OPM or PWM mode.

- The output compare functions can be used both for generating external events on the OCMP*i* pins even if the input capture mode is also used.

- 5. The value in the 16-bit OC*i*R register and the OLV*i* bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

### Forced Compare Output capability

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit = 1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

The FOLVL*i* bits have no effect in both One Pulse mode and PWM mode.

### Figure 48. Output Compare Block Diagram

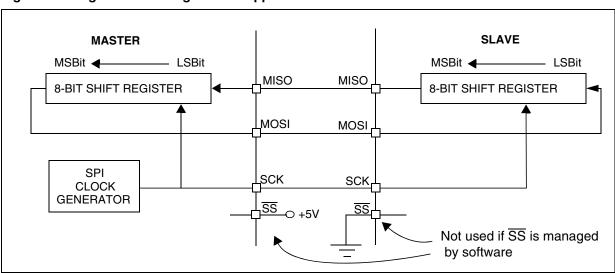

### SERIAL PERIPHERAL INTERFACE (Cont'd)

- SS: Slave select:

57/

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master MCU.

### 10.5.3.1 Functional Description

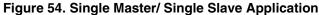

A basic example of interconnections between a single master and a single slave is illustrated in Figure 54.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 57) but master and slave must be programmed with the same timing mode.

### **10.6 SERIAL COMMUNICATIONS INTERFACE (SCI)**

### 10.6.1 Introduction

The Serial Communications Interface (SCI) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format. The SCI offers a very wide range of baud rates using two baud rate generator systems.

### 10.6.2 Main Features

- Full duplex, asynchronous communications

- NRZ standard format (Mark/Space)

- Dual baud rate generator systems

- Independently programmable transmit and receive baud rates up to 500K baud

- Programmable data word length (8 or 9 bits)

- Receive buffer full, Transmit buffer empty and End of Transmission flags

- Two receiver wake-up modes:

- Address bit (MSB)

- Idle line

- Muting function for multiprocessor configurations

- Separate enable bits for Transmitter and Receiver

- Four error detection flags:

- Overrun error

- Noise error

- Frame error

- Parity error

- Five interrupt sources with flags:

- Transmit data register empty

- Transmission complete

- Receive data register full

- Idle line received

- Overrun error detected

- Parity control:

5/

- Transmits parity bit

- Checks parity of received data byte

- Reduced power consumption mode

### **10.6.3 General Description**

The interface is externally connected to another device by two pins (see Figure 2.):

- TDO: Transmit Data Output. When the transmitter and the receiver are disabled, the output pin returns to its I/O port configuration. When the transmitter and/or the receiver are enabled and nothing is to be transmitted, the TDO pin is at high level.

- RDI: Receive Data Input is the serial data input. Oversampling techniques are used for data recovery by discriminating between valid incoming data and noise.

Through these pins, serial data is transmitted and received as frames comprising:

- An Idle Line prior to transmission or reception

- A start bit

- A data word (8 or 9 bits) least significant bit first

- A Stop bit indicating that the frame is complete

- This interface uses two types of baud rate generator:

- A conventional type for commonly-used baud rates

- An extended type with a prescaler offering a very wide range of baud rates even with non-standard oscillator frequencies

### I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C STATUS REGISTER 1 (SR1)

Read Only

Reset Value: 0000 0000 (00h)

| 7   |       |     |      |     |      |      | 0  |

|-----|-------|-----|------|-----|------|------|----|

| EVF | ADD10 | TRA | BUSY | BTF | ADSL | M/SL | SB |

### Bit 7 = **EVF** Event flag.

This bit is set by hardware as soon as an event occurs. It is cleared by software reading SR2 register in case of error event or as described in Figure 66. It is also cleared by hardware when the interface is disabled (PE=0).

### 0: No event

- 1: One of the following events has occurred:

- BTF=1 (Byte received or transmitted)

- ADSL=1 (Address matched in Slave mode while ACK=1)

- SB=1 (Start condition generated in Master mode)

- AF=1 (No acknowledge received after byte transmission)

- STOPF=1 (Stop condition detected in Slave mode)

- ARLO=1 (Arbitration lost in Master mode)

- BERR=1 (Bus error, misplaced Start or Stop condition detected)

- ADD10=1 (Master has sent header byte)

- Address byte successfully transmitted in Master mode.

Bit 6 = **ADD10** *10-bit addressing in Master mode.* This bit is set by hardware when the master has sent the first byte in 10-bit address mode. It is cleared by software reading SR2 register followed by a write in the DR register of the second address byte. It is also cleared by hardware when the peripheral is disabled (PE=0).

0: No ADD10 event occurred.

1: Master has sent first address byte (header)

### Bit 5 = TRA Transmitter/Receiver.

When BTF is set, TRA=1 if a data byte has been transmitted. It is cleared automatically when BTF is cleared. It is also cleared by hardware after detection of Stop condition (STOPF=1), loss of bus arbitration (ARLO=1) or when the interface is disabled (PE=0).

0: Data byte received (if BTF=1)

### 1: Data byte transmitted

### Bit 4 = **BUSY** Bus busy.

This bit is set by hardware on detection of a Start condition and cleared by hardware on detection of a Stop condition. It indicates a communication in progress on the bus. The BUSY flag of the I2CSR1 register is cleared if a Bus Error occurs.

0: No communication on the bus

1: Communication ongoing on the bus Note:

- The BUSY flag is NOT updated when the interface is disabled (PE=0). This can have consequences when operating in Multimaster mode; i.e. a second active I<sup>2</sup>C master commencing a transfer with an unset BUSY bit can cause a conflict resulting in lost data. A software workaround consists of checking that the I<sup>2</sup>C is not busy before enabling the I<sup>2</sup>C Multimaster cell.

### Bit 3 = **BTF** Byte transfer finished.

This bit is set by hardware as soon as a byte is correctly received or transmitted with interrupt generation if ITE=1. It is cleared by software reading SR1 register followed by a read or write of DR register. It is also cleared by hardware when the interface is disabled (PE=0).

- Following a byte transmission, this bit is set after reception of the acknowledge clock pulse. In case an address byte is sent, this bit is set only after the EV6 event (See Figure 66). BTF is cleared by reading SR1 register followed by writing the next byte in DR register.

- Following a byte reception, this bit is set after transmission of the acknowledge clock pulse if ACK=1. BTF is cleared by reading SR1 register followed by reading the byte from DR register.

The SCL line is held low while BTF=1.

- 0: Byte transfer not done

- 1: Byte transfer succeeded

Bit 2 = **ADSL** Address matched (Slave mode). This bit is set by hardware as soon as the received slave address matched with the OAR register content or a general call is recognized. An interrupt is generated if ITE=1. It is cleared by software reading SR1 register or by hardware when the interface is disabled (PE=0).

The SCL line is held low while ADSL=1.

- 0: Address mismatched or not received

- 1: Received address matched

### I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C CLOCK CONTROL REGISTER (CCR)

Read / Write Reset Value: 0000 0000 (00h)

| 7     |     |     |     |     |     |     | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| FM/SM | CC6 | CC5 | CC4 | CC3 | CC2 | CC1 | CC0 |

### Bit 7 = **FM/SM** Fast/Standard $l^2C$ mode.

This bit is set and cleared by software. It is not cleared when the interface is disabled (PE=0). 0: Standard  $I^2C$  mode

1: Fast I<sup>2</sup>C mode

Bit 6:0 = CC[6:0] 7-bit clock divider.

These bits select the speed of the bus ( $F_{SCL}$ ) depending on the I<sup>2</sup>C mode. They are not cleared when the interface is disabled (PE=0).

Refer to the Electrical Characteristics section for the table of values.

Note: The programmed  $\mathrm{F}_{\mathrm{SCL}}$  assumes no load on SCL and SDA lines.

### I<sup>2</sup>C DATA REGISTER (DR)

### Read / Write

Reset Value: 0000 0000 (00h)

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

Bit 7:0 = **D**[7:0] 8-bit Data Register.

These bits contain the byte to be received or transmitted on the bus.

- Transmitter mode: Byte transmission start automatically when the software writes in the DR register.

- Receiver mode: the first data byte is received automatically in the DR register using the least significant bit of the address.

Then, the following data bytes are received one by one after reading the DR register.

### INSTRUCTION SET OVERVIEW (Cont'd)

### **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | СР   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

### Using a prebyte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

- PC-2 End of previous instruction

- PC-1 Prebyte

- PC Opcode

57

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address

These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

### **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                    | Ratings                                             | Maximum value                                | Unit |  |

|-------------------------------------------|-----------------------------------------------------|----------------------------------------------|------|--|

| V <sub>DD</sub> - V <sub>SS</sub>         | Supply voltage                                      | 6.5                                          |      |  |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming Voltage                                 | 13                                           | V    |  |

| V <sub>IN</sub> <sup>1) &amp; 2)</sup>    | Input Voltage on true open drain pin                | V <sub>SS</sub> -0.3 to 6.5                  | v    |  |

| VIN / / /                                 | Input voltage on any other pin                      | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 |      |  |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | Variations between different digital power pins     | 50                                           | mV   |  |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | Variations between digital and analog ground pins   | 50                                           | IIIV |  |

| V <sub>ESD(HBM)</sub>                     | Electro-static discharge voltage (Human Body Model) | and postion 10.7.2 on page 155               |      |  |

| V <sub>ESD(MM)</sub>                      | Electro-static discharge voltage (Machine Model)    | see section 12.7.3 on page 155               |      |  |

#### **12.2.2 Current Characteristics**

| Symbol                                       | Ratings                                                                | Maximum value | Unit |

|----------------------------------------------|------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                             | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup>  | 150           | mA   |

| I <sub>VSS</sub>                             | Total current out of $V_{SS}$ ground lines (sink) <sup>3)</sup>        | 150           | IIIA |

|                                              | Output current sunk by any standard I/O and control pin                | 25            |      |

| I <sub>IO</sub>                              | Output current sunk by any high sink I/O pin                           | 50            |      |

|                                              | Output current source by any I/Os and control pin                      | - 25          |      |

|                                              | Injected current on V <sub>PP</sub> pin                                | ± 5           |      |

|                                              | Injected current on RESET pin                                          | ± 5           | mA   |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 4)</sup> | Injected current on OSC1 and OSC2 pins                                 | ± 5           |      |

|                                              | Injected current on PB0 (Flash devices only)                           | + 5           |      |

|                                              | Injected current on any other pin <sup>5) &amp; 6)</sup>               | ± 5           |      |

| ΣI <sub>INJ(PIN)</sub> <sup>2)</sup>         | Total injected current (sum of all I/O and control pins) <sup>5)</sup> | ± 25          |      |

#### Notes:

1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7k $\Omega$  for RESET, 10k $\Omega$  for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

3. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "ADC Accuracy" on page 170.

For best reliability, it is recommended to avoid negative injection of more than 1.6mA.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

6. True open drain I/O port pins do not accept positive injection.

### **12.2.3 Thermal Characteristics**

| Symbol           | Ratings                                                                 | Value       | Unit |  |  |

|------------------|-------------------------------------------------------------------------|-------------|------|--|--|

| T <sub>STG</sub> | Storage temperature range                                               | -65 to +150 | °C   |  |  |

| TJ               | Maximum junction temperature (see Section 13.2 THERMAL CHARACTERISTICS) |             |      |  |  |

### **12.3 OPERATING CONDITIONS**

### **12.3.1 General Operating Conditions**

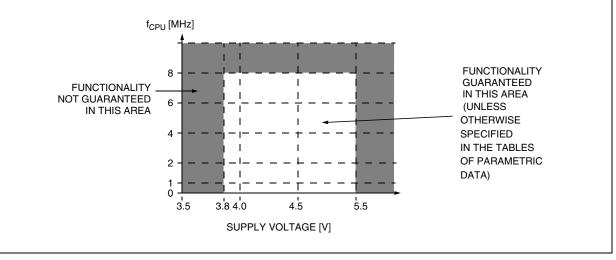

| Symbol           | Parameter                                            | Conditions                      | Min | Max | Unit |

|------------------|------------------------------------------------------|---------------------------------|-----|-----|------|

| f <sub>CPU</sub> | Internal clock frequency                             |                                 | 0   | 8   | MHz  |

| V <sub>DD</sub>  | Standard voltage range (except Flash<br>Write/Erase) |                                 | 3.8 | 5.5 | v    |

|                  | Operating Voltage for Flash Write/Erase              | V <sub>PP</sub> = 11.4 to 12.6V | 4.5 | 5.5 |      |

| Τ <sub>Α</sub>   | Ambient temperature renge                            | 3 Suffix Version                | -40 | 125 | °C   |

|                  | Ambient temperature range                            | 6 Suffix Version                | -40 | 85  |      |

### Figure 71. $f_{CPU}$ Max Versus $V_{DD}$

**Note:** Some temperature ranges are only available with a specific package and memory size. Refer to Ordering Information.

### **OPERATING CONDITIONS** (Cont'd)

### 12.3.2 Operating Conditions with Low Voltage Detector (LVD)

| Symbol                | Parameter                                                    | Conditions                                   | Min                | Тур  | Max                 | Unit |

|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|------|---------------------|------|

|                       | Reset release threshold                                      | VD level = High in option byte               | 4.0 <sup>1)</sup>  | 4.2  | 4.5                 |      |

| V <sub>IT+(LVD)</sub> | (V <sub>DD</sub> rise)                                       | VD level = Med. in option byte <sup>2)</sup> | 3.55 <sup>1)</sup> | 3.75 | 4.0 <sup>1)</sup>   |      |

|                       |                                                              | VD level = Low in option byte <sup>2)</sup>  | 2.95 <sup>1)</sup> | 3.15 | 3.35 <sup>1)</sup>  | V    |

|                       | Report generation threshold                                  | VD level = High in option byte               | 3.8                | 4.0  | 4.25 <sup>1)</sup>  | v    |

| V <sub>IT-(LVD)</sub> | Reset generation threshold (V <sub>DD</sub> fall)            | VD level = Med. in option byte <sup>2)</sup> | 3.35 <sup>1)</sup> | 3.55 | 3.75 <sup>1))</sup> |      |

|                       |                                                              | VD level = Low in option byte <sup>2)</sup>  | 2.8 <sup>1)</sup>  | 3.0  | 3.15 <sup>1)</sup>  |      |

| V <sub>hys(LVD)</sub> | LVD voltage threshold hysteresis                             | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 200  |                     | mV   |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time <sup>3)2)</sup>                    | LVD enabled                                  | 6μs/V              |      | 100ms/V             |      |

| t <sub>g(VDD)</sub>   | $V_{DD}$ glitches filtered (not detected) by LVD $^{\rm 3)}$ |                                              |                    |      | 40                  | ns   |

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

#### Notes:

57/

1. Data based on characterization results, tested in production for ROM devices only.

2. If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

3. Data based on characterization results, not tested in production.

3. When Vt<sub>POR</sub> is faster than 100  $\mu$ s/V, the Reset signal is released after a delay of max. 42 $\mu$ s after V<sub>DD</sub> crosses the V<sub>IT+(LVD)</sub> threshold.

### 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                  | Parameter                                                 | Conditions                                   | Min                | Тур  | Max                | Unit |

|-------------------------|-----------------------------------------------------------|----------------------------------------------|--------------------|------|--------------------|------|

|                         | $1 \Rightarrow 0$ AVDF flag toggle threshold              | VD level = High in option byte               | 4.4 <sup>1)</sup>  | 4.6  | 4.9 <sup>1)</sup>  |      |

| V <sub>IT+(AVD)</sub>   | $(V_{DD} rise)$                                           | VD level = Med. in option byte               | 3.95 <sup>1)</sup> | 4.15 | 4.4 <sup>1)</sup>  |      |

|                         |                                                           | VD level = Low in option byte                | 3.4 <sup>1)</sup>  | 3.6  | 3.8 <sup>1)</sup>  | v    |

|                         | $0 \Rightarrow 1 \text{ AVDF}$ flag toggle threshold      | VD level = High in option byte               | 4.2 <sup>1)</sup>  | 4.4  | 4.65 <sup>1)</sup> | v    |

| V <sub>IT-(AVD)</sub>   | $(V_{DD} \text{ fall})$                                   | VD level = Med. in option byte               | 3.75 <sup>1)</sup> | 4.0  | 4.2 <sup>1)</sup>  |      |

|                         |                                                           | VD level = Low in option byte                | 3.2 <sup>1)</sup>  | 3.4  | 3.6 <sup>1)</sup>  |      |

| V <sub>hys(AVD)</sub>   | AVD voltage threshold hysteresis                          | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub> |                    | 200  |                    | mV   |

| $\Delta V_{\text{IT-}}$ | Voltage drop between AVD flag set and LVD reset activated | V <sub>IT-(AVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 450  |                    | mV   |

1. Data based on characterization results, tested in production for ROM devices only.

### 12.3.4 External Voltage Detector (EVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                                         | Conditions                                   | Min  | Тур  | Max  | Unit |

|-----------------------|-----------------------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>IT+(EVD)</sub> | 1 $\Rightarrow$ 0 AVDF flag toggle threshold $(V_{DD} rise)^{1)}$                 |                                              | 1.15 | 1.26 | 1.35 | V    |

| V <sub>IT-(EVD)</sub> | $0 \Rightarrow 1 \text{ AVDF}$ flag toggle threshold $(V_{DD} \text{ fall})^{1)}$ |                                              | 1.1  | 1.2  | 1.3  | v    |

| V <sub>hys(EVD)</sub> | EVD voltage threshold hysteresis                                                  | V <sub>IT+(EVD)</sub> -V <sub>IT-(EVD)</sub> |      | 200  |      | mV   |

1. Data based on characterization results, not tested in production.

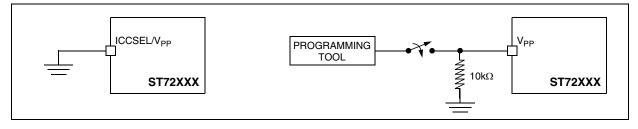

### CONTROL PIN CHARACTERISTICS (Cont'd) 12.9.2 ICCSEL/V<sub>PP</sub> Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol          | Parameter                              | Conditions                                       | Min                  | Max <sup>1</sup>    | Unit |

|-----------------|----------------------------------------|--------------------------------------------------|----------------------|---------------------|------|

| V               | Input low level voltage 1)             | FLASH versions                                   | V <sub>SS</sub>      | 0.2                 |      |

| V <sub>IL</sub> |                                        | ROM versions                                     | V <sub>SS</sub>      | 0.3xV <sub>DD</sub> | V    |

| V               | Input high level voltage <sup>1)</sup> | FLASH versions                                   | V <sub>DD</sub> -0.1 | 12.6                | v    |

| V <sub>IH</sub> |                                        | ROM versions 0.7xV <sub>DD</sub> V <sub>DD</sub> | V <sub>DD</sub>      |                     |      |

| ١L              | Input leakage current                  | V <sub>IN</sub> =V <sub>SS</sub>                 |                      | ±1                  | μA   |

### Figure 91. Two typical Applications with ICCSEL/V<sub>PP</sub> Pin<sup>2)</sup>

### Notes:

<u>ل</u>حک

1. Data based on design simulation and/or technology characteristics, not tested in production.

2. When ICC mode is not required by the application ICCSEL/V<sub>PP</sub> pin must be tied to  $V_{SS}$ .

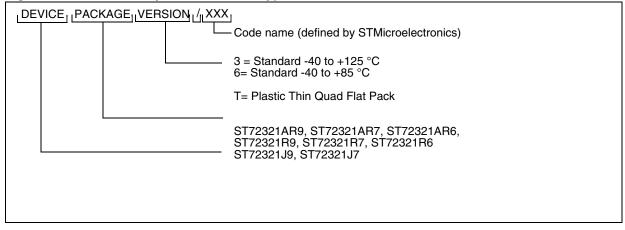

### ST723251 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

### Figure 106. ROM Factory Coded Device Types

57/

### ST72321 DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

ST72321 MICROCONTROLLER OPTION LIST (last update Mar 2009) Phone No: Reference/ROM Code\* :. . . . . . . . . . . . . . . . . . . . . . \*The ROM code name is assigned by STMicroelectronics. ROM code must be sent in .S19 format. .Hex extension cannot be processed. Device Type/Memory Size/Package (check only one option): -----|------ROM DEVICE: 48K | 32K 60K I

LQFP44 10x10:

|[] ST72321J9

|[] ST72321J7

|[] see Note 1

|

LQFP64 14x14:

|[] ST72321R9

|[] ST72321R7

|[] ST72321R6

|

LQFP64 10x10:

|[] ST72321AR9

|[] ST72321AR7

|[] ST72321AR6

|

DIE FORM: | 60K | 48K | 32K | 64-pin: | [] | Conditioning (check only one option) Packaged Product | Die Product (dice tested at 25°C only) | ------[ ] Tape & Reel [ ] Tray | [ ] Tape & Reel |[ ] Inked wafer |[ ] Sawn wafer on sticky foil Version/Temp. Range (do not check for die product):Please refer to datasheet for specific sales conditions : Standard [] -40 to +85°C [ ] -40 to +125°C Special Marking: [ ] No [ ] Yes "\_\_\_\_\_" (10 char. Authorized characters are letters, digits, '.', '-', '/' and spaces only. " (10 char. max) Clock Source Selection: [ ] Resonator: [] LP: Low power resonator (1 to 2 MHz) [ ] MP: Medium power resonator (2 to 4 MHz) [ ] MS: Medium speed resonator (4 to 8 MHz) [ ] HS: High speed resonator (8 to 16 MHz) [ ] Internal RC (4) [ ] External Clock

PLL (3)

[] Disabled

[] Enabled

CSS (5)

[] Disabled

[] Enabled

LVD Reset [] Disabled

[] High threshold

[] Med.threshold

[ ] Low threshold [ ] 256 Cycles [ ] 4096 Cycles Reset Delay Watchdog Selection: [] Softwar Watchdog reset on Halt [] Reset [] Disable [] Software Activation [] Hardware Activation [] Reset [] No reset [ ] Enabled Readout Protection(2): [ ] Disabled Date Signature Note 1 : Configure 44-pin/32K devices using separate ST72321B option list. Note 2 : Readout protection is not supported if LVD is enabled. Note 3 : PLL must not be enabled if internal RC Network or External Clock is selected. Note 4 : Internal RC can only be used if LVD is enabled. Note 5 : Device operation below 3.8V not guaranteed

### Table 31. ST7 Application Notes

| IDENTIFICATION | DESCRIPTION                                                                 |  |  |  |  |

|----------------|-----------------------------------------------------------------------------|--|--|--|--|

| AN1947         | ST7MC PMAC SINE WAVE MOTOR CONTROL SOFTWARE LIBRARY                         |  |  |  |  |

| -              | GENERAL PURPOSE                                                             |  |  |  |  |

| AN1476         | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                   |  |  |  |  |

| AN1526         | ST7FLITE0 QUICK REFERENCE NOTE                                              |  |  |  |  |

| AN1709         | EMC DESIGN FOR ST MICROCONTROLLERS                                          |  |  |  |  |

| AN1752         | ST72324 QUICK REFERENCE NOTE                                                |  |  |  |  |

| PRODUCT EVALU  | ATION                                                                       |  |  |  |  |

| AN 910         | PERFORMANCE BENCHMARKING                                                    |  |  |  |  |

| AN 990         | ST7 BENEFITS VS INDUSTRY STANDARD                                           |  |  |  |  |

| AN1077         | OVERVIEW OF ENHANCED CAN CONTROLLERS FOR ST7 AND ST9 MCUS                   |  |  |  |  |

| AN1086         | U435 CAN-DO SOLUTIONS FOR CAR MULTIPLEXING                                  |  |  |  |  |

| AN1103         | IMPROVED B-EMF DETECTION FOR LOW SPEED, LOW VOLTAGE WITH ST72141            |  |  |  |  |

| AN1150         | BENCHMARK ST72 VS PC16                                                      |  |  |  |  |

| AN1151         | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                           |  |  |  |  |

| AN1278         | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                  |  |  |  |  |

| PRODUCT MIGRA  | TION                                                                        |  |  |  |  |

| AN1131         | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324          |  |  |  |  |

| AN1322         | MIGRATING AN APPLICATION FROM ST7263 REV.B TO ST7263B                       |  |  |  |  |

| AN1365         | GUIDELINES FOR MIGRATING ST72C254 APPLICATIONS TO ST72F264                  |  |  |  |  |

| AN1604         | HOW TO USE ST7MDT1-TRAIN WITH ST72F264                                      |  |  |  |  |

| AN2200         | GUIDELINES FOR MIGRATING ST7LITE1X APPLICATIONS TO ST7FLITE1XB              |  |  |  |  |

| PRODUCT OPTIM  | ZATION                                                                      |  |  |  |  |

| AN 982         | USING ST7 WITH CERAMIC RESONATOR                                            |  |  |  |  |

| AN1014         | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                   |  |  |  |  |

| AN1015         | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE           |  |  |  |  |

| AN1040         | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                     |  |  |  |  |

| AN1070         | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                       |  |  |  |  |

| AN1181         | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                               |  |  |  |  |

| AN1324         | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS          |  |  |  |  |

| AN1502         | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                |  |  |  |  |

| AN1529         | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY        |  |  |  |  |

| AN1530         | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLATOR |  |  |  |  |

| AN1605         | USING AN ACTIVE RC TO WAKEUP THE ST7LITE0 FROM POWER SAVING MODE            |  |  |  |  |

| AN1636         | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                          |  |  |  |  |

| AN1828         | PIR (PASSIVE INFRARED) DETECTOR USING THE ST7FLITE05/09/SUPERLITE           |  |  |  |  |

| AN1946         | SENSORLESS BLDC MOTOR CONTROL AND BEMF SAMPLING METHODS WITH ST7MC          |  |  |  |  |

| AN1953         | PFC FOR ST7MC STARTER KIT                                                   |  |  |  |  |

| AN1971         | ST7LITE0 MICROCONTROLLED BALLAST                                            |  |  |  |  |

| PROGRAMMING A  |                                                                             |  |  |  |  |

| AN 978         | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                          |  |  |  |  |

| AN 983         | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                           |  |  |  |  |

| AN 985         | EXECUTING CODE IN ST7 RAM                                                   |  |  |  |  |

| AN 986         | USING THE INDIRECT ADDRESSING MODE WITH ST7                                 |  |  |  |  |

| AN 987         | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                      |  |  |  |  |

| AN 988         | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                       |  |  |  |  |

| AN1039         | ST7 MATH UTILITY ROUTINES                                                   |  |  |  |  |

|                |                                                                             |  |  |  |  |

To identify these parts, check the internal sales type on the box label or the trace code marking on the package.

| Rev         | Internal Salestype | Trace Code |

|-------------|--------------------|------------|

| Rev Q       | 72F321xxx\$A2      | 813xxxQ    |

|             | 72F321xxx\$U2      | 813xxxQ    |

| Rev S       | 72F321xxx\$A8      | 813xxxS    |

| nev 3       | 72F321xxx\$U8      | 813xxxS    |

| Rev 9 (full | 72F321xxx\$A3      | 813xxx9    |

| spec)       | 72F321xxx\$U3      | 813xxx9    |

<u>ل</u>رک

## 15.4 LIMITATIONS SPECIFIC TO ROM DEVICES

### 15.4.1 LVD Operation

Depending on the operating conditions, especially the  $V_{DD}$  ramp up speed and ambient temperature, in some cases the LVD may not start. When this occurs, the MCU may operate outside the guaranteed functional area (see datasheet Figure 76) without being forced into reset state.

In this case, proper use of the watchdog may make it possible to recover through a watchdog reset and allow normal operations to resume.

Consequently, the LVD function is not guaranteed in the current silicon revision. For complete security, an external reset circuit must be added.

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com