#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                    |

|---------------------------------|---------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 180MHz                                                                    |

| Co-Processors/DSP               | -                                                                         |

| RAM Controllers                 | SDRAM, SRAM                                                               |

| Graphics Acceleration           | No                                                                        |

| Display & Interface Controllers | -                                                                         |

| Ethernet                        | 10/100Mbps                                                                |

| SATA                            | -                                                                         |

| USB                             | USB 2.0 (2)                                                               |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                          |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                         |

| Security Features               | -                                                                         |

| Package / Case                  | 217-LFBGA                                                                 |

| Supplier Device Package         | 217-LFBGA (15x15)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9260b-cu |

|                                 |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

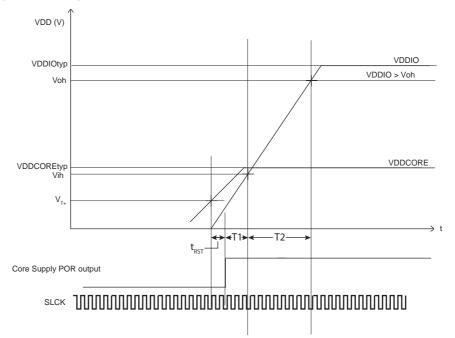

#### 4.2.1 Power-up Sequence

#### Figure 4-1. V<sub>DDCORE</sub> and V<sub>VDDIO</sub> Constraints at Startup

VDDCORE and VDDBU are controlled by internal POR (Power On Reset) to guarantee that these power sources reach their target values prior to the release of POR.

#### 4.2.1.1 VDDBU is Continuously Powered (used with a battery)

- VDDIOM, VDDIOP0 and VDDIOP1 must NOT be powered until VDDCORE has reached a level superior to  $V_{T+}$ .

- VDDIOP0 must be  $\ge$  V<sub>IH</sub> (refer to Table 39-2 "DC Characteristics" for more details) within (t<sub>RST</sub> + T1) after VDDCORE reached V<sub>T+</sub>.

- VDDIOM must reach  $V_{OH}$  (refer to Table 39-2 "DC Characteristics" for more details) within ( $t_{RST}$  + T1 + T2) after VDDCORE has reached  $V_{T+}$ .

- t<sub>RST</sub> is a POR characteristic

- T1 = 3  $\times$  t<sub>SLCK</sub>

- T2 =  $16 \times t_{SLCK}$

The t<sub>SLCK</sub> min (22 µs) is obtained for the maximum frequency of the internal RC oscillator (44 kHz).

- t<sub>RST</sub> = 100 μs

- T1 = 66 μs

- T2 = 352 μs

#### 4.2.1.2 VDDBU is not Continuously Powered (no backup features used)

If VDDBU is not used with a battery, the power sequence can be less constrained. The user can power VDDCORE, then VDDIOM, VDDIOP0 and VDDIOP1, with VDDBU following last in the sequence, thus ensuring that BMS is correctly sampled.

#### 4.2.2 Power-down Sequence

Switch-off the VDDIOM, VDDIOP0 and VDDIOP1 power supply prior to or at the same time as VDDCORE.

No power-up or power-down restrictions apply to VDDBU, VDDPLL and VDDANA.

mapped to the modified virtual address. With the MVA use disabled, context switching incurs ICache cleaning and/or invalidating.

When the ICache is disabled, all instruction fetches appear on external memory (AHB) (see Tables 4-1 and 4-2 in page 4-4 in ARM926EJ-S TRM, ref. DDI0198B).

On reset, the ICache entries are invalidated and the ICache is disabled. For best performance, ICache should be enabled as soon as possible after reset.

#### 9.7.2 Data Cache (DCache) and Write Buffer

ARM926EJ-S includes a DCache and a write buffer to reduce the effect of main memory bandwidth and latency on data access performance. The operations of DCache and write buffer are closely connected.

#### 9.7.2.1 DCache

The DCache needs the MMU to be enabled. All data accesses are subject to MMU permission and translation checks. Data accesses that are aborted by the MMU do not cause linefills or data accesses to appear on the AMBA AHB interface. If the MMU is disabled, all data accesses are noncachable, nonbufferable, with no protection checks, and appear on the AHB bus. All addresses are flat-mapped, VA = MVA = PA, which incurs DCache cleaning and/or invalidating every time a context switch occurs.

The DCache stores the Physical Address Tag (PA Tag) from which every line was loaded and uses it when writing modified lines back to external memory. This means that the MMU is not involved in write-back operations.

Each line (8 words) in the DCache has two dirty bits, one for the first four words and the other one for the second four words. These bits, if set, mark the associated half-lines as dirty. If the cache line is replaced due to a linefill or a cache clean operation, the dirty bits are used to decide whether all, half or none is written back to memory.

DCache can be enabled or disabled by writing either 1 or 0 to bit C in register 1 of CP15 (see Tables 4-3 and 4-4 on page 4-5 in ARM926EJ-S TRM, ref. DDI0222B).

The DCache supports write-through and write-back cache operations, selected by memory region using the C and B bits in the MMU translation tables.

The DCache contains an eight data word entry, single address entry write-back buffer used to hold write-back data for cache line eviction or cleaning of dirty cache lines.

The Write Buffer can hold up to 16 words of data and four separate addresses. DCache and Write Buffer operations are closely connected as their configuration is set in each section by the page descriptor in the MMU translation table.

#### 9.7.2.2 Write Buffer

The ARM926EJ-S contains a write buffer that has a 16-word data buffer and a four- address buffer. The write buffer is used for all writes to a bufferable region, write-through region and write-back region. It also allows to avoid stalling the processor when writes to external memory are performed. When a store occurs, data is written to the write buffer at core speed (high speed). The write buffer then completes the store to external memory at bus speed (typically slower than the core speed). During this time, the ARM9EJ-S processor can preform other tasks.

DCache and Write Buffer support write-back and write-through memory regions, controlled by C and B bits in each section and page descriptor within the MMU translation tables.

#### Write-though Operation

When a cache write hit occurs, the DCache line is updated. The updated data is then written to the write buffer which transfers it to external memory.

When a cache write miss occurs, a line, chosen by round robin or another algorithm, is stored in the write buffer which transfers it to external memory.

# 18.4 Application Example

#### 18.4.1 Hardware Interface

Table 18-3 details the connections to be applied between the EBI pins and the external devices for each memory controller.

|               | Pins of the SMC Interfaced Device |                                |                         |                                |                                 |                         |  |  |  |

|---------------|-----------------------------------|--------------------------------|-------------------------|--------------------------------|---------------------------------|-------------------------|--|--|--|

| Signals: EBI_ | 8-bit Static<br>Device            | 2 x 8-bit<br>Static<br>Devices | 16-bit Static<br>Device | 4 x 8-bit<br>Static<br>Devices | 2 x 16-bit<br>Static<br>Devices | 32-bit Static<br>Device |  |  |  |

| D0–D7         | D0D7                              | D0–D7                          | D0–D7                   | D0–D7                          | D0D7                            | D0–D7                   |  |  |  |

| D8–D15        | _                                 | D8–D15                         | D8–D15                  | D8–D15                         | D8–15                           | D8–15                   |  |  |  |

| D16–D23       | _                                 | _                              | -                       | D16–D23                        | D16–D23                         | D16–D23                 |  |  |  |

| D24–D31       | _                                 | _                              | -                       | D24–D31                        | D24–D31                         | D24–D31                 |  |  |  |

| A0/NBS0       | A0                                | _                              | NLB                     | _                              | NLB <sup>(3)</sup>              | BE0 <sup>(5)</sup>      |  |  |  |

| A1/NWR2/NBS2  | A1                                | A0                             | A0                      | WE <sup>(2)</sup>              | NLB <sup>(4)</sup>              | BE2 <sup>(5)</sup>      |  |  |  |

| A2-A25        | A[2:25]                           | A[1:24]                        | A[1:24]                 | A[0:23]                        | A[0:23]                         | A[0:23]                 |  |  |  |

| NCS0          | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NCS1/SDCS     | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NCS2          | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NCS3/NANDCS   | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NCS4/CFCS0    | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NCS5/CFCS1    | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NCS6          | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NCS7          | CS                                | CS                             | CS                      | CS                             | CS                              | CS                      |  |  |  |

| NRD/CFOE      | OE                                | OE                             | OE                      | OE                             | OE                              | OE                      |  |  |  |

| NWR0/NWE      | WE                                | WE <sup>(1)</sup>              | WE                      | WE <sup>(2)</sup>              | WE                              | WE                      |  |  |  |

| NWR1/NBS1     | _                                 | WE <sup>(1)</sup>              | NUB                     | WE <sup>(2)</sup>              | NUB <sup>(3)</sup>              | BE1 <sup>(5)</sup>      |  |  |  |

| NWR3/NBS3     | _                                 | _                              | _                       | WE <sup>(2)</sup>              | NUB (4)                         | BE3 (5)                 |  |  |  |

Notes: 1. NWR1 enables upper byte writes. NWR0 enables lower byte writes.

2. NWRx enables corresponding byte x writes. (x = 0, 1, 2 or 3)

3. NBS0 and NBS1 enable respectively lower and upper bytes of the lower 16-bit word.

4. NBS2 and NBS3 enable respectively lower and upper bytes of the upper 16-bit word.

5. BEx: Byte x Enable (x = 0, 1, 2 or 3)

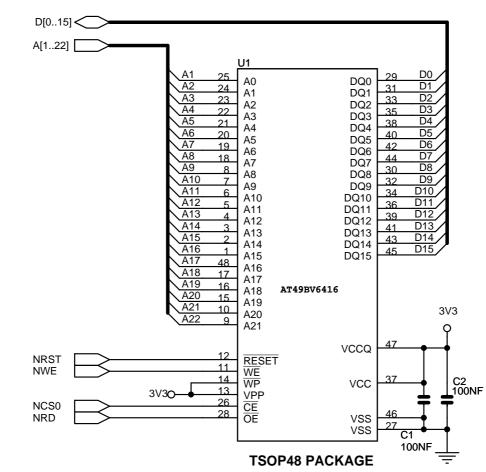

#### 18.7.5 NOR Flash on NCS0

18.7.5.1 Hardware Configuration - NOR Flash on NCS0

#### 18.7.5.2 Software Configuration - NOR Flash on NCS0

The default configuration for the Static Memory Controller, byte select mode, 16-bit data bus, Read/Write controlled by Chip Select, allows boot on 16-bit non-volatile memory at slow clock.

For another configuration, configure the Static Memory Controller CS0 Setup, Pulse, Cycle and Mode depending on Flash timings and system bus frequency.

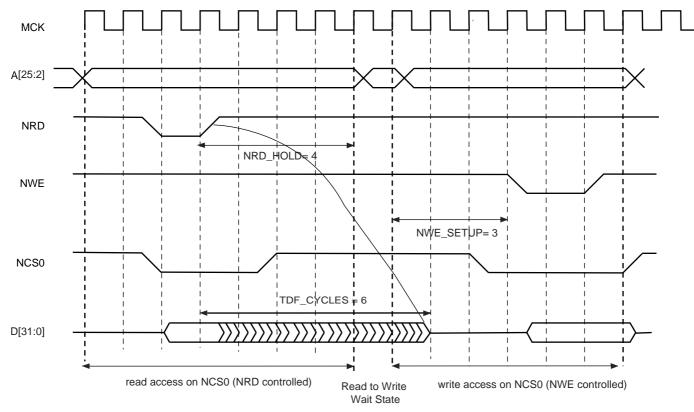

#### 19.10.2 TDF Optimization Enabled (TDF\_MODE = 1)

When the TDF\_MODE of the SMC\_MODE register is set to 1 (TDF optimization is enabled), the SMC takes advantage of the setup period of the next access to optimize the number of wait states cycle to insert.

Figure 19-22 shows a read access controlled by NRD, followed by a write access controlled by NWE, on Chip Select 0 has been programmed with:

NRD\_HOLD = 4; READ\_MODE = 1 (NRD controlled)

NWE\_SETUP = 3; WRITE\_MODE = 1 (NWE controlled)

TDF\_CYCLES = 6; TDF\_MODE = 1 (optimization enabled).

#### Figure 19-22. TDF Optimization: No TDF wait states are inserted if the TDF period is over when the next access begins

#### 19.10.3 TDF Optimization Disabled (TDF\_MODE = 0)

When optimization is disabled, tdf wait states are inserted at the end of the read transfer, so that the data float period is ended when the second access begins. If the hold period of the read1 controlling signal overlaps the data float period, no additional tdf wait states will be inserted.

Figure 19-23, Figure 19-24 and Figure 19-25 illustrate the cases:

- read access followed by a read access on another chip select,

- read access followed by a write access on another chip select,

- read access followed by a write access on the same chip select,

with no TDF optimization.

## 20.6.6 SDRAMC Interrupt Disable Register

| Name:<br>Access: | SDRAMC_IDR<br>Write-only |    |    |    |    |    |     |

|------------------|--------------------------|----|----|----|----|----|-----|

| 31               | 30                       | 29 | 28 | 27 | 26 | 25 | 24  |

| -                | -                        | _  | -  | —  | —  | _  | —   |

| 23               | 22                       | 21 | 20 | 19 | 18 | 17 | 16  |

| —                | -                        | _  | _  | _  | -  | _  | -   |

| 15               | 14                       | 13 | 12 | 11 | 10 | 9  | 8   |

| —                | -                        | _  | -  | —  | —  | _  | —   |

| 7                | 6                        | 5  | 4  | 3  | 2  | 1  | 0   |

| -                | -                        | -  | -  | -  | -  | -  | RES |

## • RES: Refresh Error Status

0: No effect.

1: Disables the refresh error interrupt.

## 24.9.2 PMC System Clock Disable Register

| -       |            |    |    |    |

|---------|------------|----|----|----|

| Name:   | PMC_SCDR   |    |    |    |

| Access: | Write-only |    |    |    |

| 31      | 30         | 29 | 28 | 27 |

| -       | -          | -  | -  | I  |

| 23      | 22         | 21 | 20 | 19 |

| -       | -          | -  | _  | 1  |

| 15      | 14         | 13 | 12 | 11 |

| -       | -          | -  | -  | ١  |

| 7       | 6          | 5  | 4  | 3  |

|         |            |    |    |    |

#### • PCK: Processor Clock Disable

UHP

0: No effect.

UDP

1: Disables the Processor clock. This is used to enter the processor in Idle Mode.

26

\_

18

\_

10

\_

2

\_

\_

25

\_

17

\_

9

PCK1

1

\_

24

\_

16

\_

8

PCK0

0

PCK

#### • UHP: USB Host Port Clock Disable

0: No effect.

1: Disables the 12 and 48 MHz clock of the USB Host Port.

#### • UDP: USB Device Port Clock Disable

0: No effect.

1: Disables the 48 MHz clock of the USB Device Port.

#### • PCKx: Programmable Clock x Output Disable

0: No effect.

1: Disables the corresponding Programmable Clock output.

## 25.9.9 AIC Interrupt Mask Register

| Name:   | AIC_IMR   |

|---------|-----------|

| Access: | Read-only |

| 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PID31 | PID30 | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| PID23 | PID22 | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| PID15 | PID14 | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| PID7  | PID6  | PID5  | PID4  | PID3  | PID2  | SYS   | FIQ   |

#### • FIQ, SYS, PID2–PID31: Interrupt Mask

0: Corresponding interrupt is disabled.

1: Corresponding interrupt is enabled.

# 27.5 I/O Lines Programming Example

The programing example as shown in Table 27-1 below is used to define the following configuration.

- 4-bit output port on I/O lines 0 to 3, (should be written in a single write operation), open-drain, with pull-up resistor

- Four output signals on I/O lines 4 to 7 (to drive LEDs for example), driven high and low, no pull-up resistor

- Four input signals on I/O lines 8 to 11 (to read push-button states for example), with pull-up resistors, glitch filters and input change interrupts

- Four input signals on I/O line 12 to 15 to read an external device status (polled, thus no input change interrupt), no pull-up resistor, no glitch filter

- I/O lines 16 to 19 assigned to peripheral A functions with pull-up resistor

- I/O lines 20 to 23 assigned to peripheral B functions, no pull-up resistor

- I/O line 24 to 27 assigned to peripheral A with Input Change Interrupt and pull-up resistor

| Table 27-1. Programming Examp |

|-------------------------------|

|-------------------------------|

| Register | Value to be Written |

|----------|---------------------|

| PIO_PER  | 0x0000 FFFF         |

| PIO_PDR  | 0x0FFF 0000         |

| PIO_OER  | 0x0000 00FF         |

| PIO_ODR  | 0x0FFF FF00         |

| PIO_IFER | 0x0000 0F00         |

| PIO_IFDR | 0x0FFF F0FF         |

| PIO_SODR | 0x0000 0000         |

| PIO_CODR | 0x0FFF FFFF         |

| PIO_IER  | 0x0F00 0F00         |

| PIO_IDR  | 0x00FF F0FF         |

| PIO_MDER | 0x0000 000F         |

| PIO_MDDR | 0x0FFF FFF0         |

| PIO_PUDR | 0x00F0 00F0         |

| PIO_PUER | 0x0F0F FF0F         |

| PIO_ASR  | 0x0F0F 0000         |

| PIO_BSR  | 0x00F0 0000         |

| PIO_OWER | 0x0000 000F         |

| PIO_OWDR | 0x0FFF FFF0         |

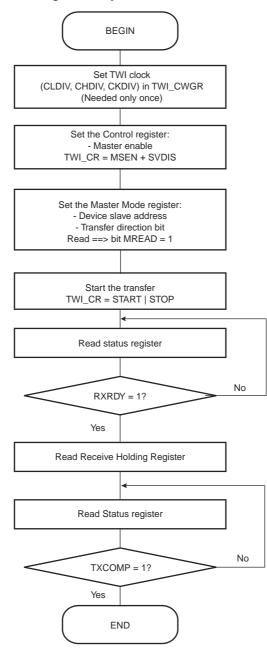

Figure 29-17. TWI Read Operation with Single Data Byte without Internal Address

#### 29.8.1 TWI Control Register

| Name:   | TWI_CR     |       |      |       |      |      |       |

|---------|------------|-------|------|-------|------|------|-------|

| Access: | Write-only |       |      |       |      |      |       |

| 31      | 30         | 29    | 28   | 27    | 26   | 25   | 24    |

| _       | -          | -     | -    | -     | -    | -    | -     |

| 23      | 22         | 21    | 20   | 19    | 18   | 17   | 16    |

| _       | _          | _     | -    | _     | -    | _    | -     |

| 15      | 14         | 13    | 12   | 11    | 10   | 9    | 8     |

| _       | -          | _     | _    | _     | -    | _    | -     |

| 7       | 6          | 5     | 4    | 3     | 2    | 1    | 0     |

| SWRST   | -          | SVDIS | SVEN | MSDIS | MSEN | STOP | START |

#### • START: Send a START Condition

0: No effect.

1: A frame beginning with a START bit is transmitted according to the features defined in the mode register.

This action is necessary when the TWI peripheral wants to read data from a slave. When configured in Master Mode with a write operation, a frame is sent as soon as the user writes a character in the Transmit Holding Register (TWI\_THR).

#### • STOP: Send a STOP Condition

0: No effect.

1: STOP Condition is sent just after completing the current byte transmission in master read mode.

- In single data byte master read, the START and STOP must both be set.

- In multiple data bytes master read, the STOP must be set after the last data received but one.

- In master read mode, if a NACK bit is received, the STOP is automatically performed.

- In multiple data write operation, when both THR and shift register are empty, a STOP condition is automatically sent.

#### • MSEN: TWI Master Mode Enabled

0: No effect.

1: If MSDIS = 0, the master mode is enabled.

Note: Switching from Slave to Master mode is only permitted when TXCOMP = 1.

#### MSDIS: TWI Master Mode Disabled

0: No effect.

1: The master mode is disabled, all pending data is transmitted. The shifter and holding characters (if it contains data) are transmitted in case of write operation. In read operation, the character being transferred must be completely received before disabling.

#### • SVEN: TWI Slave Mode Enabled

0: No effect.

1: If SVDIS = 0, the slave mode is enabled.

Note: Switching from Master to Slave mode is only permitted when TXCOMP = 1.

# 30. Universal Synchronous Asynchronous Receiver Transmitter (USART)

## 30.1 Description

The Universal Synchronous Asynchronous Receiver Transmitter (USART) provides one full duplex universal synchronous asynchronous serial link. Data frame format is widely programmable (data length, parity, number of stop bits) to support a maximum of standards. The receiver implements parity error, framing error and overrun error detection. The receiver time-out enables handling variable-length frames and the transmitter timeguard facilitates communications with slow remote devices. Multidrop communications are also supported through address bit handling in reception and transmission.

The USART features three test modes: remote loopback, local loopback and automatic echo.

The USART supports specific operating modes providing interfaces on RS485 buses, with ISO7816 T = 0 or T = 1 smart card slots, infrared transceivers and connection to modem ports. The hardware handshaking feature enables an out-of-band flow control by automatic management of the pins RTS and CTS.

The USART supports the connection to the Peripheral DMA Controller, which enables data transfers to the transmitter and from the receiver. The PDC provides chained buffer management without any intervention of the processor.

## 30.2 Embedded Characteristics

- Programmable Baud Rate Generator

- 5- to 9-bit full-duplex synchronous or asynchronous serial communications

- 1, 1.5 or 2 stop bits in Asynchronous Mode or 1 or 2 stop bits in Synchronous Mode

- Parity generation and error detection

- Framing error detection, overrun error detection

- MSB- or LSB-first

- Optional break generation and detection

- By 8 or by-16 over-sampling receiver frequency

- Hardware handshaking RTS-CTS

- Optional modem signal management DTR-DSR-DCD-RI

- Receiver time-out and transmitter timeguard

- Optional Multi-drop Mode with address generation and detection

- RS485 with driver control signal

- ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- IrDA modulation and demodulation

- Communication at up to 115.2 Kbps

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

The USART contains features allowing management of the Modern Signals DTR, DSR, DCD and RI. In the SAM9260, only the USART0 implements these signals, named DTR0, DSR0, DCD0 and RI0.

The USART1 and USART2 do not implement all the modem signals. Only RTS and CTS (RTS1 and CTS1, RTS2 and CTS2, respectively) are implemented in these USARTs for other features.

Thus, programming the USART1, USART2 or the USART3 in Modem Mode may lead to unpredictable results. In these USARTs, the commands relating to the Modem Mode have no effect and the status bits relating the status of the modem signals are never activated.

| 31.9.9 SS | C Receive Synchro | onization Hold | ling Register |     |    |    |    |

|-----------|-------------------|----------------|---------------|-----|----|----|----|

| Name:     | SSC_RSHR          |                |               |     |    |    |    |

| Access:   | Read-only         |                |               |     |    |    |    |

| 31        | 30                | 29             | 28            | 27  | 26 | 25 | 24 |

| _         | -                 | _              | -             | -   | -  | _  | -  |

| 23        | 22                | 21             | 20            | 19  | 18 | 17 | 16 |

| —         | -                 | -              | —             | -   | -  | _  | _  |

| 15        | 14                | 13             | 12            | 11  | 10 | 9  | 8  |

|           |                   |                | RS            | DAT |    |    |    |

| 7         | 6                 | 5              | 4             | 3   | 2  | 1  | 0  |

|           |                   |                | RS            | DAT |    |    |    |

• RSDAT: Receive Synchronization Data

## 32.7.4 TC Channel Mode Register: Capture Mode

| Name:   | $TC_CMRx [x = 02] (WAVE = 0)$ |

|---------|-------------------------------|

| Access: | Read/Write                    |

| 31     | 30      | 29 | 28  | 27   | 26     | 25     | 24   |

|--------|---------|----|-----|------|--------|--------|------|

| _      | -       | -  | -   | -    | -      | -      | -    |

| 23     | 22      | 21 | 20  | 19   | 18     | 17     | 16   |

| -      | —       | -  | _   | LD   | RB     | LC     | DRA  |

| 15     | 14      | 13 | 12  | 11   | 10     | 9      | 8    |

| WAVE   | CPCTRG  | _  | -   | _    | ABETRG | ETR    | GEDG |

| 7      | 6       | 5  | 4   | 3    | 2      | 1      | 0    |

| LDBDIS | LDBSTOP | BU | RST | CLKI |        | TCCLKS |      |

#### • TCCLKS: Clock Selection

| ١ | /alue | е | Clock Selected |

|---|-------|---|----------------|

| 0 | 0     | 0 | TIMER_CLOCK1   |

| 0 | 0     | 1 | TIMER_CLOCK2   |

| 0 | 1     | 0 | TIMER_CLOCK3   |

| 0 | 1     | 1 | TIMER_CLOCK4   |

| 1 | 0     | 0 | TIMER_CLOCK5   |

| 1 | 0     | 1 | XC0            |

| 1 | 1     | 0 | XC1            |

| 1 | 1     | 1 | XC2            |

#### • CLKI: Clock Invert

0: Counter is incremented on rising edge of the clock.

1: Counter is incremented on falling edge of the clock.

#### • BURST: Burst Signal Selection

| Value |   |                                               |

|-------|---|-----------------------------------------------|

| 0     | 0 | The clock is not gated by an external signal. |

| 0     | 1 | XC0 is ANDed with the selected clock.         |

| 1     | 0 | XC1 is ANDed with the selected clock.         |

| 1     | 1 | XC2 is ANDed with the selected clock.         |

## • LDBSTOP: Counter Clock Stopped with RB Loading

0: Counter clock is not stopped when RB loading occurs.

1: Counter clock is stopped when RB loading occurs.

#### LDBDIS: Counter Clock Disable with RB Loading

0: Counter clock is not disabled when RB loading occurs.

1: Counter clock is disabled when RB loading occurs.

#### 34.6.9 Interrupt Enable Register

| Name:   | EMAC_IER   |     |      |       |       |       |     |

|---------|------------|-----|------|-------|-------|-------|-----|

| Access: | Write-only |     |      |       |       |       |     |

| 31      | 30         | 29  | 28   | 27    | 26    | 25    | 24  |

| _       | -          | -   | -    | -     | -     | -     | -   |

| 23      | 22         | 21  | 20   | 19    | 18    | 17    | 16  |

| -       | -          | _   | _    | _     | _     | _     | _   |

| 15      | 14         | 13  | 12   | 11    | 10    | 9     | 8   |

| -       | -          | PTZ | PFR  | HRESP | ROVR  | -     | -   |

| 7       | 6          | 5   | 4    | 3     | 2     | 1     | 0   |

| TCOMP   | TXERR      | RLE | TUND | TXUBR | RXUBR | RCOMP | MFD |

#### • MFD: Management Frame sent

Enable management done interrupt.

#### • RCOMP: Receive Complete

Enable receive complete interrupt.

#### • RXUBR: Receive Used Bit Read

Enable receive used bit read interrupt.

#### • TXUBR: Transmit Used Bit Read

Enable transmit used bit read interrupt.

#### • TUND: Ethernet Transmit Buffer Underrun

Enable transmit underrun interrupt.

#### RLE: Retry Limit Exceeded

Enable retry limit exceeded interrupt.

#### TXERR

Enable transmit buffers exhausted in mid-frame interrupt.

#### • TCOMP: Transmit Complete

Enable transmit complete interrupt.

#### • ROVR: Receive Overrun

Enable receive overrun interrupt.

#### • HRESP: Hresp not OK

Enable Hresp not OK interrupt.

#### • PFR: Pause Frame Received

Enable pause frame received interrupt.

#### 34.6.11 Interrupt Mask Register

| Name:   | EMAC_IMR  |     |      |       |       |       |     |

|---------|-----------|-----|------|-------|-------|-------|-----|

| Access: | Read-only |     |      |       |       |       |     |

| 31      | 30        | 29  | 28   | 27    | 26    | 25    | 24  |

| -       | -         | _   | —    | _     | -     | -     | -   |

| 23      | 22        | 21  | 20   | 19    | 18    | 17    | 16  |

| _       | -         | _   | _    | _     | _     | _     | _   |

| 15      | 14        | 13  | 12   | 11    | 10    | 9     | 8   |

| _       | -         | PTZ | PFR  | HRESP | ROVR  | -     | -   |

| 7       | 6         | 5   | 4    | 3     | 2     | 1     | 0   |

| TCOMP   | TXERR     | RLE | TUND | TXUBR | RXUBR | RCOMP | MFD |

#### • MFD: Management Frame sent

Management done interrupt masked.

#### RCOMP: Receive Complete

Receive complete interrupt masked.

#### • RXUBR: Receive Used Bit Read

Receive used bit read interrupt masked.

#### • TXUBR: Transmit Used Bit Read

Transmit used bit read interrupt masked.

#### • TUND: Ethernet Transmit Buffer Underrun

Transmit underrun interrupt masked.

#### RLE: Retry Limit Exceeded

Retry limit exceeded interrupt masked.

#### TXERR

Transmit buffers exhausted in mid-frame interrupt masked.

#### • TCOMP: Transmit Complete

Transmit complete interrupt masked.

#### • ROVR: Receive Overrun

Receive overrun interrupt masked.

#### HRESP: Hresp not OK

Hresp not OK interrupt masked.

#### • PFR: Pause Frame Received

Pause frame received interrupt masked.

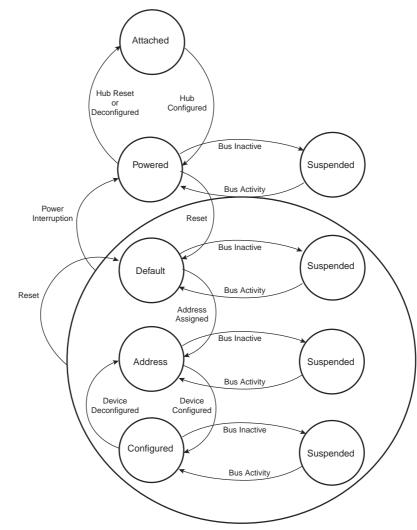

#### 35.6.3 Controlling Device States

A USB device has several possible states. Refer to Chapter 9 of the Universal Serial Bus Specification, Rev 2.0.

Figure 35-14. USB Device State Diagram

Movement from one state to another depends on the USB bus state or on standard requests sent through control transactions via the default endpoint (endpoint 0).

After a period of bus inactivity, the USB device enters Suspend Mode. Accepting Suspend/Resume requests from the USB host is mandatory. Constraints in Suspend Mode are very strict for bus-powered applications; devices may not consume more than 500 µA on the USB bus.

While in Suspend Mode, the host may wake up a device by sending a resume signal (bus activity) or a USB device may send a wake up request to the host, e.g., waking up a PC by moving a USB mouse.

The wake up feature is not mandatory for all devices and must be negotiated with the host.

#### 35.6.3.1 Not Powered State

Self powered devices can detect 5V VBUS using a PIO as described in the typical connection section. When the device is not connected to a host, device power consumption can be reduced by disabling MCK for the UDP, disabling UDPCK and disabling the transceiver. DDP and DDM lines are pulled down by 330 K $\Omega$  resistors.

| Mode      | Byte   | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

|-----------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

|           | Byte 0 | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   | R5(i)   | R6(i)   | R7(i)   |

| RGB 8:8:8 | Byte 1 | G0(i)   | G1(i)   | G2(i)   | G3(i)   | G4(i)   | G5(i)   | G6(i)   | G7(i)   |

| KGD 0.0.0 | Byte 2 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | B5(i)   | B6(i)   | B7(i)   |

|           | Byte 3 | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) | R5(i+1) | R6(i+1) | R7(i+1) |

|           | Byte 0 | G3(i)   | G4(i)   | G5(i)   | R0(i)   | R1(i)   | R2(i)   | R3(i)   | R4(i)   |

|           | Byte 1 | B0(i)   | B1(i)   | B2(i)   | B3(i)   | B4(i)   | G0(i)   | G1(i)   | G2(i)   |

| RGB 5:6:5 | Byte 2 | G3(i+1) | G4(i+1) | G5(i+1) | R0(i+1) | R1(i+1) | R2(i+1) | R3(i+1) | R4(i+1) |

|           | Byte 3 | B0(i+1) | B1(i+1) | B2(i+1) | B3(i+1) | B4(i+1) | G0(i+1) | G1(i+1) | G2(i+1) |

#### Table 37-5. RGB Format in Default Mode, RGB\_CFG = 00, Swap Activated

The RGB 5:6:5 input format is processed to be displayed as RGB 5:5:5 format, compliant with the 16-bit mode of the LCD controller.

#### 37.4.3 Clocks

The sensor master clock (ISI\_MCK) can be generated either by the Advanced Power Management Controller (APMC) through a Programmable Clock output or by an external oscillator connected to the sensor.

None of the sensors embeds a power management controller, so providing the clock by the APMC is a simple and efficient way to control power consumption of the system.

Care must be taken when programming the system clock. The ISI has two clock domains, the system bus clock and the pixel clock provided by sensor. The two clock domains are not synchronized, but the system clock must be faster than pixel clock.

## 37.5.4 Interrupt Enable Register

| Name:    | ISI_IER    |          |         |    |         |        |          |

|----------|------------|----------|---------|----|---------|--------|----------|

| Access:  | Write-only |          |         |    |         |        |          |

| 31       | 30         | 29       | 28      | 27 | 26      | 25     | 24       |

| _        | -          | -        | -       | _  | -       | _      | -        |

| 23       | 22         | 21       | 20      | 19 | 18      | 17     | 16       |

| _        | -          | -        | -       | -  | -       | -      | -        |

| 15       | 14         | 13       | 12      | 11 | 10      | 9      | 8        |

| —        | -          | -        | -       | -  | —       | FR_OVR | FO_C_EMP |

| 7        | 6          | 5        | 4       | 3  | 2       | 1      | 0        |

| FO_P_EMP | FO_P_OVF   | FO_C_OVF | CRC_ERR | -  | SOFTRST | DIS    | SOF      |

#### • SOF: Start of Frame

1: Enables the Start of Frame interrupt.

## • DIS: Image Sensor Interface Disable

1: Enables the DIS interrupt.

#### • SOFTRST: Soft Reset

1: Enables the Soft Reset Completion interrupt.

#### • CRC\_ERR: CRC Synchronization Error

1: Enables the CRC\_SYNC interrupt.

#### • FO\_C\_OVF: FIFO Codec Overflow

1: Enables the codec FIFO overflow interrupt.

#### • FO\_P\_OVF: FIFO Preview Overflow

1: Enables the preview FIFO overflow interrupt.

#### • FO\_P\_EMP

1: Enables the preview FIFO empty interrupt.

#### • FO\_C\_EMP

1: Enables the codec FIFO empty interrupt.

#### • FR\_OVR: Frame Overrun

1: Enables the Frame overrun interrupt.

## 39.11 Peripheral Timings

#### 39.11.1 SPI

#### 39.11.1.1 Maximum SPI Frequency

The following formulas give maximum SPI frequency in Master read and write modes and in Slave read and write modes.

#### **Master Write Mode**

The SPI is only sending data to a slave device such as an LCD, for example. The limit is given by  $SPI_2$  (or  $SPI_5$ ) timing. Since it gives a maximum frequency above the maximum pad speed (see Section 39.6.6 "I/Os"), the maximum SPI frequency is the one from the pad.

#### **Master Read Mode**

$$f_{SPCK}Max = \frac{1}{SPI_0(orSPI_3) + t_{valid}}$$

$t_{valid}$  is the slave time response to output data after deleting an SPCK edge. For a non-volatile memory with  $t_{valid}$  (or  $t_v$ ) = 12 ns,  $f_{SPCK}max$  = 35.4 MHz at  $V_{DDIO}$  = 3.3V.

#### **Slave Read Mode**

In slave mode, SPCK is the input clock for the SPI. The maximum SPCK frequency is given by setup and hold timings  $SPI_7/SPI_8$  (or  $SPI_{10}/SPI_{11}$ ). Since this gives a frequency well above the pad limit, the limit in slave read mode is given by the SPCK pad.

#### **Slave Write Mode**

$$f_{SPCK}Max = \frac{1}{SPI_6(orSPI_9) + t_{setup}}$$

For 3.3V I/O domain and SPI6,  $f_{SPCK}Max = 33$  MHz.  $t_{setup}$  is the setup time from the master before sampling data.

#### **39.11.1.2 Timing Conditions**

Timings are given assuming a capacitance load on MISO, SPCK and MOSI as defined in Table 39-32.

| Table 39-32. | Capacitance Load for MISO, SPCK and MOSI (product dependent) |

|--------------|--------------------------------------------------------------|

|--------------|--------------------------------------------------------------|

|        | Corner |      |  |  |

|--------|--------|------|--|--|

| Supply | Мах    | Min  |  |  |

| 3.3V   | 40 pF  | 5 pF |  |  |

| 1.8V   | 20 pF  | 5 pF |  |  |

#### 39.11.1.3 Timing Extraction

In Figure 39-10 "SPI Master Mode 1 and 2" and Figure 39-11 "SPI Master Mode 0 and 3" the MOSI line shifting edge is represented with a hold time = 0. However, it is important to note that for this device, the MISO line is sampled prior to the MOSI line shifting edge. As shown in Figure 39-9 "MISO Capture in Master Mode", the device sampling point extends the propagation delay  $(t_p)$  for slave and routing delays to more than half the SPI clock period, whereas the common sampling point allows only less than half the SPI clock period.

As an example, an SPI Slave working in Mode 0 is safely driven if the SPI Master is configured in Mode 0.