#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product StatusActiveCore ProcessorH85/2000Core Size16-BitSpeed25MHzConnectivitySCI, SmartCardPeriperalsDMA, POR, PWM, WDTNumber of I/O106Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-Nutber of V/Cor/VdOI3V ~ 3.6VPotage Supply (Vcc/VdI)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOperating Temperature-20°C ~ 75°C (TA)Mounting Type144-BFQFPSupplier Device Package144-QFP (2020)Purchase URLhttps://www.exfl.com/product-detail/renesa-electronics-america/df233bt/c25v |                            |                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------|

| Core Size16-BitSpeed25MHzConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O106Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-GFP (20x20)                                                                                                                          | Product Status             | Active                                                                        |

| Speed25MHzConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O106Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-PFP (20x20)                                                                                                                                         | Core Processor             | H8S/2000                                                                      |

| ConnectivitySCI, SmartCardPeripheralsDMA, POR, PWM, WDTNumber of I/O106Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-0FP (20x20)                                                                                                                                                   | Core Size                  | 16-Bit                                                                        |

| PeripheralsDMA, POR, PWM, WDTNumber of I/O106Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                             | Speed                      | 25MHz                                                                         |

| Number of I/O106Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-0FP (20x20)                                                                                                                                                                                                          | Connectivity               | SCI, SmartCard                                                                |

| Program Memory Size256KB (256K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                          | Peripherals                | DMA, POR, PWM, WDT                                                            |

| Program Memory TypeFLASHEEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                             | Number of I/O              | 106                                                                           |

| EEPROM Size-RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                                                     | Program Memory Size        | 256KB (256K x 8)                                                              |

| RAM Size8K x 8Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                                                                 | Program Memory Type        | FLASH                                                                         |

| Voltage - Supply (Vcc/Vdd)3V ~ 3.6VData ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                                                                               | EEPROM Size                | -                                                                             |

| Data ConvertersA/D 12x10b; D/A 4x8bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                                                                                                                  | RAM Size                   | 8K x 8                                                                        |

| Oscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                     | Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                     |

| Operating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                                            | Data Converters            | A/D 12x10b; D/A 4x8b                                                          |

| Mounting TypeSurface MountPackage / Case144-BFQFPSupplier Device Package144-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                                                                                  | Oscillator Type            | Internal                                                                      |

| Package / Case     144-BFQFP       Supplier Device Package     144-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                                                                                           | Operating Temperature      | -20°C ~ 75°C (TA)                                                             |

| Supplier Device Package 144-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | Surface Mount                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Package / Case             | 144-BFQFP                                                                     |

| Purchase URL https://www.e-xfl.com/product-detail/renesas-electronics-america/df2338vfc25v                                                                                                                                                                                                                                                                                                                                                                                                               | Supplier Device Package    | 144-QFP (20x20)                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2338vfc25v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Item                                 | Page | Revision (See                                                                                                                                      | Manual for De                                    | tails)           |                   |                     |        |          |  |

|--------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|-------------------|---------------------|--------|----------|--|

| 19.13.1 Features                     | 789  | Description am                                                                                                                                     | ended                                            |                  |                   |                     |        |          |  |

|                                      |      | Reprogram                                                                                                                                          | ming capability                                  |                  |                   |                     |        |          |  |

|                                      |      | The flash mem                                                                                                                                      | ory can be repro                                 | ogramr           | ned n             | nin. 100            | ) time | es.      |  |

| 22.2.6 Flash Memory                  | 910  | Table 22.21 an                                                                                                                                     | nended                                           |                  |                   |                     |        |          |  |

| Characteristics                      |      | Item                                                                                                                                               |                                                  | Symbol           | Min               | Тур                 | Max    | Unit     |  |

| Table 22.21 Flash                    |      | Erase time <sup>*1*3*6</sup>                                                                                                                       |                                                  | t <sub>E</sub>   | _                 | 50                  | 1000   | ms/block |  |

| Memory<br>Characteristics            |      | Reprogramming count                                                                                                                                |                                                  | N <sub>WEC</sub> | 100 <sup>*7</sup> | 10000 <sup>*8</sup> | -      | Times    |  |

|                                      |      | Data retention time <sup>*9</sup>                                                                                                                  |                                                  | t <sub>DRP</sub> | 10                | _                   | _      | Years    |  |

|                                      |      |                                                                                                                                                    | Wait time after SWE bit<br>setting <sup>*1</sup> | x                | 1                 | -                   | _<br>  | μs       |  |

|                                      | 911  | Notes 7 to 9 added                                                                                                                                 |                                                  |                  |                   |                     |        |          |  |

|                                      |      | Notes: 7. Minimum number of times for which all<br>characteristics are guaranteed after rewriting<br>(Guarantee range is 1 to minimum value).      |                                                  |                  |                   |                     |        |          |  |

|                                      |      |                                                                                                                                                    | erence value for<br>uld normally fun             |                  | •                 | •                   |        | ewriting |  |

|                                      |      | <ol> <li>Data retention characteristic when rewriting is<br/>performed within the specification range, including<br/>the minimum value.</li> </ol> |                                                  |                  |                   |                     |        |          |  |

| D.1 Port States in                   | 1207 | Note *1 delete                                                                                                                                     | d                                                |                  |                   |                     |        |          |  |

| Each Mode                            |      | (Before) $\overline{\text{WDTOVF}}^{*1} \rightarrow (\text{After}) \overline{\text{WDTOVF}}$                                                       |                                                  |                  |                   |                     |        |          |  |

| Table D.1 I/O Port<br>States in Each | 1208 | Note 1 shown below deleted                                                                                                                         |                                                  |                  |                   |                     |        |          |  |

| Processing State                     |      |                                                                                                                                                    | VDTOVF pin fur<br>version.                       | nction o         | canno             | t be us             | ed in  | the F-   |  |

### Table 8.3DTC Functions

|    |                                                                                                                                   |                                                        | Addres             | s Registers             |

|----|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|-------------------------|

| Tr | ansfer Mode                                                                                                                       | Activation Source                                      | Transfer<br>Source | Transfer<br>Destination |

| •  | Normal mode                                                                                                                       | • IRQ                                                  | 24 bits            | 24 bits                 |

|    | <ul> <li>One transfer request transfers one byte<br/>or one word</li> </ul>                                                       | <ul><li>TPU TGI</li><li>8-bit timer CMI</li></ul>      |                    |                         |

|    | <ul> <li>Memory addresses are incremented<br/>or decremented by 1 or 2</li> </ul>                                                 | <ul><li>SCI TXI or RXI</li><li>A/D converter</li></ul> |                    |                         |

|    | <ul> <li>Up to 65,536 transfers possible</li> </ul>                                                                               | ADI                                                    |                    |                         |

| ٠  | Repeat mode                                                                                                                       | DMAC DEND                                              |                    |                         |

|    | <ul> <li>One transfer request transfers one byte<br/>or one word</li> </ul>                                                       | Software                                               |                    |                         |

|    | <ul> <li>Memory addresses are incremented<br/>or decremented by 1 or 2</li> </ul>                                                 |                                                        |                    |                         |

|    | <ul> <li>After the specified number of transfers<br/>(1 to 256), the initial state resumes and<br/>operation continues</li> </ul> |                                                        |                    |                         |

| •  | Block transfer mode                                                                                                               |                                                        |                    |                         |

|    | <ul> <li>One transfer request transfers a block<br/>of the specified size</li> </ul>                                              |                                                        |                    |                         |

|    | <ul> <li>Block size is from 1 to 256 bytes or words</li> </ul>                                                                    |                                                        |                    |                         |

|    | <ul> <li>Up to 65,536 transfers possible</li> </ul>                                                                               |                                                        |                    |                         |

| _  | <ul> <li>A block area can be designated at either<br/>the source or destination</li> </ul>                                        |                                                        |                    |                         |

### 9.6.2 Register Configuration

Table 9.9 shows the port 5 register configuration. Bits 7 to 4 of port 5 are input ports, and have no data direction register or data register.

### Table 9.9Port 5 Registers

| Name                             | Abbreviation | R/W | Initial Value     | Address <sup>*1</sup> |

|----------------------------------|--------------|-----|-------------------|-----------------------|

| Port 5 data direction register   | P5DDR        | W   | H'0 <sup>*2</sup> | H'FEB4                |

| Port 5 data register             | P5DR         | R/W | H'0 <sup>*2</sup> | H'FF64                |

| Port 5 register                  | PORT5        | R   | Undefined         | H'FF54                |

| Port function control register 2 | PFCR2        | R/W | H'30              | H'FFAC                |

| System control register          | SYSCR        | R/W | H'01              | H'FF39                |

Notes: 1. Lower 16 bits of the address.

2. Value of bits 3 to 0.

### Port 5 Data Direction Register (P5DDR)

| Bit        | :      | 7         | 6         | 5         | 4         | 3      | 2      | 1      | 0      |

|------------|--------|-----------|-----------|-----------|-----------|--------|--------|--------|--------|

|            |        | —         | _         | —         | —         | P53DDR | P52DDR | P51DDR | P50DDR |

| Initial va | alue : | Undefined | Undefined | Undefined | Undefined | 0      | 0      | 0      | 0      |

| R/W        | :      | _         | _         | _         | _         | W      | W      | W      | W      |

P5DDR is an 8-bit write-only register, the individual bits of which specify input or output for the pins of port 5. Bits 7 to 4 are reserved. P5DDR cannot be read; if it is, an undefined value will be read.

Setting a P5DDR bit to 1 makes the corresponding port 5 pin an output pin, while clearing the bit to 0 makes the pin an input pin.

P5DDR is initialized to H'0 (bits 3 to 0) by a reset, and in hardware standby mode. It retains its prior state in software standby mode. As the SCI is initialized, the pin states are determined by the P5DDR and P5DR specifications.

### 9.10.3 Pin Functions

Port 9 pins also function as interrupt input pins ( $\overline{IRQ}_2$ ,  $\overline{IRQ}_3$ ,  $\overline{IRQ}_4$ ,  $\overline{IRQ}_5$ ,  $\overline{IRQ}_6$ , and  $\overline{IRQ}_7$ ). Port 9 pin functions are shown in table 9.18.

### Table 9.18 Port 9 Pin Functions

| Selection Method an                                                                                 | d Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| The pin function is switched as shown below according to the combination of bits P97DDR and IRQPAS. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| P97DDR                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Pin function                                                                                        | P97 input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P97 output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                                                                     | IRQ <sub>7</sub> interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | pt input pin <sup>*</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Note: * IRQ7 input whe                                                                              | en IRQPAS = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ding to the combination of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| P96DDR                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Pin function                                                                                        | P9 <sub>6</sub> input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P96 output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| IRQ <sub>6</sub> interrupt input pin*                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Note: $* \overline{IRQ}_6$ input when IRQPAS = 0.                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                     | vitched as shown below according to the combination of QPAS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| P95DDR                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Pin function                                                                                        | P9₅ input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P9₅ output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                                                                     | IRQ₅ interrupt input pin*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Note: * IRQ5 input whe                                                                              | Note: * IRQ₅ input when IRQPAS = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| •                                                                                                   | The pin function is switched as shown below according to the combination bits P94DDR and IRQPAS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| P94DDR                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Pin function                                                                                        | P9₄ input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P9₄ output pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                                                                     | IRQ₄ interrupt input pin*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Note: * IRQ <sub>4</sub> input whe                                                                  | en IRQPAS = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                     | The pin function is sw         bits P97DDR and IRG         P97DDR         Pin function         Note: * IRQ7 input wh         The pin function is sw         bits P96DDR and IRG         P96DDR         Pin function         Note: * IRQ6 input wh         The pin function is sw         bits P95DDR and IRG         P95DDR         Pin function         Note: * IRQ5 input wh         The pin function is sw         bits P95DDR         Pin function         Note: * IRQ5 input wh         The pin function is sw         bits P94DDR         Pin function         P94DDR         Pin function | bits P97DDR and IRQPAS.P97DDR0Pin functionP97 input pinIRQ7 input when IRQPAS = 0.The pin function is switched as shown below accordits P96DDR and IRQPAS.P96DDR0Pin functionP96 input pinIRQ6 input when IRQPAS = 0.Note: * IRQ6 input when IRQPAS = 0.The pin function is switched as shown below accordits P95DDR and IRQPAS = 0.The pin function is switched as shown below accordits P95DDR and IRQPAS.P95DDR0Pin functionP95 input pinIRQ5 interruptionNote: * IRQ5 input when IRQPAS = 0.The pin function is switched as shown below accordits P95DDR and IRQPAS.P95DDR0Pin function is switched as shown below accordits P95DDR and IRQPAS.P95DDR0Pin function is switched as shown below accordits P95DDR and IRQPAS.P95DDR0Pin function is switched as shown below accordits P94DDR and IRQPAS.P94DDR0Pin functionP94 input pin |  |  |  |  |  |  |

### 9.15.4 MOS Input Pull-Up Function

Port E has a built-in MOS input pull-up function that can be controlled by software. This MOS input pull-up function can be used in modes 4, 5, and 6 when 8-bit bus mode is selected, or in mode 7, and can be specified as on or off on an individual bit basis.

When a PEDDR bit is cleared to 0 in mode 4, 5, or 6 when 8-bit bus mode is selected, or in mode 7, setting the corresponding PEPCR bit to 1 turns on the MOS input pull-up for that pin.

The MOS input pull-up function is in the off state after a reset, and in hardware standby mode. The prior state is retained in software standby mode.

Table 9.29 summarizes the MOS input pull-up states.

### Table 9.29MOS Input Pull-Up States (Port E)

| Modes  |            | Reset | Hardware<br>Standby Mode | Software<br>Standby Mode | In Other<br>Operations |

|--------|------------|-------|--------------------------|--------------------------|------------------------|

| 7      |            | Off   | Off                      | On/off                   | On/off                 |

| 4 to 6 | 8-bit bus  |       |                          |                          |                        |

|        | 16-bit bus |       |                          | Off                      | Off                    |

Legend

Off: MOS input pull-up is always off.

On/off: On when PEDDR = 0 and PEPCR = 1; otherwise off.

## Renesas

| Channel | Bit 3<br>IOC3 | Bit 2<br>IOC2 | Bit 1<br>IOC1 | Bit 0<br>IOC0 | Descripti                                             | on                                                  |                                                |                               |

|---------|---------------|---------------|---------------|---------------|-------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|-------------------------------|

| 3       | 0             | 0             | 0             | 0             | TGR3C                                                 | Output disabled                                     | (Initial value)                                |                               |

|         |               |               |               | 1             | is output                                             | Initial output is 0                                 | 0 output at compare match                      |                               |

|         |               |               | 1             | 0             | <ul> <li>compare<br/>register*<sup>1</sup></li> </ul> | output                                              | 1 output at compare match                      |                               |

|         |               |               |               | 1             | _ 0                                                   |                                                     | Toggle output at compare match                 |                               |

|         |               | 1             | 0             | 0             | _                                                     | Output disabled                                     |                                                |                               |

|         |               |               |               | 1             | _                                                     | Initial output is 1                                 | 0 output at compare match                      |                               |

|         |               |               | 1             | 0             | _                                                     | output                                              | 1 output at compare match                      |                               |

|         |               |               |               | 1             | _                                                     |                                                     | Toggle output at compare match                 |                               |

|         | 1             | 0             | 0             | 0             | TGR3C                                                 | Capture input                                       | Input capture at rising edge                   |                               |

|         |               |               |               | 1             | is input                                              |                                                     | •                                              | Input capture at falling edge |

|         |               |               | 1             | *             | <ul> <li>capture<br/>register<sup>*1</sup></li> </ul> | TIOCC3 pin                                          | Input capture at both edges                    |                               |

|         |               | 1             | *             | *             |                                                       | Capture input<br>source is channel<br>4/count clock | Input capture at TCNT4 count-<br>up/count-down |                               |

\*: Don't care

Note: 1. When the BFA bit in TMDR3 is set to 1 and TGR3C is used as a buffer register, this setting is invalid and input capture/output compare is not generated.

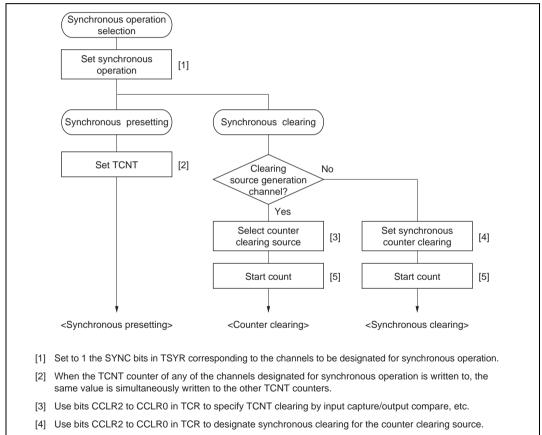

### 10.4.3 Synchronous Operation

In synchronous operation, the values in a number of TCNT counters can be rewritten simultaneously (synchronous presetting). Also, a number of TCNT counters can be cleared simultaneously by making the appropriate setting in TCR (synchronous clearing).

Synchronous operation enables TGR to be incremented with respect to a single time base.

Channels 0 to 5 can all be designated for synchronous operation.

**Example of Synchronous Operation Setting Procedure:** Figure 10.14 shows an example of the synchronous operation setting procedure.

[5] Set to 1 the CST bits in TSTR for the relevant channels, to start the count operation.

### Figure 10.14 Example of Synchronous Operation Setting Procedure

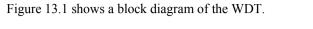

### 13.1.2 Block Diagram

Figure 13.1 Block Diagram of WDT

### **Restrictions on Use of DMAC or DTC**

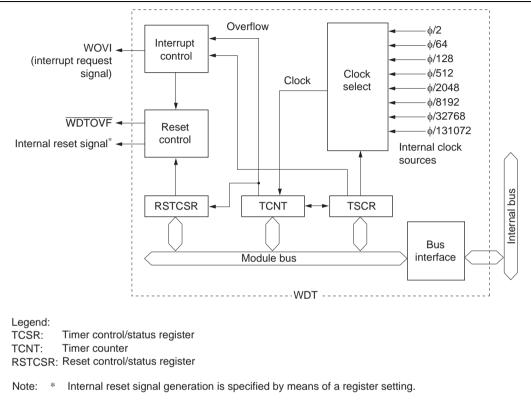

- When an external clock source is used as the serial clock, the transmit clock should not be input until at least 5 φ clock cycles after TDR is updated by the DMAC or DTC. Misoperation may occur if the transmit clock is input within 4 φ clocks after TDR is updated. (Figure 14.22)

- When RDR is read by the DMAC or DTC, be sure to set the activation source to the relevant SCI receive-data-full interrupt (RXI).

Figure 14.22 Example of Synchronous Transmission Using DTC

# Section 16 A/D Converter (12 Analog Input Channel Version)

## 16.1 Overview

The chip incorporates a successive-approximations type 10-bit A/D converter that allows up to twelve analog input channels to be selected.

### 16.1.1 Features

A/D converter features are listed below.

- 10-bit resolution

- Twelve input channels

- Settable analog conversion voltage range

- Conversion of analog voltages with the reference voltage pin ( $V_{ref}$ ) as the analog reference voltage

- High-speed conversion

- Minimum conversion time: 6.7 µs per channel (at 20-MHz operation)

- Choice of single mode or scan mode

- Single mode: Single-channel A/D conversion

- --- Scan mode: Continuous A/D conversion on 1 to 4 channels

- Four data registers

- Conversion results are held in a 16-bit data register for each channel

- Sample and hold function

- Three kinds of conversion start

- Choice of software or timer conversion start trigger (TPU or 8-bit timer), or ADTRG pin

- A/D conversion end interrupt generation

- A/D conversion end interrupt (ADI) request can be generated at the end of A/D conversion

- The DMA controller (DMAC) or data transfer controller (DTC) can be activated for data transfer by an interrupt

- Module stop mode can be set

- As the initial setting, A/D converter operation is halted. Register access is enabled by exiting module stop mode.

## Renesas

### **19.13.9** Register Configuration

The registers used to control the on-chip flash memory when enabled are shown in table 19.27. In order to access the FLMCR1, FLMCR2, EBR1, and EBR2 registers, the FLSHE bit must be set to 1 in SYSCR2 (except RAMER).

### Table 19.27 Flash Memory Registers

| Register Name                   | Abbreviation         | R/W   | Initial Value           | Address <sup>*1</sup> |

|---------------------------------|----------------------|-------|-------------------------|-----------------------|

| Flash memory control register 1 | FLMCR1 <sup>*6</sup> | R/W*3 | H'00/H'80 <sup>*4</sup> | H'FFC8 <sup>*2</sup>  |

| Flash memory control register 2 | FLMCR2 <sup>*6</sup> | R/W*3 | H'00                    | H'FFC9 <sup>*2</sup>  |

| Erase block register 1          | EBR1 <sup>*6</sup>   | R/W*3 | H'00 <sup>*5</sup>      | H'FFCA <sup>*2</sup>  |

| Erase block register 2          | EBR2 <sup>*6</sup>   | R/W*3 | H'00 <sup>*5</sup>      | H'FFCB <sup>*2</sup>  |

| System control register 2       | SYSCR2*7             | R/W   | H'00                    | H'FF42                |

| RAM emulation register          | RAMER                | R/W   | H'00                    | H'FEDB                |

Notes: 1. Lower 16 bits of the address.

2. Flash memory. Registers selection is performed by the FLSHE bit in system control register 2 (SYSCR2).

In modes in which the on-chip flash memory is disabled, a read will return H'00, and writes are invalid. Writes are also disabled when the FWE bit is cleared to 0 in FLMCR1.

- 4. When a high level is input to the FWE pin, the initial value is H'80.

- 5. When a low level is input to the FWE pin, or if a high level is input and the SWE bit in FLMCR1 is not set, these registers are initialized to H'00.

- 6. FLMCR1, FLMCR2, EBR1, and EBR2 are 8-bit registers. Only byte accesses are valid for these registers, the access requiring 2 states.

- 7. The SYSCR2 register can only be used in the F-ZTAT version. In the mask ROM version this register will return an undefined value if read, and cannot be modified.

| Block (Size)     | Address              |

|------------------|----------------------|

| EB0 (4 kbytes)   | H'000000 to H'000FFF |

| EB1 (4 kbytes)   | H'001000 to H'001FFF |

| EB2 (4 kbytes)   | H'002000 to H'002FFF |

| EB3 (4 kbytes)   | H'003000 to H'003FFF |

| EB4 (4 kbytes)   | H'004000 to H'004FFF |

| EB5 (4 kbytes)   | H'005000 to H'005FFF |

| EB6 (4 kbytes)   | H'006000 to H'006FFF |

| EB7 (4 kbytes)   | H'007000 to H'007FFF |

| EB8 (32 kbytes)  | H'008000 to H'00FFFF |

| EB9 (64 kbytes)  | H'010000 to H'01FFFF |

| EB10 (64 kbytes) | H'020000 to H'02FFFF |

| EB11 (64 kbytes) | H'030000 to H'03FFFF |

### Table 19.28 Flash Memory Erase Blocks

### 19.14.5 System Control Register 2 (SYSCR2)

| Bit        | :     | 7 | 6 | 5 | 4 | 3     | 2 | 1 | 0 |

|------------|-------|---|---|---|---|-------|---|---|---|

|            |       |   | _ | _ |   | FLSHE | _ |   | — |

| Initial va | lue : | 0 | 0 | 0 | 0 | 0     | 0 | 0 | 0 |

| R/W        | :     | — | — | — | — | R/W   | — | — | — |

SYSCR2 is an 8-bit readable/writable register that performs on-chip flash memory control.

SYSCR2 is initialized to H'00 by a reset and in hardware standby mode.

SYSCR2 can only be used in the F-ZTAT versions. In the mask ROM versions this register will return an undefined value if read, and cannot be modified.

Bits 7 to 4—Reserved: These bits cannot be modified and are always read as 0.

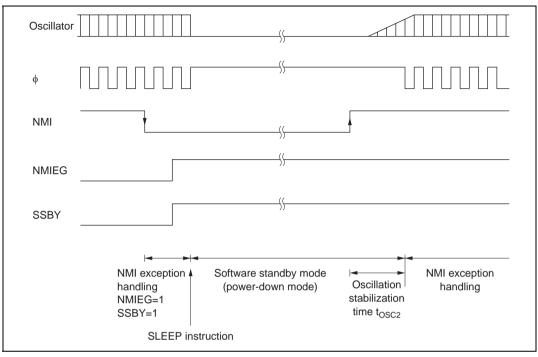

Software standby mode is then cleared at the rising edge on the NMI pin.

Figure 21.2 Software Standby Mode Application Example

### 21.6.5 Usage Notes

**I/O Port Status:** In software standby mode, I/O port states are retained. If the OPE bit is set to 1, the address bus and bus control signal output is also retained. Therefore, there is no reduction in current dissipation for the output current when a high-level signal is output.

**Current Dissipation during Oscillation Stabilization Wait Period:** Current dissipation increases during the oscillation stabilization wait period.

**Write Data Buffer Function:** The write data buffer function and software standby mode cannot be used at the same time. When the write data buffer function is used, the WDBE bit in BCRL should be cleared to 0 to cancel the write data buffer function before entering software standby mode. Also check that external writes have finished, by reading external addresses, etc., before executing a SLEEP instruction to enter software standby mode. See section 6.9, Write Data Buffer Function, for details of the write data buffer function.

## Renesas

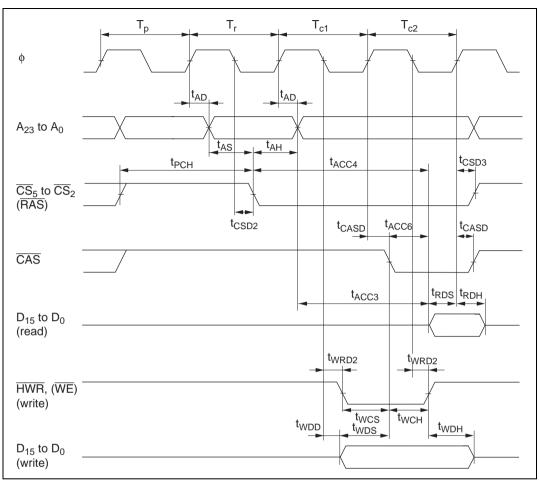

Figure 22.9 DRAM Bus Timing

### Section 22 Electrical Characteristics

|                                         |                              |                  |                   | Con | dition A | Con | dition B |                     | Test            |

|-----------------------------------------|------------------------------|------------------|-------------------|-----|----------|-----|----------|---------------------|-----------------|

| Item                                    |                              |                  | Symbol            | Min | Max      | Min | Мах      | Unit                | Conditions      |

| SCI                                     | Input clock                  | Asynchronous     | t <sub>Scyc</sub> | 4   | _        | 4   | _        | t <sub>cyc</sub>    | Figure          |

|                                         | cycle                        | Synchronous      |                   | 6   | _        | 6   |          | _                   | 22.28           |

|                                         | Input clock pu               | ulse width       | t <sub>scкw</sub> | 0.4 | 0.6      | 0.4 | 0.6      | $\mathbf{t}_{Scyc}$ | _               |

|                                         | Input clock rise time        |                  | t <sub>SCKr</sub> | —   | 1.5      | —   | 1.5      | t <sub>cyc</sub>    | _               |

|                                         | Input clock fa               | II time          | t <sub>SCKf</sub> | —   | 1.5      | —   | 1.5      | _                   |                 |

|                                         | Transmit data                | a delay time     | $t_{TXD}$         | —   | 50       | —   | 40       | ns                  | Figure          |

| Receive data setup tim<br>(synchronous) |                              | •                | t <sub>RXS</sub>  | 50  | —        | 40  | _        | ns                  | 22.29           |

|                                         | Receive data<br>(synchronous | t <sub>RXH</sub> | 50                | _   | 40       | _   | ns       | _                   |                 |

| A/D<br>converter                        | Trigger input                | setup time       | t <sub>TRGS</sub> | 30  | _        | 30  | _        | ns                  | Figure<br>22.30 |

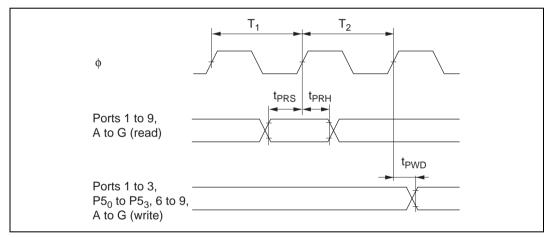

### Figure 22.20 I/O Port Input/Output Timing

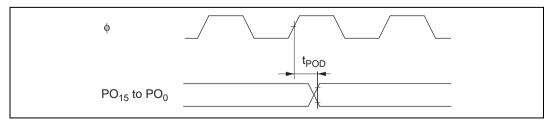

### Figure 22.21 PPG Output Timing

### 22.1.5 D/A Conversion Characteristics

### Table 22.10 D/A Conversion Characteristics

Condition A:  $V_{CC} = 2.7 \text{ V}$  to 3.6 V,  $AV_{CC} = 2.7 \text{ V}$  to 3.6 V,  $V_{ref} = 2.7 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to 20 MHz,  $T_a = -20^{\circ}\text{C}$  to 75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to 85°C (wide-range specifications)

Condition B:  $V_{CC} = 3.0 \text{ V}$  to 3.6 V,  $AV_{CC} = 3.0 \text{ V}$  to 3.6 V,  $V_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 2 \text{ MHz}$  to 25 MHz,  $T_a = -20^{\circ}\text{C}$  to 75°C (regular specifications),  $T_a = -40^{\circ}\text{C}$  to 85°C (wide-range specifications)

|                      |     | Conditio | on A |     | Conditio |      | Test |                             |  |  |

|----------------------|-----|----------|------|-----|----------|------|------|-----------------------------|--|--|

| ltem                 | Min | Тур      | Max  | Min | Тур      | Мах  | Unit | Conditions                  |  |  |

| Resolution           | 8   | 8        | 8    | 8   | 8        | 8    | Bits |                             |  |  |

| Conversion time      |     | —        | 10   | —   | —        | 10   | μS   | 20 pF-capacitive load       |  |  |

| Absolute<br>accuracy |     | ±2.0     | ±3.0 | —   | ±2.0     | ±3.0 | LSB  | 2 M $\Omega$ resistive load |  |  |

|                      | _   | _        | ±2.0 |     | —        | ±2.0 | LSB  | 4 M $\Omega$ resistive load |  |  |

| -           | _                 | _           | _             | _                 | _               | _               | _              | _                | _                 | _                  | _                  | _             | _               | _                | _                 | _                 | _             | _               | _                | _                 | _                 | _             | _                 | _                 | _                 | _                 | _              | _                | _                 | _                  | _                  | _            | _              | _               | _                | _                |               |