#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8S/2000                                                                       |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 25MHz                                                                          |

| Connectivity               | SCI, SmartCard                                                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 106                                                                            |

| Program Memory Size        | 384KB (384K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 12x10b; D/A 4x8b                                                           |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 144-BFQFP                                                                      |

| Supplier Device Package    | 144-QFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df2339evfc25v |

|                            |                                                                                |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

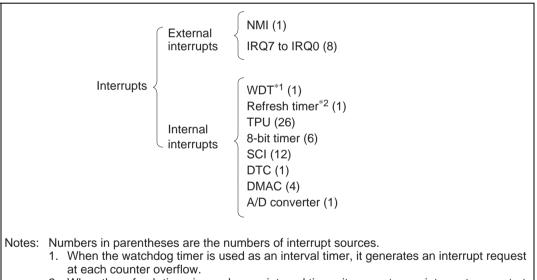

## 4.4 Interrupts

Interrupt exception handling can be requested by nine external sources (NMI, IRQ7 to IRQ0) and 52 internal sources in the on-chip supporting modules. Figure 4.3 classifies the interrupt sources and the number of interrupts of each type.

The on-chip supporting modules that can request interrupts include the watchdog timer (WDT), refresh timer, 16-bit timer-pulse unit (TPU), 8-bit timer, serial communication interface (SCI), data transfer controller (DTC), DMA controller (DMAC), and A/D converter. Each interrupt source has a separate vector address.

NMI is the highest-priority interrupt. Interrupts are controlled by the interrupt controller. The interrupt controller has two interrupt control modes and can assign interrupts other than NMI to eight priority/mask levels to enable multiplexed interrupt control.

For details of interrupts, see section 5, Interrupt Controller.

2. When the refresh timer is used as an interval timer, it generates an interrupt request at each compare match.

Figure 4.3 Interrupt Sources and Number of Interrupts

## 6.2 Register Descriptions

| Bit :           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0          |

|-----------------|------|------|------|------|------|------|------|------------|

|                 | ABW7 | ABW6 | ABW5 | ABW4 | ABW3 | ABW2 | ABW1 | ABW0       |

| Modes 5 to 7    |      |      |      |      |      |      |      | . <u> </u> |

| Initial value : | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1          |

| R/W :           | R/W        |

| Mode 4          |      |      |      |      |      |      |      |            |

| Initial value : | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0          |

| R/W :           | R/W        |

## 6.2.1 Bus Width Control Register (ABWCR)

ABWCR is an 8-bit readable/writable register that designates each area as either 8-bit access space or 16-bit access space.

ABWCR sets the data bus width for the external memory space. The bus width for on-chip memory and internal I/O registers is fixed regardless of the settings in ABWCR.

After a reset and in hardware standby mode, ABWCR is initialized to H'FF in modes 5 to  $7^*$ , and to H'00 in mode 4. It is not initialized in software standby mode.

Note: \* Modes 6 and 7 cannot be used in the ROMless version.

Bits 7 to 0—Area 7 to 0 Bus Width Control (ABW7 to ABW0): These bits select whether the corresponding area is to be designated as 8-bit access space or 16-bit access space.

| Bit n<br>ABWn | Description                            |

|---------------|----------------------------------------|

| 0             | Area n is designated for 16-bit access |

| 1             | Area n is designated for 8-bit access  |

| (n = 7 to 0)  |                                        |

| ABWCR | ASTCR | WCF | RH, WCRL | Bus S     | pecifications (Ba | sic Bus Interface)  |

|-------|-------|-----|----------|-----------|-------------------|---------------------|

| ABWn  | ASTn  | Wn1 | Wn0      | Bus Width | Access States     | Program Wait States |

| 0     | 0     |     |          | 16        | 2                 | 0                   |

|       | 1     | 0   | 0        | -         | 3                 | 0                   |

|       |       |     | 1        | -         |                   | 1                   |

|       |       | 1   | 0        | -         |                   | 2                   |

|       |       |     | 1        | -         |                   | 3                   |

| 1     | 0     | —   | _        | 8         | 2                 | 0                   |

|       | 1     | 0   | 0        | -         | 3                 | 0                   |

|       |       |     | 1        | -         |                   | 1                   |

|       |       | 1   | 0        | -         |                   | 2                   |

|       |       |     | 1        | -         |                   | 3                   |

Table 6.3Bus Specifications for Each Area (Basic Bus Interface)

#### 6.3.3 Memory Interfaces

The chip's interfaces comprise a basic bus interface that allows direct connection of ROM, SRAM, and so on; a DRAM interface that allows direct connection of DRAM; and a burst ROM interface that allows direct connection of burst ROM. The interface can be selected independently for each area.

An area for which the basic bus interface is designated functions as normal space, an area for which the DRAM interface is designated functions as DRAM space, and an area for which the burst ROM interface is designated functions as burst ROM space.

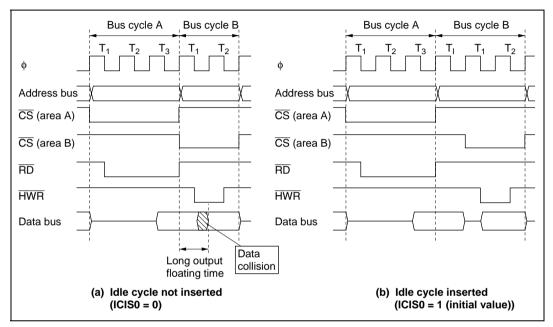

Write after Read: If an external write occurs after an external read while the ICIS0 bit in BCRH is set to 1, an idle cycle is inserted at the start of the write cycle.

Figure 6.32 shows an example of the operation in this case. In this example, bus cycle A is a read cycle for ROM with a long output floating time, and bus cycle B is a CPU write cycle. In (a), an idle cycle is not inserted, and a collision occurs in bus cycle B between the read data from ROM and the CPU write data. In (b), an idle cycle is inserted, and a data collision is prevented.

Figure 6.32 Example of Idle Cycle Operation (2)

## 6.12 Resets and Bus Controller

In a reset, the chip, including the bus controller, enters the reset state immediately, and any executing bus cycle is aborted.

Block Transfer Mode

| Bit 3<br>DTF3 | Bit 2<br>DTF2 | Bit 1<br>DTF1 | Bit 0<br>DTF0                                                      | Description                                                        |

|---------------|---------------|---------------|--------------------------------------------------------------------|--------------------------------------------------------------------|

| 0             | 0             | 0             | 0                                                                  | — (Initial value)                                                  |

|               |               |               | 1                                                                  | Activated by A/D converter conversion end interrupt                |

|               |               | 1             | 0                                                                  | Activated by DREQ pin falling edge input*                          |

|               |               |               | 1                                                                  | Activated by DREQ pin low-level input                              |

|               | 1             | 0             | 0                                                                  | Activated by SCI channel 0 transmit-data-empty interrupt           |

|               |               |               | 1                                                                  | Activated by SCI channel 0 receive-data-full interrupt             |

|               |               | 1             | 0                                                                  | Activated by SCI channel 1 transmit-data-empty interrupt           |

|               |               |               | 1                                                                  | Activated by SCI channel 1 receive-data-full interrupt             |

| 1 0           | 0             | 0             | Activated by TPU channel 0 compare match/input capture A interrupt |                                                                    |

|               |               |               | 1                                                                  | Activated by TPU channel 1 compare match/input capture A interrupt |

|               |               | 1             | 0                                                                  | Activated by TPU channel 2 compare match/input capture A interrupt |

|               |               |               | 1                                                                  | Activated by TPU channel 3 compare match/input capture A interrupt |

|               | 1             | 0             | 0                                                                  | Activated by TPU channel 4 compare match/input capture A interrupt |

|               |               |               | 1                                                                  | Activated by TPU channel 5 compare match/input capture A interrupt |

|               |               | 1             | 0                                                                  | _                                                                  |

|               |               |               | 1                                                                  | _                                                                  |

Note: \* Detected as a low level in the first transfer after transfer is enabled.

The same factor can be selected for more than one channel. In this case, activation starts with the highest-priority channel according to the relative channel priorities. For relative channel priorities, see section 7.5.13, DMAC Multi-Channel Operation.

Operation Incremented/ decremented every

transfer. Initial

setting is restored

#### 7.5.4 Repeat Mode

Repeat mode can be specified by setting the RPE bit in DMACR to 1, and clearing the DTIE bit to 0. In repeat mode, MAR is updated after each byte or word transfer in response to a single transfer request, and this is executed the number of times specified in ETCRL. On completion of the specified number of transfers, MAR and ETCRL are automatically restored to their original settings and operation continues.

One address is specified by MAR, and the other by IOAR. The transfer direction can be specified by the DTDIR bit in DMACR.

Table 7.8 summarizes register functions in repeat mode.

|          |     |   | Fur       | nction      |                      |   |

|----------|-----|---|-----------|-------------|----------------------|---|

| Register |     |   | DTDIR = 0 | DTDIR = 1   | Initial Setting      |   |

| 23       |     | 0 | Source    | Destination | Start address of     |   |

|          | MAR |   | address   | address     | transfer destination | , |

|          |     |   | register  | register    | or transfer source   | 1 |

#### Table 7.8 Register Functions in Repeat Mode

|    |      |    |             |         |                                    |                               |                                                          | when value reaches<br>H'0000                                                         |

|----|------|----|-------------|---------|------------------------------------|-------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|

| 23 | H'FF | 15 | IOAR        | 0       | Destination<br>address<br>register | Source<br>address<br>register | Start address of transfer source or transfer destination | Fixed                                                                                |

|    |      |    | 7<br>ETCR   |         | Holds numb<br>transfers            | per of                        | Number of transfers                                      | Fixed                                                                                |

|    |      |    | 7 V<br>ETCR | 0<br>१L | Transfer co                        | unter                         | Number of transfers                                      | Decremented every<br>transfer. Loaded with<br>ETCRH value when<br>count reaches H'00 |

Legend:

- MAR: Memory address register

- IOAR: I/O address register

- ETCR: Execute transfer count register

- DTDIR: Data transfer direction bit

## Port 1 Data Register (P1DR)

| Bit        | :     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|            |       | P17DR | P16DR | P15DR | P14DR | P13DR | P12DR | P11DR | P10DR |

| Initial va | lue : | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W        | :     | R/W   |

P1DR is an 8-bit readable/writable register that stores output data for the port 1 pins (P17 to P10).

P1DR is initialized to H'00 by a reset, and in hardware standby mode. It retains its prior state in software standby mode.

#### Port 1 Register (PORT1)

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            |       | P17 | P16 | P15 | P14 | P13 | P12 | P11 | P10 |

| Initial va | lue : | *   | *   | *   | *   | *   | *   | *   | *   |

| R/W        | :     | R   | R   | R   | R   | R   | R   | R   | R   |

Note: \* Determined by state of pins P17 to P10.

PORT1 is an 8-bit read-only register that shows the pin states. It cannot be written to. Writing of output data for the port 1 pins ( $P1_7$  to  $P1_0$ ) must always be performed on P1DR.

If a port 1 read is performed while P1DDR bits are set to 1, the P1DR values are read. If a port 1 read is performed while P1DDR bits are cleared to 0, the pin states are read.

After a reset and in hardware standby mode, PORT1 contents are determined by the pin states, as P1DDR and P1DR are initialized. PORT1 retains its prior state in software standby mode.

## 9.4.3 **Pin Functions**

Port 3 pins also function as SCI I/O pins (TxD<sub>0</sub>, RxD<sub>0</sub>, SCK<sub>0</sub>, TxD<sub>1</sub>, RxD<sub>1</sub>, and SCK<sub>1</sub>). Port 3 pin functions are shown in table 9.7.

#### Table 9.7Port 3 Pin Functions

| P3 <sub>5</sub> /SCK <sub>1</sub> |                                                       | The pin function is switched as shown below according to the combination of bit C/ $\overline{A}$ in the SCI1 SMR, bits CKE0 and CKE1 in SCR, and bit P35DDR. |                                   |                                 |                                 |                               |  |  |  |

|-----------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------|---------------------------------|-------------------------------|--|--|--|

|                                   | CKE1                                                  |                                                                                                                                                               | (                                 |                                 | 1                               |                               |  |  |  |

|                                   | C/Ā                                                   |                                                                                                                                                               | 0                                 |                                 | 1                               |                               |  |  |  |

|                                   | CKE0                                                  |                                                                                                                                                               | 0                                 | 1                               | _                               | _                             |  |  |  |

|                                   | P35DDR                                                | 0                                                                                                                                                             | 1                                 | _                               | _                               |                               |  |  |  |

|                                   | Pin function                                          | P3₅<br>input pin                                                                                                                                              | P3₅<br>output pin*                | SCK <sub>1</sub><br>output pin* | SCK <sub>1</sub><br>output pin* | SCK <sub>1</sub><br>input pin |  |  |  |

|                                   | Note: * When                                          | P350DR = 1                                                                                                                                                    | , the pin beco                    | omes an NM                      | OS open-dra                     | in output.                    |  |  |  |

| P34/SCK0                          | Note: * When<br>The pin function<br>bit C/A in the So | n is switched                                                                                                                                                 | as shown be                       | ow accordin                     | g to the com                    | pination of                   |  |  |  |

| P34/SCK0                          | The pin functior                                      | n is switched                                                                                                                                                 | as shown bel<br>s CKE0 and 0      | ow accordin                     | g to the com                    | pination of                   |  |  |  |

| P34/SCK0                          | The pin function bit C/A in the Section               | n is switched                                                                                                                                                 | as shown bel<br>s CKE0 and 0      | low accordin<br>CKE1 in SCF     | g to the com                    | pination of                   |  |  |  |

| P3₄/SCK₀                          | The pin function bit C/A in the St                    | n is switched<br>CI0 SMR, bits                                                                                                                                | as shown bel<br>s CKE0 and 0      | low accordin<br>CKE1 in SCF     | g to the com                    | pination of                   |  |  |  |

| P34/SCK0                          | The pin functior<br>bit C/Ā in the S<br>CKE1<br>C/Ā   | n is switched<br>CI0 SMR, bits                                                                                                                                | as shown bel<br>s CKE0 and (<br>0 | low accordin<br>CKE1 in SCF     | g to the com                    | pination of                   |  |  |  |

## 9.12 Port B

## 9.12.1 Overview

Port B is an 8-bit I/O port. Port B has an address bus output function, and the pin functions change according to the operating mode.

Port B has a built-in MOS input pull-up function that can be controlled by software.

Figure 9.11 shows the port B pin configuration.

|                                           | Port B pins                         | Pin functions in modes 4 and 5 |

|-------------------------------------------|-------------------------------------|--------------------------------|

|                                           | ► PB <sub>7</sub> / A <sub>15</sub> | A <sub>15</sub> (output)       |

|                                           | ► PB <sub>6</sub> / A <sub>14</sub> | A <sub>14</sub> (output)       |

|                                           | ► PB <sub>5</sub> / A <sub>13</sub> | A <sub>13</sub> (output)       |

|                                           | ► PB <sub>4</sub> / A <sub>12</sub> | A <sub>12</sub> (output)       |

| Port B                                    | ► PB <sub>3</sub> / A <sub>11</sub> | A <sub>11</sub> (output)       |

|                                           | ► PB <sub>2</sub> / A <sub>10</sub> | A <sub>10</sub> (output)       |

|                                           | ► PB <sub>1</sub> / A <sub>9</sub>  | A <sub>9</sub> (output)        |

|                                           | ► PB <sub>0</sub> / A <sub>8</sub>  | A <sub>8</sub> (output)        |

| Pin functions in                          | n mode 6                            | Pin functions in mode 7        |

| PB <sub>7</sub> (input) / A <sub>15</sub> | (output)                            | PB <sub>7</sub> (I/O)          |

| PB <sub>6</sub> (input) / A <sub>14</sub> | (output)                            | PB <sub>6</sub> (I/O)          |

| PB <sub>5</sub> (input) / A <sub>13</sub> | (output)                            | PB <sub>5</sub> (I/O)          |

| PB <sub>4</sub> (input) / A <sub>12</sub> | (output)                            | PB <sub>4</sub> (I/O)          |

| PB <sub>3</sub> (input) / A <sub>11</sub> | (output)                            | PB <sub>3</sub> (I/O)          |

| PB <sub>2</sub> (input) / A <sub>10</sub> | (output)                            | PB <sub>2</sub> (I/O)          |

| PB <sub>1</sub> (input) / A <sub>9</sub>  | (output)                            | PB <sub>1</sub> (I/O)          |

| PB <sub>0</sub> (input) / A <sub>8</sub>  | (output)                            | PB <sub>0</sub> (I/O)          |

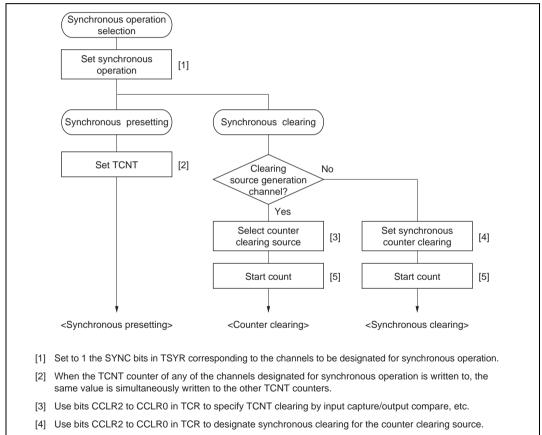

#### 10.4.3 Synchronous Operation

In synchronous operation, the values in a number of TCNT counters can be rewritten simultaneously (synchronous presetting). Also, a number of TCNT counters can be cleared simultaneously by making the appropriate setting in TCR (synchronous clearing).

Synchronous operation enables TGR to be incremented with respect to a single time base.

Channels 0 to 5 can all be designated for synchronous operation.

**Example of Synchronous Operation Setting Procedure:** Figure 10.14 shows an example of the synchronous operation setting procedure.

[5] Set to 1 the CST bits in TSTR for the relevant channels, to start the count operation.

#### Figure 10.14 Example of Synchronous Operation Setting Procedure

## 14.2 Register Descriptions

# 14.2.1 Receive Shift Register (RSR) Bit : 7 6 5 4 3 2 1 0 R/W : -

RSR is a register used to receive serial data.

The SCI sets serial data input from the RxD pin in RSR in the order received, starting with the LSB (bit 0), and converts it to parallel data. When one byte of data has been received, it is transferred to RDR automatically.

RSR cannot be directly read or written to by the CPU.

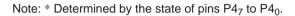

## 14.2.2 Receive Data Register (RDR)

| Bit        | :     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|-------|---|---|---|---|---|---|---|---|

|            | ſ     |   |   |   |   |   |   |   |   |

| Initial va | lue : | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W        | :     | R | R | R | R | R | R | R | R |

RDR is a register that stores received serial data.

When the SCI has received one byte of serial data, it transfers the received serial data from RSR to RDR where it is stored, and completes the receive operation. After this, RSR is receive-enabled.

Since RSR and RDR function as a double buffer in this way, continuous receive operations can be performed.

RDR is a read-only register, and cannot be written to by the CPU.

RDR is initialized to H'00 by a reset, and in standby mode or module stop mode.

## 17.2 Register Descriptions

#### 17.2.1 D/A Data Registers 0 to 3 (DADR0 to DADR3)

| Bit        | :     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|

|            |       |     |     |     |     |     |     |     |     |

| Initial va | lue : | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W        | :     | R/W |

DADR0 to DADR3 are 8-bit readable/writable registers that store data for conversion.

Whenever output is enabled, the values in DADR0 to DADR3 are converted and output from the analog output pins.

DADR0 to DADR3 are each initialized to H'00 by a reset and in hardware standby mode.

#### 17.2.2 D/A Control Registers 01 and 23 (DACR01, DACR23)

| Bit        | :     | 7     | 6     | 5   | 4 | 3 | 2 | 1 | 0 |   |

|------------|-------|-------|-------|-----|---|---|---|---|---|---|

|            |       | DAOE1 | DAOE0 | DAE | — | — | — | — | — | ] |

| Initial va | lue : | 0     | 0     | 0   | 1 | 1 | 1 | 1 | 1 | - |

| R/W        | :     | R/W   | R/W   | R/W | _ | _ | _ | _ | _ |   |

DACR01 and DACR23 are 8-bit readable/writable registers that control the operation of the D/A converter.

DACR01 and DACR23 are each initialized to H'1F by a reset and in hardware standby mode.

Bit 7—D/A Output Enable 1 (DAOE1): Controls D/A conversion and analog output.

| Bit 7 |                                                         |                             |

|-------|---------------------------------------------------------|-----------------------------|

| DAOE1 | Description                                             |                             |

| 0     | Analog output DA1 (DA3) is disabled                     | (Initial value)             |

| 1     | Channel 1 (channel 3) D/A conversion is enabled; analog | output DA1 (DA3) is enabled |

**Bit 3—Flash Memory Control Register Enable (FLSHE):** Controls CPU access to the flash memory control registers (FLMCR1, FLMCR2, EBR1, and EBR2). Writing 1 to the FLSHE bit enables the flash memory control registers to be read and written to. Clearing FLSHE to 0 designates these registers as unselected (the register contents are retained).

| Bit 3<br>FLSHE | Description                                                                                 |

|----------------|---------------------------------------------------------------------------------------------|

| 0              | Flash control registers are not selected for addresses H'FFFFC8 to H'FFFFCB (Initial value) |

| 1              | Flash control registers are selected for addresses H'FFFFC8 to H'FFFFCB                     |

Bits 2 and 1—Reserved: These bits cannot be modified and are always read as 0.

Bit 0—Reserved: This bit should be written with 0.

#### 19.5.6 RAM Emulation Register (RAMER)

| Bit        | :     | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|------------|-------|---|---|---|---|------|------|------|------|

|            |       |   | _ | _ |   | RAMS | RAM2 | RAM1 | RAM0 |

| Initial va | lue : | 0 | 0 | 0 | 0 | 0    | 0    | 0    | 0    |

| R/W        | :     | — | _ | _ | — | R/W  | R/W  | R/W  | R/W  |

RAMER specifies the area of flash memory to be overlapped with part of RAM when emulating real-time flash memory programming. RAMER is initialized to H'00 by a reset and in hardware standby mode. It is not initialized in software standby mode. RAMER settings should be made in user mode or user program mode.

Flash memory area divisions are shown in table 19.8. To ensure correct operation of the emulation function, the ROM for which RAM emulation is performed should not be accessed immediately after this register has been modified. Normal execution of an access immediately after register modification is not guaranteed.

Bits 7 to 4—Reserved: These bits cannot be modified and are always read as 0.

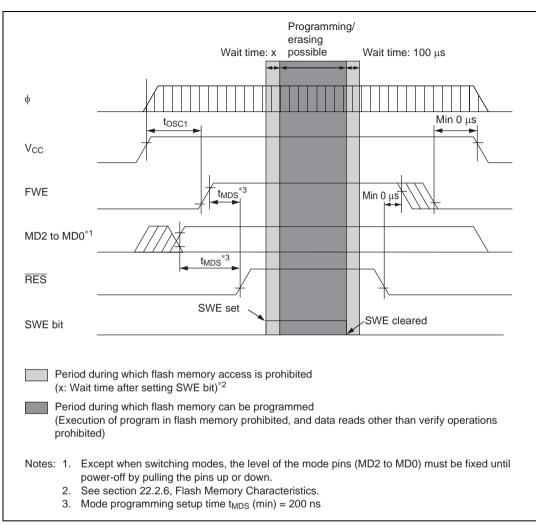

## Figure 19.56 Power-On/Off Timing (Boot Mode)

#### TIOR3H—Timer I/O Control Register 3H

H'FE82

TPU3

| Bit :           | 7    | 6    | 5    | 4    | ;     | 3    |      | 2                  | 1     | 0                          |                                  |

|-----------------|------|------|------|------|-------|------|------|--------------------|-------|----------------------------|----------------------------------|

| Initial value : | IOB3 | IOB2 | IOB1 | IOB0 | 10    | A3   |      | OA2                | IOA1  | IOA0                       |                                  |

|                 | 0    | 0    | 0    | 0    | (     | 0    |      | 0                  | 0     | 0                          |                                  |

| Read/Write :    | R/W  | R/W  | R/W  | R/W  | R     | W    |      | R/W                | R/W   | R/W                        |                                  |

|                 |      |      |      |      |       |      |      |                    |       |                            |                                  |

|                 |      |      |      |      |       |      |      |                    |       |                            |                                  |

|                 |      |      |      | TGR  | 3A I, | /0 C | ontr | ol                 |       |                            |                                  |

|                 |      |      |      | 0    | 0     | 0    | 0    | TGR3A              |       | ut disabled                |                                  |

|                 |      |      |      |      |       |      | 1    | is outpu<br>compar | e     | l output is                | 0 output at compare match        |

|                 |      |      |      |      |       | 1    | 0    | register           |       |                            | 1 output at compare match        |

|                 |      |      |      |      |       |      | 1    | ]                  |       |                            | Toggle output at compare match   |

|                 |      |      |      |      | 1     | 0    | 0    | ]                  | Outp  | ut disabled                |                                  |

|                 |      |      |      |      |       |      | 1    | ]                  |       | l output is                | 0 output at compare match        |

|                 |      |      |      |      |       | 1    | 0    | ]                  | 1 out | iput                       | 1 output at compare match        |

|                 |      |      |      |      |       |      | 1    |                    |       |                            | Toggle output at compare match   |

|                 |      |      |      | 1    | 0     | 0    | 0    | TGR3A<br>is input  | Capt  | ure input                  | Input capture at rising edge     |

|                 |      |      |      |      |       |      | 1    | capture            | TIOC  | CA <sub>3</sub> pin        | Input capture at falling edge    |

|                 |      |      |      |      |       | 1    | *    | register           |       |                            | Input capture at both edges      |

|                 |      |      |      |      | 1     | *    | *    |                    |       | ure input                  | Input capture at TCNT4 count-up/ |

|                 |      |      |      |      |       |      |      |                    |       | ce is channel<br>unt clock | count-down                       |

|                 |      |      |      |      |       |      |      |                    |       |                            | * : Don't care                   |

|                 |      |      |      |      |       |      |      |                    |       |                            |                                  |

TGR3B I/O Control

| 0 | 0 | 0 | 0 | TGR3B                | Output disabled                                     |                                                  |  |  |  |  |

|---|---|---|---|----------------------|-----------------------------------------------------|--------------------------------------------------|--|--|--|--|

|   |   |   | 1 | is output<br>compare | Initial output is                                   | 0 output at compare match                        |  |  |  |  |

|   |   | 1 | 0 | register             | 0 output                                            | 1 output at compare match                        |  |  |  |  |

|   |   |   | 1 |                      |                                                     | Toggle output at compare match                   |  |  |  |  |

|   | 1 | 0 | 0 |                      | Output disabled                                     |                                                  |  |  |  |  |

|   |   |   | 1 |                      | Initial output is 1                                 | 0 output at compare match                        |  |  |  |  |

|   |   | 1 | 0 |                      | output                                              | 1 output at compare match                        |  |  |  |  |

|   |   |   | 1 |                      |                                                     | Toggle output at compare match                   |  |  |  |  |

| 1 | 0 | 0 | 0 | TGR3B                | Capture input source is                             | Input capture at rising edge                     |  |  |  |  |

|   |   |   | 1 | is input<br>capture  | TIOCB <sub>3</sub> pin                              | Input capture at falling edge                    |  |  |  |  |

|   |   | 1 | * | register             |                                                     | Input capture at both edges                      |  |  |  |  |

|   | 1 | * | * |                      | Capture input<br>source is channel<br>4/count clock | Input capture at TCNT4 count-up/<br>count-down*1 |  |  |  |  |

\* : Don't care

Note: 1. When bits TPSC2 to TPSC0 in TCR4 are set to B'000, and  $\phi/1$  is used as the TCNT4 count clock, this setting is invalid and input capture does not occur.

#### NDRH—Next Data Register H

## H'FF4C (FF4E)

PPG

(1) When pulse output group output triggers are the same

(a) Address: H'FF4C

(2)

|     | Bit :               | 7          | 6            | 5            | 4             | 3          | 2           | 1    | 0    |  |  |

|-----|---------------------|------------|--------------|--------------|---------------|------------|-------------|------|------|--|--|

|     |                     | NDR15      | NDR14        | NDR13        | NDR12         | NDR11      | NDR10       | NDR9 | NDR8 |  |  |

|     | Initial value :     | 0          | 0            | 0            | 0             | 0          | 0           | 0    | 0    |  |  |

|     | Read/Write :        | R/W        | R/W          | R/W          | R/W           | R/W        | R/W         | R/W  | R/W  |  |  |

|     |                     |            | Sto          | res the next | t data for pu | Ise output | groups 3 an | d 2  |      |  |  |

| (b) | (b) Address: H'FF4E |            |              |              |               |            |             |      |      |  |  |

|     |                     |            |              |              |               |            |             |      |      |  |  |

|     | Bit :               | 7          | 6            | 5            | 4             | 3          | 2           | 1    | 0    |  |  |

|     |                     | _          | _            | _            | —             | —          | —           | —    | —    |  |  |

|     | Initial value :     | 1          | 1            | 1            | 1             | 1          | 1           | 1    | 1    |  |  |

|     | Read/Write :        | _          | _            | _            | _             | _          | _           | _    | _    |  |  |

|     | en pulse outpu      | •          | put trigger  | s are diffe  | rent          |            |             |      |      |  |  |

| (a) | Address: H'FF       | 4C         |              |              |               |            |             |      |      |  |  |

|     | Bit :               | 7          | 6            | 5            | 4             | 3          | 2           | 1    | 0    |  |  |

|     |                     | NDR15      | NDR14        | NDR13        | NDR12         | _          | —           | —    | _    |  |  |

|     | Initial value :     | 0          | 0            | 0            | 0             | 1          | 1           | 1    | 1    |  |  |

|     | Read/Write :        | R/W        | R/W          | R/W          | R/W           | _          |             | _    | _    |  |  |

|     |                     | Stores the | next data fo | or pulse out | put group 3   |            |             |      |      |  |  |

| (b) | Address: H'FF       | 4E         |              |              |               |            |             |      |      |  |  |

|     | Bit :               | 7          | 6            | 5            | 4             | 3          | 2           | 1    | 0    |  |  |

| Bit          | :    | 7 | 6 | 5 | 4 | 3     | 2     | 1    | 0    | _ |

|--------------|------|---|---|---|---|-------|-------|------|------|---|

|              |      | — | — | — | — | NDR11 | NDR10 | NDR9 | NDR8 |   |

| Initial valu | re : | 1 | 1 | 1 | 1 | 0     | 0     | 0    | 0    | - |

| Read/Wri     | te : | — | — | — | — | R/W   | R/W   | R/W  | R/W  |   |

|              |      |   |   |   |   |       |       | 1    |      |   |

Stores the next data for pulse output group 2

| PORT4—Port           | 4 Register | r   |     |     | Port 4 |     |     |     |   |  |

|----------------------|------------|-----|-----|-----|--------|-----|-----|-----|---|--|

| Bit :                | 7          | 6   | 5   | 4   | 3      | 2   | 1   | 0   | _ |  |

|                      | P47        | P46 | P45 | P44 | P43    | P42 | P41 | P40 |   |  |

| Initial value :      | *          | *   | *   | *   | *      | *   | *   | *   |   |  |

| Read/Write :         | R          | R   | R   | R   | R      | R   | R   | R   |   |  |

|                      |            |     |     |     |        |     |     |     |   |  |

|                      |            |     |     |     |        |     |     |     |   |  |

| State of port 4 pins |            |     |     |     |        |     |     |     |   |  |

| PORT5—      | Port 5 | S Register | •   |     | Port 5     |             |     |     |     |   |

|-------------|--------|------------|-----|-----|------------|-------------|-----|-----|-----|---|

| Bit         | :      | 7          | 6   | 5   | 4          | 3           | 2   | 1   | 0   |   |

|             |        | P57        | P56 | P55 | P54        | P53         | P52 | P51 | P50 | ] |

| Initial val | ue :   | *          | *   | *   | *          | *           | *   | *   | *   | - |

| Read/Wr     | rite : | R          | R   | R   | R          | R           | R   | R   | R   |   |

|             |        |            |     |     |            |             |     |     |     |   |

|             |        |            |     |     | State of p | oort 5 pins |     |     |     |   |

Note: \* Determined by the state of pins  $P5_7$  to  $P5_0$ .

| PORT6-     | –Port 6 | Register | •   |     | Por        | Port 6     |     |     |     |   |

|------------|---------|----------|-----|-----|------------|------------|-----|-----|-----|---|

| Bit        | :       | 7        | 6   | 5   | 4          | 3          | 2   | 1   | 0   |   |

|            |         | P67      | P66 | P65 | P64        | P63        | P62 | P61 | P60 | ] |

| Initial va | alue :  | *        | *   | *   | *          | *          | *   | *   | *   | 1 |

| Read/W     | /rite : | R        | R   | R   | R          | R          | R   | R   | R   |   |

|            |         |          |     |     |            |            |     |     |     |   |

|            |         |          |     |     |            |            |     |     |     |   |

|            |         |          |     |     | State of p | ort 6 pins |     |     |     |   |

Note: \* Determined by the state of pins  $P6_7$  to  $P6_0$ .

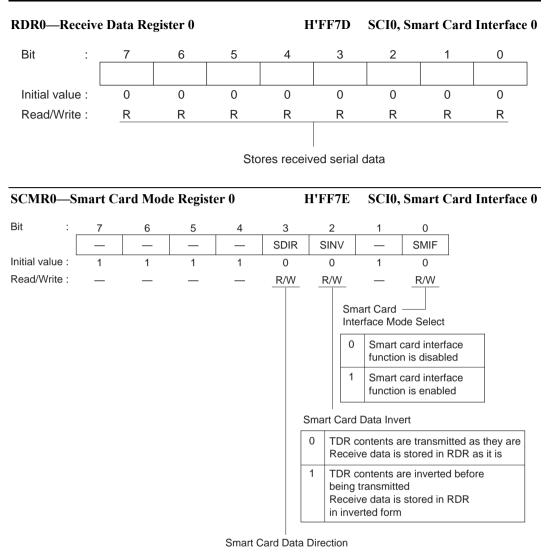

| 0 | TDR contents are transmitted LSB-first<br>Receive data is stored in RDR LSB-first |

|---|-----------------------------------------------------------------------------------|

| 1 | TDR contents are transmitted MSB-first<br>Receive data is stored in RDR MSB-first |

| Port Name<br>Pin Name                                                                                    | MCU<br>Operating<br>Mode |               | Reset | Hardware<br>Standby<br>Mode | Software<br>Standby Mode                                    | Bus-Released<br>State | Program Execution<br>State<br>Sleep Mode               |

|----------------------------------------------------------------------------------------------------------|--------------------------|---------------|-------|-----------------------------|-------------------------------------------------------------|-----------------------|--------------------------------------------------------|

| PA <sub>3</sub> /A <sub>19</sub><br>PA <sub>2</sub> /A <sub>18</sub><br>PA <sub>1</sub> /A <sub>17</sub> | 4, 5                     |               | L     | Т                           | [OPE = 0]<br>T<br>[OPE = 1]                                 | Т                     | Address output                                         |

| PA <sub>0</sub> /A <sub>16</sub>                                                                         | 6                        |               | Т     | Т                           | kept<br>[DDR · OPE = 0]<br>T                                | т                     | [DDR = 0]<br>Input port                                |

|                                                                                                          |                          |               |       |                             | [DDR · OPE = 1]<br>kept                                     |                       | [DDR = 1]<br>Address output                            |

|                                                                                                          | 7                        |               | Т     | Т                           | kept                                                        | kept                  | I/O port                                               |

| Port B                                                                                                   | 4, 5                     |               | L     | Т                           | [OPE = 0]<br>T<br>[OPE = 1]<br>kept                         | Т                     | Address output                                         |

|                                                                                                          | 6                        |               | Т     | Т                           | $[DDR \cdot OPE = 0]$ T<br>[DDR \cdot OPE = 1]<br>kept      | Т                     | [DDR = 0]<br>Input port<br>[DDR = 1]<br>Address output |

|                                                                                                          | 7                        |               | Т     | Т                           | kept                                                        | kept                  | I/O port                                               |

| Port C                                                                                                   | 4, 5<br>6                |               | L     | Т                           | [OPE = 0]<br>T<br>[OPE = 1]<br>kept                         | Т                     | Address output                                         |

|                                                                                                          |                          |               | Т     | Т                           | $[DDR \cdot OPE = 0]$<br>T<br>$[DDR \cdot OPE = 1]$<br>kept | Т                     | [DDR = 0]<br>Input port<br>[DDR = 1]<br>Address output |

|                                                                                                          | 7                        |               | Т     | Т                           | kept                                                        | kept                  | I/O port                                               |

| Port D                                                                                                   | 4 to 6                   |               | Т     | T                           | Т                                                           | Т                     | Data bus                                               |

|                                                                                                          | 7                        |               | Т     | Т                           | kept                                                        | kept                  | I/O port                                               |

| Port E                                                                                                   | 4 to<br>6                | 8-bit<br>bus  | Т     | Т                           | kept                                                        | kept                  | I/O port                                               |

|                                                                                                          |                          | 16-bit<br>bus | Т     | Т                           | Т                                                           | Т                     | Data bus                                               |

|                                                                                                          | 7                        |               |       | Т                           | kept                                                        | kept                  | I/O port                                               |

#### Appendix D Pin States