Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 48                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 1.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C                                                              |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-LQFP                                                                   |

| Supplier Device Package    | 64-VQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51rd2-rdtil |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Description

T89C51RD2 is high performance CMOS Flash version of the 80C51 CMOS single chip 8-bit microcontroller. It contains a 64 Kbytes Flash memory block for program and for data.

The 64 Kbytes Flash memory can be programmed either in parallel mode or in serial mode with the ISP capability or with software. The programming voltage is internally generated from the standard  $V_{CC}$  pin.

The T89C51RD2 retains all features of the ATMEL 80C52 with 256 bytes of internal RAM, a 7-source 4-level interrupt controller and three timer/counters.

In addition, the T89C51RD2 has a Programmable Counter Array, an XRAM of 1024 bytes, an EEPROM of 2048 bytes, a Hardware Watchdog Timer, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 mode). Pinout is either the standard 40/44 pins of the C52 or an extended version with 6 ports in a 64/68 pins package.

The fully static design of the T89C51RD2 allows to reduce system power consumption by bringing the clock frequency down to any value, even DC, without loss of data.

The T89C51RD2 has 2 software-selectable modes of reduced activity for further reduction in power consumption. In the idle mode the CPU is frozen while the peripherals and the interrupt system are still operating. In the power-down mode the RAM is saved and all other functions are inoperative.

The added features of the T89C51RD2 makes it more powerful for applications that need pulse width modulation, high speed I/O and counting capabilities such as alarms, motor control, corded phones, smart card readers.

| PDIL40<br>PLCC44<br>VQFP44 1.4 | Flash (bytes) | EEPROM<br>(bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | 1/0 |

|--------------------------------|---------------|-------------------|--------------|----------------------|-----|

| T89C51RD2                      | 64K           | 2K                | 1024         | 1280                 | 32  |

Table 1. Memory Size

|    | PLCC68<br>QFP64 1.4 | Flash (bytes) | EEPROM<br>(bytes) | XRAM (bytes) | TOTAL RAM<br>(bytes) | I/O |

|----|---------------------|---------------|-------------------|--------------|----------------------|-----|

| Т8 | 39C51RD2            | 64K           | 2K                | 1024         | 1280                 | 48  |

2

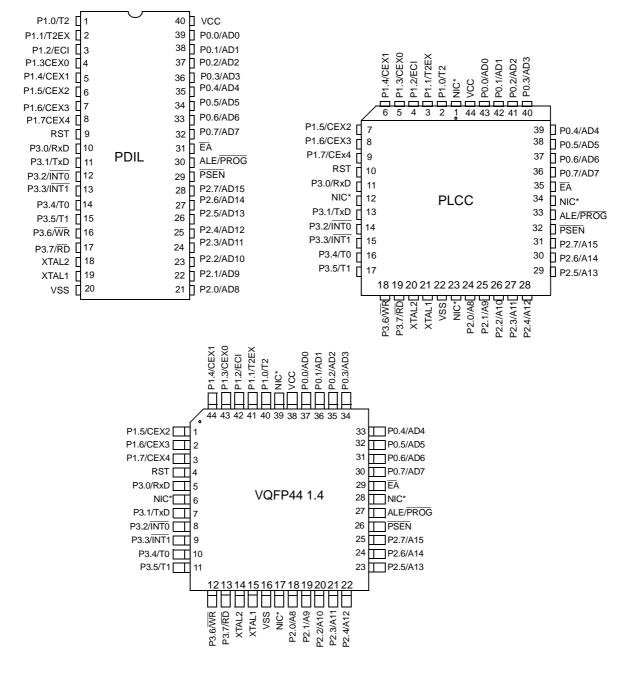

## **Pin Configuration**

Note: NIC = No Internal Connection

4

## SFR Mapping The Special Fund

The Special Function Registers (SFRs) of the T89C51RD2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP, AUXR1

- I/O port registers: P0, P1, P2, P3, P4, P5

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- Power and clock control registers: PCON

- Hardware Watchdog Timer register: WDTRST, WDTPRG

- Interrupt system registers: IE, IP, IPH

- Flash and EEPROM registers: FCON, EECON, EETIM

- Others: AUXR, AUXR1, CKCON

8

# **Enhanced Features** In comparison to the original 80C52, the T89C51RD2 implements some new features, which are:

- The X2 option

- The Dual Data Pointer

- The extended RAM

- The Programmable Counter Array (PCA)

- The Watchdog

- The 4 level interrupt priority system

- The power-off flag

- The ONCE mode

- The ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

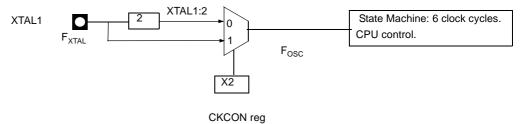

# X2 Feature and Clock Generation

The T89C51RD2 core needs only 6 clock periods per machine cycle. This feature called "X2" provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

Description

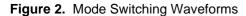

The clock for the whole circuit and peripheral is first divided by two before being used by the CPU core and peripherals. This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%. Figure 1 shows the clock generation block diagram. X2 bit is validated on XTAL1÷2 rising edge to avoid glitches when switching from X2 to STD mode. Figure 2 shows the mode switching waveforms.

Figure 1. Clock Generation Diagram

The X2 bit in the CKCON register (Table 4) allows to switch from 12 clock periods per instruction to 6 clock periods and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

The T0X2, T1X2, T2X2, SiX2, PcaX2 and WdX2 bits in the CKCON register (Table 4) allow to switch from standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2 mode.

More information about the X2 mode can be found in the application note ANM072 "How to take advantage of the X2 features in TS80C51 microcontroller".

Table 4.

CKCON Register

CKCON - Clock Control Register (8Fh)

| 7             | 6               | 5                                                                                                                                                                                                                                                                    | 4                                                                                                                                                                                                                                                                  | 3    | 2    | 1    | 0  |  |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|--|--|--|

| -             | WdX2            | PcaX2                                                                                                                                                                                                                                                                | SiX2                                                                                                                                                                                                                                                               | T2X2 | T1X2 | T0X2 | X2 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                    |      |      |      |    |  |  |  |

| 7             | -               | Reserved                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                    |      |      |      |    |  |  |  |

| 6             | WdX2            | Watchdog clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                     |                                                                                                                                                                                                                                                                    |      |      |      |    |  |  |  |

| 5             | PcaX2           | clock X2 is set<br>Clear to select                                                                                                                                                                                                                                   | Programmable Counter Array clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |      |      |      |    |  |  |  |

| 4             | SiX2            | Enhanced UART clock (Mode 0 and 2) (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |                                                                                                                                                                                                                                                                    |      |      |      |    |  |  |  |

| 3             | T2X2            | <b>Timer2 clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                |                                                                                                                                                                                                                                                                    |      |      |      |    |  |  |  |

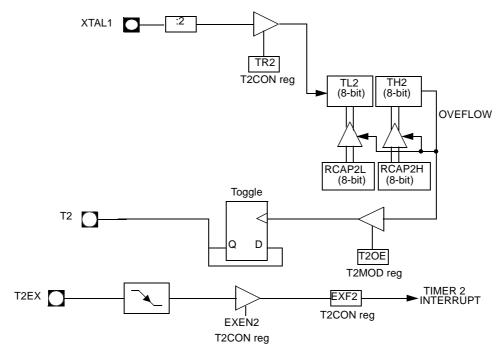

**Figure 6.** Clock-Out Mode  $C/\overline{T2} = 0$

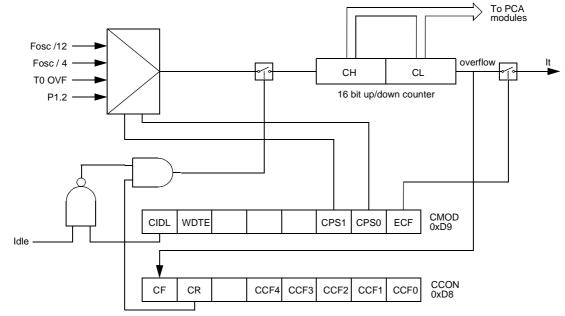

#### Figure 7. PCA Timer/Counter

Table 10.

CMOD: PCA Counter Mode Register

| <b>CMOD</b><br>Address 0D9⊦ | CMOD<br>Address 0D9H                                                                                                                                                                           |                                                                                                                                                    |                                                                          | WDT<br>E                       | -         | -          | -                        | CPS1    | CPS0     | ECF    |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------|-----------|------------|--------------------------|---------|----------|--------|--|

|                             | Re                                                                                                                                                                                             | eset value                                                                                                                                         | 0                                                                        | 0                              | Х         | Х          | Х                        | 0       | 0        | 0      |  |

| Symbol                      | Functio                                                                                                                                                                                        | on                                                                                                                                                 |                                                                          |                                |           |            |                          |         |          |        |  |

| CIDL                        |                                                                                                                                                                                                | Counter Idle control: CIDL = 0 programs the PCA Counter to continue functioning during dle Mode. CIDL = 1 programs it to be gated off during idle. |                                                                          |                                |           |            |                          |         |          |        |  |

| WDTE                        |                                                                                                                                                                                                | Watchdog Timer Enable: WDTE = 0 disables Watchdog Timer function on PCA Module 4.<br>WDTE = 1 enables it.                                          |                                                                          |                                |           |            |                          |         |          |        |  |

| -                           | Not imp                                                                                                                                                                                        | Not implemented, reserved for future use. (1)                                                                                                      |                                                                          |                                |           |            |                          |         |          |        |  |

| CPS1                        | PCA Count Pulse Select bit 1.                                                                                                                                                                  |                                                                                                                                                    |                                                                          |                                |           |            |                          |         |          |        |  |

| CPS0                        | PCA Co                                                                                                                                                                                         | ount Pulse S                                                                                                                                       | elect bit (                                                              | 0.                             |           |            |                          |         |          |        |  |

|                             | CPS<br>1                                                                                                                                                                                       | CPS<br>0 Se                                                                                                                                        | lected PC                                                                | cted PCA input. <sup>(2)</sup> |           |            |                          |         |          |        |  |

|                             | 0                                                                                                                                                                                              | 0 Int                                                                                                                                              | Internal clock $f_{osc}/12$ ( Or $f_{osc}/6$ in X2 Mode).                |                                |           |            |                          |         |          |        |  |

|                             | 0                                                                                                                                                                                              | 1 Int                                                                                                                                              | Internal clock f <sub>osc</sub> /4 ( Or f <sub>osc</sub> /2 in X2 Mode). |                                |           |            |                          |         |          |        |  |

|                             | 1                                                                                                                                                                                              | 0 Tir                                                                                                                                              | ner 0 Ove                                                                | erflow                         |           |            |                          |         |          |        |  |

|                             | 1                                                                                                                                                                                              | 1 Ex                                                                                                                                               | ternal clo                                                               | ck at ECI                      | /P1.2 pin | (max rat   | $e = f_{osc} / \epsilon$ | 3)      |          |        |  |

| ECF                         |                                                                                                                                                                                                |                                                                                                                                                    |                                                                          |                                | •         | = 1 enable | es CF bit                | in CCON | to gener | ate an |  |

| ECF                         | 11External clock at ECI/P1.2 pin (max rate = $f_{osc}/8$ )PCA Enable Counter Overflow interrupt: ECF = 1 enables CF bit in CCON to generate a interrupt. ECF = 0 disables that function of CF. |                                                                                                                                                    |                                                                          |                                |           |            |                          |         |          |        |  |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

2.  $f_{osc} = oscillator frequency$

• The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

Table 13 shows the CCAPMn settings for the various PCA functions.

| CCAPM0=0DAH<br>CCAPM1=0DBH |

|----------------------------|

| CCAPM2=0DCH                |

| CCAPM3=0DDH<br>CCAPM4=0DEH |

|                            |

|             | - | ECO<br>Mn | CAPP<br>n | CAPN<br>n | MATn | TOGn | PWM<br>m | ECCF<br>n |

|-------------|---|-----------|-----------|-----------|------|------|----------|-----------|

| Reset value | Х | 0         | 0         | 0         | 0    | 0    | 0        | 0         |

| -      |                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Symbol | Function                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| -      | Not implemented, reserved for future use. <sup>(1)</sup>                                                                                                   |  |  |  |  |  |  |  |  |  |

| ECOMn  | Enable Comparator. ECOMn = 1 enables the comparator function.                                                                                              |  |  |  |  |  |  |  |  |  |

| CAPPn  | Capture Positive, CAPPn = 1 enables positive edge capture.                                                                                                 |  |  |  |  |  |  |  |  |  |

| CAPNn  | Capture Negative, CAPNn = 1 enables negative edge capture.                                                                                                 |  |  |  |  |  |  |  |  |  |

| MATn   | Match. When MATn = 1, a match of the PCA counter with this module's compare/capture register causes the CCFn bit in CCON to be set, flagging an interrupt. |  |  |  |  |  |  |  |  |  |

| TOGn   | Toggle. When TOGn = 1, a match of the PCA counter with this module's compare/capture register causes the CEXn pin to toggle.                               |  |  |  |  |  |  |  |  |  |

| PWMn   | Pulse Width Modulation Mode. PWMn = 1 enables the CEXn pin to be used as a pulse width modulated output.                                                   |  |  |  |  |  |  |  |  |  |

| ECCFn  | Enable CCF interrupt. Enables compare/capture flag CCFn in the CCON register to generate an interrupt.                                                     |  |  |  |  |  |  |  |  |  |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

| Table 13. | PCA Module Modes ( | (CCAPMn Registers) |

|-----------|--------------------|--------------------|

|-----------|--------------------|--------------------|

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                   |

|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                      |

| х     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn |

| x     | 0     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х     | 16-bit Software Timer / Compare mode.             |

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

The SADEN byte is selected so that each slave may be addressed separately. For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g. 1111 0000b).

For slave A, bit 1 is a 1; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves B and C, but not slave A, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

**Broadcast Address** A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR 0101 0110b SADEN 1111 1100b Broadcast =SADDR OR SADEN1111 111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

Slave A:SADDR1111 0001b <u>SADEN1111 1010b</u> Broadcast1111 1X11b, Slave B:SADDR1111 0011b <u>SADEN1111 1001b</u> Broadcast1111 1X11B, Slave C:SADDR=1111 0010b <u>SADEN1111 1101b</u> Broadcast1111 1111b

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

Reset AddressesOn reset, the SADDR and SADEN registers are initialized to 00h, i.e. the given and<br/>broadcast addresses are XXXX XXXb (all don't-care bits). This ensures that the serial<br/>port will reply to any address, and so, that it is backwards compatible with the 80C51<br/>microcontrollers that do not support automatic address recognition.

| Table 18. | SADEN - | Slave | Address | Mask | Register | (B9h) | ) |

|-----------|---------|-------|---------|------|----------|-------|---|

|-----------|---------|-------|---------|------|----------|-------|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

Reset Value = 0000 0000b Not bit addressable

## Table 24. IP Register

IP - Interrupt Priority Register (B8h)

| 7             | 6               | 5                                  | 4                                                                            | 3              | 2              | 1         | 0   |  |

|---------------|-----------------|------------------------------------|------------------------------------------------------------------------------|----------------|----------------|-----------|-----|--|

| -             | PPC             | PT2                                | PS                                                                           | PT1            | PX1            | PT0       | PX0 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                        |                                                                              |                |                |           |     |  |

| 7             | -               | Reserved<br>The value read         | from this bit                                                                | is indetermina | te. Do not set | this bit. |     |  |

| 6             | PPC             | PCA interrupt<br>Refer to PPCH     |                                                                              | vel.           |                |           |     |  |

| 5             | PT2             |                                    | Timer 2 overflow interrupt Priority bit<br>Refer to PT2H for priority level. |                |                |           |     |  |

| 4             | PS              | Serial port Pri<br>Refer to PSH fe | •                                                                            | el.            |                |           |     |  |

| 3             | PT1             | Timer 1 overfl<br>Refer to PT1H    | •                                                                            | •              |                |           |     |  |

| 2             | PX1             | External internal Refer to PX1H    |                                                                              |                |                |           |     |  |

| 1             | PT0             |                                    | Timer 0 overflow interrupt Priority bit<br>Refer to PT0H for priority level. |                |                |           |     |  |

| 0             | PX0             | External internal Refer to PX0H    |                                                                              |                |                |           |     |  |

Reset Value = X000 0000b Bit addressable

# 40 T89C51RD2

| Oscillator    | VDD Rise Time |        |        |  |  |  |  |

|---------------|---------------|--------|--------|--|--|--|--|

| Start-Up Time | 1 ms          | 10 ms  | 100 ms |  |  |  |  |

| 5 ms          | 820 nF        | 1.2 µF | 12 µF  |  |  |  |  |

| 20 ms         | 2.7 µF        | 3.9 µF | 12 µF  |  |  |  |  |

**Table 26.** Minimum Reset Capacitor Value for a 50 k $\Omega$  Pull-down Resistor<sup>(1)</sup>

Note: These values assume V<sub>DD</sub> starts from 0V to the nominal value. If the time between 2 on/off sequences is too fast, the power-supply de-coupling capacitors may not be fully discharged, leading to a bad reset sequence.

## Warm Reset

To achieve a valid reset, the reset signal must be maintained for at least 2 machine cycles (24 oscillator clock periods) while the oscillator is running. The number of clock periods is mode independent (X2 or X1).

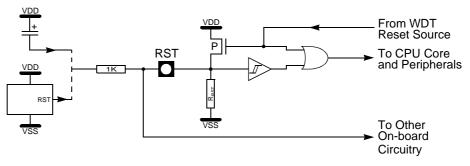

Watchdog ResetAs detailed in Section "Watchdog Timer", the WDT generates a 96-clock period pulse<br/>on the RST pin. In order to properly propagate this pulse to the rest of the application in<br/>case of external capacitor or power-supply supervisor circuit, a 1 kΩ resistor must be<br/>added as shown Figure 18.

#### Figure 18. Reset Circuitry for WDT Reset-out Usage

Table 33. EETIM Register

### EETIM (S:*0D3*h)

EEPROM timing Control Register

| 7          | 6                               | 5                        | 4                               | 3 | 2                                          | 1 | 0              |  |  |

|------------|---------------------------------|--------------------------|---------------------------------|---|--------------------------------------------|---|----------------|--|--|

| EETIM      |                                 |                          |                                 |   |                                            |   |                |  |  |

| Bit Number | Bit Number Mnemonic Description |                          |                                 |   |                                            |   |                |  |  |

| 7-0        | EETIM                           | frequency<br>Value = 5 * | mer register v<br>Fxtal (MHz) i | · | ed to adapt the<br>e, 10 * Fxtal in<br>A5h |   | the oscillator |  |  |

Reset Value = 0000 0000b

# 52 T89C51RD2

| Table 34. | Program | Lock bits |

|-----------|---------|-----------|

|-----------|---------|-----------|

| Program Lock Bits |     |     |     | Protection Description                                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------------|-----|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Security<br>level | LB0 | LB1 | LB2 |                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 1                 | U   | U   | U   | No program lock features enabled. MOVC instruction executed from external program memory returns non encrypted data.                                                                                                                                                                   |  |  |  |  |

| 2                 | Р   | U   | U   | MOVC instruction executed from external program memory are disabled from fetching code bytes from internal memory, $\overline{EA}$ is sampled and latched on reset, and further parallel programming of the Flash is disabled.ISP and software programming with API are still allowed. |  |  |  |  |

| 3                 | х   | Р   | U   | Same as 2, also verify through parallel programming interface is disabled.                                                                                                                                                                                                             |  |  |  |  |

| 4                 | Х   | Х   | Р   | Same as 3, also external execution is disabled.                                                                                                                                                                                                                                        |  |  |  |  |

Note: U: unprogrammed or "one" level.

Note: P: programmed or "zero" level.

Note: X:do not care

Note: WARNING: Security level 2 and 3 should only be programmed after Flash and code verification.

These security bits protect the code access through the parallel programming interface. They are set by default to level 4. The code access through the ISP is still possible and is controlled by the "software security bits" which are stored in the extra Flash memory accessed by the ISP firmware.

To load a new application with the parallel programmer, a chip erase must first be done. This will set the HSB in its inactive state and will erase the Flash memory, including the boot loader and the "Extra Flash Memory" (XAF). If needed, the 1K boot loader and the XAF content must be programmed in the Flash; the code is provided by ATMEL Wireless and Microcontrollers (see section 8.7.); the part reference can always be read using Flash parallel programming modes.

#### Default Values

The default value of the HSB provides parts ready to be programmed with ISP:

- SB: Cleared to secure the content of the HSB.

- BLJB: Cleared to force ISP operation.

- BLLB: Clear to protect the default boot loader.

- LB2-0: Security level four to protect the code from a parallel access with maximum security.

#### Software Registers

Several registers are used, in factory and by parallel programmers, to make copies of hardware registers contents. These values are used by ATMEL Wireless and Microcontrollers ISP (see section 8.7.).

These registers are in the "Extra Flash Memory" part of the Flash memory. This block is also called "XAF" or eXtra Array Flash. They are accessed in the following ways:

- Commands issued by the parallel memory programmer.

- Commands issued by the ISP software.

Calls of API issued by the application software.

They are several software registers described in Table 35

## Set-up modes configuration

Control and program signals must be held at the levels indicated in the two following tables.

| Mada         |                                                                                                                   |     |      | Ale                            |    |      |        |      |      |                                    |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|------|--------------------------------|----|------|--------|------|------|------------------------------------|

| Mode<br>Name | Mode                                                                                                              | Rst | Psen | <br>Ц                          | EA | P2.6 | P2.7   | P3.6 | P3.7 | P0[70]                             |

| PELCK        | Program or Erase Lock.<br>Disable the Erasure or Programming access                                               | 1   | 0    | <br> _                         | 1  | 1    | 0      | 1    | 0    | хх                                 |

| PEULCK       | Program or Erase UnLock.<br>Enable the Erasure or Programming access                                              | 1   | 0    | Note 2                         | 1  | 1    | 0      | 1    | 0    | 55-AA                              |

| PGMC         | Write Code Data (byte)<br>or write Page<br>Always precedeed by PGML                                               | 1   | 0    | <br> _ <br>Internally<br>timed | 1  | 0    | 1      | 1    | 1    | хх                                 |

| PGML         | Memory Page Load<br>(up to 128 bytes)                                                                             | 1   | 0    | Note 1                         | 1  | 0    | 1      | 0    | 1    | Din                                |

| PGMV         | Read Code Data (byte)                                                                                             | 1   | 0    | 1                              | 1  | 0    | <br> _ | 1    | 1    | Dout                               |

| VSB          | Read Security Byte (=HSB)                                                                                         | 1   | 0    | 1                              | 1  | 0    | <br> _ | 0    | 1    | Dout                               |

| PGMS         | Write Security Byte (Note 3)<br>(security byte = HSB)                                                             | 1   | 0    | 10 ms                          | 1  | 1    | 1      | 0    | 0    | Din                                |

| CERR         | Chip Erase User + XAF                                                                                             | 1   | 0    | 100 ms                         | 1  | 1    | 0      | 0    | 0    | xx                                 |

| PGXC         | Write Byte or Page in Extra Memory (XAF)<br>Always precedeed by PGXL                                              | 1   | 0    | <br> _ <br>Internally<br>timed | 1  | 1    | 1      | 0    | 1    | xx                                 |

| PGXL         | Memory Page Load XAF<br>(up to 128 bytes)                                                                         | 1   | 0    | Note 1                         | 1  | 1    | 1      | 0    | 1    | Din                                |

| TMS          | Read Signature bytes<br>30h (Manufacturer code)<br>31h (Device ID #1)<br>60h (Device ID #2)<br>61h (Device ID #3) | 1   | 0    | 1                              | 1  | 0    | <br> _ | 0    | 0    | Dout =<br>58h<br>D7h<br>FCh<br>FFh |

| RXAF         | Read Extra Memory (XAF)                                                                                           | 1   | 0    | 1                              | 1  | 0    | <br> _ | 0    | 0    | Dout                               |

## Table 44. DC Parameters for Standard Voltage <sup>(2)</sup>

| Symbol                   | Parameter                                             | Min | <b>Typ</b> <sup>(5)</sup> | Max                      | Unit | Test Conditions                        |

|--------------------------|-------------------------------------------------------|-----|---------------------------|--------------------------|------|----------------------------------------|

| I <sub>CCProgFlash</sub> | Power Supply Current during Flash Write / Erase       |     | 0.3 Freq<br>(MHz) + 10    | 0.4 Freq (MHz)<br>+ 12   | mA   | $V_{CC} = 5.5 V^{(1)}$                 |

|                          | Power Supply Current during EEprom data Write / Erase |     | 0.7 Freq<br>(MHz) + 3     | 0.7 Freq (MHz)<br>+ 18   | mA   | $V_{CC} = 5.5 V^{(1)}$                 |

|                          | Power Supply Current on idle mode                     |     |                           | 0.5 Freq (MHz)<br>+ 2 mA | mA   | V <sub>CC</sub> = 5.5 V <sup>(2)</sup> |

# 82 T89C51RD2

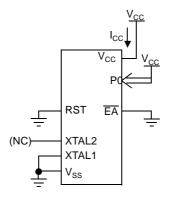

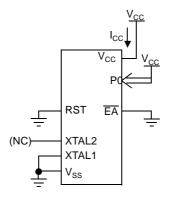

Figure 35.  $I_{CC}$  Test Condition, Power-Down Mode

All other pins are disconnected.

#### **AC Parameters**

Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

$\begin{array}{l} \mbox{Example:} T_{AVLL} = \mbox{Time for Address Valid to ALE Low.} \\ T_{LLPL} = \mbox{Time for ALE Low to PSEN Low.} \end{array}$

$\begin{array}{l} T_{A}=0 \ to \ +70^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V\pm10\%; \ M \ range. \\ T_{A}=-40^{\circ}C \ to \ +85^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V\pm10\%; \ M \ range. \\ T_{A}=0 \ to \ +70^{\circ}C; \ V_{SS}=0 \ V; \ 2.7 \ V < V_{CC} < 3.3 \ V; \ L \ range. \\ T_{A}=-40^{\circ}C \ to \ +85^{\circ}C; \ V_{SS}=0 \ V; \ 2.7 \ V < V_{CC} < 3.3 \ V; \ L \ range. \end{array}$

AC characteristics of -M parts at 3 volts are similar to -L parts

(Load Capacitance for port 0, ALE and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF.)

Table 44, Table 48 and Table 50 give the description of each AC symbols.

Table 46, Table 49 and Table 51 give for each range the AC parameter.

Table 47, Table 50 and Table 52 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols. take the x value in the correponding column (-M or -L) and use this value in the formula.

Example:  $T_{LLIU}$  for -M and 20 MHz, Standard clock.

x = 35 ns T = 50 ns T<sub>CCIV</sub> = 4T - x = 165 ns

Table 43. DC Parameters in Standard Voltage <sup>(1)</sup>

| Symbol                   | Parameter                                                | Min | <b>Typ</b> <sup>(5)</sup> | Мах                    | Unit | Test Conditions                        |

|--------------------------|----------------------------------------------------------|-----|---------------------------|------------------------|------|----------------------------------------|

| C <sub>IO</sub>          | Capacitance of I/O Buffer                                |     |                           | 10                     | pF   | Fc = 1 MHz<br>TA = 25 C                |

| I <sub>PD</sub>          | Power Down Current                                       |     | 120                       | 150                    | А    | $V_{CC} = 3 V \text{ to } 5.5 V^{(3)}$ |

| I <sub>CCOP</sub>        | Power Supply Current on normal mode                      |     |                           | 0.7 Freq<br>(MHz) + 3  | mA   | V <sub>CC</sub> = 5.5 V <sup>(1)</sup> |

| I <sub>CCProgFlash</sub> | Power Supply Current during Flash Write / Erase          |     | 0.3 Freq<br>(MHz) + 10    | 0.4 Freq<br>(MHz) + 12 | mA   | $V_{CC} = 5.5 V^{(1)}$                 |

| I <sub>CCProgEE</sub>    | Power Supply Current during EEprom data Write<br>/ Erase |     | 0.7 Freq<br>(MHz) + 3     | 0.7 Freq<br>(MHz) + 18 | mA   | V <sub>CC</sub> = 5.5 V <sup>(1)</sup> |

| I <sub>CCIDLE</sub>      | Power Supply Current on idle mode                        |     |                           | 0.4 Freq<br>(MHz) + 2  | mA   | $V_{CC} = 5.5 V^{(2)}$                 |

### DC Parameters for Standard Voltage (2)

$\begin{array}{l} T_{A}=0\ C\ to\ +70\ C;\ V_{SS}=0\ V;\ V_{CC}=3\ V\ to\ 5.5\ V;\ F=0\ to\ 33\ MHz.\\ T_{A}=-40\ C\ to\ +85\ C;\ V_{SS}=0\ V;\ V_{CC}=3\ V\ to\ 5.5\ V;\ F=0\ to\ 33\ MHz. \end{array}$

Table 44.

DC Parameters for Standard Voltage <sup>(2)</sup>

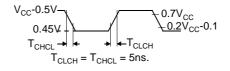

| Symbol            | Parameter                                                 | Min                       | <b>Typ</b> <sup>(5)</sup> | Мах                       | Unit | Test Conditions                         |

|-------------------|-----------------------------------------------------------|---------------------------|---------------------------|---------------------------|------|-----------------------------------------|

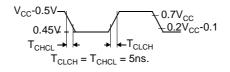

| V <sub>IL</sub>   | Input Low Voltage                                         | -0.5                      |                           | 0.2 V <sub>CC</sub> - 0.1 | V    |                                         |

| V <sub>IH</sub>   | Input High Voltage except XTAL1, RST                      | 0.2 V <sub>CC</sub> + 0.9 |                           | V <sub>CC</sub> + 0.5     | V    |                                         |

| V <sub>IH1</sub>  | Input High Voltage, XTAL1, RST                            | 0.7 V <sub>CC</sub>       |                           | V <sub>CC</sub> + 0.5     | V    |                                         |

| V <sub>OL</sub>   | Output Low Voltage, ports 1, 2, 3, 4 and 5 <sup>(6)</sup> |                           |                           | 0.45                      | V    | I <sub>OL</sub> = 0.8 mA <sup>(4)</sup> |

| V <sub>OL1</sub>  | Output Low Voltage, port 0, ALE, PSEN (6)                 |                           |                           | 0.45                      | V    | I <sub>OL</sub> = 1.6 mA <sup>(4)</sup> |

| V <sub>OH</sub>   | Output High Voltage, ports 1, 2, 3, 4 and 5               | 0.9 V <sub>CC</sub>       |                           |                           | V    | I <sub>OH</sub> = -10 A                 |

| V <sub>OH1</sub>  | Output High Voltage, port 0, ALE, PSEN                    | 0.9 V <sub>CC</sub>       |                           |                           | V    | I <sub>OH</sub> = -40 A                 |

| I <sub>IL</sub>   | Logical 0 Input Current ports 1, 2, 3, 4 and 5            |                           |                           | -50                       | А    | Vin = 0.45 V                            |

| ILI               | Input Leakage Current for P0 only                         |                           |                           | 10                        | А    | 0.45 V < Vin < V <sub>CC</sub>          |

| Ι <sub>τι</sub>   | Logical 1 to 0 Transition Current, ports 1, 2, 3, 4 and 5 |                           |                           | -650                      | A    | Vin = 2.0 V                             |

| R <sub>RST</sub>  | RST Pulldown Resistor                                     | 50                        | 90                        | 200                       | k    |                                         |

| CIO               | Capacitance of I/O Buffer                                 |                           |                           | 10                        | pF   | Fc = 1 MHz<br>TA = 25 C                 |

| I <sub>PD</sub>   | Power Down Current                                        |                           | 120                       | 150                       | А    | $V_{CC} = 3 V \text{ to } 5.5 V^{(3)}$  |

| I <sub>CCOP</sub> | Power Supply Current on normal mode                       |                           |                           | 0.7 Freq (MHz)<br>+ 3 mA  | mA   | $V_{\rm CC} = 5.5 \ V^{(1)}$            |

Figure 35.  $I_{CC}$  Test Condition, Power-Down Mode

All other pins are disconnected.

#### **AC Parameters**

Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

Example:  $T_{AVLL}$  = Time for Address Valid to ALE Low.  $T_{LLPL}$  = Time for ALE Low to PSEN Low.

$\begin{array}{l} T_{A}=0 \ to \ +70 \ C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V \quad 10\%; \ M \ range. \\ T_{A}=-40 \ C \ to \ +85 \ C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V \quad 10\%; \ M \ range. \\ T_{A}=0 \ to \ +70 \ C; \ V_{SS}=0 \ V; \ 2.7 \ V < V_{CC} < 3.3 \ V; \ L \ range. \\ T_{A}=-40 \ C \ to \ +85 \ C; \ V_{SS}=0 \ V; \ 2.7 \ V < V_{CC} < 3.3 \ V; \ L \ range. \\ \end{array}$

AC characteristics of -M parts at 3 volts are similar to -L parts

(Load Capacitance for port 0, ALE and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF.)

Table 44, Table 48 and Table 50 give the description of each AC symbols.

Table 46, Table 49 and Table 51 give for each range the AC parameter.

Table 47, Table 50 and Table 52 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols. take the x value in the correponding column (-M or -L) and use this value in the formula.

Example:  $T_{LLIU}$  for -M and 20 MHz, Standard clock.

x = 35 ns T = 50 ns T<sub>CCIV</sub> = 4T - x = 165 ns