Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | 8051                                                                      |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | SPI, UART/USART                                                           |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 1.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                               |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C                                                              |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-LCC (J-Lead)                                                           |

| Supplier Device Package    | 44-PLCC (16.6x16.6)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/t89c51rd2-slsim |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 3 below shows all SFRs with their address and their reset value.

### Table 3. SFR Table

|     | Bit<br>Addressable | Non Bit addressable |                     |                     |                     |                     |                     |                     |     |

|-----|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----|

|     | 0/8                | 1/9                 | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                 |     |

| F8h |                    | CH<br>0000 0000     | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAP2H<br>XXXX XXXX | CCAP3H<br>XXXX XXXX | CCAP4H<br>XXXX XXXX |                     | FFh |

| F0h | B<br>0000 0000     |                     |                     |                     |                     |                     |                     |                     | F7h |

| E8h | P5<br>1111 1111    | CL<br>0000 0000     | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAP2L<br>XXXX XXXX | CCAP3L<br>XXXX XXXX | CCAP4L<br>XXXX XXXX |                     | EFh |

| E0h | ACC<br>0000 0000   |                     |                     |                     |                     |                     |                     |                     | E7h |

| D8h | CCON<br>00X0 0000  | CMOD<br>00XX X000   | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000 | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000 |                     | DFh |

| D0h | PSW<br>0000 0000   | FCON<br>XXXX 0000   | EECON<br>XXXX XX00  | EETIM<br>0000 0000  |                     |                     |                     |                     | D7h |

| C8h | T2CON<br>0000 0000 | T2MOD<br>XXXX XX00  | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000    | TH2<br>0000 0000    |                     |                     | CFh |

| C0h | P4<br>1111 1111    |                     |                     |                     |                     |                     |                     | P5<br>1111 1111     | C7h |

| B8h | IP<br>X000 000     | SADEN<br>0000 0000  |                     |                     |                     |                     |                     |                     | BFh |

| B0h | P3<br>1111 1111    |                     |                     |                     |                     |                     |                     | IPH<br>X000 0000    | B7h |

| A8h | IE<br>0000 0000    | SADDR<br>0000 0000  |                     |                     |                     |                     |                     |                     | AFh |

| A0h | P2<br>1111 1111    |                     | AUXR1<br>XXXX 00X0  |                     |                     |                     | WDTRST<br>XXXX XXXX | WDTPRG<br>XXXX X000 | A7h |

| 98h | SCON<br>0000 0000  | SBUF<br>XXXX XXXX   |                     |                     |                     |                     |                     |                     | 9Fh |

| 90h | P1<br>1111 1111    |                     |                     |                     |                     |                     |                     |                     | 97h |

| 88h | TCON<br>0000 0000  | TMOD<br>0000 0000   | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000    | TH1<br>0000 0000    | AUXR<br>XX0X 1000   | CKCON<br>X000 0000  | 8Fh |

| 80h | P0<br>1111 1111    | SP<br>0000 0111     | DPL<br>0000 0000    | DPH<br>0000 0000    |                     |                     |                     | PCON<br>00X1 0000   | 87h |

|     | 0/8                | 1/9                 | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                 |     |

reserved

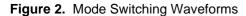

The X2 bit in the CKCON register (Table 4) allows to switch from 12 clock periods per instruction to 6 clock periods and vice versa. At reset, the standard speed is activated (STD mode). Setting this bit activates the X2 feature (X2 mode).

The T0X2, T1X2, T2X2, SiX2, PcaX2 and WdX2 bits in the CKCON register (Table 4) allow to switch from standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2 mode.

More information about the X2 mode can be found in the application note ANM072 "How to take advantage of the X2 features in TS80C51 microcontroller".

Table 4.

CKCON Register

CKCON - Clock Control Register (8Fh)

| 7             | 6               | 5                                                                                                                                                                                                                                                                    | 4                                                                                                                                                                                                                                                                         | 3    | 2    | 1    | 0  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|--|

| -             | WdX2            | PcaX2                                                                                                                                                                                                                                                                | SiX2                                                                                                                                                                                                                                                                      | T2X2 | T1X2 | T0X2 | X2 |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                           |      |      |      |    |  |

| 7             | -               | Reserved                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                           |      |      |      |    |  |

| 6             | WdX2            | X2 is low, this I<br>Clear to select                                                                                                                                                                                                                                 | Watchdog clock (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                          |      |      |      |    |  |

| 5             | PcaX2           | clock X2 is set<br>Clear to select                                                                                                                                                                                                                                   | <b>Programmable Counter Array clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |      |      |      |    |  |

| 4             | SiX2            | Enhanced UART clock (Mode 0 and 2) (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |                                                                                                                                                                                                                                                                           |      |      |      |    |  |

| 3             | T2X2            | is low, this bit h<br>Clear to select                                                                                                                                                                                                                                | <b>Timer2 clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                     |      |      |      |    |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                          |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2             | T1X2            | <b>Timer1 clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle |

| 1             | T0X2            | <b>Timer0 clock</b> (This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect)<br>Clear to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle |

| 0             | X2              | <b>CPU clock</b><br>Clear to select 12 clock periods per machine cycle (STD mode) for CPU and all the<br>peripherals.<br>Set to select 6clock periods per machine cycle (X2 mode) and to enable the<br>individual peripherals "X2" bits.             |

Reset Value = X000 0000b Not bit addressable

# 12 T89C51RD2

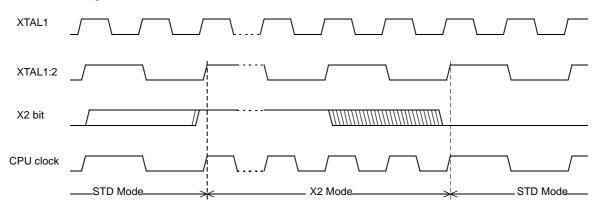

**Figure 6.** Clock-Out Mode  $C/\overline{T2} = 0$

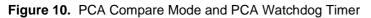

### Programmable Counter Array PCA

The PCA provides more timing capabilities with less CPU intervention than the standard timer/counters. Its advantages include reduced software overhead and improved accuracy. The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/ capture modules. Its clock input can be programmed to count any one of the following signals:

- Oscillator frequency ÷ 12 (÷ 6 in X2 mode)

- Oscillator frequency  $\div$  4 ( $\div$  2 in X2 mode)

- Timer 0 overflow

- External input on ECI (P1.2)

Each compare/capture modules can be programmed in any one of the following modes:

- rising and/or falling edge capture,

- software timer,

- high-speed output, or

- pulse width modulator.

Module 4 can also be programmed as a watchdog timer (See Section "PCA Watchdog Timer", page 32).

When the compare/capture modules are programmed in the capture mode, software timer, or high speed output mode, an interrupt can be generated when the module executes its function. All five modules plus the PCA timer overflow share one interrupt vector.

The PCA timer/counter and compare/capture modules share Port 1 for external I/O. These pins are listed below. If one or several bits in the port are not used for the PCA, they can still be used for standard I/O.

| PCA component   | External I/O Pin |

|-----------------|------------------|

| 16-bit Counter  | P1.2 / ECI       |

| 16-bit Module 0 | P1.3 / CEX0      |

| 16-bit Module 1 | P1.4 / CEX1      |

| 16-bit Module 2 | P1.5 / CEX2      |

| 16-bit Module 3 | P1.6 / CEX3      |

| 16-bit Module 4 | P1.7 / CEX4      |

**The PCA timer** is a common time base for all five modules (See Figure 7). The timer count source is determined from the CPS1 and CPS0 bits in the **CMOD SFR** (See Table 10) and can be programmed to run at:

- 1/12 the oscillator frequency. (Or 1/6 in X2 Mode)

- 1/4 the oscillator frequency. (Or 1/2 in X2 Mode)

- The Timer 0 overflow

- The input on the ECI pin (P1.2)

• The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function.

Table 13 shows the CCAPMn settings for the various PCA functions.

| CCAPM0=0DAH<br>CCAPM1=0DBH |

|----------------------------|

| CCAPM2=0DCH                |

| CCAPM3=0DDH<br>CCAPM4=0DEH |

|                            |

|             | - | ECO<br>Mn | CAPP<br>n | CAPN<br>n | MATn | TOGn | PWM<br>m | ECCF<br>n |

|-------------|---|-----------|-----------|-----------|------|------|----------|-----------|

| Reset value | Х | 0         | 0         | 0         | 0    | 0    | 0        | 0         |

| -      |                                                                                                                                                            |  |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol | Function                                                                                                                                                   |  |  |  |  |  |  |  |  |

| -      | Not implemented, reserved for future use. <sup>(1)</sup>                                                                                                   |  |  |  |  |  |  |  |  |

| ECOMn  | Enable Comparator. ECOMn = 1 enables the comparator function.                                                                                              |  |  |  |  |  |  |  |  |

| CAPPn  | Capture Positive, CAPPn = 1 enables positive edge capture.                                                                                                 |  |  |  |  |  |  |  |  |

| CAPNn  | Capture Negative, CAPNn = 1 enables negative edge capture.                                                                                                 |  |  |  |  |  |  |  |  |

| MATn   | Match. When MATn = 1, a match of the PCA counter with this module's compare/capture register causes the CCFn bit in CCON to be set, flagging an interrupt. |  |  |  |  |  |  |  |  |

| TOGn   | Toggle. When TOGn = 1, a match of the PCA counter with this module's compare/capture register causes the CEXn pin to toggle.                               |  |  |  |  |  |  |  |  |

| PWMn   | Pulse Width Modulation Mode. PWMn = 1 enables the CEXn pin to be used as a pulse width modulated output.                                                   |  |  |  |  |  |  |  |  |

| ECCFn  | Enable CCF interrupt. Enables compare/capture flag CCFn in the CCON register to generate an interrupt.                                                     |  |  |  |  |  |  |  |  |

1. User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features. In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

| Table 13. | PCA Module Modes ( | (CCAPMn Registers) |

|-----------|--------------------|--------------------|

|-----------|--------------------|--------------------|

| ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMm | ECCFn | Module Function                                   |

|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| 0     | 0     | 0     | 0    | 0    | 0    | 0     | No Operation                                      |

| х     | 1     | 0     | 0    | 0    | 0    | х     | 16-bit capture by a positive-edge trigger on CEXn |

| x     | 0     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a negative trigger on CEXn      |

| х     | 1     | 1     | 0    | 0    | 0    | х     | 16-bit capture by a transition on CEXn            |

| 1     | 0     | 0     | 1    | 0    | 0    | х     | 16-bit Software Timer / Compare mode.             |

| 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

\* Only for Module 4

Before enabling ECOM bit, CCAPnL and CCAPnH should be set with a non zero value, otherwise an unwanted match could happen. Writing to CCAPnH will set the ECOM bit.

Once ECOM set, writing CCAPnL will clear ECOM so that an unwanted match doesn't occur while modifying the compare value. Writing to CCAPnH will set ECOM. For this reason, user software should write CCAPnL first, and then CCAPnH. Of course, the ECOM bit can still be controlled by accessing to CCAPMn register.

**High Speed Output Mode** In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (See Figure 11).

A prior write must be done to CCAPnL and CCAPnH before writing the ECOMn bit.

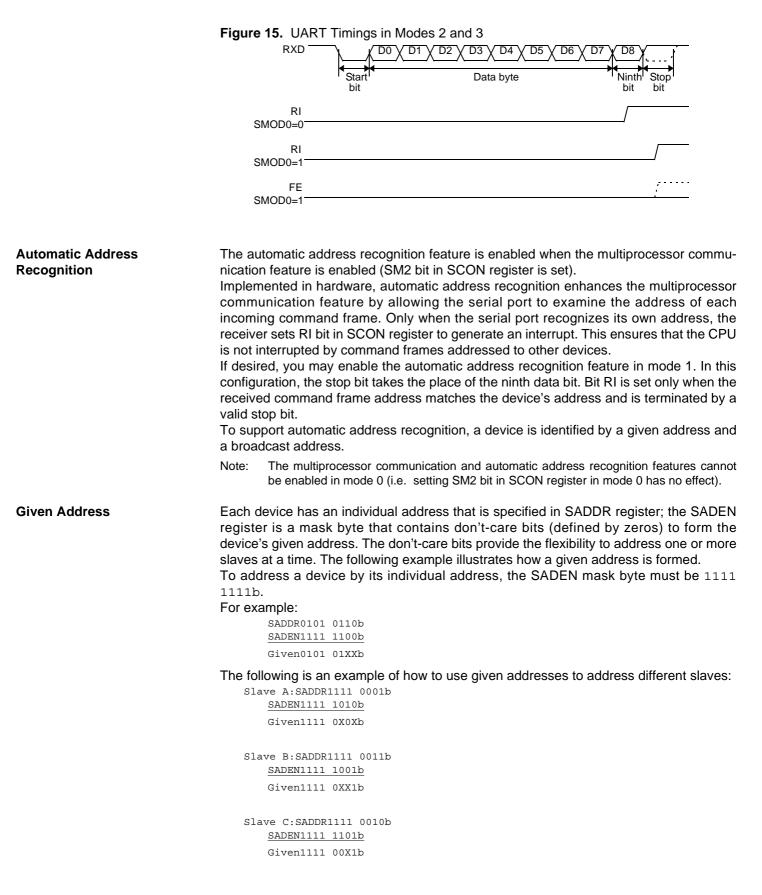

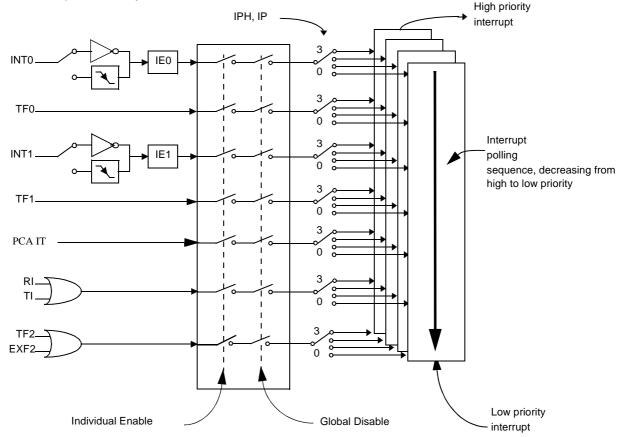

### Interrupt System

The T89C51RD2 has a total of 7 interrupt vectors: two external interrupts (INT0 and INT1), three timer interrupts (timers 0, 1 and 2), the serial port interrupt and the PCA global interrupt. These interrupts are shown in Figure 16.

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the Interrupt Enable register (See Table 23.). This register also contains a global disable bit, which must be cleared to disable all interrupts at once.

Each interrupt source can also be individually programmed to one out of four priority levels by setting or clearing a bit in the Interrupt Priority register (See Table 24.) and in the Interrupt Priority High register (See Table 22). shows the bit values and priority levels associated with each combination.

Table 22. Priority Level Bit Values

| IPH.x | IP.x | Interrupt Level Priority |

|-------|------|--------------------------|

| 0     | 0    | 0 (Lowest)               |

| 0     | 1    | 1                        |

| 1     | 0    | 2                        |

| 1     | 1    | 3 (Highest)              |

# T89C51RD2

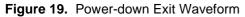

Exit from Power-down by reset redefines all the SFRs, exit from Power-down by external interrupt does no affect the SFRs.

Exit from Power-down by either reset or external interrupt does not affect the internal RAM content.

Note: If idle mode is activated with Power-down mode (IDL and PD bits set), the exit sequence is unchanged, when execution is vectored to interrupt, PD and IDL bits are cleared and idle mode is not entered.

Table 27 shows the state of ports during idle and power-down modes.

Table 27. State of Ports

| Mode       | Program Memory | ALE | PSEN | PORT0                    | PORT1     | PORT2     | PORT3     |

|------------|----------------|-----|------|--------------------------|-----------|-----------|-----------|

| Idle       | Internal       | 1   | 1    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Idle       | External       | 1   | 1    | Floating                 | Port Data | Address   | Port Data |

| Power Down | Internal       | 0   | 0    | Port Data <sup>(1)</sup> | Port Data | Port Data | Port Data |

| Power Down | External       | 0   | 0    | Floating                 | Port Data | Port Data | Port Data |

Port 0 can force a 0 level. A "one" will leave port floating.

| Bit<br>Number | Bit<br>Mnemonic | Descr                                   | iptio                                   | n                |

|---------------|-----------------|-----------------------------------------|-----------------------------------------|------------------|

| 0             | S0              | WDT -                                   | Time-                                   | out select bit 0 |

|               |                 | <u>S2</u><br>0<br>0<br>1<br>1<br>1<br>1 | <u>S1</u><br>0<br>1<br>1<br>0<br>1<br>1 |                  |

Reset value XXXX X000

WDT During Power Down and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in Power Down mode the user does not need to service the WDT. There are 2 methods of exiting Power Down mode: by a hardware reset or via a level activated external interrupt which is enabled prior to entering Power Down mode. When Power Down is exited with hardware reset, servicing the WDT should occur as it normally should whenever the T89C51RD2 is reset. Exiting Power Down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service routine.

To ensure that the WDT does not overflow within a few states of exiting of powerdown, it is best to reset the WDT just before entering powerdown.

In the Idle mode, the oscillator continues to run. To prevent the WDT from resetting the T89C51RD2 while in Idle mode, the user should always set up a timer that will periodically exit Idle, service the WDT, and re-enter Idle mode.

If the WDT is activated, the power consumption in stand-by mode will be above the specified value.

## **EEPROM Data Memory**

| General Description                 | The EEPROM memory block contains 2048 bytes and is organized in 32 pages (or rows) of 64 bytes. The necessary high programming voltage is generated on-chip using the standard Vcc pin of the microcontroller.                                                                                                                                               |  |  |  |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                     | The EEPROM memory block is located at the addresses 0000h to 07FFh of the XRAM memory space and is selected by setting control bits in the EECON register.                                                                                                                                                                                                   |  |  |  |  |

|                                     | A read in the EEPROM memory is done with a MOVX instruction.                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                                     | A physical write in the EEPROM memory is done in two steps : write data in the column latches and transfer of all data latches in a EEPROM memory row (programming).                                                                                                                                                                                         |  |  |  |  |

|                                     | The number of data written in the page may vary from 1 to 64 (the page size). When programming, only the data written in the column latch are programmed. This provides the capability to program the whole memory by bytes, by page or by a number of bytes in a page.                                                                                      |  |  |  |  |

| Write Data in the Column<br>Latches | Data is written by byte to the column latches as if it was in an external RAM memory.<br>Out of the 16 address bits of the data pointer, the 10 MSB are used for page selection<br>and 6 are used for byte selection. Between two EEPROM programming, all addresses in<br>the column latches must remain in the same page, thus the 10MSB must be unchanged. |  |  |  |  |

|                                     | The following procedure is used to write in the colums latches :                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                     | Map the program space (Set bit EEE of EECON register)                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                                     | Load DPTR with the address to write                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                     | Load A register with the data to be written                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                                     | Execute a MOVX @DPTR, A                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                     | <ul> <li>If needed loop the three last instructions until the end of a 64bytes page</li> </ul>                                                                                                                                                                                                                                                               |  |  |  |  |

| Programming                         | The EEPROM programming consists on the following actions :                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                     | • write one or more bytes in a page in the column latches. Normally, all bytes must belong to the same page; if this is not the case, the first page address is latched and the others are discarded.                                                                                                                                                        |  |  |  |  |

|                                     | <ul> <li>Set EETIM with the value corresponding to the XTAL frequency.</li> </ul>                                                                                                                                                                                                                                                                            |  |  |  |  |

|                                     | • Launch the programming by writing the control sequence (52h or 50h followed by A2h or A0h) to the EECON register (see Table 32).                                                                                                                                                                                                                           |  |  |  |  |

|                                     | • EEBUSY flag in EECON is then set by hardware to indicate that programming is in progress and that EEPROM segment is not available for read.                                                                                                                                                                                                                |  |  |  |  |

|                                     | • The end of programming is signaled by a hardware clear of the EEBUSY flag.                                                                                                                                                                                                                                                                                 |  |  |  |  |

|                                     | Example : ; DPTR = EEPROM data pointer, A = Data to write<br>Wait : MOV A, EECON                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                     | ANL A,#01h<br>JNZ Wait                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                     | MOV EETIM,#3Ch ; 12MHz*5 = 3Ch                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                                     | MOV EECON,#02h ; EEE=1 EEPROM mapped                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                     | MOVX @DPTR,A ; Write data to EEPROM                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                                     | MOV EECON, #50h or 52h ; Write Sequence                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                     | MOV EECON, #A0h or A2h                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                     | ••••                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

Table 33. EETIM Register

## EETIM (S:*0D3*h)

EEPROM timing Control Register

| 7          | 6               | 5                        | 4                               | 3 | 2                                          | 1 | 0              |  |  |

|------------|-----------------|--------------------------|---------------------------------|---|--------------------------------------------|---|----------------|--|--|

|            | EETIM           |                          |                                 |   |                                            |   |                |  |  |

| Bit Number | Bit<br>Mnemonic | Descriptio               | n                               |   |                                            |   |                |  |  |

| 7-0        | EETIM           | frequency<br>Value = 5 * | mer register v<br>Fxtal (MHz) i | · | ed to adapt the<br>e, 10 * Fxtal in<br>A5h |   | the oscillator |  |  |

Reset Value = 0000 0000b

## 52 T89C51RD2

| 7             | 6               | 5                                                                                                                                                                                                                     | 4                                                                                                                                                                                                                                                                                                                    | 3 | 2   | 1   | 0   |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|--|--|

| SB            | BLJB            | BLLB                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                                    | - | LB2 | LB1 | LB0 |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                          |   |     |     |     |  |  |

| 7             | SB              |                                                                                                                                                                                                                       | Safe Bit<br>This bit must be cleared to secure the content of the HSB. Only security level can<br>be increased.                                                                                                                                                                                                      |   |     |     |     |  |  |

| 6             | BLJB            | Boot loader Jump Bit<br>Set to force hardware boot address at 0000h. (unless previously force by hardware<br>conditions as described in the chapter 9.6).<br>Clear to force hardware boot address at FC03h (default). |                                                                                                                                                                                                                                                                                                                      |   |     |     |     |  |  |

| 5             | BLLB            | Set to allow p<br>Clear to forbid<br>(default). This                                                                                                                                                                  | Boot loader Lock Bit<br>Set to allow programming and writing of the boot loader segment.<br>Clear to forbid software programming and writing of the boot loader segment<br>(default). This protection protect only ISP or IAP access; protection through parallel<br>access is done globally by the lock bits LB2-0. |   |     |     |     |  |  |

| 4             | -               | Reserved<br>Do not clear this bit.                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                      |   |     |     |     |  |  |

| 3             | -               | Reserved<br>Do not clear this bit.                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                      |   |     |     |     |  |  |

| 2-0           | LB2-0           | User Memory<br>See Table 29                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                      |   |     |     |     |  |  |

#### Boot Loader Lock Bit (BLLB)

One bit of the HSB is used to secure by hardware the internal boot loader sector against software reprogramming.

When the BLLB is cleared, any attempt to write in the boot loader segment (Address FC00h to FFFFh) will have no effect. This protection applies for software writing only.

Boot Loader Jump Bit (BLJB)

One bit of the HSB, the BLJB bit, is used to force the boot address:

- When this bit is set the boot address is 0000h.

- When this bit is reset the boot address is FC03h. By default, this bit is cleared and the ISP is enabled.

*Flash memory lock bits* The three lock bits provide different levels of protection for the on-chip code and data, when programmed according to Table 29.

## **Functional Description**

### Configuration and Manufacturer Information

The table below lists Configuration and Manufacturer byte information used by the bootloader. This information can be accessed through a set of API or ISP commands.

| Mnemonic              | Description            | Default Value |

|-----------------------|------------------------|---------------|

| BSB                   | Boot Status Byte       | FFh           |

| SBV                   | Software Boot Vector   | FCh           |

| SSB                   | Software Security Byte | FFh           |

| Manufacturer Id       |                        | 58h           |

| Id1: Family code      |                        | D7h           |

| Id2: Product Name     |                        | FCh           |

| Id3: Product Revision |                        | FFh           |

### Software Security Bits (SSB)

The SSB protects any Flash access from ISP command. The command "Program Software Security bit" can only write a higher priority level.

There are three levels of security:

• level 0: NO\_SECURITY (FFh)

This is the default level. From level 0, one can write level 1 or level 2.

level 1: WRITE\_SECURITY (10h)

For this level it is impossible to write in the Flash memory, BSB and SBV. The Bootloader returns 'P' on write access. From level 1, one can write only level 2.

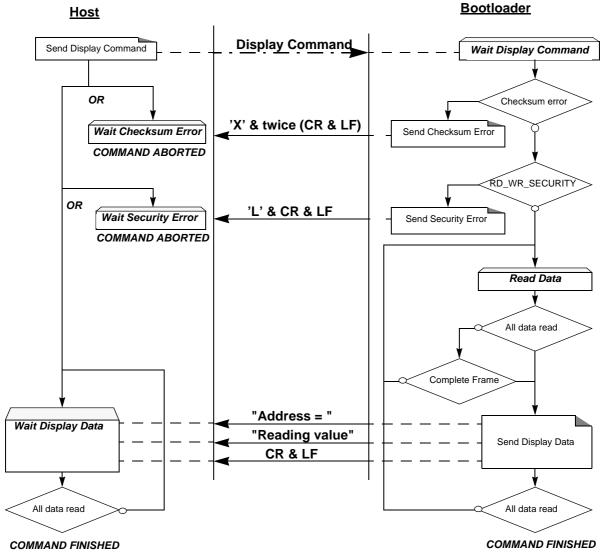

level 2: RD\_WR\_SECURITY (00h

The level 2 forbids all read and write accesses to/from the Flash/EEPROM memory. The Bootloader returns 'L' on read or write access.

Only a full chip erase in parallel mode (using a programmer) or ISP command can reset the software security bits.

From level 2, one cannot read and write anything.

|              | Level 0            | Level 1                  | Level 2                  |

|--------------|--------------------|--------------------------|--------------------------|

| Flash/EEPROM | Any access allowed | Read only access allowed | Any access not allowed   |

| Fuse Bit     | Any access allowed | Read only access allowed | Any access not allowed   |

| BSB & SBV    | Any access allowed | Read only access allowed | Any access not allowed   |

| SSB          | Any access allowed | Write level 2 allowed    | Read only access allowed |

Table 38. Software Security Byte Behavior

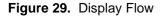

### **Display Data**

Description

Note: The maximum size of block is 400h. To read more than 400h Bytes, the Host must send a new command.

The API calls description and arguments are shown in Table 41.

### Table 41. API Call Summary

| Command              | R1  | Α                               | DPTR0                                                                | DPTR1                                                 | Returned Value         | Command Effect                                                                                                                                                                                                            |

|----------------------|-----|---------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ MANUF ID        | 00h | XXh                             | 0000h                                                                | XXh                                                   | ACC=Manufacturer<br>ID | Read Manufacturer identifier                                                                                                                                                                                              |

| READ DEVICE ID1      | 00h | XXh                             | 0001h                                                                | XXh                                                   | ACC= Device ID 1       | Read Device identifier 1                                                                                                                                                                                                  |

| READ DEVICE ID2      | 00h | XXh                             | 0002h                                                                | XXh                                                   | ACC=Device ID 2        | Read Device identifier 2                                                                                                                                                                                                  |

| READ DEVICE ID3      | 00h | XXh                             | 0003h                                                                | XXh                                                   | ACC=Device ID 3        | Read Device identifier 3                                                                                                                                                                                                  |

| PROGRAM DATA<br>BYTE | 02h | Byte value to program           | Address of<br>Byte to<br>program                                     |                                                       | ACC = 0 : DONE         | Program one Data Byte in user Flash                                                                                                                                                                                       |

| ERASE BOOT<br>VECTOR | 04h | XXh                             | XXh                                                                  | XXh                                                   | ACC=FCh                | Erase Software boot vector and boot status<br>Byte. (SBV=FCh and BSB=FFh)                                                                                                                                                 |

|                      |     |                                 | DPH = 00h<br>DPL = 00h                                               |                                                       |                        | Set SSB level 1                                                                                                                                                                                                           |

|                      | 051 | XX4                             | DPH = 00h<br>DPL = 01h                                               | 001                                                   |                        | Set SSB level 2                                                                                                                                                                                                           |

| PROGRAM SSB          | 05h | XXh                             | DPH = 00h<br>DPL = 10h                                               | 00h                                                   | ACC= SSB value         | Set SSB level 0                                                                                                                                                                                                           |

|                      |     |                                 | DPH = 00h<br>DPL = 11h                                               |                                                       |                        | Set SSB level 1                                                                                                                                                                                                           |

| PROGRAM BSB          | 06h | New BSB<br>value                | 0000h                                                                | XXh                                                   | none                   | Program boot status Byte                                                                                                                                                                                                  |

| PROGRAM SBV          | 06h | New SBV<br>value                | 0001h                                                                | XXh                                                   | none                   | Program software boot vector                                                                                                                                                                                              |

| READ SSB             | 07h | XXh                             | 0000h                                                                | XXh                                                   | ACC=SSB                | Read Software Security Byte                                                                                                                                                                                               |

| READ HSB             | 07h | XXh                             | 0004h                                                                | XXh                                                   | ACC=HSB                | Read Hardware Byte                                                                                                                                                                                                        |

| READ BSB             | 07h | XXh                             | 0001h                                                                | XXh                                                   | ACC=BSB                | Read Boot Status Byte                                                                                                                                                                                                     |

| READ SBV             | 07h | XXh                             | 0002h                                                                | XXh                                                   | ACC=SBV                | Read Software Boot Vector                                                                                                                                                                                                 |

| PROGRAM DATA<br>PAGE | 09h | Number of<br>Byte to<br>program | Address of<br>the first Byte<br>to program in<br>the Flash<br>memory | Address in<br>XRAM of the<br>first data to<br>program | ACC = 0 : DONE         | Program up to 128 Bytes in user Flash.<br>Remark: number of Bytes to program is<br>limited such as the Flash write remains in a<br>single 128 Bytes page. Hence, when ACC is<br>128, valid values of DPL are 00h, or 80h. |

| READ BOOT ID1        | 0Eh | XXh                             | DPL = 00h                                                            | XXh                                                   | ACC=ID1                | Read boot ID1                                                                                                                                                                                                             |

| READ BOOT ID2        | 0Eh | XXh                             | DPL = 01h                                                            | XXh                                                   | ACC=ID2                | Read boot ID2                                                                                                                                                                                                             |

| READ BOOT VERSION    | 0Fh | XXh                             | XXXXh                                                                | XXh                                                   | ACC=Boot_Version       | Read bootloader version                                                                                                                                                                                                   |

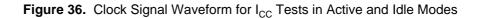

Figure 35.  $I_{CC}$  Test Condition, Power-Down Mode

All other pins are disconnected.

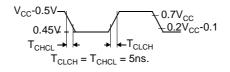

### **AC Parameters**

Explanation of the AC Symbols

Each timing symbol has 5 characters. The first character is always a "T" (stands for time). The other characters, depending on their positions, stand for the name of a signal or the logical status of that signal. The following is a list of all the characters and what they stand for.

$\begin{array}{l} \mbox{Example:} T_{AVLL} = \mbox{Time for Address Valid to ALE Low.} \\ T_{LLPL} = \mbox{Time for ALE Low to PSEN Low.} \end{array}$

$\begin{array}{l} T_{A}=0 \ to \ +70^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V\pm10\%; \ M \ range. \\ T_{A}=-40^{\circ}C \ to \ +85^{\circ}C; \ V_{SS}=0 \ V; \ V_{CC}=5 \ V\pm10\%; \ M \ range. \\ T_{A}=0 \ to \ +70^{\circ}C; \ V_{SS}=0 \ V; \ 2.7 \ V < V_{CC} < 3.3 \ V; \ L \ range. \\ T_{A}=-40^{\circ}C \ to \ +85^{\circ}C; \ V_{SS}=0 \ V; \ 2.7 \ V < V_{CC} < 3.3 \ V; \ L \ range. \end{array}$

AC characteristics of -M parts at 3 volts are similar to -L parts

(Load Capacitance for port 0, ALE and PSEN = 100 pF; Load Capacitance for all other outputs = 80 pF.)

Table 44, Table 48 and Table 50 give the description of each AC symbols.

Table 46, Table 49 and Table 51 give for each range the AC parameter.

Table 47, Table 50 and Table 52 give the frequency derating formula of the AC parameter for each speed range description. To calculate each AC symbols. take the x value in the correponding column (-M or -L) and use this value in the formula.

Example:  $T_{LLIU}$  for -M and 20 MHz, Standard clock.

x = 35 ns T = 50 ns T<sub>CCIV</sub> = 4T - x = 165 ns

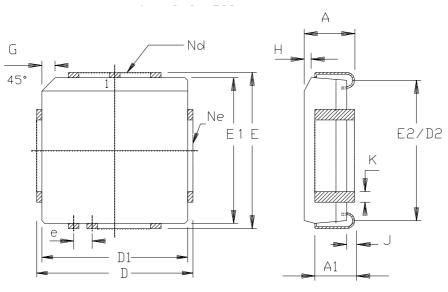

## PLCC44

|    | М     | M ·   | IN    | СН    |  |  |

|----|-------|-------|-------|-------|--|--|

| A  | 4. 20 | 4. 57 | . 165 | . 180 |  |  |

| A1 | 2. 29 | 3.04  | . 090 | . 120 |  |  |

| D  | 17.40 | 17.65 | . 685 | . 695 |  |  |

| D1 | 16.44 | 16.66 | . 647 | . 656 |  |  |

| D2 | 14.99 | 16.00 | . 590 | . 630 |  |  |

| E  | 17.40 | 17.65 | . 685 | . 695 |  |  |

| E1 | 16.44 | 16.66 | . 647 | . 656 |  |  |

| E5 | 14.99 | 16.00 | . 590 | . 630 |  |  |

| e  | 1.27  | BSC   | .050  | BSC   |  |  |

| G  | 1.07  | 1.22  | . 042 | . 048 |  |  |

| н  | 1.07  | 1.42  | . 042 | .056  |  |  |

| J  | 0.51  | -     | .020  | -     |  |  |

| К  | 0.33  | 0.53  | . 013 | . 021 |  |  |

| Nd | 1     | 1     | 1 :   | l     |  |  |

| Ne | 1     | 1     | 1 :   | l     |  |  |

|    |       |       |       |       |  |  |

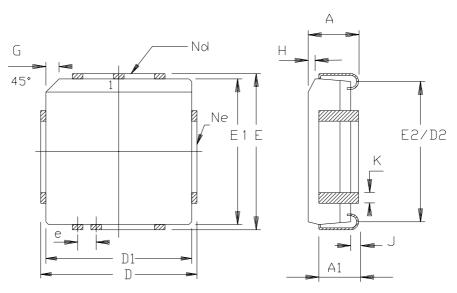

PLCC68

|    | ٢      | IM     | IN    | СН    |

|----|--------|--------|-------|-------|

| A  | 4. 20  | 5.08   | . 165 | . 200 |

| A1 | 2, 29  | 3. 30  | . 090 | . 130 |

| D  | 25. 02 | 25. 27 | . 985 | . 995 |

| D1 | 24.13  | 24. 33 | . 950 | . 958 |

| D2 | 22. 61 | 23. 62 | . 890 | . 930 |

| E  | 25. 02 | 25. 27 | . 985 | . 995 |

| E1 | 24.13  | 24. 33 | . 950 | . 958 |

| E2 | 22. 61 | 23. 62 | . 890 | . 930 |

| e  | 1.27   | BSC    | .050  | BSC   |

| G  | 1.07   | 1.22   | . 042 | . 048 |

| н  | 1.07   | 1.42   | . 042 | .056  |

| J  | 0.51   | -      | . 020 | -     |

| К  | 0.33   | 0.53   | . 013 | . 021 |

| Nd | 17     |        | 1     | 7     |

| Ne | 17     |        | 1     | 7     |

| P  | KG STD | 00     |       |       |