# E. Renesas Electronics America Inc - UPD78F0442GK-GAJ-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 46                                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | -                                                                                    |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0442gk-gaj-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.7 Outline of Functions (µPD78F044x)

|                                                         | Item                                                            | μPD78F0441                                                                                                                                                                                                                                                                                     | μPD78F0442                                   | μPD78F0443         | μPD78F0444        | μPD78F0445 |  |  |

|---------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------|-------------------|------------|--|--|

| Internal<br>memory                                      | Flash memory<br>(self-programming<br>supported) <sup>∾ote</sup> | 16 KB                                                                                                                                                                                                                                                                                          | 24 KB                                        | 32 KB              | 48 KB             | 60 KB      |  |  |

|                                                         | High-speed RAM <sup>Note</sup>                                  | 768 bytes                                                                                                                                                                                                                                                                                      | 1 KB                                         |                    |                   |            |  |  |

|                                                         | Expansion RAM <sup>Note</sup>                                   |                                                                                                                                                                                                                                                                                                | -                                            |                    | 1 KB              |            |  |  |

|                                                         | LCD display RAM                                                 | $32 \times 4$ bits (with 4                                                                                                                                                                                                                                                                     | com) or $28 \times 8$ bits                   | s (with 8 com)     |                   |            |  |  |

| Memory space                                            | e                                                               | 64 KB                                                                                                                                                                                                                                                                                          |                                              |                    |                   |            |  |  |

| Main system<br>clock<br>(oscillation                    | High-speed system<br>clock                                      | X1 (crystal/ceram<br>2 to 10 MHz: Vp<br>2 to 5 MHz: Vpp                                                                                                                                                                                                                                        | D = 2.7 to 5.5 V,                            | mal main system cl | ock input (EXCLK) |            |  |  |

| frequency)                                              | Internal high-speed oscillation clock                           | Internal oscillation<br>8 MHz (TYP.): \                                                                                                                                                                                                                                                        | n<br>/pp = 1.8 to 5.5 V                      |                    |                   |            |  |  |

| Subsystem cl<br>(oscillation fre                        |                                                                 | XT1 (crystal) osci<br>32.768 kHz (TY                                                                                                                                                                                                                                                           | llation<br>P.): V <sub>DD</sub> = 1.8 to 5.8 | 5 V                |                   |            |  |  |

| Internal low-speed oscillation clock<br>(for TMH1, WDT) |                                                                 | Internal oscillation<br>240 kHz (TYP.): V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                                                                                                         |                                              |                    |                   |            |  |  |

| General-purpose registers                               |                                                                 | 8 bits × 32 registers (8 bits × 8 registers × 4 banks)                                                                                                                                                                                                                                         |                                              |                    |                   |            |  |  |

| Minimum inst                                            | ruction execution time                                          | 0.2 $\mu$ s (high-speed system clock: @ fx <sub>H</sub> = 10 MHz operation)                                                                                                                                                                                                                    |                                              |                    |                   |            |  |  |

|                                                         |                                                                 | 0.25 $\mu$ s (internal high-speed oscillation clock: @ f <sub>RH</sub> = 8 MHz (TYP.) operation)                                                                                                                                                                                               |                                              |                    |                   |            |  |  |

|                                                         |                                                                 | 122 μs (subsystem clock: @ fsue = 32.768 kHz operation)                                                                                                                                                                                                                                        |                                              |                    |                   |            |  |  |

| Instruction se                                          | t                                                               | <ul> <li>8-bit operation and 16-bit operation</li> <li>Bit manipulate (set, reset, test, and Boolean operation)</li> <li>BCD adjust, etc.</li> </ul>                                                                                                                                           |                                              |                    |                   |            |  |  |

| I/O ports                                               |                                                                 | Total:                                                                                                                                                                                                                                                                                         |                                              | 46                 |                   |            |  |  |

|                                                         |                                                                 | CMOS I/O:                                                                                                                                                                                                                                                                                      |                                              | 42                 |                   |            |  |  |

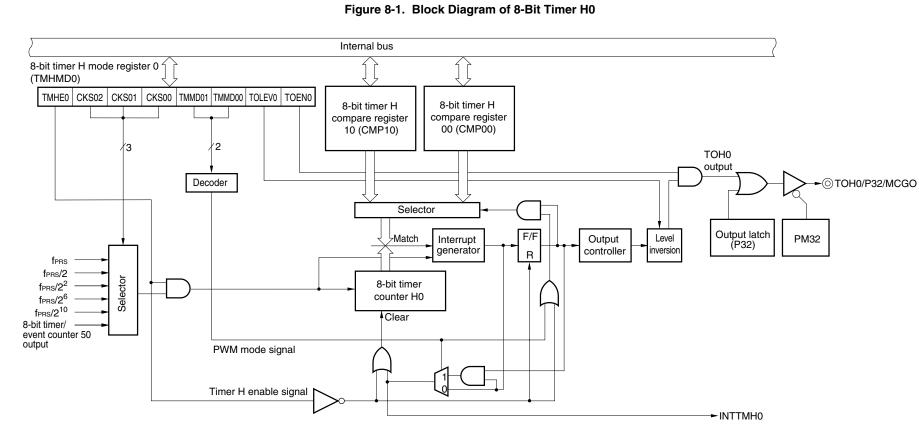

| Timers                                                  |                                                                 | CMOS input:       4         • 16-bit timer/event counter: 1 channel         • 8-bit timer/event counter: 3 channels (out of which 2 channels can perform PWM output)         • 8-bit timer: 3 channels (out of which 2 channels can perform PWM output)         • Real-time counter: 1 channel |                                              |                    |                   |            |  |  |

| Timor outputs                                           |                                                                 | Watchdog timer: 1 channel                                                                                                                                                                                                                                                                      |                                              |                    |                   |            |  |  |

|                                                         | Timer outputs                                                   | 5 (PWM output: 4 and PPG output: 1)                                                                                                                                                                                                                                                            |                                              |                    |                   |            |  |  |

|                                                         | RTC outputs                                                     | 2<br>• 1 Hz (Subsystem clock: fsuв = 32.768 kHz)<br>• 512 Hz or 16.384 kHz or 32.768 kHz (Subsystem clock: fsuв = 32.768 kHz)                                                                                                                                                                  |                                              |                    |                   |            |  |  |

| Buzzer outpu                                            | t                                                               | ,                                                                                                                                                                                                                                                                                              | kHz, 4.88 kHz, 9.7<br>ware clock: @ fprs     |                    | n)                |            |  |  |

**Note** The internal flash memory capacity, internal high-speed RAM capacity, and internal expansion RAM capacity can be changed using the internal memory size switching register (IMS) and the internal expansion RAM size switching register (IXS).

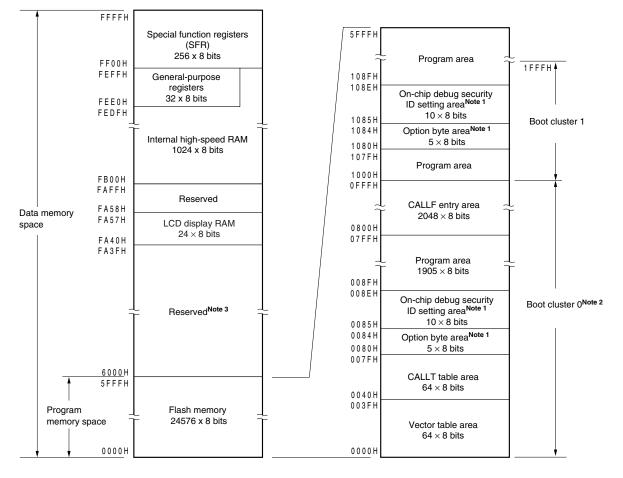

Figure 3-4. Memory Map (µPD78F0462)

When boot swap is used:

Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Setting).

- <R>

- 3. However, FA26H and FA27H can be used (See 13.3 Registers Used in 16-Bit  $\Delta\Sigma$  Type A/D Converter).

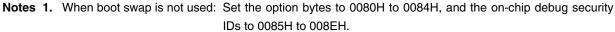

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

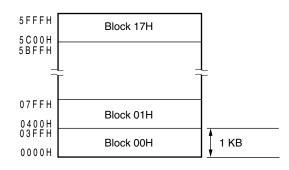

# 3.4.4 Short direct addressing

# [Function]

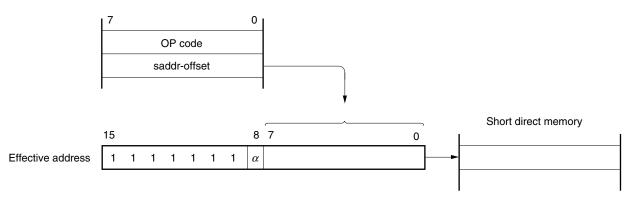

The memory to be manipulated in the fixed space is directly addressed with 8-bit data in an instruction word. This addressing is applied to the 256-byte space FE20H to FF1FH. Internal high-speed RAM and special function registers (SFRs) are mapped at FE20H to FEFFH and FF00H to FF1FH, respectively.

The SFR area (FF00H to FF1FH) where short direct addressing is applied is a part of the overall SFR area. Ports that are frequently accessed in a program and compare and capture registers of the timer/event counter are mapped in this area, allowing SFRs to be manipulated with a small number of bytes and clocks. When 8-bit immediate data is at 20H to FFH, bit 8 of an effective address is set to 0. When it is at 00H to 1FH,

bit 8 is set to 1. See the **[Illustration]** shown below.

# [Operand format]

| Identifier | Description                                                              |  |  |  |

|------------|--------------------------------------------------------------------------|--|--|--|

| saddr      | dr Immediate data that indicate label or FE20H to FF1FH                  |  |  |  |

| saddrp     | Immediate data that indicate label or FE20H to FF1FH (even address only) |  |  |  |

# [Description example]

MOV 0FE30H, A ; When transferring the value of A register to the saddr (FE30H)

# [Illustration]

When 8-bit immediate data is 20H to FFH,  $\alpha$  = 0 When 8-bit immediate data is 00H to 1FH,  $\alpha$  = 1

# (iii) Setting range when CR000 or CR010 is used as a compare register

When CR000 or CR010 is used as a compare register, set it as shown below.

| Operation                                                                    | CR000 Register Setting Range                                            | CR010 Register Setting Range                                |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------|

| Operation as interval timer                                                  | $0000H < N \le FFFFH$                                                   | $0000H^{\text{Note}} \leq M \leq \text{FFFH}$               |

| Operation as square-wave output                                              |                                                                         | Normally, this setting is not used. Mask the                |

| Operation as external event counter                                          |                                                                         | match interrupt signal (INTTM010).                          |

| Operation in the clear & start mode<br>entered by TI000 pin valid edge input | $0000H^{\text{Note}} \leq N \leq \text{FFFH}$                           | $0000H^{\text{Note}} \leq M \leq \text{FFFFH}$              |

| Operation as free-running timer                                              |                                                                         |                                                             |

| Operation as PPG output                                                      | M < N ≤ FFFFH                                                           | $0000 H^{\text{Note}} \leq M < N$                           |

| Operation as one-shot pulse output                                           | $0000H^{\text{Note}} \leq N \leq \text{FFFH} \text{ (N} \neq \text{M)}$ | $0000 H^{\text{Note}} \leq M \leq \text{FFFH} \ (M \neq N)$ |

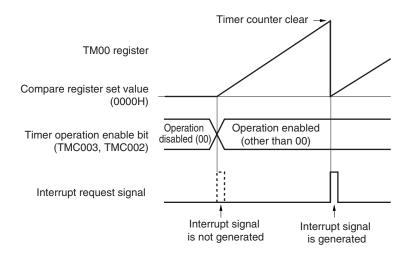

- **Note** When 0000H is set, a match interrupt immediately after the timer operation does not occur and timer output is not changed, and the first match timing is as follows. A match interrupt occurs at the timing when the timer counter (TM00 register) is changed from 0000H to 0001H.

- When the timer counter is cleared due to overflow

- When the timer counter is cleared due to TI000 pin valid edge (when clear & start mode is entered by TI000 pin valid edge input)

- When the timer counter is cleared due to compare match (when clear & start mode is entered by match between TM00 and CR000 (CR000 = other than 0000H, CR010 = 0000H))

#### Remarks 1. N: CR000 register set value, M: CR010 register set value

2. For details of TMC003 and TMC002, see 6.3 (1) 16-bit timer mode control register 00 (TMC00).

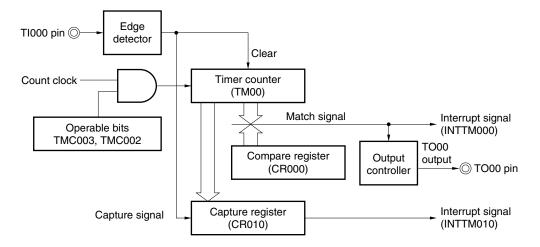

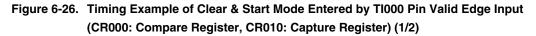

(2) Operation in clear & start mode entered by TI000 pin valid edge input (CR000: compare register, CR010: capture register)

Figure 6-25. Block Diagram of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Compare Register, CR010: Capture Register)

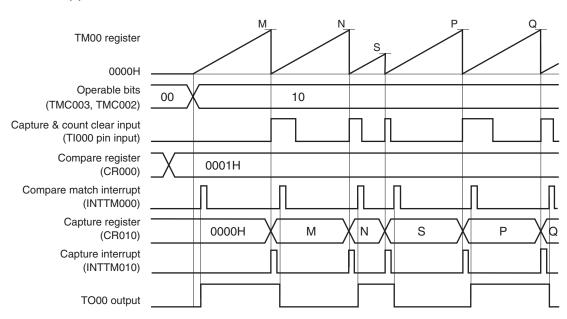

(a) TOC00 = 13H, PRM00 = 10H, CRC00, = 04H, TMC00 = 08H, CR000 = 0001H

This is an application example where the TO00 output level is inverted when the count value has been captured & cleared.

The count value is captured to CR010 and TM00 is cleared (to 0000H) when the valid edge of the TI000 pin is detected. When the count value of TM00 is 0001H, a compare match interrupt signal (INTTM000) is generated, and the TO00 output level is inverted.

# Figure 6-30. Timing Example of Clear & Start Mode Entered by TI000 Pin Valid Edge Input (CR000: Capture Register, CR010: Capture Register) (3/3)

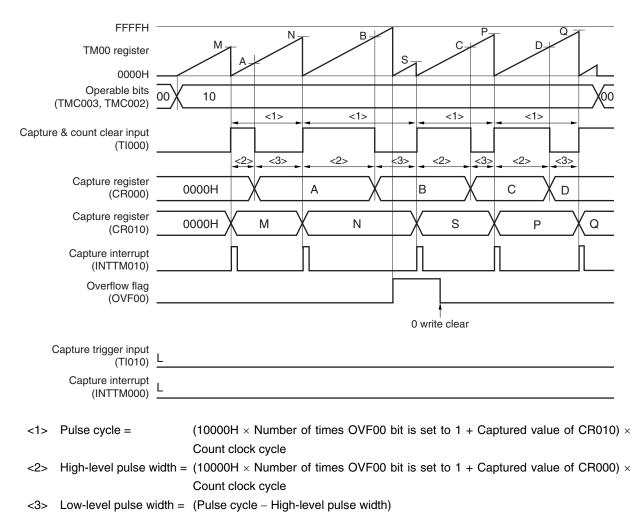

(c) TOC00 = 13H, PRM00 = 00H, CRC00 = 07H, TMC00 = 0AH

This is an application example where the pulse width of the signal input to the TI000 pin is measured.

By setting CRC00, the count value can be captured to CR000 in the phase reverse to the falling edge of the TI000 pin (i.e., rising edge) and to CR010 at the falling edge of the TI000 pin.

The high- and low-level widths of the input pulse can be calculated by the following expressions.

- High-level width = [CR010 value] [CR000 value] × [Count clock cycle]

- Low-level width = [CR000 value] × [Count clock cycle]

If the reverse phase of the TI000 pin is selected as a trigger to capture the count value to CR000, the INTTM000 signal is not generated. Read the values of CR000 and CR010 to measure the pulse width immediately after the INTTM010 signal is generated.

However, if the valid edge specified by bits 6 and 5 (ES101 and ES100) of prescaler mode register 00 (PRM00) is input to the TI010 pin, the count value is not captured but the INTTM000 signal is generated. To measure the pulse width of the TI000 pin, mask the INTTM000 signal when it is not used.

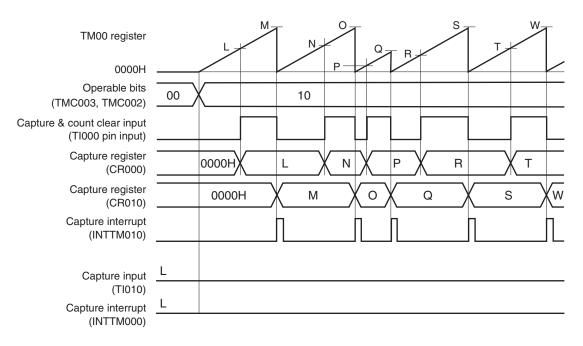

(3) Measuring the pulse width by using one input signal of the TI000 pin (clear & start mode entered by the TI000 pin valid edge input)

Set the clear & start mode entered by the TI000 pin valid edge (TMC003 and TMC002 = 10). The count value of TM00 is captured to CR000 in the phase reverse to the valid edge of the TI000 pin, and the count value of TM00 is captured to CR010 and TM00 is cleared (0000H) when the valid edge of the TI000 pin is detected. Therefore, a cycle is stored in CR010 if TM00 does not overflow.

If an overflow occurs, take the value that results from adding 10000H to the value stored in CR010 as a cycle. Clear bit 0 (OVF00) of 16-bit timer mode control register 00 (TMC00) to 0.

# Figure 6-51. Timing Example of Pulse Width Measurement (3)

# • TMC00 = 08H, PRM00 = 10H, CRC00 = 07H

# Figure 6-52. Example of Register Settings for Pulse Width Measurement (2/2)

# (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

# (f) 16-bit capture/compare register 000 (CR000)

This register is used as a capture register. Either the TI000 or TI010 pin is selected as a capture trigger. When a specified edge of the capture trigger is detected, the count value of TM00 is stored in CR000.

#### (g) 16-bit capture/compare register 010 (CR010)

This register is used as a capture register. The signal input to the TI000 pin is used as a capture trigger. When the capture trigger is detected, the count value of TM00 is stored in CR010.

User's Manual U18696EJ3V0UD

**Example:** Frequency of base clock = 2.5 MHz = 2,500,000 Hz

Set value of MDL04 to MDL00 bits of BRGC0 register = 10000B (k = 16) Target baud rate = 76,800 bps

Baud rate = 2.5 M/(2 × 16) = 2,500,000/(2 × 16) = 78,125 [bps]

Error = (78,125/76,800 - 1) × 100 = 1.725 [%]

# (3) Example of setting baud rate

| Table 14-5. | Set Data of | f Baud Rate | Generator |

|-------------|-------------|-------------|-----------|

|             |             |             |           |

| Baud          | fprs = 2.0 MHz  |    |                      | fprs = 5.0 MHz |                 |    | fprs = 10.0 MHz      |            |                 |    |                      |            |

|---------------|-----------------|----|----------------------|----------------|-----------------|----|----------------------|------------|-----------------|----|----------------------|------------|

| Rate<br>[bps] | TPS01,<br>TPS00 | k  | Calculate<br>d Value | ERR<br>[%]     | TPS01,<br>TPS00 | k  | Calculate<br>d Value | ERR<br>[%] | TPS01,<br>TPS00 | k  | Calculate<br>d Value | ERR<br>[%] |

| 1200          | ЗН              | 26 | 1202                 | 0.16           | _               | I  | -                    | -          | _               | I  | -                    | _          |

| 2400          | ЗН              | 13 | 2404                 | 0.16           | -               | -  | -                    | -          | _               | -  | -                    | -          |

| 4800          | 2H              | 26 | 4808                 | 0.16           | ЗH              | 16 | 4883                 | 1.73       | -               | -  | -                    | -          |

| 9600          | 2H              | 13 | 9615                 | 0.16           | ЗH              | 8  | 9766                 | 1.73       | ЗН              | 16 | 9766                 | 1.73       |

| 10400         | 2H              | 12 | 10417                | 0.16           | 2H              | 30 | 10417                | 0.16       | ЗН              | 15 | 10417                | 0.16       |

| 19200         | 1H              | 26 | 19231                | 0.16           | 2H              | 16 | 19531                | 1.73       | ЗН              | 8  | 19531                | 1.73       |

| 24000         | 1H              | 21 | 23810                | -0.79          | 2H              | 13 | 24038                | 0.16       | 2H              | 26 | 24038                | 0.16       |

| 31250         | 1H              | 16 | 31250                | 0              | 2H              | 10 | 31250                | 0          | 2H              | 20 | 31250                | 0          |

| 33600         | 1H              | 15 | 33333                | -0.79          | 2H              | 9  | 34722                | 3.34       | 2H              | 19 | 32895                | -2.1       |

| 38400         | 1H              | 13 | 38462                | 0.16           | 2H              | 8  | 39063                | 1.73       | 2H              | 16 | 39063                | 1.73       |

| 56000         | 1H              | 9  | 55556                | -0.79          | 1H              | 22 | 56818                | 1.46       | 2H              | 11 | 56818                | 1.46       |

| 62500         | 1H              | 8  | 62500                | 0              | 1H              | 20 | 62500                | 0          | 2H              | 10 | 62500                | 0          |

| 76800         | _               | _  | -                    | _              | 1H              | 16 | 78125                | 1.73       | 2H              | 8  | 78125                | 1.73       |

| 115200        | _               | -  | -                    | _              | 1H              | 11 | 113636               | -1.36      | 1H              | 22 | 113636               | -1.36      |

| 153600        | _               | Ι  | -                    | -              | 1H              | 8  | 156250               | 1.73       | 1H              | 16 | 156250               | 1.73       |

| 312500        | -               |    | -                    | -              | -               | -  | -                    | -          | 1H              | 8  | 312500               | 0          |

<R>

Remark TPS01, TPS00: Bits 7 and 6 of baud rate generator control register 0 (BRGC0) (setting of base clock

(fxclko))

k:

f<sub>PRS</sub>:

Value set by the MDL04 to MDL00 bits of BRGC0 (k = 8, 9, 10, ..., 31)

Peripheral hardware clock frequency

ERR: Baud rate error

# (4) Clock selection register 6 (CKSR6)

This register selects the base clock of serial interface UART6. CKSR6 can be set by an 8-bit memory manipulation instruction. Reset signal generation sets this register to 00H.

# Figure 15-8. Format of Clock Selection Register 6 (CKSR6)

Address: FF56H After reset: 00H R/W

| Symbol | 7 | 6 | 5 | 4 | 3     | 2     | 1     | 0     |

|--------|---|---|---|---|-------|-------|-------|-------|

| CKSR6  | 0 | 0 | 0 | 0 | TPS63 | TPS62 | TPS61 | TPS60 |

| TPS63 | TPS62            | TPS61 | TPS60 | Base clock (fxclk6) selection Note 1 |                             |                             |                             |                              |

|-------|------------------|-------|-------|--------------------------------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|

|       |                  |       |       |                                      | f <sub>PRS</sub> =<br>2 MHz | f <sub>PRS</sub> =<br>5 MHz | f <sub>PRS</sub> =<br>8 MHz | f <sub>PRS</sub> =<br>10 MHz |

| 0     | 0                | 0     | 0     | fprs <sup>Note 2</sup>               | 2 MHz                       | 5 MHz                       | 8 MHz                       | 10 MHz                       |

| 0     | 0                | 0     | 1     | fprs/2                               | 1 MHz                       | 2.5 MHz                     | 4 MHz                       | 5 MHz                        |

| 0     | 0                | 1     | 0     | fprs/2 <sup>2</sup>                  | 500 kHz                     | 1.25 MHz                    | 2 MHz                       | 2.5 MHz                      |

| 0     | 0                | 1     | 1     | fprs/2 <sup>3</sup>                  | 250 kHz                     | 625 kHz                     | 1 MHz                       | 1.25 MHz                     |

| 0     | 1                | 0     | 0     | fprs/2⁴                              | 125 kHz                     | 312.5 kHz                   | 500 kHz                     | 625 kHz                      |

| 0     | 1                | 0     | 1     | fprs/2⁵                              | 62.5 kHz                    | 156.25 kHz                  | 250 kHz                     | 312.5 kHz                    |

| 0     | 1                | 1     | 0     | fprs/2 <sup>6</sup>                  | 31.25 kHz                   | 78.13 kHz                   | 125 kHz                     | 156.25 kHz                   |

| 0     | 1                | 1     | 1     | fprs/27                              | 15.625 kHz                  | 39.06 kHz                   | 62.5 kHz                    | 78.13 kHz                    |

| 1     | 0                | 0     | 0     | fprs/2 <sup>8</sup>                  | 7.813 kHz                   | 19.53 kHz                   | 31.25 kHz                   | 39.06 kHz                    |

| 1     | 0                | 0     | 1     | fprs/2 <sup>9</sup>                  | 3.906 kHz                   | 9.77 kHz                    | 15.625 kHz                  | 19.53 kHz                    |

| 1     | 0                | 1     | 0     | fprs/2 <sup>10</sup>                 | 1.953 kHz                   | 4.88 kHz                    | 7.513 kHz                   | 9.77 kHz                     |

| 1     | 0                | 1     | 1     | TM50 output <sup>Note 3</sup>        |                             |                             |                             |                              |

|       | Other than above |       |       |                                      | prohibited                  |                             |                             |                              |

- **Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

- VDD = 2.7 to 5.5 V: fPRs  $\leq$  10 MHz

- VDD = 1.8 to 2.7 V: fPRs  $\leq$  5 MHz

- 2. If the peripheral hardware clock (fPRS) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V ≤ VDD < 2.7 V, the setting of TPS63 = TPS62 = TPS61 = TPS60 = 0 (base clock: fPRS) is prohibited.</p>

- 3. Note the following points when selecting the TM50 output as the base clock.

- Mode in which the count clock is cleared and started upon a match of TM50 and CR50 (TMC506 = 0) Start the operation of 8-bit timer/event counter 50 first and then enable the timer F/F inversion operation (TMC501 = 1).

- PWM mode (TMC506 = 1)

Start the operation of 8-bit timer/event counter 50 first and then set the count clock to make the duty = 50%.

It is not necessary to enable (TOE50 = 1) TO50 output in any mode.

**Remark** CKSR6 can be refreshed (the same value is written) by software during a communication operation (when bits 7 and 6 (POWER6, TXE6) of ASIM6 = 1 or bits 7 and 5 (POWER6, RXE6) of ASIM6 = 1).

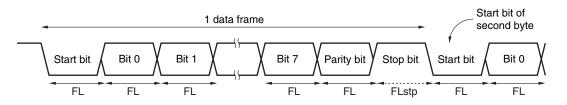

# (5) Data frame length during continuous transmission

When data is continuously transmitted, the data frame length from a stop bit to the next start bit is extended by two clocks of base clock from the normal value. However, the result of communication is not affected because the timing is initialized on the reception side when the start bit is detected.

# Figure 15-28. Data Frame Length During Continuous Transmission

Where the 1-bit data length is FL, the stop bit length is FLstp, and base clock frequency is fxclk6, the following expression is satisfied.

FLstp = FL + 2/fxclk6

Therefore, the data frame length during continuous transmission is:

Data frame length =  $11 \times FL + 2/f_{XCLK6}$

Table 17-1 lists the maximum number of pixels that can be displayed in each display mode.

#### (a) μPD78F044x, 78F045x

| LCD Driver Voltage<br>Generator                               | Bias<br>Mode | Number of<br>Time Slices | Common Signals Used | Number of<br>Segments | Maximum Number of<br>Pixels                                     |

|---------------------------------------------------------------|--------------|--------------------------|---------------------|-----------------------|-----------------------------------------------------------------|

| External resistance division     Internal resistance division | -            | Static                   | COM0 (COM1 to COM3) | 32                    | 32 (32 segment signals,<br>1 common signal) <sup>№te 2</sup>    |

|                                                               | 1/2          | 2 <sup>Note 1</sup>      | COM0, COM1          |                       | 64 (32 segment signals,<br>2 common signals) <sup>№te 3</sup>   |

|                                                               |              | 3 Note 1                 | COM0 to COM2        |                       | 96 (32 segment signals,                                         |

|                                                               | 1/3          | 3 <sup>Note 1</sup>      | COM0 to COM2        |                       | 3 common signals) <sup>№0™ 4</sup>                              |

|                                                               |              | 4 Note 1                 | COM0 to COM3        |                       | 128 (32 segment signals,<br>4 common signals) <sup>№te 5</sup>  |

|                                                               | 1/4          | 8 <sup>Note 1</sup>      | COM0 to COM7        | 28                    | 224 (28 segment signals,<br>8 common signals) <sup>Note 6</sup> |

**Notes 1.** When using the segment key scan function (KSON = 1), "number of time slices + 1" is added for segment key scan signal output.

- **2.** 4-digit LCD panel, each digit having an 8-segment  $\mathcal{B}$  configuration.

- **3.** 8-digit LCD panel, each digit having a 4-segment  $\beta$  configuration.

- **4.** 12-digit LCD panel, each digit having a 3-segment  $\mathcal{B}$  configuration.

- **5.** 16-digit LCD panel, each digit having a 2-segment  $\mathcal{B}$  configuration.

- **6.** 28-digit LCD panel, each digit having a 1-segment *B* configuration.

# (b) µPD78F046x

| LCD Driver Voltage<br>Generator                               | Bias<br>Mode | Number of<br>Time Slices | Common Signals Used | Number of Segments | Maximum Number of<br>Pixels                                    |

|---------------------------------------------------------------|--------------|--------------------------|---------------------|--------------------|----------------------------------------------------------------|

| External resistance division     Internal resistance division | -            | Static                   | COM0 (COM1 to COM3) | 24                 | 24 (24 segment signals,<br>1 common signal) <sup>№te 2</sup>   |

|                                                               | 1/2          | 2 <sup>Note 1</sup>      | COM0, COM1          |                    | 48 (24 segment signals,<br>2 common signals) <sup>№™ 3</sup>   |

|                                                               |              | 3 Note 1                 | COM0 to COM2        |                    | 72 (24 segment signals,                                        |

|                                                               | 1/3          | 3 <sup>Note 1</sup>      | COM0 to COM2        |                    | 3 common signals) <sup>№0® 4</sup>                             |

|                                                               |              | 4 Note 1                 | COM0 to COM3        |                    | 96 (24 segment signals,<br>4 common signals) <sup>№te 5</sup>  |

|                                                               | 1/4          | 8 <sup>Note 1</sup>      | COM0 to COM7        | 20                 | 160 (20 segment signals,<br>8 common signals) <sup>№te 6</sup> |

**Notes 1.** When using the segment key scan function (KSON = 1), "number of time slices + 1" is added for segment key scan signal output.

- 2. 3-digit LCD panel, each digit having an 8-segment  $\,\beta\,$  configuration.

- **3.** 6-digit LCD panel, each digit having a 4-segment  $\beta$  configuration.

- 4. 9-digit LCD panel, each digit having a 3-segment  $\mathcal{B}$  configuration.

- **5.** 12-digit LCD panel, each digit having a 2-segment  $\mathcal{B}$  configuration.

- 6. 20-digit LCD panel, each digit having a 1-segment  $\mathcal{B}$  configuration.

# (b) µPD78F046x

The segment signals correspond to 24 bytes of the LCD display data memory (FA40H to FA57H) during an LCD display period, bits 0, 1, 2, and 3 of each byte are read in synchronization with COM0, COM1, COM2, and COM3, respectively. If a bit is 1, it is converted to the select voltage, and if it is 0, it is converted to the deselect voltage. The conversion results are output to the segment pins (SEG0 to SEG23).

Furthermore, segment signals correspond to the setting values of port registers 14 and 15 during a segment key scan output period. Bits 0 to 3 and bits 4 to 7 of each port register will be read in synchronization with the first half and latter half of the segment key scan output period, respectively, and if the content of each bit is 1 or 0, high levels or low levels will be output to the segment pins (SEG16 to SEG23), respectively.

Check, with the information given above, what combination of front-surface electrodes (corresponding to the segment signals) and rear-surface electrodes (corresponding to the common signals) forms display patterns in the LCD display data memory, and write the bit data that corresponds to the desired display pattern on a one-to-one basis.

LCD display data memory bits 1 to 3, bits 2 and 3, and bit 3 are not used for LCD display in the static display, two-time slot, and three-time slot modes, respectively. So these bits can be used for purposes other than display.

The higher 4 bits of FA40H to FA43H are fixed to 0.

# CHAPTER 18 MANCHESTER CODE GENERATOR

# 18.1 Functions of Manchester Code Generator

The following three types of modes are available for the Manchester code generator.

# (1) Operation stop mode

This mode is used when output by the Manchester code generator/bit sequential buffer is not performed. This mode reduces the power consumption.

For details, refer to 18.4.1 Operation stop mode.

#### (2) Manchester code generator mode

This mode is used to transmit Manchester code from the MCGO pin. The transfer bit length can be set and transfers of various bit lengths are enabled. Also, the output level of the data transfer and LSB- or MSB-first can be set for 8-bit transfer data.

# (3) Bit sequential buffer mode

This mode is used to transmit bit sequential data from the MCGO pin. The transfer bit length can be set and transfers of various bit lengths are enabled. Also, the output level of the data transfer and LSB- or MSB-first can be set for 8-bit transfer data.

# 18.2 Configuration of Manchester Code Generator

The Manchester code generator includes the following hardware.

# Table 18-1. Configuration of Manchester Code Generator

| Item              | Configuration                                                                                                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers         | MCG transmit buffer register (MC0TX)<br>MCG transmit bit count specification register (MC0BIT)                                                                                                 |

| Control registers | MCG control register 0 (MC0CTL0)<br>MCG control register 1 (MC0CTL1)<br>MCG control register 2 (MC0CTL2)<br>MCG status register (MC0STR)<br>Port mode register 3 (PM3)<br>Port register 3 (P3) |

# (3) MCG control register 2 (MC0CTL2)

This register is used to set the transmit baud rate. This register can be set by an 8-bit memory manipulation instruction. Reset signal generation sets this register to 1FH.

# Figure 18-6. Format of MCG Control Register 2 (MC0CTL2)

| Address: FF4 | EH After re | set: 1FH | R/W |         |         |         |         |         |

|--------------|-------------|----------|-----|---------|---------|---------|---------|---------|

| Symbol       | 7           | 6        | 5   | 4       | 3       | 2       | 1       | 0       |

| MC0CTL2      | 0           | 0        | 0   | MC0BRS4 | MC0BRS3 | MC0BRS2 | MC0BRS1 | MC0BRS0 |

| MC0BRS4 | MC0BRS3 | MC0BRS2 | MC0BRS1 | MC0BRS0 | k  | Output clock selection of 5-bit counter |

|---------|---------|---------|---------|---------|----|-----------------------------------------|

| 0       | 0       | 0       | ×       | ×       | 4  | fxclk/4                                 |

| 0       | 0       | 1       | 0       | 0       | 4  | fxclk/4                                 |

| 0       | 0       | 1       | 0       | 1       | 5  | fxclk/5                                 |

| 0       | 0       | 1       | 1       | 0       | 6  | fxclк/6                                 |

| 0       | 0       | 1       | 1       | 1       | 7  | fxclk/7                                 |

| •       | •       | •       | •       | •       | •  | •                                       |

| •       | •       | •       | •       | •       | •  | •                                       |

| •       | •       | •       | •       | •       | •  | •                                       |

| •       | •       | •       | •       | •       | •  | •                                       |

| •       | •       | •       | •       | •       | ٠  | •                                       |

| 1       | 1       | 1       | 0       | 0       | 28 | fxclк/28                                |

| 1       | 1       | 1       | 0       | 1       | 29 | fxclк/29                                |

| 1       | 1       | 1       | 1       | 0       | 30 | fxclk/30                                |

| 1       | 1       | 1       | 1       | 1       | 31 | fxclk/31                                |

# Cautions 1. Clear bit 7 (MC0PWR) of the MC0CTL0 register to 0 before rewriting the MC0BRS4 to MC0BRS0 bits.

- 2. The value from further dividing the output clock of the 5-bit counter by 2 is the baud rate value.

- Remarks 1. fxcLK: Frequency of the base clock selected by the MC0CKS2 to MC0CKS0 bits of the MC0CTL1 register

- 2. k: Value set by the MC0BRS4 to MC0BRS0 bits (k = 4, 5, 6, 7, ...., 31)

- 3. ×: Don't care

# (4) MCG status register (MC0STR)

This register is used to indicate the operation status of the Manchester code generator.

This register can be read by a 1-bit or 8-bit memory manipulation instruction. Writing to this register is not possible.

Reset signal generation or setting MC0PWR = 0 clears this register to 00H.

# CHAPTER 19 REMOTE CONTROLLER RECEIVER

# **19.1 Remote Controller Receiver Functions**

The remote controller receiver uses the following remote controller modes.

- Type A reception mode ... Guide pulse (half clock) provided

- Type B reception mode ... Guide pulse (1clock) provided

- Type C reception mode ... Guide pulse not provided

# **19.2 Remote Controller Receiver Configuration**

The remote controller receiver includes the following hardware.

# Table 19-1. Remote Controller Receiver Configuration

| Item             | Configuration                                                     |

|------------------|-------------------------------------------------------------------|

| Registers        | Remote controller receive shift register (RMSR)                   |

|                  | Remote controller receive data register (RMDR)                    |

|                  | Remote controller shift register receive counter register (RMSCR) |

|                  | Remote controller receive GPLS compare register (RMGPLS)          |

|                  | Remote controller receive GPLL compare register (RMGPLL)          |

|                  | Remote controller receive GPHS compare register (RMGPHS)          |

|                  | Remote controller receive GPHL compare register (RMGPHL)          |

|                  | Remote controller receive DLS compare register (RMDLS)            |

|                  | Remote controller receive DLL compare register (RMDLL)            |

|                  | Remote controller receive DH0S compare register (RMDH0S)          |

|                  | Remote controller receive DH0L compare register (RMDH0L)          |

|                  | Remote controller receive DH1S compare register (RMDH1S)          |

|                  | Remote controller receive DH1L compare register (RMDH1L)          |

|                  | Remote controller receive end width select register (RMER)        |

| Control register | Remote controller receive interrupt status register (INTS)        |

| -                | Remote controller receive interrupt status clear register (INTC)  |

|                  | Remote controller receive control register (RMCN)                 |

<R>

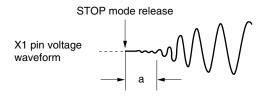

#### (2) Oscillation stabilization time select register (OSTS)

This register is used to select the X1 clock oscillation stabilization wait time when the STOP mode is released. When the X1 clock is selected as the CPU clock, the operation waits for the time set using OSTS after the STOP mode is released.

When the internal high-speed oscillation clock is selected as the CPU clock, confirm with OSTC that the desired oscillation stabilization time has elapsed after the STOP mode is released. The oscillation stabilization time can be checked up to the time set using OSTC.

OSTS can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets OSTS to 05H.

#### Figure 22-2. Format of Oscillation Stabilization Time Select Register (OSTS)

| Address: FF | A4H After | reset: 05H | R/W |   |   |       |       |       |

|-------------|-----------|------------|-----|---|---|-------|-------|-------|

| Symbol      | 7         | 6          | 5   | 4 | 3 | 2     | 1     | 0     |

| OSTS        | 0         | 0          | 0   | 0 | 0 | OSTS2 | OSTS1 | OSTS0 |

|             |           |            |     |   |   |       |       |       |

| OSTS2            | OSTS1 | OSTS0 | Oscillation stabilization time selection |                  |  |

|------------------|-------|-------|------------------------------------------|------------------|--|

|                  |       |       |                                          | fx = 10 MHz      |  |

| 0                | 0     | 1     | 2 <sup>11</sup> /fx                      | 204.8 μs         |  |

| 0                | 1     | 0     | 2 <sup>13</sup> /fx                      | 819.2 <i>μ</i> s |  |

| 0                | 1     | 1     | 2 <sup>14</sup> /fx                      | 1.64 ms          |  |

| 1                | 0     | 0     | 2 <sup>15</sup> /fx                      | 3.27 ms          |  |

| 1                | 0     | 1     | 2 <sup>16</sup> /fx                      | 6.55 ms          |  |

| Other than above |       |       | Setting prohibited                       |                  |  |

- Cautions 1. To set the STOP mode when the X1 clock is used as the CPU clock, set OSTS before executing the STOP instruction.

- 2. Do not change the value of the OSTS register during the X1 clock oscillation stabilization time.

- 3. The oscillation stabilization time counter counts up to the oscillation stabilization time set by OSTS. If the STOP mode is entered and then released while the internal high-speed oscillation clock is being used as the CPU clock, set the oscillation stabilization time as follows.

- Desired OSTC oscillation stabilization time ≤ Oscillation stabilization time set by OSTS

Note, therefore, that only the status up to the oscillation stabilization time set by OSTS is set to OSTC after STOP mode is released.

4. The X1 clock oscillation stabilization wait time does not include the time until clock oscillation starts ("a" below).

Remark fx: X1 clock oscillation frequency

|                           | Hardware                                                         | After Reset<br>Acknowledgment <sup>Note 1</sup>                |  |  |

|---------------------------|------------------------------------------------------------------|----------------------------------------------------------------|--|--|

| Program counter (P        | (C)                                                              | The contents of the reset vector table (0000H, 0001H) are set. |  |  |

| Stack pointer (SP)        |                                                                  | Undefined                                                      |  |  |

| Program status wor        | d (PSW)                                                          | 02H                                                            |  |  |

| RAM                       | Data memory                                                      | Undefined <sup>Note 2</sup>                                    |  |  |

|                           | General-purpose registers                                        | Undefined <sup>Note 2</sup>                                    |  |  |

| Port registers (P1 to     | p P4, P8, P10 to P12, P14, P15) (output latches)                 | 00H                                                            |  |  |

| Port mode registers       | ; (PM1 to PM4, PM8, PM10 to PM12, PM14, PM15)                    | FFH                                                            |  |  |

| Pull-up resistor opti     | on registers (PU1, PU3, PU4, PU8, PU10 to PU12, PU14, PU15)      | 00H                                                            |  |  |

| Port function registe     | er 1 (PF1)                                                       | 00H                                                            |  |  |

| Port function registe     | er 2 (PF2)                                                       | 00H                                                            |  |  |

| Port function registe     | 00H                                                              |                                                                |  |  |

| Internal expansion        | 0CH <sup>Note 3</sup>                                            |                                                                |  |  |

| Internal memory siz       | e switching register (IMS)                                       | CFH <sup>Note 3</sup>                                          |  |  |

| Clock operation mo        | de select register (OSCCTL)                                      | 00H                                                            |  |  |

| Processor clock cor       | ntrol register (PCC)                                             | 01H                                                            |  |  |

| Internal oscillation r    | node register (RCM)                                              | 80H                                                            |  |  |

| Main OSC control r        | egister (MOC)                                                    | 80H                                                            |  |  |

| Main clock mode re        | gister (MCM)                                                     | 00H                                                            |  |  |

| Oscillation stabilizat    | tion time counter status register (OSTC)                         | 00H                                                            |  |  |

| Oscillation stabilization | tion time select register (OSTS)                                 | 05H                                                            |  |  |

| Internal high-speed       | oscillation trimming register (HIOTRM)                           | 10H                                                            |  |  |

| 16-bit timer/event        | Timer counters 00 (TM00)                                         | 0000H                                                          |  |  |

| counters 00               | Capture/compare registers 000, 010 (CR000, CR010)                | 0000H                                                          |  |  |

|                           | Mode control registers 00 (TMC00)                                | 00H                                                            |  |  |

|                           | Prescaler mode registers 00 (PRM00)                              | 00H                                                            |  |  |

|                           | Capture/compare control registers 00 (CRC00)                     | 00H                                                            |  |  |

|                           | Timer output control registers 00 (TOC00)                        | 00H                                                            |  |  |

| 8-bit timer/event         | Timer counters 50, 51, 52 (TM50, TM51, TM52)                     | 00H                                                            |  |  |

| counters 50, 51, 52       | Compare registers 50, 51, 52 (CR50, CR51, CR52)                  | 00H                                                            |  |  |

|                           | Timer clock selection registers 50, 51, 52 (TCL50, TCL51, TCL52) | 00H                                                            |  |  |

|                           | Mode control registers 50, 51, 52 (TMC50, TMC51, TMC52)          | 00H                                                            |  |  |

# Table 23-2. Hardware Statuses After Reset Acknowledgment (1/4)

**Notes 1.** During reset signal generation or oscillation stabilization time wait, only the PC contents among the hardware statuses become undefined. All other hardware statuses remain unchanged after reset.

- 2. When a reset is executed in the standby mode, the pre-reset status is held even after reset.

- **3.** The initial values of the internal memory size switching register (IMS) and internal expansion RAM size switching register (IXS) after a reset release are constant (IMS = CFH, IXS = 0CH) in all the 78K0/LE3 products, regardless of the internal memory capacity. Therefore, after a reset is released, be sure to set the following values for each product.

| Flash Memory Version<br>(78K0/LE3) | IMS | IXS |

|------------------------------------|-----|-----|

| μPD78F0441, 78F0451, 78F0461       | 04H | 0CH |

| μPD78F0442, 78F0452, 78F0462       | C6H |     |

| µPD78F0443, 78F0453, 78F0463       | C8H |     |

| μPD78F0444, 78F0454, 78F0464       | ССН | 0AH |

| μPD78F0445, 78F0455, 78F0465       | CFH |     |

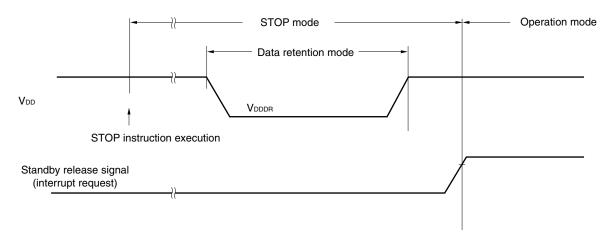

#### Standard products

#### Data Memory STOP Mode Low Supply Voltage Data Retention Characteristics (T<sub>A</sub> = -40 to +85°C)

| Parameter                     | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-------------------------------|--------|------------|----------------------|------|------|------|

| Data retention supply voltage | VDDDR  |            | 1.44 <sup>Note</sup> |      | 5.5  | V    |

# **Note** The value depends on the POC detection voltage. When the voltage drops, the data is retained until a POC reset is effected, but data is not retained when a POC reset is effected.

# Flash Memory Programming Characteristics

$(T_A = -40 \text{ to } +85^{\circ}C, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{ Vss} = \text{AVss} = 0 \text{ V})$

# Basic characteristics

| Parameter                                        |                              | Symbol | Conditions                                                        |                                                                                                                           |                                        | MIN.  | TYP. | MAX. | Unit  |

|--------------------------------------------------|------------------------------|--------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------|------|------|-------|

| VDD supply current                               |                              | lod    |                                                                   |                                                                                                                           |                                        |       | 4.5  | 11.0 | mA    |

| Erase time <sup>Note 1, 2</sup> All block Teraca |                              |        |                                                                   | 20                                                                                                                        | 200                                    | ms    |      |      |       |

|                                                  | Block unit                   | Terasa |                                                                   |                                                                                                                           |                                        |       | 20   | 200  | ms    |

| Write time (in 8-b                               | oit units) <sup>Note 1</sup> | Twrwa  |                                                                   |                                                                                                                           |                                        |       | 10   | 100  | μs    |

| Number of rewrites per chip                      |                              | Cerwr  | 1 erase + 1 write<br>after erase = 1<br>rewrite <sup>Note 3</sup> | When a flash memory<br>programmer is used, and<br>the libraries provided by<br>NEC Electronics are used                   | Retention:<br>15 years                 | 1000  |      |      | Times |

|                                                  |                              |        |                                                                   | When the EEPROM<br>emulation libraries provided<br>by NEC Electronics are<br>used, and the rewritable<br>ROM size is 4 KB | Retention:<br>3 years <sup>№te 4</sup> | 10000 |      |      | Times |

<R>

<R>

<R>

- **Notes 1.** Characteristic of the flash memory. For the characteristic when a dedicated flash programmer, PG-FP5, is used and the rewrite time during self programming, see **Tables 27-12** and **27-13**.

- 2. The prewrite time before erasure and the erase verify time (writeback time) are not included.

- 3. When a product is first written after shipment, "erase  $\rightarrow$  write" and "write only" are both taken as one rewrite.

- **4.** Data retention is guaranteed for three years after data has been written. If rewriting has been performed, data retention is guaranteed for another three years thereafter.

**Remark** fxp: Main system clock oscillation frequency