# E. Renesas Electronics America Inc - UPD78F0452GK-GAJ-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 46                                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-TQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0452gk-gaj-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

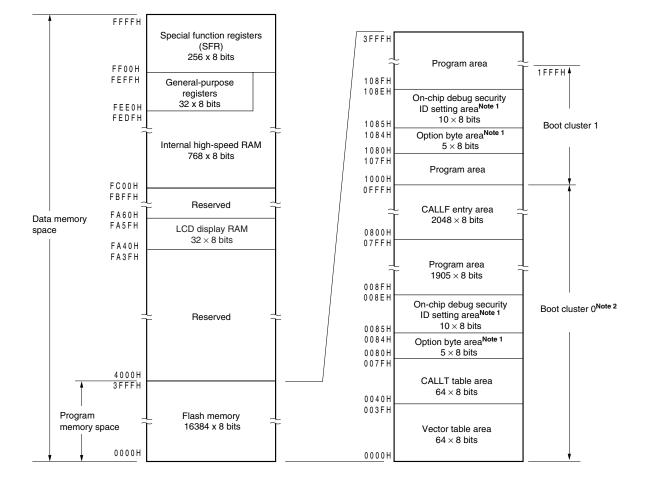

#### Figure 3-1. Memory Map (µPD78F0441, 78F0451)

**Notes 1.** When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used:

Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Setting).

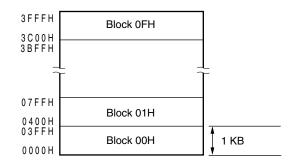

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

### (2) Processor clock control register (PCC)

This register is used to select the CPU clock, the division ratio, and operation mode for subsystem clock. PCC is set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets PCC to 01H.

| Address: FF | FBH After | reset: 01H   | $R/W^{Note 1}$                            |     |                |      |      |      |

|-------------|-----------|--------------|-------------------------------------------|-----|----------------|------|------|------|

| Symbol      | 7         | 6            | <5>                                       | <4> | 3              | 2    | 1    | 0    |

| PCC         | 0         | 0            | CLS                                       | CSS | 0              | PCC2 | PCC1 | PCC0 |

|             |           |              |                                           |     |                |      |      |      |

|             | CLS       |              |                                           | С   | PU clock stati | JS   |      |      |

|             | 0         | Main system  | l clock                                   |     |                |      |      |      |

|             | 1         | Subsystem of | Subsystem clock                           |     |                |      |      |      |

|             |           |              |                                           |     |                |      |      |      |

|             | CSS       | PCC2         | PCC2 PCC1 PCC0 CPU clock (fcpu) selection |     |                |      |      |      |

| Figure 5-3. | Format of | Processor | Clock | Control | Register | (PCC) |

|-------------|-----------|-----------|-------|---------|----------|-------|

|-------------|-----------|-----------|-------|---------|----------|-------|

| CSS | PCC2      | PCC1     | PCC0 | CPU clock (fcPu) selection |

|-----|-----------|----------|------|----------------------------|

| 0   | 0         | 0        | 0    | fxp                        |

|     | 0         | 0        | 1    | fxp/2 (default)            |

|     | 0         | 1        | 0    | fxp/2 <sup>2</sup>         |

|     | 0         | 1        | 1    | fxp/2 <sup>3</sup>         |

|     | 1         | 0        | 0    | fxp/2 <sup>4</sup>         |

| 1   | 0         | 0        | 0    | fsub/2                     |

|     | 0         | 0        | 1    |                            |

|     | 0         | 1        | 0    |                            |

|     | 0         | 1        | 1    |                            |

|     | 1         | 0        | 0    |                            |

|     | Other the | an above |      | Setting prohibited         |

Note Bit 5 is read-only.

Caution Be sure to clear bits 3, 6, and 7 to "0".

Remarks 1. fxp: Main system clock oscillation frequency

2. fsub: Subsystem clock oscillation frequency

The fastest instruction can be executed in 2 clocks of the CPU clock in the 78K0/LE3. Therefore, the relationship between the CPU clock (fcPu) and the minimum instruction execution time is as shown in Table 5-2.

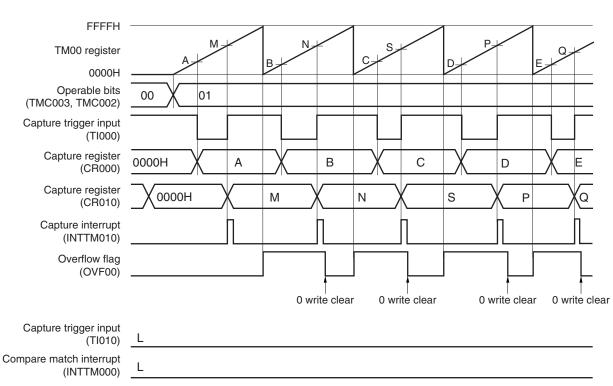

#### (2) Measuring the pulse width by using one input signal of the TI000 pin (free-running mode)

Set the free-running timer mode (TMC003 and TMC002 = 01). The count value of TM00 is captured to CR000 in the phase reverse to the valid edge detected on the Tl000 pin. When the valid edge of the Tl000 pin is detected, the count value of TM00 is captured to CR010.

By this measurement method, values are stored in separate capture registers when a width from one edge to another is measured. Therefore, the capture values do not have to be saved. By subtracting the value of one capture register from that of another, a high-level width, low-level width, and cycle are calculated.

If an overflow occurs, the value becomes negative if one captured value is simply subtracted from another and, therefore, a borrow occurs (bit 0 (CY) of the program status word (PSW) is set to 1). If this happens, ignore CY and take the calculated value as the pulse width. In addition, clear bit 0 (OVF00) of 16-bit timer mode control register 00 (TMC00) to 0.

#### Figure 6-50. Timing Example of Pulse Width Measurement (2)

• TMC00 = 04H, PRM00 = 10H, CRC00 = 07H

#### (2) Cautions for input enable control for TI52 pin

The input enable control signal (TMH2 output signal) for the TI52 pin is synchronized by the TI52 pin input clock, as described in Figure 6-54 Configuration Diagram of External 24-bit Event Counter and Figure 6-55 Operation Timing of External 24-bit Event Counter. Thus, when the counter is operated as an external event counter, an error up to one count may be caused.

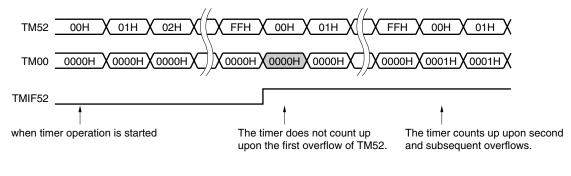

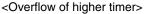

#### (3) Cautions for 16-bit timer/event counter 00 count up during external 24-bit event counter operation

16-bit timer/event counter 00 has an internal synchronization circuit to eliminate noise when starting operation, and the first clock immediately after operation start is not counted.

When using the counter as a 24-bit counter, by setting 16-bit timer/event counter 00 and 8-bit timer/event counter 52 as the higher and lower timer and connecting them in cascade, the interrupt request flag of 8-bit timer/event counter 52 which is the lower timer must be checked as described below, in order to accurately read the 24-bit count values.

- If TMIF52 = 1 when TM52 and TM00 are read:

The actual TM00 count value is "read value of TM00 + 1".

- If TMIF52 = 0 when TM52 and TM00 are read:

The read value is the correct value.

This phenomenon of 16-bit timer/event counter 00 occurs only when operation is started. A count delay will not occur when 16-bit timer/event counter 00 overflows and the count is restarted from 0000H, since synchronization has already been implemented.

<When starting operation>

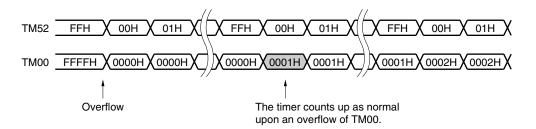

#### <R> (12) Reading of 16-bit timer counter 00 (TM00)

TM00 can be read without stopping the actual counter, because the count values captured to the buffer are fixed when it is read. The buffer, however, may not be updated when it is read immediately before the counter counts up, because the buffer is updated at the timing the counter counts up.

#### Figure 6-62. 16-bit Timer Counter 00 (TM00) Read Timing

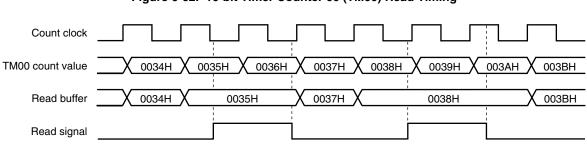

#### 7.4 Operations of 8-Bit Timer/Event Counters 50, 51, and 52

#### 7.4.1 Operation as interval timer

8-bit timer/event counter 5n operates as an interval timer that generates interrupt requests repeatedly at intervals of the count value preset to 8-bit timer compare register 5n (CR5n).

When the count value of 8-bit timer counter 5n (TM5n) matches the value set to CR5n, counting continues with the TM5n value cleared to 0 and an interrupt request signal (INTTM5n) is generated.

The count clock of TM5n can be selected with bits 0 to 2 (TCL5n0 to TCL5n2) of timer clock selection register 5n (TCL5n).

#### Setting

- <1> Set the registers.

- TCL5n: Select the count clock.

- CR5n: Compare value

- TMC5n: Stop the count operation, select the mode in which clear & start occurs on a match of TM5n and CR5n.

$(TMC5n = 0000 \times \times \times 0B \times = Don't care)$

- <2> After TCE5n = 1 is set, the count operation starts.

- <3> If the values of TM5n and CR5n match, INTTM5n is generated (TM5n is cleared to 00H).

- <4> INTTM5n is generated repeatedly at the same interval.

Set TCE5n to 0 to stop the count operation.

#### Caution Do not write other values to CR5n during operation.

**Remarks 1.** For how to enable the INTTM5n signal interrupt, see **CHAPTER 20 INTERRUPT FUNCTIONS**. **2.** n = 0 to 2

#### Figure 7-15. Interval Timer Operation Timing (1/2)

(a) Basic operation

**Remark** Interval time =  $(N + 1) \times t$ N = 01H to FFH n = 0 to 2

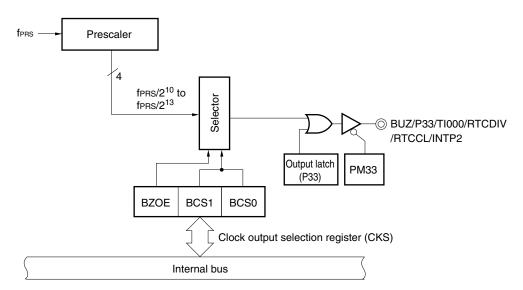

## CHAPTER 11 BUZZER OUTPUT CONTROLLER

## **11.1 Functions of Buzzer Output Controller**

The buzzer output is intended for square-wave output of buzzer frequency selected with CKS. Figure 11-1 shows the block diagram of buzzer output controller.

The setting methods are described below.

- <1> Set bit 0 (ADCE) of the A/D converter mode register (ADM) to 1.

- <2> Set the channel to be used in the analog input mode by using bits 3 to 0 (ADPC03 to ADPC00) of the A/D port configuration register 0 (ADPC0) and bits 7 to 0 (PM27 to PM20) of port mode register 2 (PM2).

- <3> Select conversion time by using bits 6 to 1 (FR3 to FR0, LV1, and LV0) of ADM.

- <4> Select a channel to be used by using bits 2 to 0 (ADS2 to ADS0) of the analog input channel specification register (ADS).

- <5> Set bit 7 (ADCS) of ADM to 1 to start A/D conversion.

- <6> When one A/D conversion has been completed, an interrupt request signal (INTAD) is generated.

- <7> Transfer the A/D conversion data to the A/D conversion result register (ADCR, ADCRH).

<Change the channel>

- <8> Change the channel using bits 2 to 0 (ADS2 to ADS0) of ADS to start A/D conversion.

- <9> When one A/D conversion has been completed, an interrupt request signal (INTAD) is generated.

<10> Transfer the A/D conversion data to the A/D conversion result register (ADCR, ADCRH).

<Complete A/D conversion>

<11> Clear ADCS to 0.

<12> Clear ADCE to 0.

#### Cautions 1. Make sure the period of <1> to <5> is 1 $\mu$ s or more.

- 2. <1> may be done between <2> and <4>.

- 3. <1> can be omitted. However, ignore data of the first conversion after <5> in this case.

- 4. The period from <6> to <9> differs from the conversion time set using bits 6 to 1 (FR3 to FR0, LV1, LV0) of ADM. The period from <8> to <9> is the conversion time set using FR3 to FR0, LV1, and LV0.

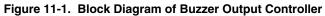

Figure 16-8. Output Operation of First Bit (2/2)

The first bit is directly latched by the SOTB10 register at the falling edge of the write signal of the SOTB10 register or the read signal of the SIO10 register, and output from the SO10 pin via an output selector. Then, the value of the SOTB10 register is transferred to the SIO10 register at the next falling (or rising) edge of SCK10, and shifted one bit. At the same time, the first bit of the receive data is stored in the SIO10 register via the SI10 pin. The second and subsequent bits are latched by the SIO10 register to the output latch at the next rising (or falling) edge of SCK10, and the data is output from the SO10 pin.

## (2) LCD display mode register (LCDM)

LCDM specifies whether to enable display operation. It also specifies whether to enable segment pin/common pin output, gate booster circuit control, and the display mode. LCDM is set using a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets LCDM to 00H.

#### Figure 17-3. Format of LCD Display Mode Register

| Address | s: FFB1H | After reset: 00H | R/W |      |   |       |       |       |   |

|---------|----------|------------------|-----|------|---|-------|-------|-------|---|

| Symbol  | <7>      | <6>              | 5   | <4>  | 3 | 2     | 1     | 0     | _ |

| LCDM    | LCDON    | SCOC             | 0   | VAON | 0 | LCDM2 | LCDM1 | LCDM0 | 1 |

| LCDON | LCD display enable/disable                       |  |  |

|-------|--------------------------------------------------|--|--|

| 0     | isplay off (all segment outputs are deselected.) |  |  |

| 1     | Display on                                       |  |  |

|   | SCOC                                                                  | Segment pin/common pin output control <sup>Note 1</sup> |  |  |

|---|-----------------------------------------------------------------------|---------------------------------------------------------|--|--|

| I | 0                                                                     | Dutput ground level to segment/common pin               |  |  |

| l | 1 Output deselect level to segment pin and LCD waveform to common pin |                                                         |  |  |

| VAON | Gate booster circuit control <sup>Notes 1, 2</sup> |  |

|------|----------------------------------------------------|--|

| 0    | lo gate voltage boosting                           |  |

| 1    | Gate voltage boosting                              |  |

| LCDM2            | LCDM1 | LCDM0 | LCD controller/driver display mode selection |                |

|------------------|-------|-------|----------------------------------------------|----------------|

|                  |       |       | Resistance d                                 | ivision method |

|                  |       |       | Number of time slices                        | Bias mode      |

| 1                | 1     | 1     |                                              | 1/4 Note 4     |

| 0                | 0     | 0     | 4 Note 3                                     | 1/3            |

| 0                | 0     | 1     | 3 Note 3                                     | 1/3            |

| 0                | 1     | 0     | 2 <sup>Note 3</sup>                          | 1/2            |

| 0                | 1     | 1     | 3 Note 3                                     | 1/2            |

| 1                | 0     | 0     | Static                                       |                |

| Other than above | e     |       | Setting prohibited                           |                |

(Note and Caution are listed on the next page.)

## (3) LCD clock control register (LCDC0)

LCDC0 specifies the LCD source clock and LCD clock. The frame frequency is determined according to the LCD clock and the number of time slices. LCDC0 is set using a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets LCDC0 to 00H.

#### Figure 17-4. Format of LCD Clock Control Register

| Address | s: FFB2H | After reset: 00H | I R/W |       |   |       |       |       |   |

|---------|----------|------------------|-------|-------|---|-------|-------|-------|---|

| Symbol  | 7        | 6                | 5     | 4     | 3 | 2     | 1     | 0     | _ |

| LCDC0   | 0        | LCDC6            | LCDC5 | LCDC4 | 0 | LCDC2 | LCDC1 | LCDC0 | ĺ |

| LCDC6          | LCDC5            | LCDC4 | LCD source clock (fLCD) selection |

|----------------|------------------|-------|-----------------------------------|

| 0              | 0                | 0     | fхт (32.768 kHz)                  |

| 0              | 0                | 1     | fprs/2 <sup>6</sup>               |

| 0              | 1                | 0     | fprs/2 <sup>7</sup>               |

| 0              | 1                | 1     | fprs/2 <sup>8</sup>               |

| 1              | 0                | 0     | f <sub>RL</sub> /2 <sup>3</sup>   |

| Other than abo | Other than above |       | Setting prohibited                |

| LCDC2          | LCDC1            | LCDC0 | LCD clock (LCDCL) selection |

|----------------|------------------|-------|-----------------------------|

| 0              | 0                | 0     | fLCD/2 <sup>4</sup>         |

| 0              | 0                | 1     | fLCD/2 <sup>5</sup>         |

| 0              | 1                | 0     | fLCD/2 <sup>6</sup>         |

| 0              | 1                | 1     | flcd/2 <sup>7</sup>         |

| 1              | 0                | 0     | fLCD/2 <sup>8</sup>         |

| 1              | 0                | 1     | fLCD/2º                     |

| Other than abo | Other than above |       | Setting prohibited          |

#### Caution Bits 3 and 7 must be set to 0.

- Remarks 1. fxT: XT1 clock oscillation frequency

- 2. fPRS: Peripheral hardware clock frequency

- 3. fr.L: Internal low-speed oscillation clock frequency

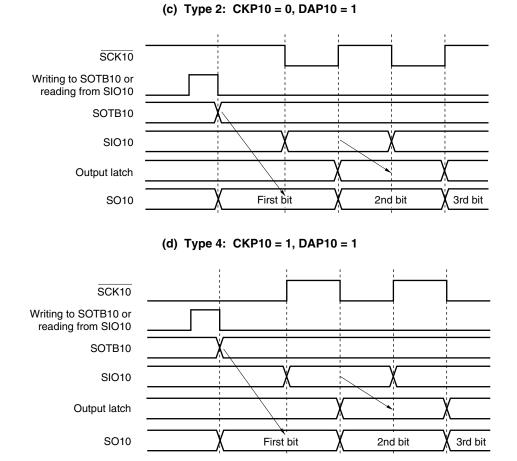

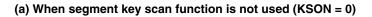

#### 17.7.2 Two-time-slice display example

Figure 17-21 shows how the 6-digit LCD panel having the display pattern shown in Figure 17-20 is connected to the segment signals (SEG0 to SEG23) and the common signals (COM0 and COM1) of the 78K0/LE3 chip. This example displays data "12345.6" in the LCD panel. The contents of the display data memory (FA40H to FA57H) correspond to this display.

The following description focuses on numeral "3" ( $\exists$ ) displayed in the fourth digit. To display "3" in the LCD panel, it is necessary to apply the select or deselect voltage to the SEG12 to SEG15 pins according to Table 17-7 at the timing of the common signals COM0 and COM1; see Figure 17-20 for the relationship between the segment signals and LCD segments.

| Segment | SEG12    | SEG13  | SEG14    | SEG15    |

|---------|----------|--------|----------|----------|

| Common  |          |        |          |          |

| COM0    | Select   | Select | Deselect | Deselect |

| COM1    | Deselect | Select | Select   | Select   |

Table 17-7. Select and Deselect Voltages (COM0 and COM1)

According to Table 17-7, it is determined that the display data memory location (FA4FH) that corresponds to SEG15 must contain xx10.

Figure 17-22 shows examples of LCD drive waveforms between the SEG15 signal and each common signal. When the select voltage is applied to SEG15 at the timing of COM1, an alternate rectangle waveform,  $+V_{LCD}/-V_{LCD}$ , is generated to turn on the corresponding LCD segment.

COM1

**Remark** n = 0 to 5

## Figure 17-22. Two-Time-Slice LCD Drive Waveform Examples (1/2 Bias Method)

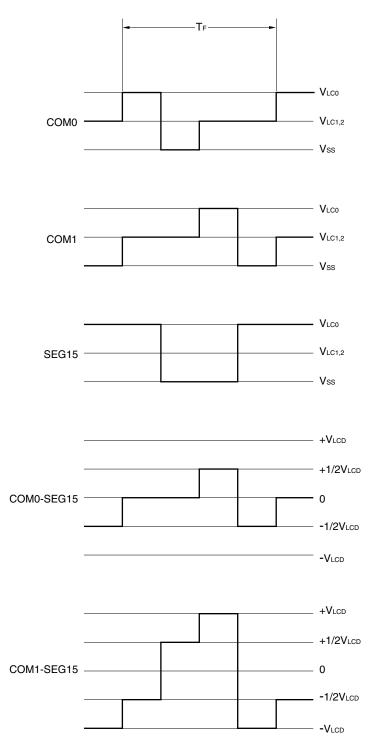

# Figure 24-2. Timing of Generation of Internal Reset Signal by Power-on-Clear Circuit and Low-Voltage Detector (1/2)

#### (1) In 1.59 V POC mode (option byte: POCMODE = 0)

- Notes 1. The operation guaranteed range is 1.8 V ≤ V<sub>DD</sub> ≤ 5.5 V. To make the state at lower than 1.8 V reset state when the supply voltage falls, use the reset function of the low-voltage detector, or input the low level to the RESET pin.

- If the voltage rises to 1.8 V at a rate slower than 0.5 V/ms (MIN.) on power application, input a low level to the RESET pin after power application and before the voltage reaches 1.8 V, or set the 2.7 V/1.59 V POC mode by using an option byte (POCMODE = 1).

- **3.** The internal voltage stabilization time includes the oscillation accuracy stabilization time of the internal high-speed oscillation clock.

- 4. The internal high-speed oscillation clock and a high-speed system clock or subsystem clock can be selected as the CPU clock. To use the X1 clock, use the OSTC register to confirm the lapse of the oscillation stabilization time. To use the XT1 clock, use the timer function for confirmation of the lapse of the stabilization time.

- Caution Set the low-voltage detector by software after the reset status is released (see CHAPTER 25 LOW-VOLTAGE DETECTOR).

- Remark

VLVI:

LVI detection voltage

VPOC:

POC detection voltage

#### 27.3 Writing with Flash memory programmer

Data can be written to the flash memory on-board or off-board, by using a dedicated flash memory programmer.

#### (1) On-board programming

The contents of the flash memory can be rewritten after the 78K0/LE3 has been mounted on the target system. The connectors that connect the dedicated flash memory programmer must be mounted on the target system.

#### (2) Off-board programming

Data can be written to the flash memory with a dedicated program adapter (FA series) before the 78K0/LE3 is mounted on the target system.

**Remark** The FA series is a product of Naito Densei Machida Mfg. Co., Ltd.

#### Table 27-3. Wiring Between 78K0/LE3 and Dedicated Flash memory programmer

| Pin Configuration of Dedicated Flash memory programmer |        |                         | With CSI10                       | )       | With UART6              |         |  |

|--------------------------------------------------------|--------|-------------------------|----------------------------------|---------|-------------------------|---------|--|

| Signal Name                                            | I/O    | Pin Function            | Pin Name                         | Pin No. | Pin Name                | Pin No. |  |

| SI/RxD                                                 | Input  | Receive signal          | SO10/TxD0<br>/ <txd6>/P13</txd6> | 62      | TxD6/SEG14/P112         | 28      |  |

| SO/TxD                                                 | Output | Transmit signal         | SI10/RxD0<br>/ <rxd6>/P12</rxd6> | 63      | RxD6/SEG15/P113         | 27      |  |

| SCK                                                    | Output | Transfer clock          | SCK10/P11                        | 64      | -                       | -       |  |

| CLK                                                    | Output | Clock to 78K0/LE3       | _Note 1                          | -       | Note 2                  | Note 2  |  |

| /RESET                                                 | Output | Reset signal            | RESET                            | 10      | RESET                   | 10      |  |

| FLMD0                                                  | Output | Mode signal             | FLMD0                            | 13      | FLMD0                   | 13      |  |

| VDD                                                    | I/O    | VDD voltage generation/ | VDD                              | 18      | VDD                     | 18      |  |

|                                                        |        | power monitoring        | VDD <sup>Note 3</sup>            | 47      | VDD <sup>Note 3</sup>   | 47      |  |

|                                                        |        |                         | AVREF <sup>Note 4</sup>          |         | AVREF <sup>Note 4</sup> |         |  |

| GND                                                    | -      | Ground                  | Vss                              | 17      | Vss                     | 17      |  |

|                                                        |        |                         | Vss <sup>Note 3</sup>            | 48      | Vss <sup>Note 3</sup>   | 48      |  |

|                                                        |        |                         | AVss <sup>Note 4</sup>           | 1       | AVss <sup>Note 4</sup>  |         |  |

Notes 1. Only the internal high-speed oscillation clock (fRH) can be used when CSI10 is used.

2. Only the X1 clock (fx), external main system clock (fexcLk), or internal high-speed oscillation clock (fRH) can be used when UART6 is used. When using the clock output of the dedicated flash memory programmer, connect CLK of the PG-FP5 or FL-PR5 to EXCLK/X2/P122 (pin number 14).

**3.** *μ*PD78F044x only.

**4.** *μ*PD78F045x and 78F046x only.

<R>

<R>

Caution Only the bottom side pins (pin numbers 27 and 28) correspond to the UART6 pins (RxD6 and TxD6) when writing by a flash memory programmer. Writing cannot be performed by the top side pins (pin numbers 63 and 62).

#### 27.7.4 Communication commands

The 78K0/LE3 communicates with the dedicated flash memory programmer by using commands. The signals sent from the flash memory programmer to the 78K0/LE3 are called commands, and the signals sent from the 78K0/LE3 to the dedicated flash memory programmer are called response.

Figure 27-14. Communication Commands

The flash memory control commands of the 78K0/LE3 are listed in the table below. All these commands are issued from the programmer and the 78K0/LE3 perform processing corresponding to the respective commands.

| Classification      | Command Name              | Function                                                                                                 |

|---------------------|---------------------------|----------------------------------------------------------------------------------------------------------|

| Verify              | Verify                    | Compares the contents of a specified area of the flash memory with data transmitted from the programmer. |

| Erase               | Chip Erase                | Erases the entire flash memory.                                                                          |

|                     | Block Erase               | Erases a specified area in the flash memory.                                                             |

| Blank check         | Block Blank Check         | Checks if a specified block in the flash memory has been correctly erased.                               |

| Write               | Programming               | Writes data to a specified area in the flash memory.                                                     |

| Getting information | Status                    | Gets the current operating status (status data).                                                         |

|                     | Silicon Signature         | Gets 78K0/Lx3 information (such as the part number and flash memory configuration).                      |

|                     | Version Get               | Gets the 78K0/Lx3 version and firmware version.                                                          |

|                     | Checksum                  | Gets the checksum data for a specified area.                                                             |

| Security            | Security Set              | Sets security information.                                                                               |

| Others              | Reset                     | Used to detect synchronization status of communication.                                                  |

|                     | Oscillating Frequency Set | Specifies an oscillation frequency.                                                                      |

Table 27-8. Flash Memory Control Commands

The 78K0/LE3 return a response for the command issued by the dedicated flash memory programmer. The response names sent from the 78K0/LE3 are listed below.

#### Table 27-9. Response Names

| Response Name | Function                           |

|---------------|------------------------------------|

| ACK           | Acknowledges command/data.         |

| NAK           | Acknowledges illegal command/data. |

memory programmer

| Function Name              | Interrupt Response Time (µs)     |                    |                          |                                                 |                             |                          |  |  |

|----------------------------|----------------------------------|--------------------|--------------------------|-------------------------------------------------|-----------------------------|--------------------------|--|--|

|                            | When entry RA                    | M is allocated out | side short direct        | When entry RAM is allocated within short direct |                             |                          |  |  |

|                            |                                  | addressing range   |                          |                                                 | addressing range            |                          |  |  |

|                            | RSTOP = 0 a                      | and RSTS = 1       | RSTOP = 1                | RSTOP = 0 a                                     | RSTOP = 1                   |                          |  |  |

|                            | (during stable                   | e operation of     | (internal                | (during stable                                  | (during stable operation of |                          |  |  |

|                            | internal high-sp                 | peed oscillator)   | high-speed               | internal high-s                                 | peed oscillator)            | high-speed               |  |  |

|                            |                                  |                    | oscillator               |                                                 |                             | oscillator               |  |  |

|                            |                                  |                    | stopped) <sup>Note</sup> |                                                 |                             | stopped) <sup>Note</sup> |  |  |

|                            | MCS = 0                          | MCS = 1            | MCS = 1                  | MCS = 0                                         | MCS = 1                     | MCS = 1                  |  |  |

|                            | (CPU operates with internal with |                    | (CPU operates            | (CPU operates                                   | (CPU operates               | (CPU operates            |  |  |

|                            |                                  |                    | with                     | with internal                                   | with                        | with                     |  |  |

|                            | high-speed                       | high-speed         | high-speed               | high-speed                                      | high-speed                  | high-speed               |  |  |

|                            | oscillation                      | system clock)      | system clock)            | oscillation                                     | system clock)               | system clock)            |  |  |

|                            | clock)                           |                    |                          | clock)                                          |                             |                          |  |  |

| Block erase function       | 136/fcpu+1269                    | 136/fcpu+1269      | 136/fcpu+1912            | 136/fcpu+703                                    | 136/fcpu+703                | 136/fcpu+713             |  |  |

| Word write function        | 272/fcpu+1098                    | 272/fcpu+1098      | 272/fcpu+1742            | 272/fcpu+533                                    | 272/fcpu+533                | 272/fcpu+543             |  |  |

| Block verify function      | 136/fcpu+1013                    | 136/fcpu+1013      | 136/fcpu+1656            | 136/fcpu+448                                    | 136/fcpu+448                | 136/fcpu+456             |  |  |

| Block blank check function | 136/fcpu+993                     | 136/fcpu+993       | 136/fcpu+1637            | 136/fcpu+428                                    | 136/fcpu+428                | 136/fcpu+438             |  |  |

| Set information function   | 72/fcpu+833                      | 72/fcpu+833        | 72/fcpu+1477             | 72/fcpu+346                                     | 72/fcpu+346                 | 72/fcpu+346              |  |  |

| EEPROM write function      | 268/fcpu+1107                    | 268/fcpu+1107      | 268/fcpu+1751            | 268/fcpu+542                                    | 268/fcpu+542                | 268/fcpu+552             |  |  |

#### Table 27-14. Interrupt Response Time (Library for Static Model) (2/2)

- **Note** This is the function processing time when the function is executed immediately after the self programming start function has been executed. The processing time after a function other than the self programming start function has been executed is the same as that of RSTOP = 0.

- Remark RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- RSTS: Bit 7 of RCM

- MCS: Bit 1 of main clock mode register (MCM)

- fcpu: CPU clock frequency

- W: Number of words to be written (1 word = 4 bytes)

| Instruction | Mnemonic  | Operands       | Bytes          |        | ocks   | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | Flag | g    |

|-------------|-----------|----------------|----------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|

| Group       | Minemonic | Operands       | bytes          | Note 1 | Note 2 | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Z | AC   | ; CY |

| 16-bit data | MOVW      | rp, #word      | 3              | 6      | -      | $rp \leftarrow word$                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      |      |

| transfer    |           | saddrp, #word  | 4              | 8      | 10     | $(saddrp) \leftarrow word$                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      |      |

|             |           | sfrp, #word    | 4              | -      | 10     | $sfrp \leftarrow word$                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |      |

|             |           | AX, saddrp     | 2              | 6      | 8      | $AX \leftarrow (saddrp)$                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      |      |

|             |           | saddrp, AX     | 2              | 6      | 8      | $(saddrp) \leftarrow AX$                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      |      |

|             |           | AX, sfrp       | 2              | -      | 8      | $AX \leftarrow sfrp$                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      |      |

|             |           | sfrp, AX       | 2              | -      | 8      | sfrp $\leftarrow$ AX                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      |      |

|             |           | AX, rp         | <sup>3</sup> 1 | 4      | -      | $AX \leftarrow rp$                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |      |

|             |           | rp, AX         | <sup>3</sup> 1 | 4      | -      | $rp \leftarrow AX$                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |      |      |

|             |           | AX, !addr16    | 3              | 10     | 12     | $AX \leftarrow (addr16)$                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      |      |

|             |           | !addr16, AX    | 3              | 10     | 12     | (addr16) ← AX                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |      |      |

|             | XCHW      | AX, rp         | <sup>3</sup> 1 | 4      | -      | $AX \leftrightarrow rp$                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      |      |

| 8-bit       | ADD       | A, #byte       | 2              | 4      | -      | A, CY $\leftarrow$ A + byte                                                                                                                                                                                                                                                                                                                                                                                                                                  | × | ×    | ×    |

| operation   |           | saddr, #byte   | 3              | 6      | 8      | (saddr), CY $\leftarrow$ (saddr) + byte                                                                                                                                                                                                                                                                                                                                                                                                                      | × | ×    | ×    |

|             |           | A, r           | ⁴ 2            | 4      | -      | $\begin{array}{l} rp \leftarrow AX \\ AX \leftarrow (addr16) \\ (addr16) \leftarrow AX \\ AX \leftrightarrow rp \\ A, CY \leftarrow A + byte \\ (saddr), CY \leftarrow (saddr) + byte \\ A, CY \leftarrow A + r \\ r, CY \leftarrow r + A \\ A, CY \leftarrow A + (saddr) \\ A, CY \leftarrow A + (saddr) \\ A, CY \leftarrow A + (hL) \\ A, CY \leftarrow A + (HL + byte) \\ A, CY \leftarrow A + (HL + B) \\ A, CY \leftarrow A + (HL + C) \\ \end{array}$ | × | ×    | ×    |

|             |           | r, A           | 2              | 4      | -      | $r, CY \leftarrow r + A$                                                                                                                                                                                                                                                                                                                                                                                                                                     | × | ×    | ×    |

|             |           | A, saddr       | 2              | 4      | 5      | A, CY $\leftarrow$ A + (saddr)                                                                                                                                                                                                                                                                                                                                                                                                                               | × | ×    | ×    |

|             |           | A, !addr16     | 3              | 8      | 9      | A, CY $\leftarrow$ A + (addr16)                                                                                                                                                                                                                                                                                                                                                                                                                              | × | ×    | ×    |

|             |           | A, [HL]        | 1              | 4      | 5      | A, CY $\leftarrow$ A + (HL)                                                                                                                                                                                                                                                                                                                                                                                                                                  | × | ×    | ×    |

|             |           | A, [HL + byte] | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte)                                                                                                                                                                                                                                                                                                                                                                                                                           | × | ×    | ×    |

|             |           | A, [HL + B]    | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + B)                                                                                                                                                                                                                                                                                                                                                                                                                              | × | ×    | ×    |

|             |           | A, [HL + C]    | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + C)                                                                                                                                                                                                                                                                                                                                                                                                                              | × | ×    | ×    |

|             | ADDC      | A, #byte       | 2              | 4      | -      | A, CY $\leftarrow$ A + byte + CY                                                                                                                                                                                                                                                                                                                                                                                                                             | × | ×    | ×    |

|             |           | saddr, #byte   | 3              | 6      | 8      | (saddr), CY $\leftarrow$ (saddr) + byte + CY                                                                                                                                                                                                                                                                                                                                                                                                                 | × | ×    | ×    |

|             |           | A, r           | ⁴ 2            | 4      | -      | A, $CY \leftarrow A + r + CY$                                                                                                                                                                                                                                                                                                                                                                                                                                | × | ×    | ×    |

|             |           | r, A           | 2              | 4      | -      | $r,CY \leftarrow r + A + CY$                                                                                                                                                                                                                                                                                                                                                                                                                                 | × | ×    | ×    |

|             |           | A, saddr       | 2              | 4      | 5      | A, CY $\leftarrow$ A + (saddr) + CY                                                                                                                                                                                                                                                                                                                                                                                                                          | × | ×    | ×    |

|             |           | A, !addr16     | 3              | 8      | 9      | A, CY $\leftarrow$ A + (addr16) + C                                                                                                                                                                                                                                                                                                                                                                                                                          | × | ×    | ×    |

|             |           | A, [HL]        | 1              | 4      | 5      | $A, CY \leftarrow A + (HL) + CY$                                                                                                                                                                                                                                                                                                                                                                                                                             | × | ×    | ×    |

|             |           | A, [HL + byte] | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte) + CY                                                                                                                                                                                                                                                                                                                                                                                                                      | × | ×    | ×    |

|             |           | A, [HL + B]    | 2              | 8      | 9      | $A, CY \leftarrow A + (HL + B) + CY$                                                                                                                                                                                                                                                                                                                                                                                                                         | × | ×    | ×    |

|             |           | A, [HL + C]    | 2              | 8      | 9      | A, CY $\leftarrow$ A + (HL + C) + CY                                                                                                                                                                                                                                                                                                                                                                                                                         | × | ×    | ×    |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

- **3.** Only when rp = BC, DE or HL

- **4.** Except "r = A"

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.

| Instruction   | Magazia  | Onorondo  | Dutes | Clo    | ocks   | Operation                                                                                                                                                                                                    |   | -lag |

|---------------|----------|-----------|-------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|

| Group         | Mnemonic | Operands  | Bytes | Note 1 | Note 2 | Operation                                                                                                                                                                                                    |   | AC C |

| Call/return   | CALL     | !addr16   | 3     | 7      | -      | $(SP - 1) \leftarrow (PC + 3)_{H}, (SP - 2) \leftarrow (PC + 3)_{L},$<br>PC $\leftarrow$ addr16, SP $\leftarrow$ SP - 2                                                                                      |   |      |

|               | CALLF    | !addr11   | 2     | 5      | -      | $(SP - 1) \leftarrow (PC + 2)H$ , $(SP - 2) \leftarrow (PC + 2)L$ ,<br>PC <sub>15-11</sub> $\leftarrow$ 00001, PC <sub>10-0</sub> $\leftarrow$ addr11,<br>SP $\leftarrow$ SP - 2                             |   |      |

|               | CALLT    | [addr5]   | 1     | 6      | _      | $(SP - 1) \leftarrow (PC + 1)_{H}, (SP - 2) \leftarrow (PC + 1)_{L},$<br>$PC_{H} \leftarrow (addr5 + 1), PC_{L} \leftarrow (addr5),$<br>$SP \leftarrow SP - 2$                                               |   |      |

|               | BRK      |           | 1     | 6      | _      | $(SP - 1) \leftarrow PSW$ , $(SP - 2) \leftarrow (PC + 1)$ H,<br>$(SP - 3) \leftarrow (PC + 1)$ L, $PC$ H $\leftarrow (003FH)$ ,<br>$PC$ L $\leftarrow (003EH)$ , $SP \leftarrow SP - 3$ , $IE \leftarrow 0$ |   |      |

|               | RET      |           | 1     | 6      | -      | $PC_{H} \leftarrow (SP + 1), PC_{L} \leftarrow (SP),$<br>$SP \leftarrow SP + 2$                                                                                                                              |   |      |

|               | RETI     |           | 1     | 6      | _      | $PC_{H} \leftarrow (SP + 1), PC_{L} \leftarrow (SP),$<br>$PSW \leftarrow (SP + 2), SP \leftarrow SP + 3$                                                                                                     | R | RR   |

|               | RETB     |           | 1     | 6      | -      | PC <sub>H</sub> ← (SP + 1), PC <sub>L</sub> ← (SP),<br>PSW ← (SP + 2), SP ← SP + 3                                                                                                                           | R | RR   |

| Stack         | PUSH     | PSW       | 1     | 2      | -      | $(SP - 1) \leftarrow PSW, SP \leftarrow SP - 1$                                                                                                                                                              |   |      |

| manipulate    |          | rp        | 1     | 4      | -      | $(SP - 1) \leftarrow rp_H, (SP - 2) \leftarrow rp_L,$<br>$SP \leftarrow SP - 2$                                                                                                                              |   |      |

|               | POP      | PSW       | 1     | 2      | -      | $PSW \leftarrow (SP),  SP \leftarrow SP + 1$                                                                                                                                                                 | R | RR   |

|               |          | rp        | 1     | 4      | -      | $rp_{H} \leftarrow (SP + 1), rp_{L} \leftarrow (SP),$<br>SP ← SP + 2                                                                                                                                         |   |      |

|               | MOVW     | SP, #word | 4     | -      | 10     | $SP \leftarrow word$                                                                                                                                                                                         |   |      |

|               |          | SP, AX    | 2     | -      | 8      | $SP \leftarrow AX$                                                                                                                                                                                           |   |      |

|               |          | AX, SP    | 2     | -      | 8      | $AX \leftarrow SP$                                                                                                                                                                                           |   |      |

| Unconditional | BR       | !addr16   | 3     | 6      | -      | $PC \leftarrow addr16$                                                                                                                                                                                       |   |      |

| branch        |          | \$addr16  | 2     | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$                                                                                                                                                                              |   |      |

|               |          | AX        | 2     | 8      | -      | $PCH \leftarrow A,  PC_{L} \leftarrow X$                                                                                                                                                                     |   |      |

| Conditional   | вс       | \$addr16  | 2     | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 1$                                                                                                                                                                  |   |      |

| branch        | BNC      | \$addr16  | 2     | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $CY = 0$                                                                                                                                                                  |   |      |

|               | BZ       | \$addr16  | 2     | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 1$                                                                                                                                                                   |   |      |

|               | BNZ      | \$addr16  | 2     | 6      | -      | $PC \leftarrow PC + 2 + jdisp8$ if $Z = 0$                                                                                                                                                                   |   |      |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

**Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

2. This clock cycle applies to the internal ROM program.

#### Standard products

## DC Characteristics (1/5)

#### (TA = -40 to +85°C, 1.8 V $\leq$ VDD $\leq$ 5.5 V, AVREF $\leq$ VDD, Vss = AVss = 0 V)

| Parameter                             | Symbol | Condition                                                                            | S                                     | MIN. | TYP. | MAX.  | Unit |

|---------------------------------------|--------|--------------------------------------------------------------------------------------|---------------------------------------|------|------|-------|------|

| Output current, high <sup>Note1</sup> | Іон1   | Per pin for P11 to P14,                                                              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -3.0  | mA   |

|                                       |        | P31 to P34, P40 to P44,<br>P120                                                      | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -2.5  | mA   |

|                                       |        |                                                                                      | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -1.0  | mA   |

|                                       |        | Per pin for P80 to P83,                                                              | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -0.1  | mA   |

|                                       |        | P100 to P103, P110 to P113,                                                          | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -0.1  | mA   |

|                                       |        | P140 to P143, P150 to P153                                                           | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -0.1  | mA   |

|                                       |        | Total <sup>Note3</sup> of P11 to P14,                                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -20.0 | mA   |

|                                       |        | P31 to P34, P40 to P44,                                                              | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -10.0 | mA   |

|                                       |        | P120                                                                                 | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -5.0  | mA   |

|                                       |        | Total <sup>Note3</sup> of P80 to P83,                                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -2.8  | mA   |

|                                       |        | P100 to P103, P110 to P113,                                                          | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -2.8  | mA   |

|                                       |        | P140 to P143, P150 to P153                                                           | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -2.8  | mA   |

|                                       |        | Total <sup>Note3</sup> of all pins                                                   | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | -22.8 | mA   |

|                                       |        |                                                                                      | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | -12.8 | mA   |

|                                       |        |                                                                                      | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | -7.8  | mA   |

|                                       | Іон2   | Per pin for P20 to P27                                                               | AVREF = VDD                           |      |      | -0.1  | mA   |

| Output current, low <sup>Note2</sup>  | IOL1   | Per pin for P11 to P14,<br>P31 to P34, P40 to P44,<br>P120                           | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 8.5   | mA   |

|                                       |        |                                                                                      | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 5.0   | mA   |

|                                       |        |                                                                                      | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 2.0   | mA   |

|                                       |        | Per pin for P80 to P83,<br>P100 to P103, P110 to P113,<br>P140 to P143, P150 to P153 | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 0.4   | mA   |

|                                       |        |                                                                                      | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 0.4   | mA   |

|                                       |        |                                                                                      | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 0.4   | mA   |

|                                       |        | Total <sup>Note3</sup> of P11 to P14,                                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 20.0  | mA   |

|                                       |        | P31 to P34, P40 to P44,                                                              | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 15.0  | mA   |

|                                       |        | P120                                                                                 | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 9.0   | mA   |

|                                       |        | Total <sup>Note3</sup> of P80 to P83,                                                | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 11.2  | mA   |

|                                       |        | P100 to P103, P110 to P113,                                                          | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 11.2  | mA   |

|                                       |        | P140 to P143, P150 to P153                                                           | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 11.2  | mA   |

|                                       |        | Total <sup>Note3</sup> of all pins                                                   | $4.0~V \leq V_{\text{DD}} \leq 5.5~V$ |      |      | 31.2  | mA   |

|                                       |        |                                                                                      | $2.7~V \leq V_{\text{DD}} < 4.0~V$    |      |      | 26.2  | mA   |

|                                       |        |                                                                                      | $1.8~V \leq V_{\text{DD}} < 2.7~V$    |      |      | 20.2  | mA   |

|                                       | IOL2   | Per pin for P20 to P27                                                               | AVREF = VDD                           |      |      | 0.4   | mA   |

Notes 1. Value of current at which the device operation is guaranteed even if the current flows from  $V_{DD}$  to an output pin.

2. Value of current at which the device operation is guaranteed even if the current flows from an output pin to GND.

- **3.** Specification under conditions where the duty factor is 70% (time for which current is output is  $0.7 \times t$  and time for which current is not output is  $0.3 \times t$ , where t is a specific time). The total output current of the pins at a duty factor of other than 70% can be calculated by the following expression.

- Where the duty factor of IoH is n%: Total output current of pins = (IoH  $\times$  0.7)/(n  $\times$  0.01)

<Example> Where the duty factor is 50%, Iон = 20.0 mA

Total output current of pins =  $(20.0 \times 0.7)/(50 \times 0.01) = 28.0 \text{ mA}$

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of port pins.