## E. Renesas Electronics America Inc - UPD78F0454GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 46                                                                                   |

| Program Memory Size        | 48KB (48K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 2K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-TQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0454gb-gah-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| /                | Part Number                                   |                                                              |               |       |          |          |           | 7        | 8K0/LF                | 3        |                        |            |         |        |    |    |

|------------------|-----------------------------------------------|--------------------------------------------------------------|---------------|-------|----------|----------|-----------|----------|-----------------------|----------|------------------------|------------|---------|--------|----|----|

|                  |                                               |                                                              | μPD78F047x μF |       |          |          |           |          | D78F04                | 48x      |                        | μPD78F049x |         |        |    |    |

| lte              | m                                             |                                                              | 80 Pins       |       |          |          |           |          |                       |          |                        |            |         |        |    |    |

|                  | ash memory (KB)                               | 16                                                           | 24            | 32    | 48       | 60       | 16        | 24       | 32                    | 48       | 60                     | 16         | 24      | 32     | 48 | 60 |

|                  | AM (KB)                                       | 0.75                                                         | 1             | 1     | 2        | 2        | 0.75      | 1        | 1                     | 2        | 2                      | 0.75       | 1       | 1      | 2  | 2  |

|                  | wer supply voltage                            |                                                              |               |       |          |          |           |          | = 1.8 to              |          |                        |            |         |        |    |    |

|                  | egulator                                      |                                                              |               | 0.0   |          | NAL 1 X  | / 0       |          |                       |          | N41 1-1-               | V 1        | 0 to F  | 5 \/)  |    |    |

|                  | nimum instruction<br>ecution time             |                                                              |               | 0.2   |          |          |           |          |                       |          |                        | VDD = 1    |         | .5 V)  |    |    |

|                  | High-speed system                             |                                                              |               |       | 10       | ) MHZ:   |           |          |                       |          |                        | 8 to 5.5   | 5 V     |        |    |    |

| Clock            | oscillation clock                             |                                                              |               |       |          |          |           | •        | .): VDD =             |          |                        |            |         |        |    |    |

| -                | SUDCIOCK                                      |                                                              |               |       |          | 3        | 32.768 k  |          |                       |          |                        |            |         |        |    |    |

|                  | Internal low-speed oscillation clock          |                                                              |               |       |          |          | 240 k⊦    | IZ (TYF  | P.): Vdd              | = 1.8 t  | o 5.5 V                | /          |         |        |    |    |

| Port             |                                               |                                                              |               |       |          |          |           |          | 62                    |          |                        |            |         |        |    |    |

|                  | 16 bits (TM0)                                 |                                                              |               |       |          |          |           |          | 1 ch                  |          |                        |            |         |        |    |    |

| er               | 8 bits (TM5)                                  |                                                              | 3 ch          |       |          |          |           |          |                       |          |                        |            |         |        |    |    |

| Timer            | 8 bits (TMH)                                  |                                                              |               |       |          |          |           |          | 3 ch                  |          |                        |            |         |        |    |    |

|                  | RTC                                           |                                                              |               |       |          |          |           |          | 1 ch                  |          |                        |            |         |        |    |    |

|                  | WDT                                           |                                                              |               |       |          |          |           |          | 1 ch                  |          |                        |            |         |        |    |    |

| gce              | 3-wire CSI/UART <sup>Note 1</sup>             |                                                              |               |       |          |          |           |          | 1 ch                  |          |                        |            |         |        |    |    |

| interfa          | Automatic transmit/<br>receive 3-wire CSI     | 1 ch                                                         |               |       |          |          |           |          |                       |          |                        |            |         |        |    |    |

| Serial interface | UART supporting LIN-<br>bus <sup>Note 2</sup> |                                                              | 1 ch          |       |          |          |           |          |                       |          |                        |            |         |        |    |    |

| _                | Туре                                          |                                                              |               | Exter | nal res  | istance  | e divisio | n and ii | nternal               | resistar | nce div                | ision are  | e switc | hable. |    |    |

| 2                | Segment signal                                | 40 (36) [36 (32)] <sup>Note 3, 4</sup> 32 (28) [28 (24)      |               |       |          |          |           |          |                       |          | 4)] <sup>Note 3,</sup> | 4          |         |        |    |    |

| _                | Common signal                                 |                                                              |               |       |          |          |           |          | 4 (8) <sup>Note</sup> | 3        |                        |            |         |        |    |    |

|                  | -bit successive<br>proximation type A/D       |                                                              |               | -     |          |          |           |          |                       |          | 8                      | ch         |         |        |    |    |

| 16               | -bit ∆Σ type A/D                              |                                                              |               |       |          |          | _         |          |                       |          |                        |            |         | 3 ch   |    |    |

| upt.             | External                                      |                                                              |               |       |          |          |           |          | 7                     |          |                        |            |         |        |    |    |

| Interru          | Internal                                      |                                                              |               | 20    |          |          |           |          | 21                    |          |                        |            |         | 22     |    |    |

|                  | gment key source signal<br>tput               |                                                              |               |       |          |          |           |          | 8 ch                  |          |                        |            |         |        |    |    |

| Ke               | y interrupt                                   |                                                              | 8 ch          |       |          |          |           |          |                       |          |                        |            |         |        |    |    |

|                  | RESET pin                                     |                                                              |               |       |          |          |           | F        | Provide               | d        |                        |            |         |        |    |    |

| set              | POC                                           | 1.59 V ±0.15 V (Time for rising up to 1.8 V : 3.6 ms (MAX.)) |               |       |          |          |           |          |                       |          |                        |            |         |        |    |    |

| Reset            | LVI                                           | İ                                                            |               | Т     | he dete  | ection I | evel of   | the sup  | ply vol               | tage is  | selecta                | able in    | 16 step | DS.    |    |    |

|                  | WDT                                           |                                                              |               |       | Provided |          |           |          |                       |          |                        |            |         |        |    |    |

| Clo              | ock output/ Buzzer output                     | 1                                                            | Provided      |       |          |          |           |          |                       |          |                        |            |         |        |    |    |

| Re               | mote controller receiver                      |                                                              |               |       |          |          |           | F        | Provide               | d        |                        |            |         |        |    |    |

| M                | CG                                            |                                                              |               |       |          |          |           | I        | Provide               | d        |                        |            |         |        |    |    |

| Or               | n-chip debug function                         | 1                                                            |               |       |          |          |           | F        | Provide               | d        |                        |            |         |        |    |    |

|                  | erating ambient temperature                   |                                                              |               |       |          |          |           | TA =     | -40 to -              | -85°C    |                        |            |         |        |    |    |

**Notes 1.** Select either of the functions of these alternate-function pins.

- 2. The LIN-bus supporting UART pins can be changed to the Automatic transmit/receive 3-wire CSI/UART pins (pin numbers 75 and 76).

- 3. The values in parentheses are the number of signal outputs when 8com is used.

- **4.** The values in square brackets are the number of signal outputs when using the UART6 pins (RxD6, TxD6) on the bottom side.

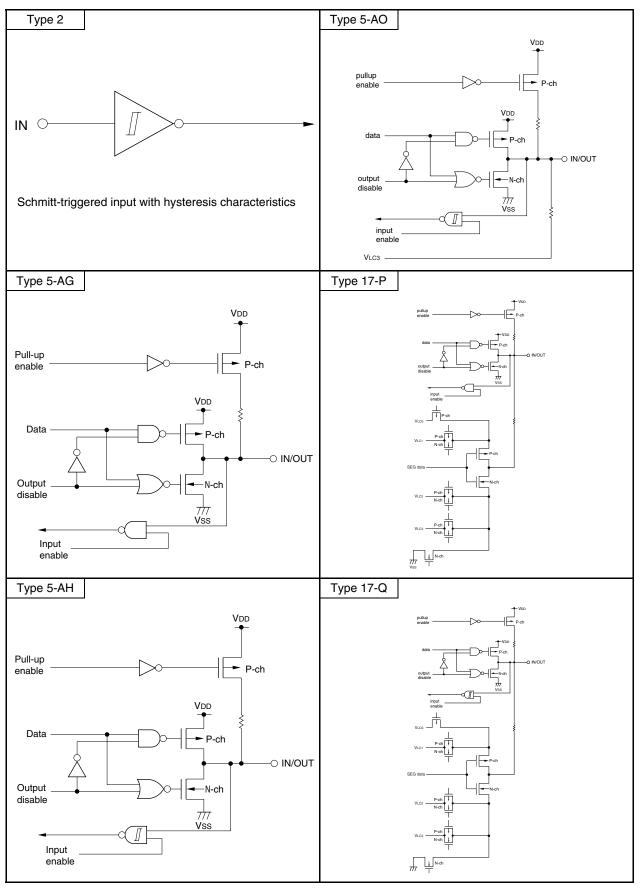

#### (2) CALLT instruction table area

The 64-byte area 0040H to 007FH can store the subroutine entry address of a 1-byte call instruction (CALLT).

#### (3) Option byte area

A 5-byte area of 0080H to 0084H and 1080H to 1084H can be used as an option byte area. Set the option byte at 0080H to 0084H when the boot swap is not used, and at 0080H to 0084H and 1080H to 1084H when the boot swap is used. For details, see **CHAPTER 26 OPTION BYTE**.

#### (4) CALLF instruction entry area

The area 0800H to 0FFFH can perform a direct subroutine call with a 2-byte call instruction (CALLF).

#### (5) On-chip debug security ID setting area

A 10-byte area of 0085H to 008EH and 1085H to 108EH can be used as an on-chip debug security ID setting area. Set the on-chip debug security ID of 10 bytes at 0085H to 008EH when the boot swap is not used and at 0085H to 008EH and 1085H to 108EH when the boot swap is used. For details, see **CHAPTER 28 ON-CHIP DEBUG FUNCTION**.

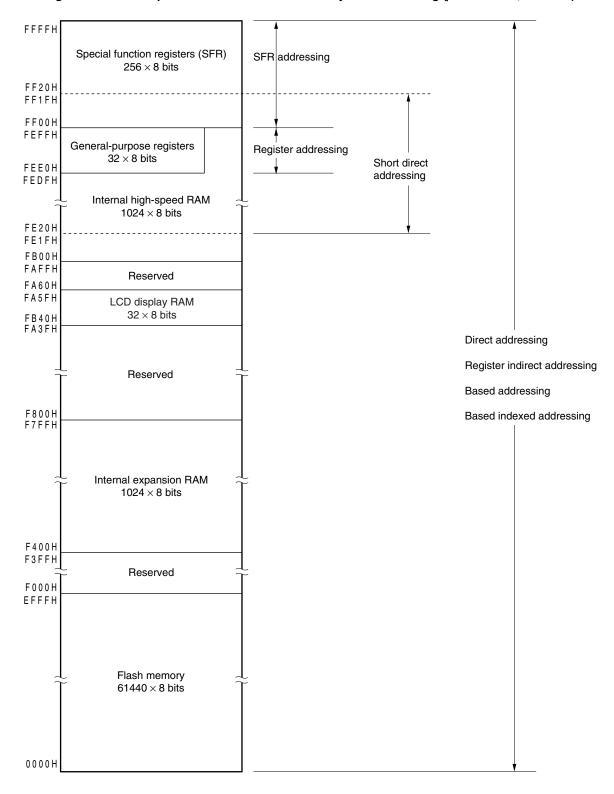

Figure 4-9. Block Diagram of P41 and P42

- P4: Port register 4

- PU4: Pull-up resistor option register 4

- PM4: Port mode register 4

- RD: Read signal

- WR××: Write signal

#### Figure 6-21. Example of Register Settings in External Event Counter Mode (2/2)

#### (e) 16-bit timer counter 00 (TM00)

By reading TM00, the count value can be read.

#### (f) 16-bit capture/compare register 000 (CR000)

If M is set to CR000, the interrupt signal (INTTM000) is generated when the number of external events reaches (M + 1).

Setting CR000 to 0000H is prohibited.

#### (g) 16-bit capture/compare register 010 (CR010)

Usually, CR010 is not used in the external event counter mode. However, a compare match interrupt (INTTM010) is generated when the set value of CR010 matches the value of TM00. Therefore, mask the interrupt request by using the interrupt mask flag (TMMK010).

#### 6.6 Cautions for 16-Bit Timer/Event Counter 00

#### (1) Restrictions for each channel of 16-bit timer/event counter 00

Table 6-3 shows the restrictions for each channel.

#### Table 6-3. Restrictions for Each Channel of 16-Bit Timer/Event Counter 00

| Operation                                                   | Restriction                                                                                                      |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| As interval timer                                           | _                                                                                                                |

| As square wave output                                       |                                                                                                                  |

| As external event counter                                   |                                                                                                                  |

| As clear & start mode entered by TI000 pin valid edge input | Using timer output (TO00) is prohibited when detection of the valid edge of the TI010 pin is used. (TOC00 = 00H) |

| As free-running timer                                       | _                                                                                                                |

| As PPG output                                               | 0000H ≤ CR010 < CR000 ≤ FFFFH                                                                                    |

| As one-shot pulse output                                    | Setting the same value to CR000 and CR010 is prohibited.                                                         |

| As pulse width measurement                                  | Using timer output (TO00) is prohibited (TOC00 = 00H)                                                            |

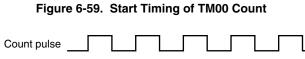

#### (2) Timer start errors

An error of up to one clock may occur in the time required for a match signal to be generated after timer start. This is because counting TM00 is started asynchronously to the count pulse.

(3) Setting of CR000 and CR010 (clear & start mode entered upon a match between TM00 and CR000) Set a value other than 0000H to CR000 and CR010 (TM00 cannot count one pulse when it is used as an external event counter).

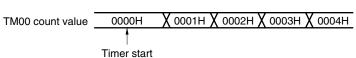

#### Figure 7-17. Square-Wave Output Operation Timing

Note The initial value of TO5n output can be set by bits 2 and 3 (LVR5n, LVS5n) of 8-bit timer mode control register 5n (TMC5n).

#### 7.4.4 PWM output operation

8-bit timer/event counter 5n operates as a PWM output when bit 6 (TMC5n6) of 8-bit timer mode control register 5n (TMC5n) is set to 1.

The duty pulse determined by the value set to 8-bit timer compare register 5n (CR5n) is output from TO5n.

Set the active level width of the PWM pulse to CR5n; the active level can be selected with bit 1 (TMC5n1) of

#### TMC5n.

The count clock can be selected with bits 0 to 2 (TCL5n0 to TCL5n2) of timer clock selection register 5n (TCL5n). PWM output can be enabled/disabled with bit 0 (TOE5n) of TMC5n.

#### Caution In PWM mode, make the CR5n rewrite period 3 count clocks of the count clock (clock selected by TCL5n) or more.

**Remark** n = 0, 1

#### Setting

<1> Set each register.

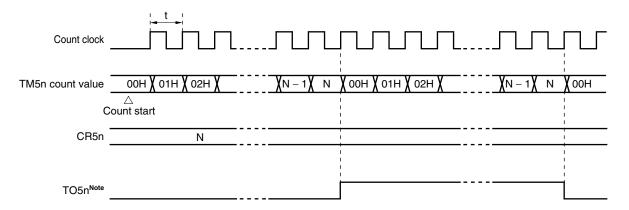

#### Figure 8-16. Register Setting in Carrier Generator Mode

#### (i) Setting 8-bit timer H mode register 1 (TMHMD1)

#### (ii) CMP01 register setting

· Compare value

#### (iii) CMP11 register setting

· Compare value

#### (iv) TMCYC1 register setting

- RMC1 = 1 ... Remote control output enable bit

- NRZB1 = 0/1 ... carrier output enable bit

#### (v) TCL51 and TMC51 register setting

- See 7.3 Registers Controlling 8-Bit Timer/Event Counters 50, 51, and 52.

- <2> When TMHE1 = 1, the 8-bit timer H1 starts counting.

- <3> When TCE51 of the 8-bit timer mode control register 51 (TMC51) is set to 1, the 8-bit timer/event counter 51 starts counting.

- <4> After the count operation is enabled, the first compare register to be compared is the CMP01 register. When the count value of the 8-bit timer counter H1 and the CMP01 register value match, the INTTMH1 signal is generated, the 8-bit timer counter H1 is cleared. At the same time, the compare register to be compared with the 8-bit timer counter H1 is switched from the CMP01 register to the CMP11 register.

- <5> When the count value of the 8-bit timer counter H1 and the CMP11 register value match, the INTTMH1 signal is generated, the 8-bit timer counter H1 is cleared. At the same time, the compare register to be compared with the 8-bit timer counter H1 is switched from the CMP11 register to the CMP01 register.

- <6> By performing procedures <4> and <5> repeatedly, a carrier clock is generated.

- <7> The INTTM51 signal is synchronized with count clock of the 8-bit timer H1 and output as the INTTM5H1 signal. The INTTM5H1 signal becomes the data transfer signal for the NRZB1 bit, and the NRZB1 bit value is transferred to the NRZ1 bit.

- <8> Write the next value to the NRZB1 bit in the interrupt servicing program that has been started by the INTTM5H1 interrupt or after timing has been checked by polling the interrupt request flag. Write data to count the next time to the CR51 register.

- <9> When the NRZ1 bit is high level, a carrier clock is output by TOH1 output.

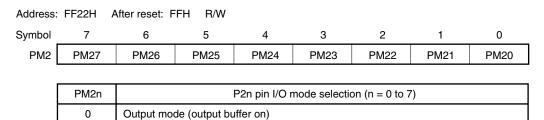

#### (6) Port mode register 2 (PM2)

When using the ANI0/P20 to ANI7/P27 pins for analog input port, set PM20 to PM27 to 1. The output latches of P20 to P27 at this time may be 0 or 1.

If PM20 to PM27 are set to 0, they cannot be used as analog input port pins.

PM2 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets this register to FFH.

#### Figure 12-10. Format of Port Mode Register 2 (PM2)

1 Input mode (output buffer off)

ANI0/P20 to ANI7/P27 pins are as shown below depending on the settings of PF2, ADPC0, PM2, ADS, and ADDCTL0.

#### Table 12-3. Setting Functions of P20/ANI0 to P27/ANI7 Pins

#### (a) *µ*PD78F045x

| PF2                  | ADPC0                                 | PM2            | ADS                  | P20/SEG31/ANI0 to P27/SEG24/ANI7 Pins                                         |

|----------------------|---------------------------------------|----------------|----------------------|-------------------------------------------------------------------------------|

| Digital/Analog       | Digital/Analog Analog input selection |                | Does not select ANI. | Analog input (not to be converted)                                            |

| selection            |                                       |                | Selects ANI.         | Analog input (to be converted by successive approximation type A/D converter) |

|                      |                                       | Output<br>mode | -                    | Setting prohibited                                                            |

|                      | Digital I/O selection                 | Input mode     | —                    | Digital input                                                                 |

|                      |                                       | Output<br>mode | _                    | Digital output                                                                |

| SEG output selection | -                                     | _              | _                    | Segment output                                                                |

#### (b) µPD78F046x

| ADPC0        | PM2         | ADS                  | ADDCTL0               | P20/ANI0/DS0- to P27/ANI7/REF+ Pins                                           |

|--------------|-------------|----------------------|-----------------------|-------------------------------------------------------------------------------|

| Analog input | Input mode  | Does not select ANI. | Does not select DSn±. | Analog input (not to be converted)                                            |

| selection    |             | Selects ANI.         | Does not select DSn±. | Analog input (to be converted by successive approximation type A/D converter) |

|              |             | Does not select ANI. | Selects DSn±.         | Analog input (to be converted by $\Delta\Sigma$ type A/D converter)           |

|              |             | Selects ANI.         | Selects DSn±.         | Setting prohibited                                                            |

|              | Output mode |                      | -                     | Setting prohibited                                                            |

| Digital I/O  | Input mode  |                      | =                     | Digital input                                                                 |

| selection    | Output mode |                      | -                     | Digital output                                                                |

#### 15.4.2 Asynchronous serial interface (UART) mode

In this mode, data of 1 byte is transmitted/received following a start bit, and a full-duplex operation can be performed.

A dedicated UART baud rate generator is incorporated, so that communication can be executed at a wide range of baud rates.

#### (1) Registers used

- Asynchronous serial interface operation mode register 6 (ASIM6)

- Asynchronous serial interface reception error status register 6 (ASIS6)

- Asynchronous serial interface transmission status register 6 (ASIF6)

- Clock selection register 6 (CKSR6)

- Baud rate generator control register 6 (BRGC6)

- Asynchronous serial interface control register 6 (ASICL6)

- Input switch control register (ISC)

- Port mode register 1 (PM1)

- Port register 1 (P1)

- Port mode register 11 (PM11)

- Port register 11 (P11)

The basic procedure of setting an operation in the UART mode is as follows.

- <1> Set the CKSR6 register (see Figure 15-8).

- <2> Set the BRGC6 register (see Figure 15-9).

- <3> Set bits 0 to 4 (ISRM6, SL6, CL6, PS60, PS61) of the ASIM6 register (see Figure 15-5).

- <4> Set bits 0 and 1 (TXDLV6, DIR6) of the ASICL6 register (see Figure 15-10).

- <5> Set bit 7 (POWER6) of the ASIM6 register to 1.

- <6> Set bit 6 (TXE6) of the ASIM6 register to 1. → Transmission is enabled. Set bit 5 (RXE6) of the ASIM6 register to 1. → Reception is enabled.

- <7> Write data to transmit buffer register 6 (TXB6).  $\rightarrow$  Data transmission is started.

### Caution Take relationship with the other party of communication when setting the port mode register and port register.

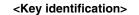

#### 17.6 Common and Segment Signals

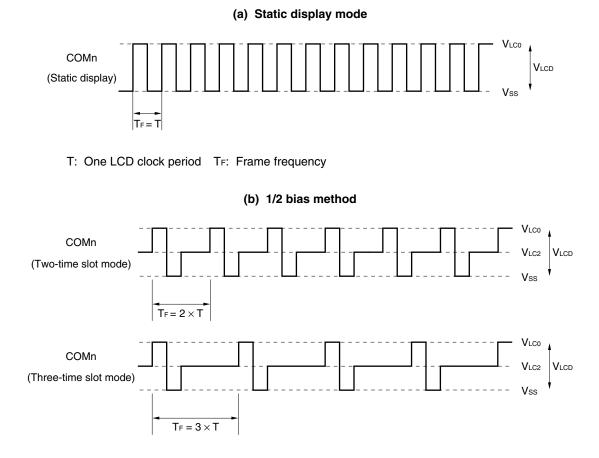

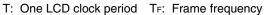

Each pixel of the LCD panel turns on when the potential difference between the corresponding common and segment signals becomes higher than a specific voltage (LCD drive voltage, VLCD). The pixels turn off when the potential difference becomes lower than VLCD.

Applying DC voltage to the common and segment signals of an LCD panel causes deterioration. To avoid this problem, this LCD panel is driven by AC voltage.

#### (1) Common signals

Each common signal is selected sequentially according to a specified number of time slices at the timing listed in Table 17-3. In the static display mode, the same signal is output to COM0 to COM3.

When using the segment key scan output function (KSON = 1), segment key scan output will be performed for a period of one time slice after one LCD output cycle. The common signal generated at that time will not be displayed when output.

In the two-time-slice mode, leave the COM2 and COM3 pins open. In the three-time-slice mode, leave the COM3 pin open.

Use the COM4 to COM7 pins other than in the eight-time-slice mode as open or segment pins.

| COM Signal                              | COM0 | COM1 | COM2 | СОМЗ    | COM4   | COM5   | COM6   | COM7   |

|-----------------------------------------|------|------|------|---------|--------|--------|--------|--------|

| Number of<br>Time Slices                |      |      |      |         |        |        |        |        |

| Static display mode                     | •    |      |      |         | Note 2 | Note 2 | Note 2 | Note 2 |

| Two-time-slice modeNote 1               | ł    | •    | Open | Open    | Note 2 | Note 2 | Note 2 | Note 2 |

| Three-time-slice modeNote 1             | 4    |      |      | Open    | Note 2 | Note 2 | Note 2 | Note 2 |

| Four-time-slice mode <sup>Note 1</sup>  | ł    |      |      | <b></b> | Note 2 | Note 2 | Note 2 | Note 2 |

| eight-time-slice mode <sup>Note 1</sup> | ł    |      |      |         |        |        |        | Å      |

Table 17-3. COM Signals

- **Notes 1.** When using the segment key scan output function (KSON = 1), non-display output will be performed for a period of one time slice after one LCD output cycle.

- 2. Use the pins as open or segment pins.

#### (2) Segment signals

#### (a) *µ*PD78F044x, 78F045x

The segment signals correspond to 32 bytes of the LCD display data memory (FA40H to FA5FH) during an LCD display period, bits 0, 1, 2, and 3 of each byte are read in synchronization with COM0, COM1, COM2, and COM3, respectively. If a bit is 1, it is converted to the select voltage, and if it is 0, it is converted to the deselect voltage. The conversion results are output to the segment pins (SEG0 to SEG31).

Furthermore, segment signals correspond to the setting values of port registers 14 and 15 during a segment key scan output period. Bits 0 to 3 and bits 4 to 7 of each port register will be read in synchronization with the first half and latter half of the segment key scan output period, respectively, and if the content of each bit is 1 or 0, high levels or low levels will be output to the segment pins (SEG16 to SEG23), respectively.

Figure 17-13 shows the common signal waveforms, and Figure 17-14 shows the voltages and phases of the common and segment signals.

(c) 1/3 bias method

T: One LCD clock period TF: Frame frequency

#### Shaded sections: Segment key scan output period

**Remark** During key identification, the residual charge of the LCD panel can be eliminated by outputting a signal with an inverted relationship between its first half and latter half.

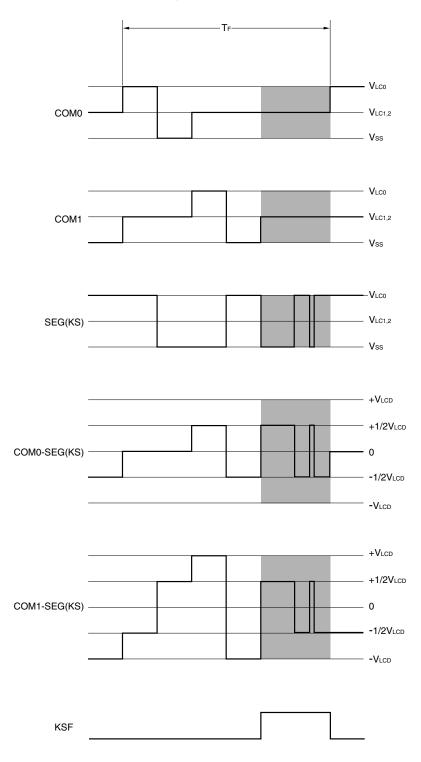

#### 19.4.5 Format of type C reception mode

Figure 19-10 shows the data format for type C.

#### Figure 19-10. Example of Type C Data Format

**Remark** RIN is the internally inverted signal of RIN.

#### 19.4.6 Operation flow of type C reception mode

Figure 19-11 shows the operation flow.

#### Cautions 1. When INTRERR is generated, RMSR and RMSCR are automatically cleared immediately.

- 2. When data has been set to all the bits of RMSR, the following processing is automatically performed.

- The value of RMSR is transferred to RMDR.

- INTDFULL is generated.

- RMSR is cleared.

- RMDR must then be read before the next data is set to all the bits of RMSR.

- 3. When INTREND has been generated, read RMSCR first followed by RMSR. When RMSR has been read, RMSCR and RMSR are automatically cleared. If INTREND is generated, the next data cannot be received until RMSR is read.

- 4. RMSR, RMSCR, and RMDR are cleared simultaneously to operation termination (RMEN = 0).

- 5. In type C reception mode, if the conditions for receiving a data low-/high-level width are not met before the first INTDFULL interrupt is generated, INTRERR and INTREND will not be generated. However, RMSR and RMSCR will be cleared.

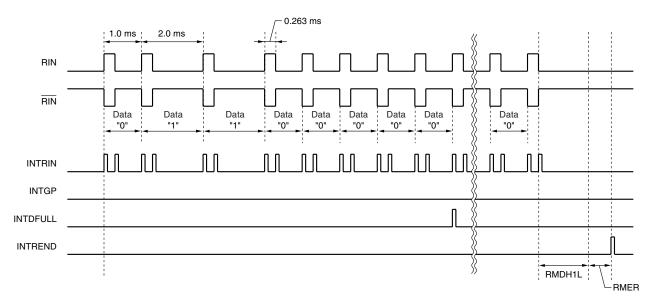

#### **CHAPTER 21 KEY INTERRUPT FUNCTION**

#### 21.1 Functions of Key Interrupt

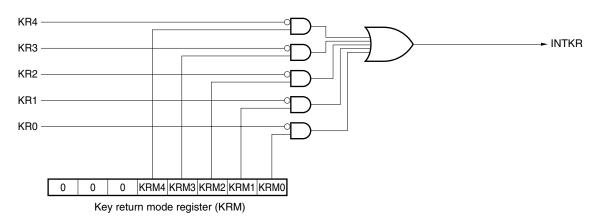

A key interrupt (INTKR) can be generated by setting the key return mode register (KRM) and inputting a falling edge to the key interrupt input pins (KR0 to KR4).

| Flag | Description                         |

|------|-------------------------------------|

| KRM0 | Controls KR0 signal in 1-bit units. |

| KRM1 | Controls KR1 signal in 1-bit units. |

| KRM2 | Controls KR2 signal in 1-bit units. |

| KRM3 | Controls KR3 signal in 1-bit units. |

| KRM4 | Controls KR4 signal in 1-bit units. |

Table 21-1. Assignment of Key Interrupt Detection Pins

#### 21.2 Configuration of Key Interrupt

The key interrupt includes the following hardware.

Table 21-2. Configuration of Key Interrupt

| Item             | Configuration                  |

|------------------|--------------------------------|

| Control register | Key return mode register (KRM) |

#### 25.5 Cautions for Low-Voltage Detector

In a system where the supply voltage ( $V_{DD}$ ) fluctuates for a certain period in the vicinity of the LVI detection voltage ( $V_{LVI}$ ), the operation is as follows depending on how the low-voltage detector is used.

#### (1) When used as reset

The system may be repeatedly reset and released from the reset status. In this case, the time from release of reset to the start of the operation of the microcontroller can be arbitrarily set by taking action (1) below.

#### (2) When used as interrupt

Interrupt requests may be frequently generated. Take (b) of action (2) below.

<Action>

#### (1) When used as reset

After releasing the reset signal, wait for the supply voltage fluctuation period of each system by means of a software counter that uses a timer, and then initialize the ports (see **Figure 25-9**).

#### (2) When used as interrupt

- (a) Confirm that "supply voltage (V<sub>DD</sub>) ≥ detection voltage (V<sub>LVI</sub>)" when detecting the falling edge of V<sub>DD</sub>, or "supply voltage (V<sub>DD</sub>) < detection voltage (V<sub>LVI</sub>)" when detecting the rising edge of V<sub>DD</sub>, in the servicing routine of the LVI interrupt by using bit 0 (LVIF) of the low-voltage detection register (LVIM). Clear bit 0 (LVIIF) of interrupt request flag register 0L (IF0L) to 0.

- (b) In a system where the supply voltage fluctuation period is long in the vicinity of the LVI detection voltage, wait for the supply voltage fluctuation period, confirm that "supply voltage (V<sub>DD</sub>) ≥ detection voltage (V<sub>LVI</sub>)" when detecting the falling edge of V<sub>DD</sub>, or "supply voltage (V<sub>DD</sub>) < detection voltage (V<sub>LVI</sub>)" when detecting the rising edge of V<sub>DD</sub>, using the LVIF flag, and clear the LVIIF flag to 0.

- **Remark** If bit 2 (LVISEL) of the low voltage detection register (LVIM) is set to "1", the meanings of the above words change as follows.

- Supply voltage (V<sub>DD</sub>)  $\rightarrow$  Input voltage from external input pin (EXLVI)

- Detection voltage (VLVI)  $\rightarrow$  Detection voltage (VEXLVI = 1.21 V)

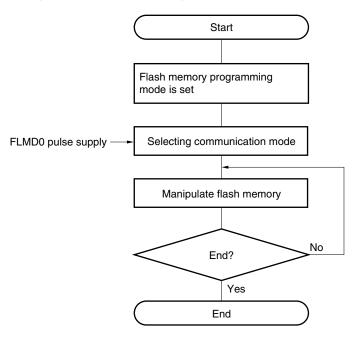

#### 27.7 Programming Method

#### 27.7.1 Controlling flash memory

The following figure illustrates the procedure to manipulate the flash memory.

<R>

#### Figure 27-12. Flash Memory Manipulation Procedure

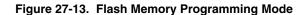

#### 27.7.2 Flash memory programming mode

To rewrite the contents of the flash memory by using the dedicated flash memory programmer, set the 78K0/LE3 in the flash memory programming mode. To set the mode, set the FLMD0 pin to V<sub>DD</sub> and clear the reset signal. Change the mode by using a jumper when writing the flash memory on-board.

#### Table 27-6. Relationship Between FLMD0 Pin and Operation Mode After Reset Release

| FLMD0 | Operation Mode                |  |  |  |  |

|-------|-------------------------------|--|--|--|--|

| 0     | Normal operation mode         |  |  |  |  |

| Vdd   | Flash memory programming mode |  |  |  |  |

Standard products

#### DC Characteristics (4/5) (TA = -40 to +85°C, 1.8 V $\leq$ VDD $\leq$ 5.5 V, AVREF $\leq$ VDD, VSS = AVSS = 0 V)

| Parameter      | Symbol     |                                    | Conditions                                           |                      | MIN. | TYP. | MAX. | Unit |

|----------------|------------|------------------------------------|------------------------------------------------------|----------------------|------|------|------|------|

| Supply current | DD1 Note 1 | Operating mode                     | $f_{XH} = 10 \text{ MHz}^{Note 2},$                  | Square wave input    |      | 1.6  | 3.0  | mA   |

|                |            |                                    | $V_{DD} = 5.0 V$                                     | Resonator connection |      | 2.3  | 3.4  |      |

|                |            |                                    | $f_{XH} = 10 \text{ MHz}^{Note 2},$                  | Square wave input    |      | 1.5  | 2.9  | mA   |

|                |            |                                    | $V_{DD} = 3.0 V$                                     | Resonator connection |      | 2.2  | 3.3  |      |

|                |            |                                    | $f_{XH} = 5 \text{ MHz}^{Note 2},$                   | Square wave input    |      | 0.9  | 1.7  | mA   |

|                |            |                                    | $V_{DD} = 3.0 V$                                     | Resonator connection |      | 1.3  | 2.0  |      |

|                |            | $f_{XH} = 5 \text{ MHz}^{Note 2},$ | Square wave input                                    |                      | 0.7  | 1.4  | mA   |      |

|                |            |                                    | $V_{DD} = 2.0 V$                                     | Resonator connection |      | 1.0  | 1.6  |      |

|                |            |                                    | fвн = 8 MHz, Vdd = 5.0 V                             | / <sup>Note 3</sup>  |      | 1.4  | 2.3  | mA   |

|                |            |                                    | fsub = 32.768 kHz <sup>Note 4</sup> ,<br>Vdd = 5.0 V | Resonator connection |      | 6.7  | 26   | μA   |

|                | DD2Note 1  | HALT mode                          | fxH = 10 MHz <sup>Note 2</sup> ,                     | Square wave input    |      | 0.4  | 1.4  | mA   |

|                |            |                                    | $V_{DD} = 5.0 V$                                     | Resonator connection |      | 1.0  | 1.7  |      |

|                |            |                                    | $f_{XH} = 5 \text{ MHz}^{\text{Note 2}},$            | Square wave input    |      | 0.2  | 0.7  | mA   |

|                |            |                                    | $V_{DD} = 3.0 V$                                     | Resonator connection |      | 0.5  | 1.0  |      |

|                |            |                                    | fвн = 8 MHz, Vdd = 5.0 V                             | / <sup>Note 3</sup>  |      | 0.4  | 1.2  | mA   |

|                |            |                                    | fsub = 32.768 kHz <sup>Note 5</sup> ,<br>Vdd = 5.0 V | Resonator connection |      | 2.4  | 22   | μA   |

| F              |            | STOP mode                          | V <sub>DD</sub> = 5.0 V                              |                      | 1    | 20   | μA   |      |

|                |            |                                    | $V_{DD} = 5.0 V, T_A = -40 tc$                       | ) +70°C              |      | 1    | 10   | μA   |

<R> Notes 1. Total current flowing into the internal power supply (VDD), including the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. The MAX. values include the peripheral operation current. However, the current flowing into the pull-up resistors and the output current of the port are not included.

2. Not including the operating current of the 8 MHz internal oscillator, 240 kHz internal oscillator and XT1 oscillation, and the current flowing into the A/D converter, watchdog timer, LVI circuit and LCD controller/driver.

**3.** Not including the operating current of the X1 oscillation, XT1 oscillation and 240 kHz internal oscillator, and the current flowing into the A/D converter, watchdog timer, LVI circuit and LCD controller/driver.

4. Not including the operating current of the X1 oscillation, 8 MHz internal oscillator and 240 kHz internal oscillator, and the current flowing into the A/D converter, watchdog timer, LVI circuit and LCD controller/driver.

Not including the operating current of the X1 oscillation, 8 MHz internal oscillator and 240 kHz internal oscillator, and the current flowing into the A/D converter, watchdog timer, LVI circuit, LCD controller/driver and real-time counter.

# Solution of the current flowing into the internal power supply (VDD), including the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. However, the current flowing into the pull-up resistors and the output current of the port, the operating current of the 240 kHz internal oscillator and XT1 oscillation, and the current flowing into the A/D converter, watchdog timer, LVI circuit, LCD controller/driver and real-time counter are not included.

- Remarks 1. fxH: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. free: Internal high-speed oscillation clock frequency

- 3. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

<R>

#### A.5 Debugging Tools (Hardware)

#### A.5.1 When using in-circuit emulator QB-78K0LX3

| QB-78K0/Lx3<br>In-circuit emulator                    | This in-circuit emulator serves to debug hardware and software when developing application systems using the 78K0/Lx3. It supports to the integrated debugger (ID78K0-QB). This emulator should be used in combination with a power supply unit and emulation probe, and the USB is used to connect this emulator to the host machine. |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QB-144-CA-01<br>Check pin adapter                     | This check pin adapter is used in waveform monitoring using the oscilloscope, etc.                                                                                                                                                                                                                                                     |

| QB-80-EP-01T<br>Emulation probe                       | This emulation probe is flexible type and used to connect the in-circuit emulator and target system.                                                                                                                                                                                                                                   |

| QB-64GB-EA-09T,<br>QB-64GK-EA-07T<br>Exchange adapter | <ul> <li>This exchange adapter is used to perform pin conversion from the in-circuit emulator to target connector.</li> <li>QB-64GB-EA-09T: For 64-pin plastic LQFP (GB-GAH type)</li> <li>QB-64GK-EA-07T: For 64-pin plastic LQFP (GK-GAJ type)</li> </ul>                                                                            |

| QB-64GB-YS-01T,<br>QB-64GK-YS-01T<br>Space adapter    | This space adapter is used to adjust the height between the target system and in-circuit emulator.<br>• QB-64GB-YS-01T: For 64-pin plastic LQFP (GB-GAH type)<br>• QB-64GK-YS-01T: For 64-pin plastic LQFP (GK-GAJ type)                                                                                                               |

| QB-64GB-YQ-01T,<br>QB-64GK-YQ-01T<br>YQ connector     | This YQ connector is used to connect the target connector and exchange adapter.<br>• QB-64GB-YQ-01T: For 64-pin plastic LQFP (GB-GAH type)<br>• QB-64GK-YQ-01T: For 64-pin plastic LQFP (GK-GAJ type)                                                                                                                                  |

| QB-64GB-HQ-01T,<br>QB-64GK-HQ-01T<br>Mount adapter    | This mount adapter is used to mount the target device with socket.<br>• QB-64GB-HQ-01T: For 64-pin plastic LQFP (GB-GAH type)<br>• QB-64GK-HQ-01T: For 64-pin plastic LQFP (GK-GAJ type)                                                                                                                                               |

| QB-64GB-NQ-01T,<br>QB-64GK-NQ-01T<br>Target connector | This target connector is used to mount on the target system.<br>• QB-64GB-NQ-01T: For 64-pin plastic LQFP (GB-GAH type)<br>• QB-64GK-NQ-01T: For 64-pin plastic LQFP (GK-GAJ type)                                                                                                                                                     |

**Remarks 1.** The QB-78K0LX3 is supplied with the integrated debugger ID78K0-QB, a USB interface cable, a power supply unit, the on-chip debug emulator QB-MINI2, connection cables (10-pin and 16-pin cables), and the 78K0-OCD board.

Download the software for operating the QB-MINI2 from the download site for development tools (http://www.necel.com/micro/ods/eng/index.html) when using the QB-MINI2.

2. The packed contents differ depending on the part number, as follows.

| Packed Contents  | In-Circuit Emulator | Emulation Probe | Exchange Adapter | YQ Connector   | Target Connector |

|------------------|---------------------|-----------------|------------------|----------------|------------------|

| Part Number      |                     |                 |                  |                |                  |

| QB-78K0LX3 -ZZZ  | QB-78K0LX3          | None            |                  |                |                  |

| QB-78K0LX3-T64GB |                     | QB-80-EP-01T    | QB-64GB-EA-09T   | QB-64GB-YQ-01T | QB-64GB-NQ-01T   |

| QB-78K0LX3-T64GK |                     |                 | QB-64GK-EA-07T   | QB-64GK-YQ-01T | QB-64GK-NQ-01T   |