# E. Renesas Electronics America Inc - UPD78F0455GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 46                                                                                   |

| Program Memory Size        | 60KB (60K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 2K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b                                                                            |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-TQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0455gb-gah-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

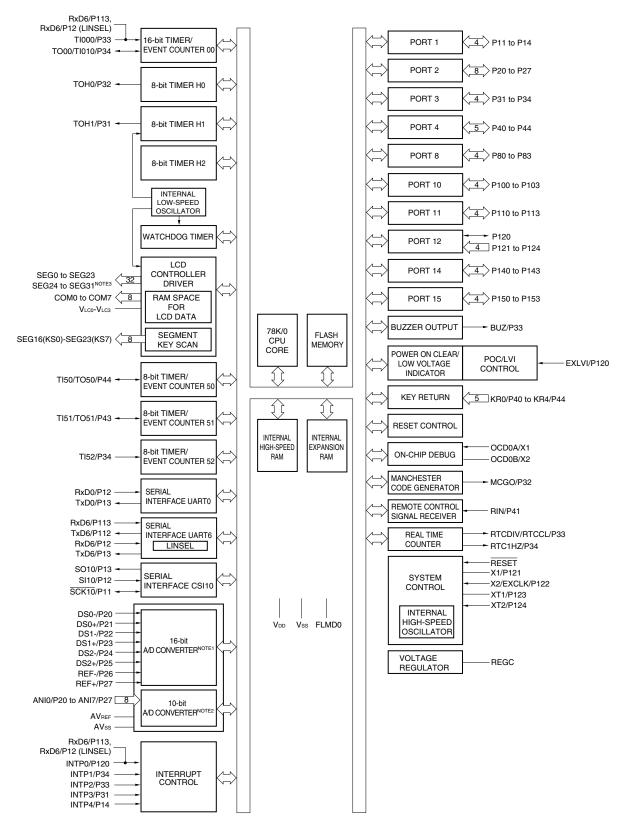

# 1.6 Block Diagram

**Notes 1.**  $\mu$ PD78F046x only.

- **2.** *μ*PD78F045x and 78F046x only.

- **3.** μPD78F044x and 78F045x only.

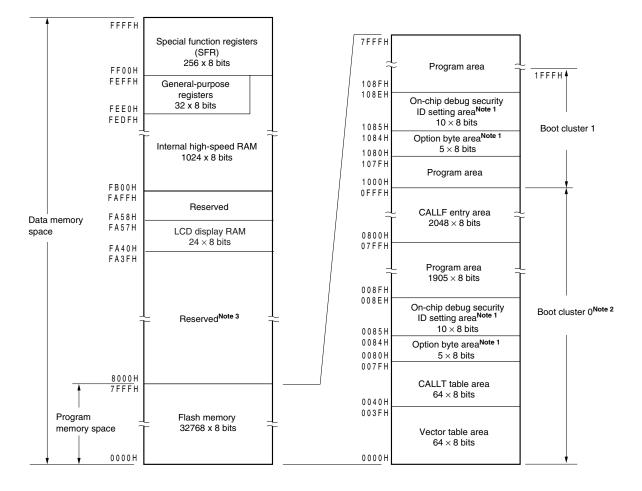

Figure 3-6. Memory Map (µPD78F0463)

**Notes 1.** When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used:

Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Setting).

- <R>

- 3. However, FA26H and FA27H can be used (See 13.3 Registers Used in 16-Bit  $\Delta\Sigma$  Type A/D Converter).

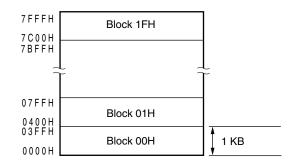

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

# (4) Internal oscillation mode register (RCM)

This register sets the operation mode of internal oscillator. RCM can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 80H<sup>Note 1</sup>.

# Figure 5-4. Format of Internal Oscillation Mode Register (RCM)

Address: FFA0H After reset: 80H<sup>Note 1</sup> R/W<sup>Note 2</sup>

| Symbol | <7>  | 6 | 5 | 4 | 3 | 2 | <1>     | <0>   |

|--------|------|---|---|---|---|---|---------|-------|

| RCM    | RSTS | 0 | 0 | 0 | 0 | 0 | LSRSTOP | RSTOP |

| RSTS | Status of internal high-speed oscillator                             |

|------|----------------------------------------------------------------------|

| 0    | Waiting for accuracy stabilization of internal high-speed oscillator |

| 1    | Stability operating of internal high-speed oscillator                |

| LSRSTOP | Internal low-speed oscillator oscillating/stopped |  |  |  |  |

|---------|---------------------------------------------------|--|--|--|--|

| 0       | Internal low-speed oscillator oscillating         |  |  |  |  |

| 1       | Internal low-speed oscillator stopped             |  |  |  |  |

| RSTOP | Internal high-speed oscillator oscillating/stopped |  |  |  |  |

|-------|----------------------------------------------------|--|--|--|--|

| 0     | nternal high-speed oscillator oscillating          |  |  |  |  |

| 1     | Internal high-speed oscillator stopped             |  |  |  |  |

- **Notes 1.** The value of this register is 00H immediately after a reset release but automatically changes to 80H after internal high-speed oscillator has been stabilized.

- 2. Bit 7 is read-only.

- Caution When setting RSTOP to 1, be sure to confirm that the CPU operates with a clock other than the internal high-speed oscillation clock. Specifically, set under either of the following conditions.

- When MCS = 1 (when CPU operates with the high-speed system clock)

- When CLS = 1 (when CPU operates with the subsystem clock)

In addition, stop peripheral hardware that is operating on the internal high-speed oscillation clock before setting RSTOP to 1.

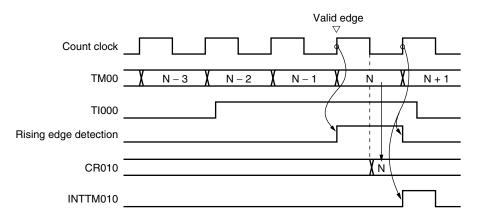

# Figure 6-7. Example of CR010 Capture Operation (When Rising Edge Is Specified)

# (3) 16-bit timer output control register 00 (TOC00)

TOC00 is an 8-bit register that controls TO00 output.

TOC00 can be rewritten while only OSPT00 is operating (when TMC003 and TMC002 = other than 00). Rewriting the other bits is prohibited during operation.

However, TOC004 can be rewritten during timer operation as a means to rewrite CR010 (see **6.5.1 Rewriting CR010 during TM00 operation**).

TOC00 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears TOC00 to 00H.

# Caution Be sure to set TOC00 using the following procedure.

<1> Set TOC004 and TOC001 to 1.

<2> Set only TOE00 to 1.

<3> Set either of LVS00 or LVR00 to 1.

# (4) Port mode registers 3 and 4 (PM3, PM4)

These registers set port 3 and 4 input/output in 1-bit units.

When using the P44/TO50/TI50/KR4 and P43/TO51/TI51/KR3 pins for timer output, clear PM44 and PM43 and the output latches of P44 and P43 to 0.

When using the P44/TO50/TI50/KR4, P43/TO51/TI51/KR3, and P34/TI52/TI010/TO00/RTC1HZ/INTP1 pins for timer input, set PM44, PM43, and PM34 to 1. The output latches of P44, PM43, and PM34 at this time may be 0 or 1.

PM3 and PM4 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

# Figure 7-13. Format of Port Mode Register 3 (PM3)

| Address: F | F23H A | After reset: FI | FH R/W                                  |      |      |      |      |   |  |

|------------|--------|-----------------|-----------------------------------------|------|------|------|------|---|--|

| Symbol     | 7      | 6               | 5                                       | 4    | 3    | 2    | 1    | 0 |  |

| PM3        | 1      | 1               | 1                                       | PM34 | PM33 | PM32 | PM31 | 1 |  |

|            |        |                 |                                         |      |      |      |      |   |  |

|            | PM3n   |                 | P1n pin I/O mode selection (n = 1 to 4) |      |      |      |      |   |  |

| 0 | Output mode (output buffer on) |

|---|--------------------------------|

| 1 | Input mode (output buffer off) |

|   |                                |

| Address: I | F24H A | After reset: FI | FH R/W |      |      |      |      |      |

|------------|--------|-----------------|--------|------|------|------|------|------|

| Symbol     | 7      | 6               | 5      | 4    | 3    | 2    | 1    | 0    |

| PM4        | 1      | 1               | 1      | PM44 | PM43 | PM42 | PM41 | PM40 |

|            |        | •               |        |      |      |      |      | •    |

| PM4n | P4n pin I/O mode selection (n = 0 to 4) |

|------|-----------------------------------------|

| 0    | Output mode (output buffer on)          |

| 1    | Input mode (output buffer off)          |

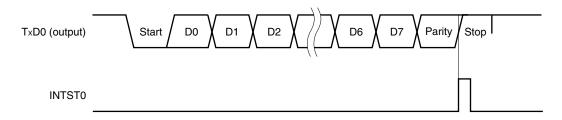

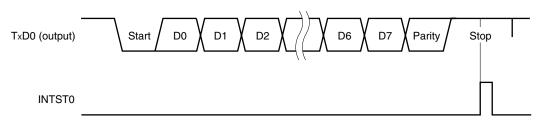

# (c) Transmission

If bit 7 (POWER0) of asynchronous serial interface operation mode register 0 (ASIM0) is set to 1 and bit 6 (TXE0) of ASIM0 is then set to 1, transmission is enabled. Transmission can be started by writing transmit data to transmit shift register 0 (TXS0). The start bit, parity bit, and stop bit are automatically appended to the data.

When transmission is started, the start bit is output from the TxD0 pin, and the transmit data is output followed by the rest of the data in order starting from the LSB. When transmission is completed, the parity and stop bits set by ASIM0 are appended and a transmission completion interrupt request (INTST0) is generated.

Transmission is stopped until the data to be transmitted next is written to TXS0.

Figure 14-9 shows the timing of the transmission completion interrupt request (INTST0). This interrupt occurs as soon as the last stop bit has been output.

# Caution After transmit data is written to TXS0, do not write the next transmit data before the transmission completion interrupt signal (INTST0) is generated.

# Figure 14-9. Transmission Completion Interrupt Request Timing

# 1. Stop bit length: 1

# 2. Stop bit length: 2

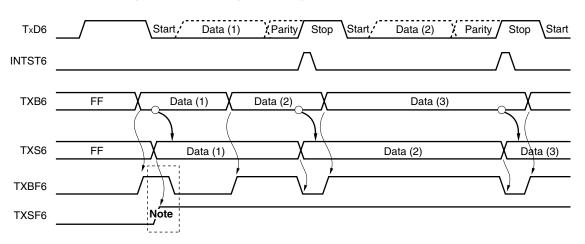

Figure 15-19 shows the timing of starting continuous transmission, and Figure 15-20 shows the timing of ending continuous transmission.

Figure 15-19. Timing of Starting Continuous Transmission

**Note** When ASIF6 is read, there is a period in which TXBF6 and TXSF6 = 1, 1. Therefore, judge whether writing is enabled using only the TXBF6 bit.

**Remark** TxD6: TxD6 pin (output)

- INTST6: Interrupt request signal

- TXB6: Transmit buffer register 6

- TXS6: Transmit shift register 6

- ASIF6: Asynchronous serial interface transmission status register 6

- TXBF6: Bit 1 of ASIF6

- TXSF6: Bit 0 of ASIF6

# 17.7 Display Modes

# 17.7.1 Static display example

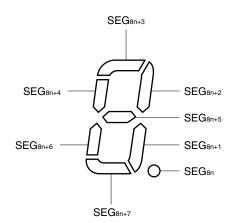

Figure 17-18 shows how the three-digit LCD panel having the display pattern shown in Figure 17-17 is connected to the segment signals (SEG0 to SEG23) and the common signal (COM0) of the 78K0/LE3 chip. This example displays data "12.3" in the LCD panel. The contents of the display data memory (FA40H to FA57H) correspond to this display.

The following description focuses on numeral "2." ( ⊇.) displayed in the second digit. To display "2." in the LCD panel, it is necessary to apply the select or deselect voltage to the SEG8 to SEG15 pins according to Table 17-6 at the timing of the common signal COM0; see **Figure 17-17** for the relationship between the segment signals and LCD segments.

Table 17-6. Select and Deselect Voltages (COM0)

| Segment | SEG8   | SEG9     | SEG10  | SEG11  | SEG12    | SEG13  | SEG14  | SEG15  |

|---------|--------|----------|--------|--------|----------|--------|--------|--------|

| Common  |        |          |        |        |          |        |        |        |

| COM0    | Select | Deselect | Select | Select | Deselect | Select | Select | Select |

According to Table 17-6, it is determined that the bit-0 pattern of the display data memory locations (FA48H to FA4FH) must be 10110111.

Figure 17-19 shows the LCD drive waveforms of SEG11 and SEG12, and COM0. When the select voltage is applied to SEG11 at the timing of COM0, an alternate rectangle waveform, +VLCD/-VLCD, is generated to turn on the corresponding LCD segment.

COM1 to COM3 are supplied with the same waveform as for COM0. So, COM0 to COM3 may be connected together to increase the driving capacity.

Remark n = 0 to 2

# 20.4 Interrupt Servicing Operations

#### 20.4.1 Maskable interrupt acknowledgment

A maskable interrupt becomes acknowledgeable when the interrupt request flag is set to 1 and the mask (MK) flag corresponding to that interrupt request is cleared to 0. A vectored interrupt request is acknowledged if interrupts are in the interrupt enabled state (when the IE flag is set to 1). However, a low-priority interrupt request is not acknowledged during servicing of a higher priority interrupt request (when the ISP flag is reset to 0).

The times from generation of a maskable interrupt request until vectored interrupt servicing is performed are listed in Table 20-4 below.

For the interrupt request acknowledgment timing, see Figures 20-8 and 20-9.

|                             | Minimum Time | Maximum Time <sup>Note</sup> |

|-----------------------------|--------------|------------------------------|

| When $\times \times PR = 0$ | 7 clocks     | 32 clocks                    |

| When ××PR = 1               | 8 clocks     | 33 clocks                    |

Table 20-4. Time from Generation of Maskable Interrupt Until Servicing

Note If an interrupt request is generated just before a divide instruction, the wait time becomes longer.

Remark 1 clock: 1/fcpu (fcpu: CPU clock)

If two or more maskable interrupt requests are generated simultaneously, the request with a higher priority level specified in the priority specification flag is acknowledged first. If two or more interrupts requests have the same priority level, the request with the highest default priority is acknowledged first.

An interrupt request that is held pending is acknowledged when it becomes acknowledgeable.

Figure 20-7 shows the interrupt request acknowledgment algorithm.

If a maskable interrupt request is acknowledged, the contents are saved into the stacks in the order of PSW, then PC, the IE flag is reset (0), and the contents of the priority specification flag corresponding to the acknowledged interrupt are transferred to the ISP flag. The vector table data determined for each interrupt request is the loaded into the PC and branched.

Restoring from an interrupt is possible by using the RETI instruction.

#### 20.4.3 Multiple interrupt servicing

Multiple interrupt servicing occurs when another interrupt request is acknowledged during execution of an interrupt. Multiple interrupt servicing does not occur unless the interrupt request acknowledgment enabled state is selected (IE = 1). When an interrupt request is acknowledged, interrupt request acknowledgment becomes disabled (IE = 0). Therefore, to enable multiple interrupt servicing, it is necessary to set (1) the IE flag with the EI instruction during interrupt servicing to enable interrupt acknowledgment.

Moreover, even if interrupts are enabled, multiple interrupt servicing may not be enabled, this being subject to interrupt priority control. Two types of priority control are available: default priority control and programmable priority control is used for multiple interrupt servicing.

In the interrupt enabled state, if an interrupt request with a priority equal to or higher than that of the interrupt currently being serviced is generated, it is acknowledged for multiple interrupt servicing. If an interrupt with a priority lower than that of the interrupt currently being serviced is generated during interrupt servicing, it is not acknowledged for multiple interrupt servicing. Interrupt requests that are not enabled because interrupts are in the interrupt disabled state or because they have a lower priority are held pending. When servicing of the current interrupt ends, the pending interrupt request is acknowledged following execution of at least one main processing instruction execution.

Table 20-5 shows relationship between interrupt requests enabled for multiple interrupt servicing and Figure 20-10 shows multiple interrupt servicing examples.

Table 20-5. Relationship Between Interrupt Requests Enabled for Multiple Interrupt Servicing

During Interrupt Servicing

| Multiple Interru         |         | Software |        |        |           |         |

|--------------------------|---------|----------|--------|--------|-----------|---------|

|                          | PR = 0  |          | PR = 1 |        | Interrupt |         |

| Interrupt Being Serviced |         | IE = 1   | IE = 0 | IE = 1 | IE = 0    | Request |

| Maskable interrupt       | ISP = 0 | 0        | ×      | ×      | ×         | 0       |

|                          | ISP = 1 | 0        | ×      | 0      | ×         | 0       |

| Software interrupt       |         | 0        | ×      | 0      | ×         | 0       |

Remarks 1. O: Multiple interrupt servicing enabled

- 2. x: Multiple interrupt servicing disabled

- 3. ISP and IE are flags contained in the PSW.

- ISP = 0: An interrupt with higher priority is being serviced.

- ISP = 1: No interrupt request has been acknowledged, or an interrupt with a lower priority is being serviced.

- IE = 0: Interrupt request acknowledgment is disabled.

- IE = 1: Interrupt request acknowledgment is enabled.

- 4. PR is a flag contained in PR0L, PR0H, PR1L, and PR1H.

- PR = 0: Higher priority level

- PR = 1: Lower priority level

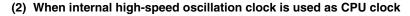

# (b) Release by reset signal generation

<R>

When the reset signal is generated, STOP mode is released, and then, as in the case with a normal reset operation, the program is executed after branching to the reset vector address.

#### STOP instruction ∯ Reset signal Reset Normal operation Normal operation processing (internal high-speed (high-speed Reset Status of CPU system clock) STOP mode period (19 to 80 µs oscillation clock) Oscillation Oscillation Oscillation stopped stopped stopped High-speed Oscillates Oscillates system clock (X1 oscillation) Oscillation stabilization time (2<sup>11</sup>/fx to 2<sup>16</sup>/fx) Starting X1 oscillation is specified by software.

### Figure 22-7. STOP Mode Release by Reset

#### (1) When high-speed system clock is used as CPU clock

Remark fx: X1 clock oscillation frequency

| Release Source                | MK×× | PR×× | IE | ISP | Operation                          |

|-------------------------------|------|------|----|-----|------------------------------------|

| Maskable interrupt<br>request | 0    | 0    | 0  | ×   | Next address instruction execution |

|                               | 0    | 0    | 1  | ×   | Interrupt servicing execution      |

|                               | 0    | 1    | 0  | 1   | Next address                       |

|                               | 0    | 1    | ×  | 0   | instruction execution              |

|                               | 0    | 1    | 1  | 1   | Interrupt servicing execution      |

|                               | 1    | ×    | ×  | ×   | STOP mode held                     |

| Reset                         | _    | _    | ×  | ×   | Reset processing                   |

×: don't care

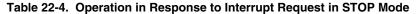

# 23.1 Register for Confirming Reset Source

Many internal reset generation sources exist in the 78K0/LE3. The reset control flag register (RESF) is used to store which source has generated the reset request.

RESF can be read by an 8-bit memory manipulation instruction.

RESET input, reset by power-on-clear (POC) circuit, and reading RESF set RESF to 00H.

### Figure 23-5. Format of Reset Control Flag Register (RESF)

| WDTRF | Internal reset request by watchdog timer (WDT)               |

|-------|--------------------------------------------------------------|

| 0     | Internal reset request is not generated, or RESF is cleared. |

| 1     | Internal reset request is generated.                         |

| LVIRF | Internal reset request by low-voltage detector (LVI)         |

|-------|--------------------------------------------------------------|

| 0     | Internal reset request is not generated, or RESF is cleared. |

| 1     | Internal reset request is generated.                         |

Note The value after reset varies depending on the reset source.

#### Caution Do not read data by a 1-bit memory manipulation instruction.

The status of RESF when a reset request is generated is shown in Table 23-3.

Table 23-3. RESF Status When Reset Request Is Generated

| Reset Source | RESET Input | Reset by POC | Reset by WDT | Reset by LVI |

|--------------|-------------|--------------|--------------|--------------|

| Flag         |             |              |              |              |

| WDTRF        | Cleared (0) | Cleared (0)  | Set (1)      | Held         |

| LVIRF        |             |              | Held         | Set (1)      |

# (3) Port mode register 12 (PM12)

When using the P120/EXLVI/INTP0 pin for external low-voltage detection potential input, set PM120 to 1. At this time, the output latch of P120 may be 0 or 1.

PM12 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets PM12 to FFH.

# Figure 25-4. Format of Port Mode Register 12 (PM12)

| Address: | FF2CH | After reset: FFH | H R/W |   |   |   |   |       |

|----------|-------|------------------|-------|---|---|---|---|-------|

| Symbol   | 7     | 6                | 5     | 4 | 3 | 2 | 1 | 0     |

| PM12     | 1     | 1                | 1     | 1 | 1 | 1 | 1 | PM120 |

| PM120 | P120 pin I/O mode selection    |  |  |  |  |

|-------|--------------------------------|--|--|--|--|

| 0     | Output mode (output buffer on) |  |  |  |  |

| 1     | Input mode (output buffer off) |  |  |  |  |

# 25.4 Operation of Low-Voltage Detector

The low-voltage detector can be used in the following two modes.

# (1) Used as reset (LVIMD = 1)

- If LVISEL = 0, compares the supply voltage (V<sub>DD</sub>) and detection voltage (V<sub>LVI</sub>), generates an internal reset signal when V<sub>DD</sub> < V<sub>LVI</sub>, and releases internal reset when V<sub>DD</sub> ≥ V<sub>LVI</sub>.

- If LVISEL = 1, compares the input voltage from external input pin (EXLVI) and detection voltage (VEXLVI = 1.21 V (TYP.)), generates an internal reset signal when EXLVI < VEXLVI, and releases internal reset when EXLVI ≥ VEXLVI.</li>

# (2) Used as interrupt (LVIMD = 0)

- If LVISEL = 0, compares the supply voltage (VDD) and detection voltage (VLVI). When VDD drops lower than VLVI (VDD < VLVI) or when VDD becomes VLVI or higher (VDD ≥ VLVI), generates an interrupt signal (INTLVI).</li>

- If LVISEL = 1, compares the input voltage from external input pin (EXLVI) and detection voltage (VEXLVI = 1.21 V (TYP.)). When EXLVI drops lower than VEXLVI (EXLVI < VEXLVI) or when EXLVI becomes VEXLVI or higher (EXLVI ≥ VEXLVI), generates an interrupt signal (INTLVI).</li>

While the low-voltage detector is operating, whether the supply voltage or the input voltage from an external input pin is more than or less than the detection level can be checked by reading the low-voltage detection flag (LVIF: bit 0 of LVIM).

Remark LVIMD: Bit 1 of low-voltage detection register (LVIM) LVISEL: Bit 2 of LVIM

# (2) When detecting level of input voltage from external input pin (EXLVI)

- When starting operation

- <1> Mask the LVI interrupt (LVIMK = 1).

- <2> Set bit 2 (LVISEL) of the low-voltage detection register (LVIM) to 1 (detects level of input voltage from external input pin (EXLVI)).

- <3> Set bit 7 (LVION) of LVIM to 1 (enables LVI operation).

- <4> Use software to wait for an operation stabilization time (10  $\mu$ s (MAX.)).

- <5> Confirm that "input voltage from external input pin (EXLVI) ≥ detection voltage (V<sub>EXLVI</sub> = 1.21 V (TYP.)" when detecting the falling edge of EXLVI, or "input voltage from external input pin (EXLVI) < detection voltage (V<sub>EXLVI</sub> = 1.21 V (TYP.)" when detecting the rising edge of EXLVI, at bit 0 (LVIF) of LVIM.

- <6> Clear the interrupt request flag of LVI (LVIIF) to 0.

- <7> Release the interrupt mask flag of LVI (LVIMK).

- <8> Clear bit 1 (LVIMD) of LVIM to 0 (generates interrupt signal when the level is detected) (default value).

- <9> Execute the El instruction (when vector interrupts are used).

Figure 25-8 shows the timing of the interrupt signal generated by the low-voltage detector. The numbers in this timing chart correspond to <1> to <8> above.

# Caution Input voltage from external input pin (EXLVI) must be EXLVI < VDD.

- When stopping operation

Either of the following procedures must be executed.

- When using 8-bit memory manipulation instruction: Write 00H to LVIM.

- When using 1-bit memory manipulation instruction: Clear LVION to 0.

# 27.3 Writing with Flash memory programmer

Data can be written to the flash memory on-board or off-board, by using a dedicated flash memory programmer.

# (1) On-board programming

The contents of the flash memory can be rewritten after the 78K0/LE3 has been mounted on the target system. The connectors that connect the dedicated flash memory programmer must be mounted on the target system.

# (2) Off-board programming

Data can be written to the flash memory with a dedicated program adapter (FA series) before the 78K0/LE3 is mounted on the target system.

**Remark** The FA series is a product of Naito Densei Machida Mfg. Co., Ltd.

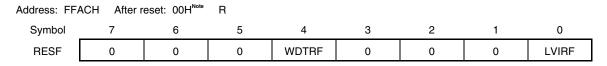

# Table 27-3. Wiring Between 78K0/LE3 and Dedicated Flash memory programmer

| Pin Configuratior | n of Dedicate | ed Flash memory programmer | With CSI10                       | )       | With UART               | 6       |

|-------------------|---------------|----------------------------|----------------------------------|---------|-------------------------|---------|

| Signal Name       | I/O           | Pin Function               | Pin Name                         | Pin No. | Pin Name                | Pin No. |

| SI/RxD            | Input         | Receive signal             | SO10/TxD0<br>/ <txd6>/P13</txd6> | 62      | TxD6/SEG14/P112         | 28      |

| SO/TxD            | Output        | Transmit signal            | SI10/RxD0<br>/ <rxd6>/P12</rxd6> | 63      | RxD6/SEG15/P113         | 27      |

| SCK               | Output        | Transfer clock             | SCK10/P11                        | 64      | -                       | -       |

| CLK               | Output        | Clock to 78K0/LE3          | _Note 1                          | -       | Note 2                  | Note 2  |

| /RESET            | Output        | Reset signal               | RESET                            | 10      | RESET                   | 10      |

| FLMD0             | Output        | Mode signal                | FLMD0                            | 13      | FLMD0                   | 13      |

| VDD               | I/O           | VDD voltage generation/    | VDD                              | 18      | VDD                     | 18      |

|                   |               | power monitoring           | VDD <sup>Note 3</sup>            | 47      | VDD <sup>Note 3</sup>   | 47      |

|                   |               |                            | AVREF <sup>Note 4</sup>          |         | AVREF <sup>Note 4</sup> |         |

| GND               | _             | Ground                     | Vss                              | 17      | Vss                     | 17      |

|                   |               |                            | Vss <sup>Note 3</sup>            | 48      | Vss <sup>Note 3</sup>   | 48      |

|                   |               |                            | AVss <sup>Note 4</sup>           |         | AVss <sup>Note 4</sup>  |         |

Notes 1. Only the internal high-speed oscillation clock (fRH) can be used when CSI10 is used.

2. Only the X1 clock (fx), external main system clock (fexcLk), or internal high-speed oscillation clock (fRH) can be used when UART6 is used. When using the clock output of the dedicated flash memory programmer, connect CLK of the PG-FP5 or FL-PR5 to EXCLK/X2/P122 (pin number 14).

**3.** *μ*PD78F044x only.

**4.** *μ*PD78F045x and 78F046x only.

<R>

<R>

Caution Only the bottom side pins (pin numbers 27 and 28) correspond to the UART6 pins (RxD6 and TxD6) when writing by a flash memory programmer. Writing cannot be performed by the top side pins (pin numbers 63 and 62).

| Function Name              | Interrupt Response Time (Unit: μs) |                    |                          |                 |                                               |                          |  |  |  |

|----------------------------|------------------------------------|--------------------|--------------------------|-----------------|-----------------------------------------------|--------------------------|--|--|--|

|                            | When entry RA                      | M is allocated out | side short direct        | When entry RA   | When entry RAM is allocated within short dire |                          |  |  |  |

|                            |                                    | addressing range   | 1                        |                 | addressing range                              |                          |  |  |  |

|                            | RSTOP = 0 a                        | ind RSTS = 1       | RSTOP = 1                | RSTOP = 0 a     | and RSTS = $1$                                | RSTOP = 1                |  |  |  |

|                            | (during stable                     | e operation of     | (internal                | (during stable  | e operation of                                | (internal                |  |  |  |

|                            | internal high-sp                   | peed oscillator)   | high-speed               | internal high-s | peed oscillator)                              | high-speed               |  |  |  |

|                            |                                    |                    | oscillator               |                 |                                               | oscillator               |  |  |  |

|                            |                                    |                    | stopped) <sup>Note</sup> |                 | r                                             | stopped) <sup>Note</sup> |  |  |  |

|                            | MCS = 0                            | MCS = 1            | MCS = 1                  | MCS = 0         | MCS = 1                                       | MCS = 1                  |  |  |  |

|                            | (CPU operates                      | (CPU operates      | (CPU operates            | (CPU operates   | (CPU operates                                 | (CPU operates            |  |  |  |

|                            | with internal                      | with               | with                     | with internal   | with                                          | with                     |  |  |  |

|                            | high-speed                         | high-speed         | high-speed               | high-speed      | high-speed                                    | high-speed               |  |  |  |

|                            | oscillation                        | system clock)      | system clock)            | oscillation     | system clock)                                 | system clock)            |  |  |  |

|                            | clock)                             |                    |                          | clock)          |                                               |                          |  |  |  |

| Block erase function       | 179/fcpu+1269                      | 179/fcpu+1269      | 179/fcpu+1912            | 179/fcpu+703    | 179/fcpu+703                                  | 179/fcpu+713             |  |  |  |

| Word write function        | 333/fcpu+1098                      | 333/fcpu+1098      | 333/fcpu+1742            | 333/fcpu+533    | 333/fcpu+533                                  | 333/fcpu+543             |  |  |  |

| Block verify function      | 179/fcpu+1013                      | 179/fcpu+1013      | 179/fcpu+1656            | 179/fcpu+448    | 179/fcpu+448                                  | 179/fcpu+456             |  |  |  |

| Block blank check function | 179/fcpu+993                       | 179/fcpu+993       | 179/fcpu+1637            | 179/fcpu+428    | 179/fcpu+428                                  | 179/fcpu+438             |  |  |  |

| Set information function   | 80/fcpu+833                        | 80/fcpu+833        | 80/fcpu+1477             | 80/fcpu+346     | 80/fcpu+346                                   | 80/fcpu+346              |  |  |  |

| EEPROM write function      | 333/fcpu+1107                      | 333/fcpu+1107      | 333/fcpu+1751            | 333/fcpu+542    | 333/fcpu+542                                  | 333/fcpu+552             |  |  |  |

# Table 27-14. Interrupt Response Time (Library for Normal Model) (1/2)

- **Note** This is the function processing time when the function is executed immediately after the self programming start function has been executed. The processing time after a function other than the self programming start function has been executed is the same as that of RSTOP = 0.

- Remark RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- RSTS: Bit 7 of RCM

- MCS: Bit 1 of main clock mode register (MCM)

- fcpu: CPU clock frequency

- W: Number of words to be written (1 word = 4 bytes)

Connect the FLMD0 pin as follows when performing self programming by means of on-chip debugging.

# Figure 28-2. Connection of FLMD0 Pin for Self Programming by Means of On-Chip Debugging

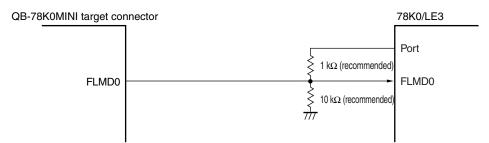

# 28.2 Reserved Area Used by QB-MINI2

QB-MINI2 uses the reserved areas shown in Figure 28-3 below to implement communication with the 78K0/LE3, or each debug function. The shaded reserved areas are used for the respective debug functions to be used, and the other areas are always used for debugging. These reserved areas can be secured by using user programs and compiler options.

When using a boot swap operation during self programming, set the same value to boot cluster 1 beforehand. For details on reserved area, refer to **QB-MINI2 User's Manual (U18371E)**.

#### Figure 28-3. Reserved Area Used by QB-MINI2

Remark Shaded reserved areas: Area used for the respective debug functions to be used Other reserved areas: Areas always used for debugging

Standard products

# X1 Oscillator Characteristics

# (TA = -40 to +85°C, 1.8 V $\leq$ VDD $\leq$ 5.5 V, Vss = AVss = 0 V)

| Resonator            | Recommended Circuit | Parameter                                                 | Conditions                                         | MIN. | TYP. | MAX. | Unit |

|----------------------|---------------------|-----------------------------------------------------------|----------------------------------------------------|------|------|------|------|

| Ceramic<br>resonator |                     | X1 clock<br>oscillation<br>frequency (fx) <sup>Note</sup> | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$              | 2.0  |      | 10.0 | MHz  |

|                      |                     |                                                           | $1.8 \text{ V} \leq V_{\text{DD}} < 2.7 \text{ V}$ | 2.0  |      | 5.0  |      |

| Crystal<br>resonator |                     | X1 clock<br>oscillation<br>frequency (fx) <sup>Note</sup> | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$              | 2.0  |      | 10.0 | MHz  |

|                      |                     |                                                           | $1.8 \text{ V} \leq V_{\text{DD}} < 2.7 \text{ V}$ | 2.0  |      | 5.0  |      |

Note Indicates only oscillator characteristics. Refer to AC Characteristics for instruction execution time.

# Cautions 1. When using the X1 oscillator, wire as follows in the area enclosed by the broken lines in the above figures to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines.

- Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss.

- Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

- 2. Since the CPU is started by the internal high-speed oscillation clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

Standard products

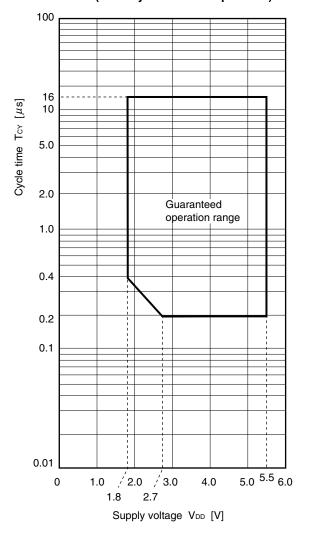

TCY vs. VDD (Main System Clock Operation)

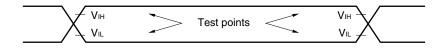

AC Timing Test Points (Excluding External Main System Clock)

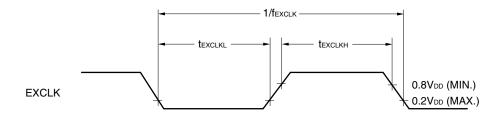

**External Main System Clock Timing**

# Standard products

# (2) Serial interface

(TA = -40 to +85°C, 1.8 V  $\leq$  VDD  $\leq$  5.5 V, Vss = AVss = 0 V)

| Parameter     | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|---------------|--------|------------|------|------|------|------|

| Transfer rate |        |            |      |      | 250  | kbps |

### (3) Serial interface

(TA = -40 to +85°C, 1.8 V  $\leq$  V dd  $\leq$  5.5 V, Vss = AVss = 0 V)

### (a) UART6 (Dedicated baud rate generator output)

| Parameter     | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|---------------|--------|------------|------|------|------|------|

| Transfer rate |        |            |      |      | 625  | kbps |

# (b) UART0 (Dedicated baud rate generator output)

| Parameter     | Symbol | Conditions | MIN. | TYP. | MAX. | Unit |

|---------------|--------|------------|------|------|------|------|

| Transfer rate |        |            |      |      | 625  | kbps |