# E. Renesas Electronics America Inc - UPD78F0461GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 46                                                                                   |

| Program Memory Size        | 16KB (16K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 768 x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b, 3x16b                                                                     |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0461gb-gah-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

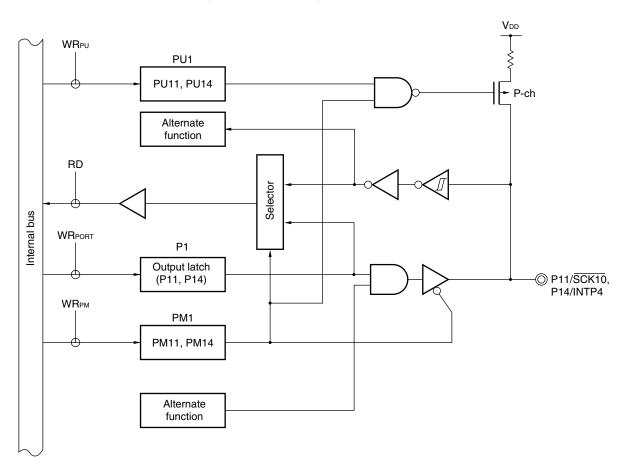

# 4.2.1 Port 1

Port 1 is a 4-bit I/O port with an output latch. Port 1 can be set to the input mode or output mode in 1-bit units using port mode register 1 (PM1). When the P11 to P14 pins are used as an input port, use of an on-chip pull-up resistor can be specified in 1-bit units by pull-up resistor option register 1 (PU1).

This port can also be used for serial clock I/O, serial interface data I/O, and maskable external interrupt input.

Reset signal generation sets port 1 to input mode.

Figures 4-2 to 4-4 show block diagrams of port 1.

Caution To use P11/SCK10, P12/SI10/RxD0/<RxD6>, and P13/SO10/TxD0/<TxD6> as general-purpose ports, set serial operation mode register 10 (CSIM10) and serial clock selection register 10 (CSIC10) to the default status (00H).

Figure 4-2. Block Diagram of P11 and P14

- P1: Port register 1

- PU1: Pull-up resistor option register 1

- PM1: Port mode register 1

- RD: Read signal

- WR××: Write signal

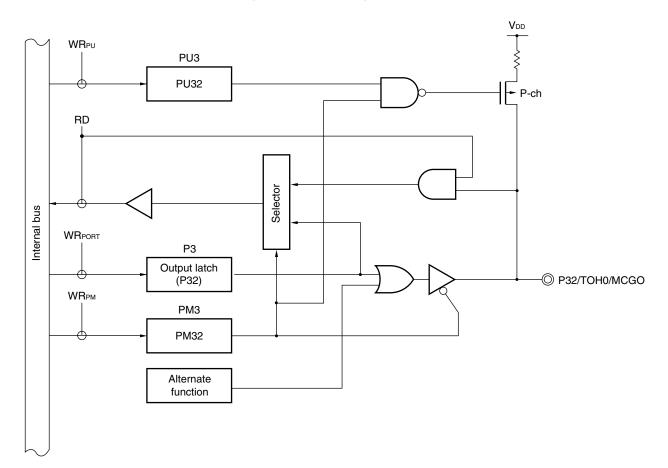

Figure 4-7. Block Diagram of P32

- P3: Port register 3

- PU3: Pull-up resistor option register 3

- PM3: Port mode register 3

- RD: Read signal

- WR××: Write signal

- Remarks 1. fx: X1 clock oscillation frequency

- 2. free: Internal high-speed oscillation clock frequency

- 3. fexclk: External main system clock frequency

- 4. fxH: High-speed system clock frequency

- 5. fxp: Main system clock frequency

- 6. fprs: Peripheral hardware clock frequency

- 7. fcpu: CPU clock frequency

- 8. fxT: XT1 clock oscillation frequency

- **9.** fsub: Subsystem clock frequency

- **10.** fRL: Internal low-speed oscillation clock frequency

# 5.3 Registers Controlling Clock Generator

The following eight registers are used to control the clock generator.

- Clock operation mode select register (OSCCTL)

- Processor clock control register (PCC)

- Internal oscillation mode register (RCM)

- Main OSC control register (MOC)

- Main clock mode register (MCM)

- Oscillation stabilization time counter status register (OSTC)

- Oscillation stabilization time select register (OSTS)

- Internal high-speed oscillation trimming register (HIOTRM)

# (1) Clock operation mode select register (OSCCTL)

This register selects the operation modes of the high-speed system and subsystem clocks, and the gain of the on-chip oscillator.

OSCCTL can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation clears this register to 00H.

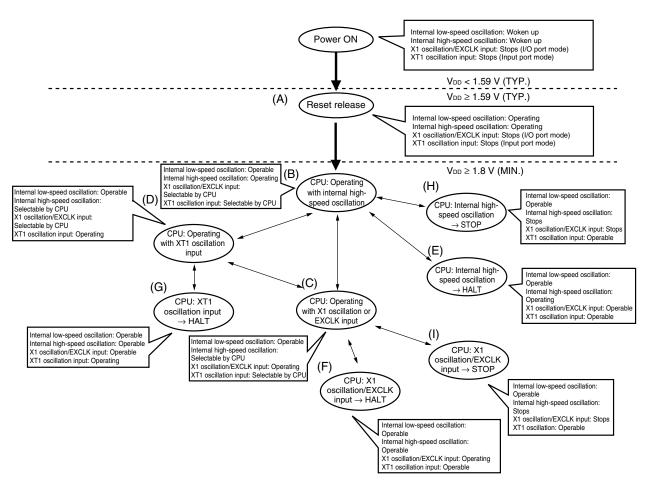

#### 5.6.6 CPU clock status transition diagram

Figure 5-15 shows the CPU clock status transition diagram of this product.

# Figure 5-15. CPU Clock Status Transition Diagram (When 1.59 V POC Mode Is Set (Option Byte: POCMODE = 0))

**Remark** In the 2.7 V/1.59 V POC mode (option byte: POCMODE = 1), the CPU clock status changes to (A) in the above figure when the supply voltage exceeds 2.7 V (TYP.), and to (B) after reset processing (11 to 47  $\mu$ s (TYP.)).

# 6.3 Registers Controlling 16-Bit Timer/Event Counter 00

Registers used to control 16-bit timer/event counter 00 are shown below.

- 16-bit timer mode control register 00 (TMC00)

- Capture/compare control register 00 (CRC00)

- 16-bit timer output control register 00 (TOC00)

- Prescaler mode register 00 (PRM00)

- Input switch control register (ISC)

- Port mode register 3 (PM3)

- Port register 3 (P3)

#### (1) 16-bit timer mode control register 00 (TMC00)

TMC00 is an 8-bit register that sets the 16-bit timer/event counter 00 operation mode, TM00 clear mode, and output timing, and detects an overflow.

Rewriting TMC00 is prohibited during operation (when TMC003 and TMC002 = other than 00). However, it can be changed when TMC003 and TMC002 are cleared to 00 (stopping operation) and when OVF00 is cleared to 0. TMC00 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets TMC00 to 00H.

# Caution 16-bit timer/event counter 00 starts operation at the moment TMC002 and TMC003 are set to values other than 00 (operation stop mode), respectively. Set TMC002 and TMC003 to 00 to stop the operation.

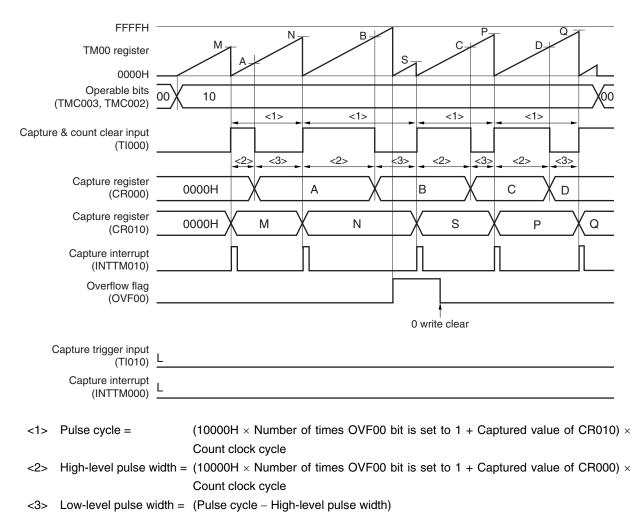

(3) Measuring the pulse width by using one input signal of the TI000 pin (clear & start mode entered by the TI000 pin valid edge input)

Set the clear & start mode entered by the TI000 pin valid edge (TMC003 and TMC002 = 10). The count value of TM00 is captured to CR000 in the phase reverse to the valid edge of the TI000 pin, and the count value of TM00 is captured to CR010 and TM00 is cleared (0000H) when the valid edge of the TI000 pin is detected. Therefore, a cycle is stored in CR010 if TM00 does not overflow.

If an overflow occurs, take the value that results from adding 10000H to the value stored in CR010 as a cycle. Clear bit 0 (OVF00) of 16-bit timer mode control register 00 (TMC00) to 0.

# Figure 6-51. Timing Example of Pulse Width Measurement (3)

# • TMC00 = 08H, PRM00 = 10H, CRC00 = 07H

#### (1) PWM output basic operation

# Setting

<1> Set each register.

- Clear the port output latch (P44 or P43)<sup>Note</sup> and port mode register (PM44 or PM43)<sup>Note</sup> to 0.

- TCL5n: Select the count clock.

- CR5n: Compare value

- TMC5n: Stop the count operation, select PWM mode.

The timer output F/F is not changed.

| TMC5n1 | Active Level Selection |

|--------|------------------------|

| 0      | Active-high            |

| 1      | Active-low             |

Timer output enabled

(TMC5n = 01000001B or 01000011B)

- <2> The count operation starts when TCE5n = 1. Clear TCE5n to 0 to stop the count operation.

- Note 8-bit timer/event counter 50: P44, PM43 8-bit timer/event counter 51: P43, PM43

#### PWM output operation

- <1> PWM output (output from TO5n) outputs an inactive level until an overflow occurs.

- <2> When an overflow occurs, the active level is output. The active level is output until CR5n matches the count value of 8-bit timer counter 5n (TM5n).

- <3> After the CR5n matches the count value, the inactive level is output until an overflow occurs again.

- <4> Operations <2> and <3> are repeated until the count operation stops.

<5> When the count operation is stopped with TCE5n = 0, PWM output becomes inactive. For details of timing, see **Figures 7-18** and **7-19**.

The cycle, active-level width, and duty are as follows.

- Cycle =  $2^{8}t$

- Active-level width = Nt

- Duty = N/2<sup>8</sup>

(N = 00H to FFH)

**Remark** n = 0, 1

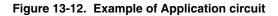

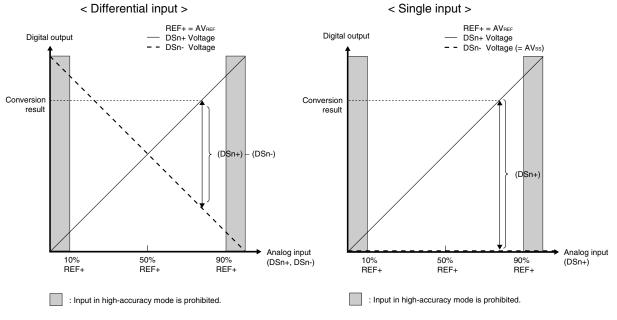

|                    |                        | Input Voltage Range to DSn+                | Input Voltage Range to DSn-     |

|--------------------|------------------------|--------------------------------------------|---------------------------------|

| Differential input | High-accuracy mode ON  | 0.5 × (REF+) + X1                          | $0.5 \times (\text{REF+}) - X1$ |

|                    | High-accuracy mode OFF | 0.5 × (REF+) + X2                          | 0.5 × (REF+) – X2               |

| Single input       | High-accuracy mode ON  | 0.1 $\times$ (REF+) to 0.9 $\times$ (REF+) | Fixed to AVss                   |

|                    | High-accuracy mode OFF | 0 to REF+                                  |                                 |

Table 13-4. Input Voltage Range

**Remark**  $X1 = -0.4 \times (REF+)$  to  $0.4 \times (REF+)$

$X2 = -0.5 \times (REF+) \text{ to } 0.5 \times (REF+)$

n = 0 to 2

Figure 13-13. Enabled input range by A/D converter mode

**Remark** n = 0 to 2

# (2) Serial clock selection register 10 (CSIC10)

This register specifies the timing of the data transmission/reception and sets the serial clock. CSIC10 can be set by a 1-bit or 8-bit memory manipulation instruction. Reset signal generation sets this register to 00H.

# Figure 16-3. Format of Serial Clock Selection Register 10 (CSIC10)

Address: FF81H After reset: 00H R/W

| Symbol | 7     | 6     | 5         | 4                                     | 3                                | 2                                            | 1            | 0      |

|--------|-------|-------|-----------|---------------------------------------|----------------------------------|----------------------------------------------|--------------|--------|

| CSIC10 | 0     | 0     | 0         | CKP10                                 | DAP10                            | CKS102                                       | CKS101       | CKS100 |

|        |       |       |           |                                       |                                  |                                              |              |        |

|        | CKP10 | DAP10 | Sp        | ecification of da                     | ata transmissio                  | n/reception tim                              | ning         | Туре   |

|        | 0     | 0     | SI10 inpu | SCK10<br>SO10<br>ut timing            |                                  | <u>□</u><br>D4(\D3(\D2)<br>                  |              | 1      |

|        | 0     | 1     | SI10 inpu | SCK10<br>SO10 XD7<br>ut timing        |                                  |                                              |              | 2      |

|        | 1     | 0     | SI10 inpu | SCK10 SO10 SO10                       |                                  | <u>↓</u> ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ |              | 3      |

|        | 1     | 1     | SI10 inpu | SCK10<br>SO10 <u>XD7</u><br>ut timing | <u>↓</u> <u>↓</u><br><u>↓</u> ↓↓ | <u>\</u><br><u>\$XD3XD2XD</u><br>            | 1 <u>χρο</u> | 4      |

| CKS102 | CKS101 | CKS100 |                                                               | CSI10 serial clock selection <sup>Notes 1, 2</sup>    |                             |                             |                              |  |  |  |  |

|--------|--------|--------|---------------------------------------------------------------|-------------------------------------------------------|-----------------------------|-----------------------------|------------------------------|--|--|--|--|

|        |        |        |                                                               | f <sub>PRS</sub> =<br>2 MHz                           | f <sub>PRS</sub> =<br>5 MHz | f <sub>PRS</sub> =<br>8 MHz | f <sub>PRS</sub> =<br>10 MHz |  |  |  |  |

| 0      | 0      | 0      | f <sub>PRS</sub> /2 1 MHz 2.5 MHz 4 MHz Setting<br>prohibited |                                                       | Master mode                 |                             |                              |  |  |  |  |

| 0      | 0      | 1      | $f_{PRS}/2^2$                                                 | 500 kHz                                               | 1.25 MHz                    | 2 MHz                       | 2.5 MHz                      |  |  |  |  |

| 0      | 1      | 0      | fprs/2 <sup>3</sup>                                           | 250 kHz                                               | 625 kHz                     | 1 MHz                       | 1.25 MHz                     |  |  |  |  |

| 0      | 1      | 1      | fprs/24                                                       | 125 kHz                                               | 312.5 kHz                   | 500 kHz                     | 625 kHz                      |  |  |  |  |

| 1      | 0      | 0      | fprs/2⁵                                                       | 62.5 kHz                                              | 156.25 kHz                  | 250 kHz                     | 312.5 kHz                    |  |  |  |  |

| 1      | 0      | 1      | fprs/2 <sup>6</sup>                                           | fprss/2 <sup>6</sup> 31.25 kHz 78.13 kHz <sup>-</sup> |                             | 125 kHz                     | 156.25 kHz                   |  |  |  |  |

| 1      | 1      | 0      | fprs/27                                                       | 15.63 kHz                                             | 39.06 kHz                   | 62.5 kHz                    | 78.13 kHz                    |  |  |  |  |

| 1      | 1      | 1      | Externa                                                       | al clock input                                        |                             | Slave mode                  |                              |  |  |  |  |

**Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

- VDD = 2.7 to 5.5 V: fPRs  $\leq$  10 MHz

- VDD = 1.8 to 2.7 V: fPRS  $\leq$  5 MHz

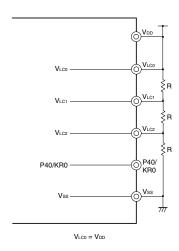

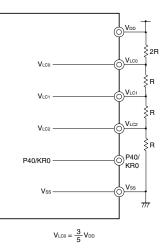

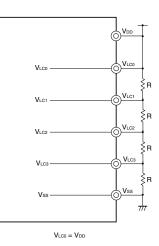

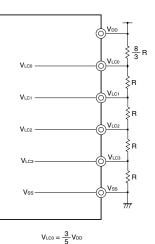

Figure 17-40. Examples of LCD Drive Power Connections (External Resistance Division Method) (2/2)

(e) 1/3 bias method (MDSET1, MDSET0 = 0, 0) (example of V<sub>DD</sub> = 5 V, V<sub>LC0</sub> = 5 V)

(f) 1/3 bias method (MDSET1, MDSET0 = 0, 0) (example of V<sub>DD</sub> = 5 V, V<sub>LC0</sub> = 3 V)

(g) 1/4 bias method (MDSET1, MDSET0 = 0, 0) (example of V<sub>DD</sub> = 5 V, V<sub>LC0</sub> = 5 V)

(h) 1/4 bias method

(MDSET1, MDSET0 = 0, 0)

(example of V<sub>DD</sub> = 5 V, V<sub>LC0</sub> = 3 V)

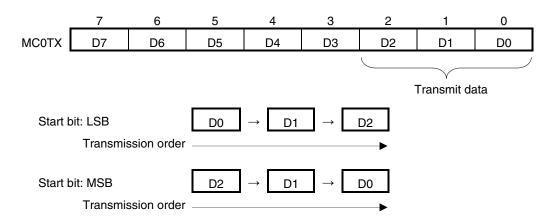

#### (2) MCG transmit bit count specification register (MC0BIT)

This register is used to set the number of transmit bits.

Set the transmit bit count to this register before setting the transmit data to MC0TX.

In continuous transmission, the number of transmit bits to be transmitted next needs to be written after the occurrence of a transmission start interrupt (INTMCG). However, if the next transmit count is the same number as the previous transmit count, this register does not need to be written.

This register can be set by an 8-bit memory manipulation instruction.

Reset signal generation sets this register to 07H.

# Figure 18-3. Format of MCG Transmit Bit Count Specification Register (MC0BIT)

| Address: FF4 | BH After re | set: 07H | R/W |   |   |         |         |         |

|--------------|-------------|----------|-----|---|---|---------|---------|---------|

| Symbol       | 7           | 6        | 5   | 4 | 3 | <2>     | <1>     | <0>     |

| MCOBIT       | 0           | 0        | 0   | 0 | 0 | MC0BIT2 | MC0BIT1 | MC0BIT0 |

| MC0BIT2 | MC0BIT1 | MC0BIT0 | Transmit bit count setting |

|---------|---------|---------|----------------------------|

| 0       | 0       | 0       | 1 bit                      |

| 0       | 0       | 1       | 2 bits                     |

| 0       | 1       | 0       | 3 bits                     |

| 0       | 1       | 1       | 4 bits                     |

| 1       | 0       | 0       | 5 bits                     |

| 1       | 0       | 1       | 6 bits                     |

| 1       | 1       | 0       | 7 bits                     |

| 1       | 1       | 1       | 8 bits                     |

- **Remark** When the number of transmit bits is set as 7 bits or smaller, the lower bits are always transmitted regardless of MSB/LSB settings as the transmission start bit.

- ex. When the number of transmit bits is set as 3 bits, and D7 to D0 are written to MCG transmit buffer register (MC0TX)

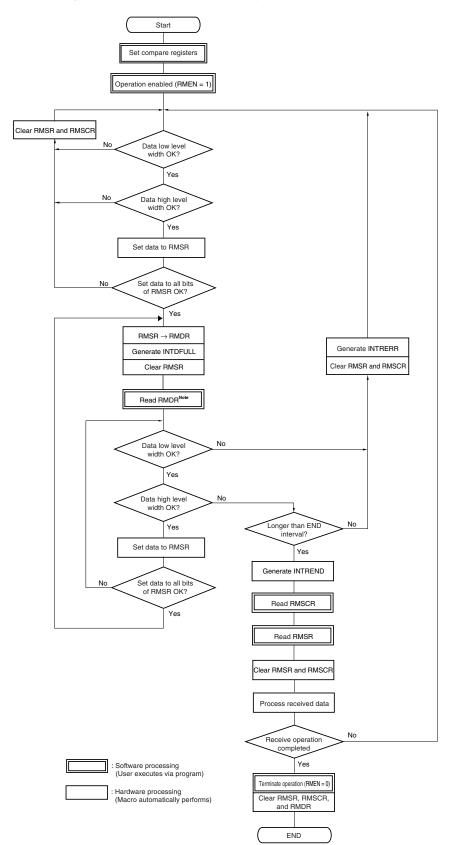

Figure 19-11. Operation Flow of Type C Reception Mode

- <1> <2> <3> <4> <5>  $\text{RIN}^{\text{Note}}$  ,  $\overline{\text{RIN}}^{\text{Note}}$  $\mathsf{RIN}^{\mathsf{Note}},\,\overline{\mathsf{RIN}}^{\,\mathsf{Note}}$  $RIN^{Note}, \overline{RIN}^{Note}$  $\mathsf{RIN}^{\mathsf{Note}}, \overline{\mathsf{RIN}}^{\mathsf{Note}}$  $\mathsf{RIN}^{\mathsf{Note}}, \overline{\mathsf{RIN}}^{\mathsf{Note}}$ **RMDH0S RMDH0L** RMDH1S RMDH1L Allowable Allowable range range Λ

- (4) Data high level width determination

# **Note** RIN is generated in type A reception mode, and RIN is generated in type B and type C reception modes.

| Relationship Between<br>RMDH0S/RMDH0L/RMDH1S/RMDH1L/Counter | Position of Waveform      | Corresponding Operation                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Counter < RMDH0S                                            | <1>: Short                | Error interrupt INTRERR is generated.<br>Measuring the guide pulse high-level width is started<br>at the next rising edge.                                                                                                                                                                                |

| $RMDH0S \le counter < RMDH0L$                               | <2>: Within the range     | Data 0 is received.<br>Measuring data low-level width is started.                                                                                                                                                                                                                                         |

| RMDH0L ≤ counter < RMDH1S                                   | <3>: Outside of the range | Error interrupt INTRERR is generated.<br>Measuring the guide pulse high-level width is started<br>at the next rising edge.                                                                                                                                                                                |

| $RMDH1S \leq counter < RMDH1L$                              | <4>: Within the range     | Data 1 is received.<br>Measuring the data low-level width is started.                                                                                                                                                                                                                                     |

| RMDH1L ≤ counter                                            | <5>: Long                 | <ul> <li>(Type A reception mode)</li> <li>Error interrupt INTRERR is generated at the ∆ point.</li> <li>(Type B, Type C reception modes)</li> <li>Measuring the end width is started from the ∆ point.</li> <li>Measuring the guide pulse high-level width is started at the next rising edge.</li> </ul> |

**Note** In type C reception mode, before the first INTDFULL interrupt is generated, INTRERR will not be generated. However, RMSR and RMSCR will be cleared.

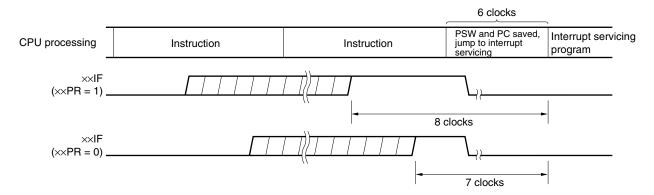

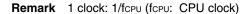

# Figure 20-8. Interrupt Request Acknowledgment Timing (Minimum Time)

Remark 1 clock: 1/fcpu (fcpu: CPU clock)

#### 20.4.2 Software interrupt request acknowledgment

A software interrupt acknowledge is acknowledged by BRK instruction execution. Software interrupts cannot be disabled.

If a software interrupt request is acknowledged, the contents are saved into the stacks in the order of the program status word (PSW), then program counter (PC), the IE flag is reset (0), and the contents of the vector table (003EH, 003FH) are loaded into the PC and branched.

Restoring from a software interrupt is possible by using the RETB instruction.

# Caution Do not use the RETI instruction for restoring from the software interrupt.

# 25.5 Cautions for Low-Voltage Detector

In a system where the supply voltage ( $V_{DD}$ ) fluctuates for a certain period in the vicinity of the LVI detection voltage ( $V_{LVI}$ ), the operation is as follows depending on how the low-voltage detector is used.

#### (1) When used as reset

The system may be repeatedly reset and released from the reset status. In this case, the time from release of reset to the start of the operation of the microcontroller can be arbitrarily set by taking action (1) below.

#### (2) When used as interrupt

Interrupt requests may be frequently generated. Take (b) of action (2) below.

<Action>

# (1) When used as reset

After releasing the reset signal, wait for the supply voltage fluctuation period of each system by means of a software counter that uses a timer, and then initialize the ports (see **Figure 25-9**).

#### (2) When used as interrupt

- (a) Confirm that "supply voltage (V<sub>DD</sub>) ≥ detection voltage (V<sub>LVI</sub>)" when detecting the falling edge of V<sub>DD</sub>, or "supply voltage (V<sub>DD</sub>) < detection voltage (V<sub>LVI</sub>)" when detecting the rising edge of V<sub>DD</sub>, in the servicing routine of the LVI interrupt by using bit 0 (LVIF) of the low-voltage detection register (LVIM). Clear bit 0 (LVIIF) of interrupt request flag register 0L (IF0L) to 0.

- (b) In a system where the supply voltage fluctuation period is long in the vicinity of the LVI detection voltage, wait for the supply voltage fluctuation period, confirm that "supply voltage (V<sub>DD</sub>) ≥ detection voltage (V<sub>LVI</sub>)" when detecting the falling edge of V<sub>DD</sub>, or "supply voltage (V<sub>DD</sub>) < detection voltage (V<sub>LVI</sub>)" when detecting the rising edge of V<sub>DD</sub>, using the LVIF flag, and clear the LVIIF flag to 0.

- **Remark** If bit 2 (LVISEL) of the low voltage detection register (LVIM) is set to "1", the meanings of the above words change as follows.

- Supply voltage (V<sub>DD</sub>)  $\rightarrow$  Input voltage from external input pin (EXLVI)

- Detection voltage (VLVI)  $\rightarrow$  Detection voltage (VEXLVI = 1.21 V)

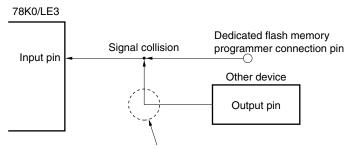

# (1) Signal collision

If the dedicated flash memory programmer (output) is connected to a pin (input) of a serial interface connected to another device (output), signal collision takes place. To avoid this collision, either isolate the connection with the other device, or make the other device go into an output high-impedance state.

#### Figure 27-9. Signal Collision (Input Pin of Serial Interface)

In the flash memory programming mode, the signal output by the device collides with the signal sent from the dedicated flash programmer. Therefore, isolate the signal of the other device.

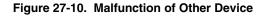

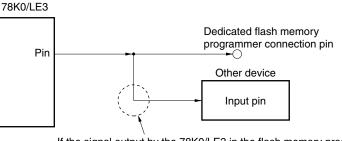

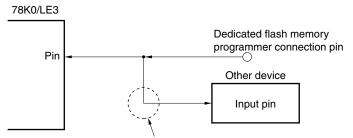

#### (2) Malfunction of other device

If the dedicated flash memory programmer (output or input) is connected to a pin (input or output) of a serial interface connected to another device (input), a signal may be output to the other device, causing the device to malfunction. To avoid this malfunction, isolate the connection with the other device.

If the signal output by the 78K0/LE3 in the flash memory programming mode affects the other device, isolate the signal of the other device.

If the signal output by the dedicated flash memory programmer in the flash memory programming mode affects the other device, isolate the signal of the other device.

| Instruction | Mnemonic  | Operands       | Bytes | Clo    | ocks   | Operation                                    |   | Flag | g    |

|-------------|-----------|----------------|-------|--------|--------|----------------------------------------------|---|------|------|

| Group       | Minemonic | Operands       | bytes | Note 1 | Note 2 | Operation                                    | Z | AC   | ; CY |

| 16-bit data | MOVW      | rp, #word      | 3     | 6      | -      | $rp \leftarrow word$                         |   |      |      |

| transfer    |           | saddrp, #word  | 4     | 8      | 10     | $(saddrp) \leftarrow word$                   |   |      |      |

|             |           | sfrp, #word    | 4     | -      | 10     | $sfrp \leftarrow word$                       |   |      |      |

|             |           | AX, saddrp     | 2     | 6      | 8      | $AX \leftarrow (saddrp)$                     |   |      |      |

|             |           | saddrp, AX     | 2     | 6      | 8      | $(saddrp) \leftarrow AX$                     |   |      |      |

|             |           | AX, sfrp       | 2     | -      | 8      | AX ← sfrp                                    |   |      |      |

|             |           | sfrp, AX       | 2     | -      | 8      | sfrp $\leftarrow AX$                         |   |      |      |

|             |           | AX, rp         | ³ 1   | 4      | -      | $AX \leftarrow rp$                           |   |      |      |

|             |           | rp, AX         | ³ 1   | 4      | -      | $rp \leftarrow AX$                           |   |      |      |

|             |           | AX, !addr16    | 3     | 10     | 12     | $AX \leftarrow (addr16)$                     |   |      |      |

|             |           | !addr16, AX    | 3     | 10     | 12     | (addr16) ← AX                                |   |      |      |

|             | XCHW      | AX, rp         | ³ 1   | 4      | -      | $AX \leftrightarrow rp$                      |   |      |      |

| 8-bit       | ADD       | A, #byte       | 2     | 4      | -      | A, CY $\leftarrow$ A + byte                  | × | ×    | ×    |

| operation   |           | saddr, #byte   | 3     | 6      | 8      | (saddr), CY $\leftarrow$ (saddr) + byte      | × | ×    | ×    |

|             |           | A, r           | * 2   | 4      | -      | A, CY ← A + r                                | × | х    | х    |

|             |           | r, A           | 2     | 4      | -      | $r, CY \leftarrow r + A$                     | × | ×    | ×    |

|             |           | A, saddr       | 2     | 4      | 5      | A, CY $\leftarrow$ A + (saddr)               | × | ×    | ×    |

|             |           | A, !addr16     | 3     | 8      | 9      | A, CY $\leftarrow$ A + (addr16)              | × | ×    | ×    |

|             |           | A, [HL]        | 1     | 4      | 5      | A, CY $\leftarrow$ A + (HL)                  | × | ×    | ×    |

|             |           | A, [HL + byte] | 2     | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte)           | × | ×    | ×    |

|             |           | A, [HL + B]    | 2     | 8      | 9      | A, CY $\leftarrow$ A + (HL + B)              | × | ×    | ×    |

|             |           | A, [HL + C]    | 2     | 8      | 9      | A, CY $\leftarrow$ A + (HL + C)              | × | ×    | ×    |

|             | ADDC      | A, #byte       | 2     | 4      | -      | A, CY $\leftarrow$ A + byte + CY             | × | ×    | ×    |

|             |           | saddr, #byte   | 3     | 6      | 8      | (saddr), CY $\leftarrow$ (saddr) + byte + CY | × | ×    | ×    |

|             |           | A, r           | * 2   | 4      | -      | A, $CY \leftarrow A + r + CY$                | × | ×    | ×    |

|             |           | r, A           | 2     | 4      | -      | $r,CY \leftarrow r + A + CY$                 | × | ×    | ×    |

|             |           | A, saddr       | 2     | 4      | 5      | A, CY $\leftarrow$ A + (saddr) + CY          | × | ×    | ×    |

|             |           | A, !addr16     | 3     | 8      | 9      | A, CY $\leftarrow$ A + (addr16) + C          | × | ×    | ×    |

|             |           | A, [HL]        | 1     | 4      | 5      | $A,CY \leftarrow A + (HL) + CY$              | × | ×    | ×    |

|             |           | A, [HL + byte] | 2     | 8      | 9      | A, CY $\leftarrow$ A + (HL + byte) + CY      | × | ×    | ×    |

|             |           | A, [HL + B]    | 2     | 8      | 9      | $A, CY \leftarrow A + (HL + B) + CY$         | × | ×    | ×    |

|             |           | A, [HL + C]    | 2     | 8      | 9      | A, CY $\leftarrow$ A + (HL + C) + CY         | × | ×    | ×    |

Notes 1. When the internal high-speed RAM area is accessed or for an instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

- **3.** Only when rp = BC, DE or HL

- **4.** Except "r = A"

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPu) selected by the processor clock control register (PCC).

- 2. This clock cycle applies to the internal ROM program.

Standard products

# X1 Oscillator Characteristics

# (TA = -40 to +85°C, 1.8 V $\leq$ VDD $\leq$ 5.5 V, Vss = AVss = 0 V)

| Resonator            | Recommended Circuit | Parameter                                                 | Conditions                                         | MIN. | TYP. | MAX. | Unit |

|----------------------|---------------------|-----------------------------------------------------------|----------------------------------------------------|------|------|------|------|

| Ceramic<br>resonator |                     | X1 clock<br>oscillation<br>frequency (fx) <sup>Note</sup> | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$              | 2.0  |      | 10.0 | MHz  |

|                      |                     |                                                           | $1.8 \text{ V} \leq V_{\text{DD}} < 2.7 \text{ V}$ | 2.0  |      | 5.0  |      |

| Crystal<br>resonator |                     | X1 clock<br>oscillation<br>frequency (fx) <sup>Note</sup> | $2.7~V \leq V_{\text{DD}} \leq 5.5~V$              | 2.0  |      | 10.0 | MHz  |

|                      |                     |                                                           | $1.8 \text{ V} \leq V_{\text{DD}} < 2.7 \text{ V}$ | 2.0  |      | 5.0  |      |

Note Indicates only oscillator characteristics. Refer to AC Characteristics for instruction execution time.

# Cautions 1. When using the X1 oscillator, wire as follows in the area enclosed by the broken lines in the above figures to avoid an adverse effect from wiring capacitance.

- Keep the wiring length as short as possible.

- Do not cross the wiring with the other signal lines.

- Do not route the wiring near a signal line through which a high fluctuating current flows.

- Always make the ground point of the oscillator capacitor the same potential as Vss.

- Do not ground the capacitor to a ground pattern through which a high current flows.

- Do not fetch signals from the oscillator.

- 2. Since the CPU is started by the internal high-speed oscillation clock after a reset release, check the X1 clock oscillation stabilization time using the oscillation stabilization time counter status register (OSTC) by the user. Determine the oscillation stabilization time of the OSTC register and oscillation stabilization time select register (OSTS) after sufficiently evaluating the oscillation stabilization time with the resonator to be used.

# Standard products

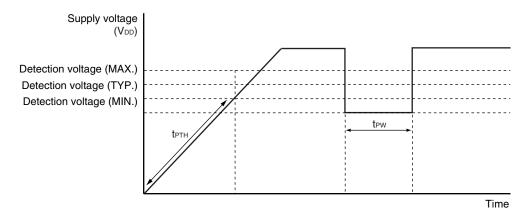

# 1.59 V POC Circuit Characteristics (T<sub>A</sub> = -40 to +85°C, Vss = 0 V)

| Parameter                             | Symbol | Conditions                                                                 | MIN. | TYP. | MAX. | Unit |

|---------------------------------------|--------|----------------------------------------------------------------------------|------|------|------|------|

| Detection voltage                     | VPOC   |                                                                            | 1.44 | 1.59 | 1.74 | V    |

| Power supply voltage rise inclination | tртн   | $V_{\text{DD}}$ : 0 $V \rightarrow$ change inclination of $V_{\text{POC}}$ | 0.5  |      |      | V/ms |

| Minimum pulse width                   | tpw    |                                                                            | 200  |      |      | μS   |

# **POC Circuit Timing**

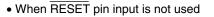

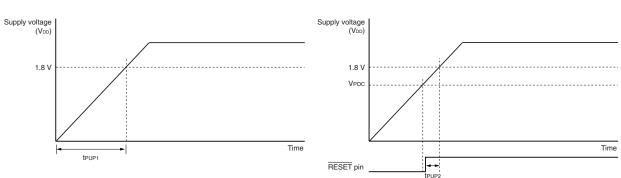

# Supply Voltage Rise Time (T<sub>A</sub> = -40 to +85°C, Vss = 0 V)

| Parameter                                                                                                                                                              | Symbol | Conditions                                                                       | MIN. | TYP. | MAX. | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------|------|------|------|------|

| Maximum time to rise to 1.8 V (V_{DD} (MIN.)) (V_{DD}: 0 V $\rightarrow$ 1.8 V)                                                                                        | tpup1  | POCMODE (option byte) = 0,<br>when RESET input is not used                       |      |      | 3.6  | ms   |

| $\begin{array}{l} \mbox{Maximum time to rise to 1.8 V (V_{DD} (MIN.))} \\ \mbox{(releasing $\overline{\mbox{RESET}}$ input $\rightarrow$ V_{DD}$: 1.8 V)} \end{array}$ | tpup2  | POCMODE (option byte) = 0,<br>when $\overrightarrow{\text{RESET}}$ input is used |      |      | 1.9  | ms   |

#### Supply Voltage Rise Time Timing

• When RESET pin input is used

# 2.7 V POC Circuit Characteristics (TA = -40 to +85°C, Vss = 0 V)

| Parameter                                          | Symbol | Conditions               | MIN. | TYP. | MAX. | Unit |

|----------------------------------------------------|--------|--------------------------|------|------|------|------|

| Detection voltage on application of supply voltage | VDDPOC | POCMODE (option bye) = 1 | 2.50 | 2.70 | 2.90 | V    |