# E. Kenesas Electronics America Inc - UPD78F0462GB-GAH-AX Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Active                                                                               |

| Core Processor             | 78K/0                                                                                |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 10MHz                                                                                |

| Connectivity               | 3-Wire SIO, LINbus, UART/USART                                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                              |

| Number of I/O              | 46                                                                                   |

| Program Memory Size        | 24KB (24K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                          |

| Data Converters            | A/D 8x10b, 3x16b                                                                     |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 64-LQFP                                                                              |

| Supplier Device Package    | -                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0462gb-gah-ax |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# CHAPTER 3 CPU ARCHITECTURE

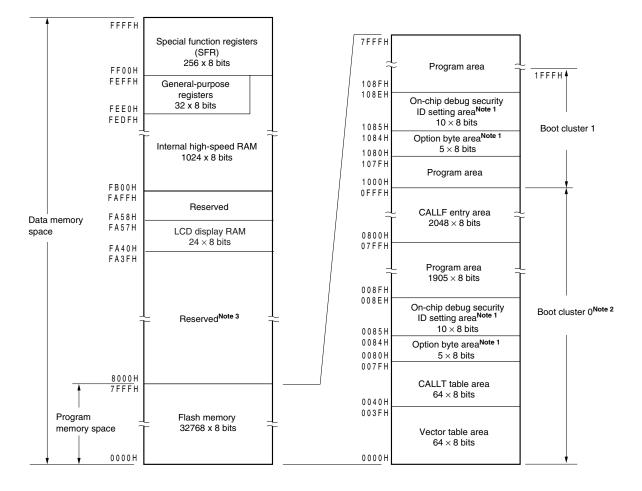

# 3.1 Memory Space

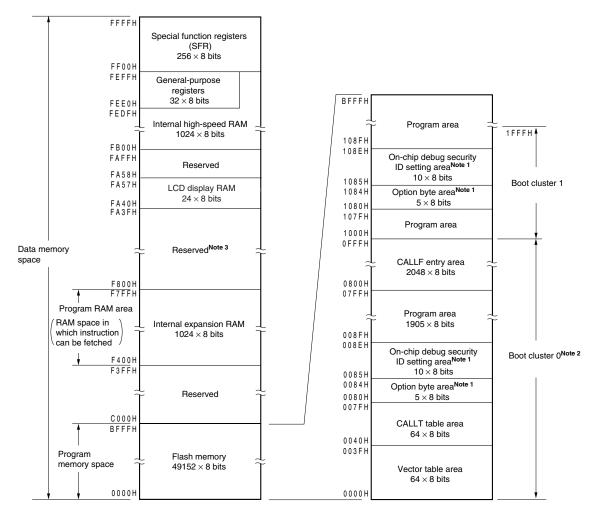

Each products in the 78K0/LE3 can access a 64 KB memory space. Figures 3-1 to 3-10 show the memory maps.

Caution Regardless of the internal memory capacity, the initial values of the internal memory size switching register (IMS) and internal expansion RAM size switching register (IXS) of all products in the 78K0/LE3 are fixed (IMS = CFH, IXS = 0CH). Therefore, set the value corresponding to each product as indicated below.

| Flash Memory Version (78K0/LE3) | IMS | IXS | ROM Capacity | Internal High-Speed<br>RAM Capacity | Internal Expansion<br>RAM Capacity |

|---------------------------------|-----|-----|--------------|-------------------------------------|------------------------------------|

| μPD78F0441, 78F0451, 78F0461    | 04H | 0CH | 16 KB        | 768 bytes                           | -                                  |

| μPD78F0442, 78F0452, 78F0462    | C6H |     | 24 KB        | 1 KB                                |                                    |

| μPD78F0443, 78F0453, 78F0463    | C8H |     | 32 KB        |                                     |                                    |

| μPD78F0444, 78F0454, 78F0464    | ССН | 0AH | 48 KB        |                                     | 1 KB                               |

| μPD78F0445, 78F0455, 78F0465    | CFH |     | 60 KB        |                                     |                                    |

Table 3-1.

Set Values of Internal Memory Size Switching Register (IMS)

and Internal Expansion RAM Size Switching Register (IXS)

Figure 3-6. Memory Map (µPD78F0463)

**Notes 1.** When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used:

Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Setting).

- <R>

- 3. However, FA26H and FA27H can be used (See 13.3 Registers Used in 16-Bit  $\Delta\Sigma$  Type A/D Converter).

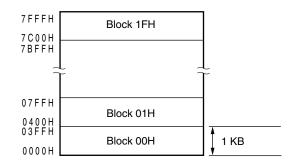

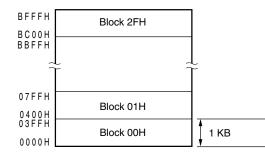

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

Notes 1. When boot swap is not used: Set the option bytes to 0080H to 0084H, and the on-chip debug security IDs to 0085H to 008EH.

When boot swap is used: Set the option bytes to 0080H to 0084H and 1080H to 1084H, and the on-chip debug security IDs to 0085H to 008EH and 1085H to 108EH.

- 2. Writing boot cluster 0 can be prohibited depending on the setting of security (see 27.8 Security Setting).

- 3. However, FA26H and FA27H can be used (See 13.3 Registers Used in 16-Bit  $\Delta\Sigma$  Type A/D Converter).

- **Remark** The flash memory is divided into blocks (one block = 1 KB). For the address values and block numbers, see **Table 3-2 Correspondence Between Address Values and Block Numbers in Flash Memory**.

<R>

#### (2) CALLT instruction table area

The 64-byte area 0040H to 007FH can store the subroutine entry address of a 1-byte call instruction (CALLT).

# (3) Option byte area

A 5-byte area of 0080H to 0084H and 1080H to 1084H can be used as an option byte area. Set the option byte at 0080H to 0084H when the boot swap is not used, and at 0080H to 0084H and 1080H to 1084H when the boot swap is used. For details, see **CHAPTER 26 OPTION BYTE**.

# (4) CALLF instruction entry area

The area 0800H to 0FFFH can perform a direct subroutine call with a 2-byte call instruction (CALLF).

# (5) On-chip debug security ID setting area

A 10-byte area of 0085H to 008EH and 1085H to 108EH can be used as an on-chip debug security ID setting area. Set the on-chip debug security ID of 10 bytes at 0085H to 008EH when the boot swap is not used and at 0085H to 008EH and 1085H to 108EH when the boot swap is used. For details, see **CHAPTER 28 ON-CHIP DEBUG FUNCTION**.

| Address | Special Function Register (SFR) Name                                        | Symbol  | R/W | Man          | After        |              |       |

|---------|-----------------------------------------------------------------------------|---------|-----|--------------|--------------|--------------|-------|

|         |                                                                             |         |     | 1 Bit        | 8 Bits       | 16 Bits      | Reset |

| FF60H   | Sub-count register                                                          | RSUBC   | R   | -            | _            |              | 0000H |

| FF61H   |                                                                             |         |     |              |              |              |       |

| FF62H   | Second count register                                                       | SEC     | R/W | _            | $\checkmark$ | _            | 00H   |

| FF63H   | Minute count register                                                       | MIN     | R/W | _            |              | _            | 00H   |

| FF64H   | Hour count register                                                         | HOUR    | R/W | _            |              | _            | 12H   |

| FF65H   | Week count register                                                         | WEEK    | R/W | _            |              | _            | 00H   |

| FF66H   | Day count register                                                          | DAY     | R/W | _            |              | _            | 01H   |

| FF67H   | Month count register                                                        | MONTH   | R/W | _            | $\checkmark$ | _            | 01H   |

| FF68H   | Year count register                                                         | YEAR    | R/W | _            |              | _            | 00H   |

| FF69H   | 8-bit timer H mode register 0                                               | TMHMD0  | R/W |              |              | _            | 00H   |

| FF6AH   | Timer clock selection register 50                                           | TCL50   | R/W | V            | V            | _            | 00H   |

| FF6BH   | 8-bit timer mode control register 50                                        | TMC50   | R/W | $\checkmark$ |              | -            | 00H   |

| FF6CH   | 8-bit timer H mode register 1                                               | TMHMD1  | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF6DH   | 8-bit timer H carrier control register 1                                    | TMCYC1  | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF6EH   | Key return mode register                                                    | KRM     | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF6FH   | 8-bit timer counter 51                                                      | TM51    | R   | _            | $\checkmark$ | -            | 00H   |

| FF70H   | Asynchronous serial interface operation mode register 0                     | ASIMO   | R/W | $\checkmark$ | $\checkmark$ | -            | 01H   |

| FF71H   | Baud rate generator control register 0                                      | BRGC0   | R/W | _            | $\checkmark$ | -            | 1FH   |

| FF72H   | Receive buffer register 0                                                   | RXB0    | R   | -            | $\checkmark$ | -            | FFH   |

| FF73H   | Asynchronous serial interface reception error<br>status register 0          | ASIS0   | R   | -            | $\checkmark$ | -            | 00H   |

| FF74H   | Transmit shift register 0                                                   | TXS0    | W   | -            | $\checkmark$ | -            | FFH   |

| FF75H   | 16-bit $\Delta\Sigma$ A/D conversion end channel register <sup>Note 1</sup> | ADDSTR  | R   | -            | $\checkmark$ | -            | 00H   |

| FF7CH   | $\Delta\Sigma$ A/D converter control register 0 <sup>Note 1</sup>           | ADDCTL0 | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF7DH   | $\Delta\Sigma$ A/D converter control register 1 <sup>Note 1</sup>           | ADDCTL1 | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF7EH   | 16-bit $\Delta\Sigma$ A/D conversion result register <sup>Note 1</sup>      | ADDCR   | R   | _            | -            | $\checkmark$ | 0000H |

| FF7FH   | 8-bit $\Delta\Sigma$ A/D conversion result register <sup>Note 1</sup>       | ADDCRH  | R   | -            | $\checkmark$ | -            | 00H   |

| FF80H   | Serial operation mode register 10                                           | CSIM10  | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF81H   | Serial clock selection register 10                                          | CSIC10  | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF82H   | Watch error correction register                                             | SUBCUD  | R/W | $\checkmark$ | $\checkmark$ | -            | 00H   |

| FF84H   | Transmit buffer register 10                                                 | SOTB10  | R/W | -            | $\checkmark$ | -            | 00H   |

| FF86H   | Alarm minute register                                                       | ALARMWM | R/W | -            |              | -            | 00H   |

| FF87H   | Alarm hour register                                                         | ALARMWH | R/W | -            | $\checkmark$ | -            | 12H   |

| FF88H   | Alarm week register                                                         | ALARMWW | R/W | -            | V            | -            | 00H   |

| FF89H   | Real-time counter control register 0                                        | RTCC0   | R/W | /            | V            | -            | 00H   |

| FF8AH   | Real-time counter control register 1                                        | RTCC1   | R/W | /            | V            | -            | 00H   |

| FF8BH   | Real-time counter control register 2                                        | RTCC2   | R/W | /            | V            | -            | 00H   |

| FF8CH   | Timer clock selection register 51                                           | TCL51   | R/W | /            | V            | -            | 00H   |

| FF8DH   | A/D converter mode register <sup>Note 2</sup>                               | ADM     | R/W | /            | V            | -            | 00H   |

| FF8EH   | Analog input channel specification register <sup>Note 2</sup>               | ADS     | R/W | /            | V            | -            | 00H   |

| FF8FH   | A/D port configuration register 0 <sup>Note 2</sup>                         | ADPC0   | R/W |              |              | -            | 08H   |

| Table 3-8. | Special | Function | Register | List | (3/5) |

|------------|---------|----------|----------|------|-------|

|------------|---------|----------|----------|------|-------|

**Notes 1.**  $\mu$ PD78F046x only.

**2.**  $\mu$ PD78F045x and 78F046x only.

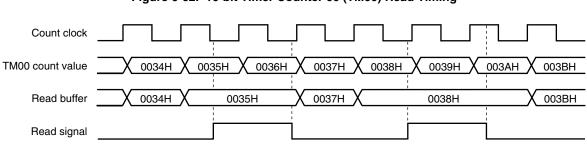

# <R> (12) Reading of 16-bit timer counter 00 (TM00)

TM00 can be read without stopping the actual counter, because the count values captured to the buffer are fixed when it is read. The buffer, however, may not be updated when it is read immediately before the counter counts up, because the buffer is updated at the timing the counter counts up.

# Figure 6-62. 16-bit Timer Counter 00 (TM00) Read Timing

| Address: FF | 5BH After                                                    | reset: 00H | R/W |                        |                |              |           |         |

|-------------|--------------------------------------------------------------|------------|-----|------------------------|----------------|--------------|-----------|---------|

| Symbol      | 7                                                            | 6          | 5   | 4                      | 3              | 2            | 1         | 0       |

| TCL52       | 0                                                            | 0          | 0   | 0                      | 0              | TCL522       | TCL521    | TCL520  |

|             |                                                              |            |     |                        |                |              |           |         |

|             | TCL522 TCL521 TCL520 Count clock selection <sup>Note 1</sup> |            |     |                        |                |              |           |         |

|             |                                                              |            |     |                        |                | fprs =       | fprs =    | fprs =  |

|             |                                                              |            |     |                        |                | 2 MHz        | 5 MHz     | 10 MHz  |

|             | 0                                                            | 0          | 0   | Falling edge           | of clock seled | cted by ISC2 |           |         |

|             | 0                                                            | 0          | 1   | Rising edge            | of clock selec | ted by ISC2  |           |         |

|             | 0                                                            | 1          | 0   | fprs <sup>Note 2</sup> |                | 2 MHz        | 5 MHz     | 10 MHz  |

|             | 0                                                            | 1          | 1   | fprs/2                 |                | 1 MHz        | 2.5 MHz   | 5 MHz   |

|             | 1                                                            | 0          | 0   | fprs/2 <sup>4</sup>    |                | 125 kHz      | 312.5 kHz | 625 kHz |

|             |                                                              |            |     |                        |                |              |           |         |

#### Figure 7-8. Format of Timer Clock Selection Register 52 (TCL52)

**Notes 1.** If the peripheral hardware clock (fPRs) operates on the high-speed system clock (fXH) (XSEL = 1), the fPRs operating frequency varies depending on the supply voltage.

fprs/26

fprs/28

$f_{PRS}/2^{12}$

1

0

1

• VDD = 2.7 to 5.5 V: fPRs  $\leq$  10 MHz

0

1

1

1

1

1

- VDD = 1.8 to 2.7 V: fPRs  $\leq$  5 MHz

- 2. If the peripheral hardware clock (fPRS) operates on the internal high-speed oscillation clock (fRH) (XSEL = 0), when 1.8 V ≤ VDD < 2.7 V, the setting of TCL522, TCL521, TCL520 = 0, 1, 0 (count clock: fPRS) is prohibited.</p>

31.25 kHz

7.81 kHz

0.49 kHz

78.13 kHz

19.53 kHz

1.22 kHz

156.25 kHz

39.06 kHz

2.44 kHz

# Cautions 1. When rewriting TCL52 to other data, stop the timer operation beforehand. 2. Be sure to clear bits 3 to 7 to 0.

Remark fprs: Peripheral hardware clock frequency

| Address: | FF8FH A   | After reset: 0 | 8H R/W   |        |                                                                                                           |            |                        |            |            |                        |                        |            |

|----------|-----------|----------------|----------|--------|-----------------------------------------------------------------------------------------------------------|------------|------------------------|------------|------------|------------------------|------------------------|------------|

| Symbol   | 7         | 6              | 5        | 4      | ;                                                                                                         | 3          | :                      | 2          |            | 1                      | (                      | )          |

| ADPC0    | 0         | 0              | 0        | 0      | ADF                                                                                                       | PC03       | ADF                    | PC02       | ADF        | PC01                   | ADF                    | 200 C00    |

|          | <µPD78F04 | 5x>            |          |        |                                                                                                           |            |                        |            |            |                        |                        |            |

|          | ADPC03    | ADPC02         | ADPC01   | ADPC00 | C                                                                                                         | igital I   | /O (D)                 | /analo     | g inpu     | t (A) sv               | witchin                | g          |

|          |           |                |          |        | P27/<br>ANI7/<br>SEG24                                                                                    | ANI6/      | P25/<br>ANI5/<br>SEG26 | ANI4/      | ANI3/      | P22/<br>ANI2/<br>SEG29 | P21/<br>ANI1/<br>SEG30 | ANI0/      |

|          | 0         | 0              | 0        | 0      | Α                                                                                                         | Α          | Α                      | Α          | Α          | А                      | Α                      | А          |

|          | 0         | 0              | 0        | 1      | Α                                                                                                         | A          | А                      | А          | А          | А                      | А                      | D          |

|          | 0         | 0              | 1        | 0      | А                                                                                                         | Α          | Α                      | Α          | Α          | А                      | D                      | D          |

|          | 0         | 0              | 1        | 1      | А                                                                                                         | Α          | А                      | А          | А          | D                      | D                      | D          |

|          | 0         | 1              | 0        | 0      | А                                                                                                         | Α          | Α                      | Α          | D          | D                      | D                      | D          |

|          | 0         | 1              | 0        | 1      | Α                                                                                                         | A          | А                      | D          | D          | D                      | D                      | D          |

|          | 0         | 1              | 1        | 0      | А                                                                                                         | A          | D                      | D          | D          | D                      | D                      | D          |

|          | 0         | 1              | 1        | 1      | А                                                                                                         | D          | D                      | D          | D          | D                      | D                      | D          |

|          | 1         | 0              | 0        | 0      | D                                                                                                         | D          | D                      | D          | D          | D                      | D                      | D          |

|          |           | Other that     | an above |        | Setting prohibited                                                                                        |            |                        |            |            |                        |                        |            |

| 1        | <µPD78F04 | 6x>            |          |        |                                                                                                           |            |                        |            |            |                        |                        |            |

|          | ADPC03    | ADPC02         | ADPC01   | ADPC00 | Digital I/O (D)/analog input (A: successive approximation type, $\Delta$ : $\Delta\Sigma$ type) switching |            |                        |            |            |                        |                        |            |

|          |           |                |          |        |                                                                                                           | ANI6/      |                        | ANI4/      | ANI3/      | P22/<br>ANI2/<br>DS1-  | ANI1/                  | ANI0/      |

|          | 0         | 0              | 0        | 0      | $A/\Delta$                                                                                                | Α/Δ        | $A/\Delta$             | $A/\Delta$ | $A/\Delta$ | $A/\Delta$             | $A/\Delta$             | $A/\Delta$ |

|          | 0         | 0              | 0        | 1      | $A/\Delta$                                                                                                | $A/\Delta$ | $A/\Delta$             | $A/\Delta$ | $A/\Delta$ | $A/\Delta$             | А                      | D          |

|          | 0         | 0              | 1        | 0      | $A/\Delta$                                                                                                | Α/Δ        | $A/\Delta$             | Α/Δ        | $A/\Delta$ | $A/\Delta$             | D                      | D          |

|          | 0         | 0              | 1        | 1      | $A/\Delta$                                                                                                | Α/Δ        | $A/\Delta$             | Α/Δ        | А          | D                      | D                      | D          |

|          | 0         | 1              | 0        | 0      | $A/\Delta$                                                                                                | Α/Δ        | $A/\Delta$             | Α/Δ        | D          | D                      | D                      | D          |

|          | 0         | 1              | 0        | 1      | А                                                                                                         | A          | А                      | D          | D          | D                      | D                      | D          |

|          | 0         | 1              | 1        | 0      | А                                                                                                         | A          | D                      | D          | D          | D                      | D                      | D          |

|          | 0         | 1              | 1        | 1      | А                                                                                                         | D          | D                      | D          | D          | D                      | D                      | D          |

|          | 1         | 0              | 0        | 0      | D                                                                                                         | D          | D                      | D          | D          | D                      | D                      | D          |

|          | I         |                |          |        |                                                                                                           |            |                        | . –        |            |                        |                        |            |

#### Figure 12-9. Format of A/D Port Configuration Register 0 (ADPC0)

- Cautions 1. Set the channel used for A/D conversion to the input mode by using port mode register 2 (PM2).

- 2. Do not set the pin set by ADPC0 as digital I/O by ADS, ADDS1, or ADDS0.

Other than above

3. If data is written to ADPC0, a wait cycle is generated. Do not write data to ADPC0 when the CPU is operating on the subsystem clock and the peripheral hardware clock is stopped. For details, see CHAPTER 33 CAUTIONS FOR WAIT.

Setting prohibited

4. If pins ANI0/P20/SEG31 to ANI7/P27/SEG24 are set to segment output pins via the PF2 register, output is set to segment output, regardless of the ADPC0 setting (for  $\mu$ PD78F045x only).

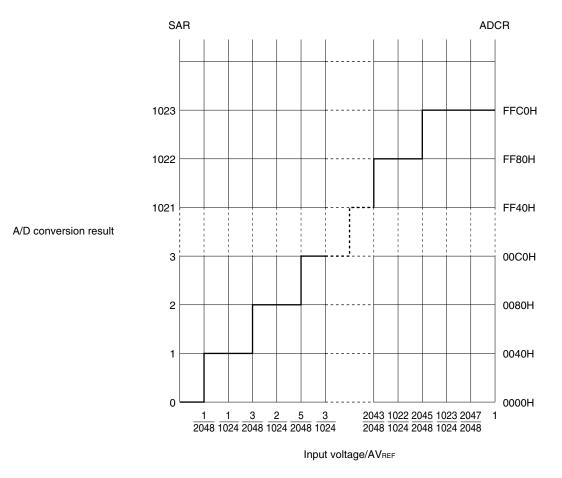

# 12.4.2 Input voltage and conversion results

The relationship between the analog input voltage input to the analog input pins (ANI0 to ANI7) and the theoretical A/D conversion result (stored in the 10-bit A/D conversion result register (ADCR)) is shown by the following expression.

SAR = INT

$$(\frac{V_{AIN}}{AV_{REF}} \times 1024 + 0.5)$$

ADCR = SAR × 64

or

$$(\frac{ADCR}{64} - 0.5) \times \frac{AV_{\mathsf{REF}}}{1024} \le V_{\mathsf{AIN}} < (\frac{ADCR}{64} + 0.5) \times \frac{AV_{\mathsf{REF}}}{1024}$$

where, INT():Function which returns integer part of value in parenthesesVAIN:Analog input voltageAVREF:AVREF pin voltageADCR:A/D conversion result register (ADCR) valueSAR:Successive approximation register

Figure 12-12 shows the relationship between the analog input voltage and the A/D conversion result.

Figure 12-12. Relationship Between Analog Input Voltage and A/D Conversion Result

#### 14.4.2 Asynchronous serial interface (UART) mode

In this mode, 1-byte data is transmitted/received following a start bit, and a full-duplex operation can be performed.

A dedicated UART baud rate generator is incorporated, so that communication can be executed at a wide range of baud rates.

# (1) Registers used

- Asynchronous serial interface operation mode register 0 (ASIM0)

- Asynchronous serial interface reception error status register 0 (ASIS0)

- Baud rate generator control register 0 (BRGC0)

- Port mode register 1 (PM1)

- Port register 1 (P1)

The basic procedure of setting an operation in the UART mode is as follows.

- <1> Set the BRGC0 register (see Figure 14-4).

- <2> Set bits 1 to 4 (SL0, CL0, PS00, and PS01) of the ASIM0 register (see Figure 14-2).

- <3> Set bit 7 (POWER0) of the ASIM0 register to 1.

- <4> Set bit 6 (TXE0) of the ASIM0 register to 1.  $\rightarrow$  Transmission is enabled. Set bit 5 (RXE0) of the ASIM0 register to 1.  $\rightarrow$  Reception is enabled.

- <5> Write data to the TXS0 register.  $\rightarrow$  Data transmission is started.

# Caution Take relationship with the other party of communication when setting the port mode register and port register.

The relationship between the register settings and pins is shown below.

| POWER0 | TXE0 | RXE0 | PM13                | P13                 | PM12                | P12                    | UART0 Pin Function |                         |                         |

|--------|------|------|---------------------|---------------------|---------------------|------------------------|--------------------|-------------------------|-------------------------|

|        |      |      |                     |                     |                     |                        | Operation          | TxD0/SO10               | RxD0/SI10               |

|        |      |      |                     |                     |                     |                        |                    | / <txd6>/P13</txd6>     | / <rxd6>/P12</rxd6>     |

| 0      | 0    | 0    | $\times^{\sf Note}$ | $\times^{\sf Note}$ | $\times^{\sf Note}$ | $\times^{^{\rm Note}}$ | Stop               | SO10/ <txd6>/P13</txd6> | SI10/ <rxd6>/P12</rxd6> |

| 1      | 0    | 1    | $\times^{\rm Note}$ | $\times^{\sf Note}$ | 1                   | ×                      | Reception          | SO10/P13                | RxD0                    |

|        | 1    | 0    | 0                   | ×                   | $\times^{\rm Note}$ | $\times^{\rm Note}$    | Transmission       | TxD0                    | SI10/P12                |

|        | 1    | 1    | 0                   | ×                   | 1                   | ×                      | Transmission/      | TxD0                    | RxD0                    |

|        |      |      |                     |                     |                     |                        | reception          |                         |                         |

Note Can be set as port function, serial interface CSI10, or serial interface UART6 (only when UART0 is stopped).

Remark ×:

K

×:

don't care

POWER0:

Bit 7 of asynchronous serial interface operation mode register 0 (ASIM0)

TXE0:

Bit 6 of ASIM0

RXE0:

Bit 5 of ASIM0

PM1×:

Port mode register

P1×:

Port output latch

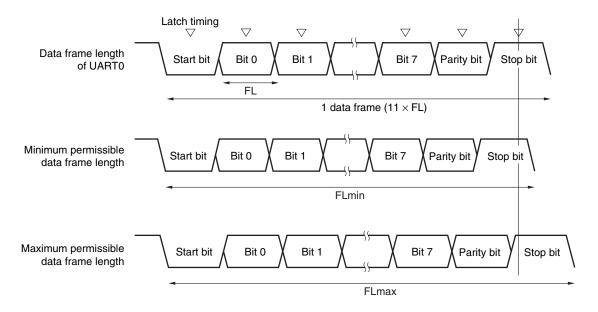

#### (4) Permissible baud rate range during reception

The permissible error from the baud rate at the transmission destination during reception is shown below.

# Caution Make sure that the baud rate error during reception is within the permissible error range, by using the calculation expression shown below.

As shown in Figure 14-13, the latch timing of the receive data is determined by the counter set by baud rate generator control register 0 (BRGC0) after the start bit has been detected. If the last data (stop bit) meets this latch timing, the data can be correctly received.

Assuming that 11-bit data is received, the theoretical values can be calculated as follows.

$FL = (Brate)^{-1}$

Brate:Baud rate of UART0k:Set value of BRGC0FL:1-bit data lengthMargin of latch timing: 2 clocks

# (d) Continuous transmission

The next transmit data can be written to transmit buffer register 6 (TXB6) as soon as transmit shift register 6 (TXS6) has started its shift operation. Consequently, even while the INTST6 interrupt is being serviced after transmission of one data frame, data can be continuously transmitted and an efficient communication rate can be realized. In addition, the TXB6 register can be efficiently written twice (2 bytes) without having to wait for the transmission time of one data frame, by reading bit 0 (TXSF6) of asynchronous serial interface transmission status register 6 (ASIF6) when the transmission completion interrupt has occurred.

To transmit data continuously, be sure to reference the ASIF6 register to check the transmission status and whether the TXB6 register can be written, and then write the data.

- Cautions 1. The TXBF6 and TXSF6 flags of the ASIF6 register change from "10" to "11", and to "01" during continuous transmission. To check the status, therefore, do not use a combination of the TXBF6 and TXSF6 flags for judgment. Read only the TXBF6 flag when executing continuous transmission.

- 2. When the device is use in LIN communication operation, the continuous transmission function cannot be used. Make sure that asynchronous serial interface transmission status register 6 (ASIF6) is 00H before writing transmit data to transmit buffer register 6 (TXB6).

| TXBF6 | Writing to TXB6 Register |

|-------|--------------------------|

| 0     | Writing enabled          |

| 1     | Writing disabled         |

Caution To transmit data continuously, write the first transmit data (first byte) to the TXB6 register. Be sure to check that the TXBF6 flag is "0". If so, write the next transmit data (second byte) to the TXB6 register. If data is written to the TXB6 register while the TXBF6 flag is "1", the transmit data cannot be guaranteed.

The communication status can be checked using the TXSF6 flag.

| TXSF6 | Transmission Status          |  |  |  |  |  |  |

|-------|------------------------------|--|--|--|--|--|--|

| 0     | Transmission is completed.   |  |  |  |  |  |  |

| 1     | Transmission is in progress. |  |  |  |  |  |  |

- Cautions 1. To initialize the transmission unit upon completion of continuous transmission, be sure to check that the TXSF6 flag is "0" after generation of the transmission completion interrupt, and then execute initialization. If initialization is executed while the TXSF6 flag is "1", the transmit data cannot be guaranteed.

- 2. During continuous transmission, the next transmission may complete before execution of INTST6 interrupt servicing after transmission of one data frame. As a countermeasure, detection can be performed by developing a program that can count the number of transmit data and by referencing the TXSF6 flag.

# (4) Port mode register 1 (PM1)

This register sets port 1 input/output in 1-bit units.

When using P11/SCK10 as the clock output pin of the serial interface, clear PM11 to 0, and set the output latches of P11 to 1.

When using P13/SO10/TxD0/<TxD6> as the data output pin of the serial interface, clear PM13 and the output latches of P13 to 0.

When using P11/SCK10 as the clock input pin of the serial interface and P12/SI10/RxD0/<RxD6> as the data input pin, set PM11 and PM12 to 1. At this time, the output latches of P11 and P12 may be 0 or 1.

PM1 can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation sets these registers to FFH.

| Symbol | 7 | 6 | 5 | 4    | 3    | 2    | 1    | 0 |

|--------|---|---|---|------|------|------|------|---|

| PM1    | 1 | 1 | 1 | PM14 | PM13 | PM12 | PM11 | 1 |

| PM1n | P1n pin I/O mode selection (n = 1 to 4) |

|------|-----------------------------------------|

| 0    | Output mode (output buffer on)          |

| 1    | Input mode (output buffer off)          |

# Figure 16-5. Format of Port Mode Register 1 (PM1)

Address: FF21H After reset: FFH R/W

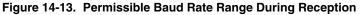

# Figure 17-22. Two-Time-Slice LCD Drive Waveform Examples (1/2 Bias Method)

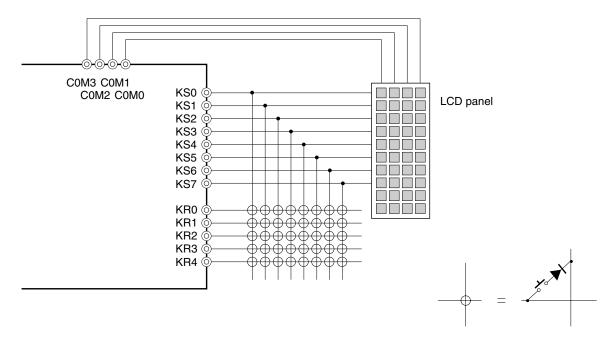

# 17.8 Operation of Segment Key Scan Function

The segment key scan function is used to reduce the number of pins used by outputting LCD display segment output and key scan signals from the same pin.

# Caution This function may affect the LCD panel, depending on how it is used. Use the function after thorough evaluation.

# 17.8.1 Circuit configuration example

Figure 17-33. Circuit configuration example

# CHAPTER 18 MANCHESTER CODE GENERATOR

# 18.1 Functions of Manchester Code Generator

The following three types of modes are available for the Manchester code generator.

# (1) Operation stop mode

This mode is used when output by the Manchester code generator/bit sequential buffer is not performed. This mode reduces the power consumption.

For details, refer to 18.4.1 Operation stop mode.

#### (2) Manchester code generator mode

This mode is used to transmit Manchester code from the MCGO pin. The transfer bit length can be set and transfers of various bit lengths are enabled. Also, the output level of the data transfer and LSB- or MSB-first can be set for 8-bit transfer data.

# (3) Bit sequential buffer mode

This mode is used to transmit bit sequential data from the MCGO pin. The transfer bit length can be set and transfers of various bit lengths are enabled. Also, the output level of the data transfer and LSB- or MSB-first can be set for 8-bit transfer data.

# 18.2 Configuration of Manchester Code Generator

The Manchester code generator includes the following hardware.

#### Table 18-1. Configuration of Manchester Code Generator

| Item              | Configuration                                                                                                                                                                                  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Registers         | MCG transmit buffer register (MC0TX)<br>MCG transmit bit count specification register (MC0BIT)                                                                                                 |  |  |  |  |  |

| Control registers | MCG control register 0 (MC0CTL0)<br>MCG control register 1 (MC0CTL1)<br>MCG control register 2 (MC0CTL2)<br>MCG status register (MC0STR)<br>Port mode register 3 (PM3)<br>Port register 3 (P3) |  |  |  |  |  |

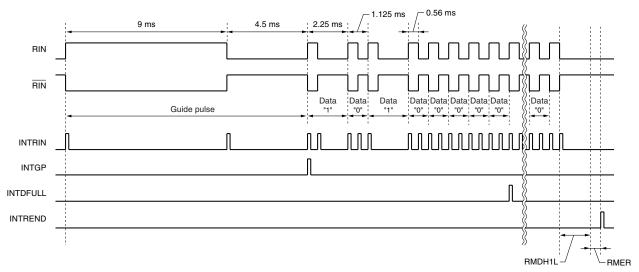

#### **19.4.3** Format of type B reception mode

Figure 19-8 shows the data format for type B.

#### Figure 19-8. Example of Type B Data Format

**Remark** RIN is the internally inverted signal of RIN.

# 19.4.4 Operation flow of type B reception mode

Figure 19-9 shows the operation flow.

#### Cautions 1. When INTRERR is generated, RMSR and RMSCR are automatically cleared immediately.

- 2. When data has been set to all the bits of RMSR, the following processing is automatically performed.

- The value of RMSR is transferred to RMDR.

- INTDFULL is generated.

- RMSR is cleared.

RMDR must then be read before the next data is set to all the bits of RMSR.

- When INTREND has been generated, read RMSCR first followed by RMSR.

When RMSR has been read, RMSCR and RMSR are automatically cleared.

If INTREND is generated, the next data cannot be received until RMSR is read.

- 4. RMSR, RMSCR, and RMDR are cleared simultaneously to operation termination (RMEN = 0).

| · · · ·               | ction Name          |                     | Interrupt                        |                                     |          |  |  |

|-----------------------|---------------------|---------------------|----------------------------------|-------------------------------------|----------|--|--|

|                       |                     | RSTOP = 0 a         | RSTOP = 0 and RSTS = 1 RSTOP = 1 |                                     |          |  |  |

|                       |                     | (during stable op   | eration of internal              | (internal high-speed                |          |  |  |

|                       |                     | high-speed          | l oscillator)                    | oscillator stopped) <sup>Note</sup> |          |  |  |

|                       |                     | MCS = 0             | MCS = 1                          | MCS = 1                             |          |  |  |

|                       |                     | (CPU operates with  | (CPU operates with               | (CPU operates with                  |          |  |  |

|                       |                     | internal high-speed | high-speed system                | high-speed system                   |          |  |  |

|                       |                     | oscillation clock)  | clock)                           | clock)                              |          |  |  |

| Self programm         | ning start function | 34/fcpu             | 34/fcpu                          | 34/fcpu                             | Disabled |  |  |

| Self programm         | ning end function   | 34/fcpu             | 34/fcpu                          | 34/fcpu                             | Disabled |  |  |

| Initialize funct      | ion                 | 55/fcpu+462         | 55/fcpu+462                      | 55/fcpu+473                         | Disabled |  |  |

| Block erase fu        | unction             | 136/fcpu+352516     | 136/fcpu+352516                  | 136/fcpu+352528                     | Enabled  |  |  |

| Word write function   |                     | 272/fcpu+477+       | 272/fcpu+477+                    | 272/fcpu+488+                       | Enabled  |  |  |

|                       |                     | 2142×W              | 2142×W                           | 2142×W                              |          |  |  |

| Block verify fu       | Inction             | 136/fcpu+24918      | 136/fcpu+24918                   | 136/fcpu+24930                      | Enabled  |  |  |

| Block blank cl        | heck function       | 136/fcpu+12128      | 136/fcpu+12128                   | 136/fcpu+12139                      | Enabled  |  |  |

| Get                   | Option value: 03H   | 134/fcpu+388        | 134/fcpu+388                     | 134/fcpu+399                        | Disabled |  |  |

| information           | Option value: 04H   | 144/fcpu+378        | 144/fcpu+378                     | 144/fcpu+390                        | Disabled |  |  |

| function              | Option value: 05H   | 304/fcpu+363        | 304/fcpu+363                     | 304/fcpu+375                        | Disabled |  |  |

| Set informatio        | on function         | 72/fcpu+752540      | 72/fcpu+752540                   | 72/fcpu+753654                      | Enabled  |  |  |

| Mode check function   |                     | 30/fcpu+274         | 30/fcpu+274                      | 30/fcpu+286                         | Disabled |  |  |

| EEPROM write function |                     | 268/fcpu+619+       | 268/fcpu+619+                    | 268/fcpu+630+                       | Enabled  |  |  |

|                       |                     | 2286×W              | 2286×W                           | 2286×W                              |          |  |  |

Table 27-13. Processing Time and Interrupt Acknowledgment (4/4) (When Static Model Library and Entry RAM Are Allocated Within Short Direct Addressing Range)

- **Note** This is the function processing time when the function is executed immediately after the self programming start function has been executed. The processing time after a function other than the self programming start function has been executed is the same as that of RSTOP = 0.

- Remark RSTOP: Bit 0 of the internal oscillation mode register (RCM)

- RSTS: Bit 7 of RCM

- MCS: Bit 1 of main clock mode register (MCM)

- fcpu: CPU clock frequency

- W: Number of words to be written (1 word = 4 bytes)

# 29.3 Instructions Listed by Addressing Type

# (1) 8-bit instructions

MOV, XCH, ADD, ADDC, SUB, SUBC, AND, OR, XOR, CMP, MULU, DIVUW, INC, DEC, ROR, ROL, RORC, ROLC, ROR4, ROL4, PUSH, POP, DBNZ

| Second Operand<br>First Operand     | #byte                                                        | A                                                            | r <sup>Note</sup>                                                   | sfr        | saddr                                                       | !addr16                                                             | PSW | [DE]       | [HL]                                                        | [HL + byte]<br>[HL + B]<br>[HL + C]                         |      | 1                          | None         |

|-------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------|------------|-------------------------------------------------------------|---------------------------------------------------------------------|-----|------------|-------------------------------------------------------------|-------------------------------------------------------------|------|----------------------------|--------------|

| A                                   | ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP        |                                                              | MOV<br>XCH<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV<br>XCH | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV<br>XCH<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV | MOV<br>XCH | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV<br>XCH<br>ADD<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP |      | ROR<br>ROL<br>RORC<br>ROLC |              |

| r                                   | MOV                                                          | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            | INC<br>DEC   |

| B, C                                |                                                              |                                                              |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             | DBNZ |                            |              |

| sfr                                 | MOV                                                          | MOV                                                          |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            |              |

| saddr                               | MOV<br>ADD<br>ADDC<br>SUB<br>SUBC<br>AND<br>OR<br>XOR<br>CMP | MOV                                                          |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             | DBNZ |                            | INC<br>DEC   |

| !addr16                             |                                                              | MOV                                                          |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            |              |

| PSW                                 | MOV                                                          | MOV                                                          |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            | PUSH<br>POP  |

| [DE]                                |                                                              | MOV                                                          |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            |              |

| [HL]                                |                                                              | MOV                                                          |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            | ROR4<br>ROL4 |

| [HL + byte]<br>[HL + B]<br>[HL + C] |                                                              | MOV                                                          |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            |              |

| х                                   |                                                              |                                                              |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            | MULU         |

| С                                   |                                                              |                                                              |                                                                     |            |                                                             |                                                                     |     |            |                                                             |                                                             |      |                            | DIVUW        |

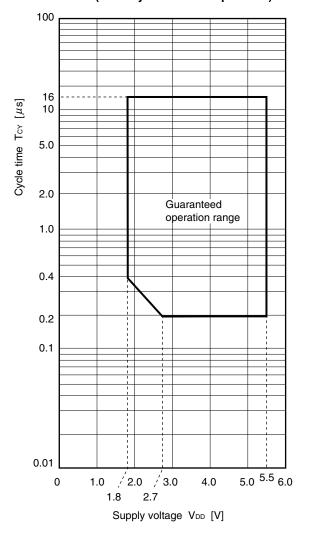

Standard products

TCY vs. VDD (Main System Clock Operation)

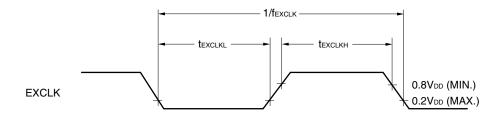

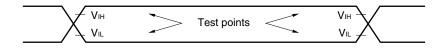

AC Timing Test Points (Excluding External Main System Clock)

**External Main System Clock Timing**