Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | UART/USART, USB                                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | - ·                                                                       |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2450-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0        | U-0                | U-0              | U-0             | R <sup>(1)</sup>     | U-0                     | R/W-0           | R/W-0 |  |  |  |

|--------------|--------------------|------------------|-----------------|----------------------|-------------------------|-----------------|-------|--|--|--|

| IDLEN        | _                  | —                | _               | OSTS                 | —                       | SCS1            | SCS0  |  |  |  |

| bit 7        |                    |                  |                 |                      |                         |                 | bit 0 |  |  |  |

|              |                    |                  |                 |                      |                         |                 |       |  |  |  |

| Legend:      |                    |                  |                 |                      |                         |                 |       |  |  |  |

| R = Readab   | ole bit            | W = Writable     | bit             | U = Unimple          | nented bit, read as '0' |                 |       |  |  |  |

| -n = Value a | at POR             | '1' = Bit is set |                 | '0' = Bit is cl€     | eared                   | x = Bit is unkr | nown  |  |  |  |

|              |                    |                  |                 |                      |                         |                 |       |  |  |  |

| bit 7        | IDLEN: Idle E      | nable bit        |                 |                      |                         |                 |       |  |  |  |

|              | 1 = Device er      | nters Idle mode  | on Sleep in     | struction            |                         |                 |       |  |  |  |

|              | 0 = Device ei      | nters Sleep mo   | de on SLEEP     | instruction          |                         |                 |       |  |  |  |

| bit 6-4      | Unimplemen         | ted: Read as '   | o'              |                      |                         |                 |       |  |  |  |

| bit 3        | OSTS: Oscilla      | ator Start-up Ti | me-out Status   | s bit <sup>(1)</sup> |                         |                 |       |  |  |  |

|              |                    | -                |                 |                      | ary oscillator is r     | •               |       |  |  |  |

|              | 0 = Oscillator     | Start-up Time    | r time-out is r | unning; primar       | y oscillator is no      | t ready         |       |  |  |  |

| bit 2        | Unimplemen         | ted: Read as '   | o'              |                      |                         |                 |       |  |  |  |

| bit 1-0      | SCS1:SCS0:         | System Clock     | Select bits     |                      |                         |                 |       |  |  |  |

|              | 1x = Internal      |                  |                 |                      |                         |                 |       |  |  |  |

|              | 01 = Timer1 c      |                  |                 |                      |                         |                 |       |  |  |  |

|              | 00 = Primary       | oscillator       |                 |                      |                         |                 |       |  |  |  |

| Note 1: D    | Depends on the sta | ate of the IESC  | Configuratio    | n bit.               |                         |                 |       |  |  |  |

|              |                    |                  |                 |                      |                         |                 |       |  |  |  |

## REGISTER 2-1: OSCCON: OSCILLATOR CONTROL REGISTER

## 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- The primary clock source is not any of the XT or HS modes

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (EC and any internal oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

# TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Microcontroller               | · Clock Source       | Exit Dolov                            | Clock Ready Status |  |

|-------------------------------|----------------------|---------------------------------------|--------------------|--|

| Before Wake-up                | After Wake-up        | Exit Delay                            | Bit (OSCCON)       |  |

|                               | XT, HS               |                                       |                    |  |

| Primary Device Clock          | XTPLL, HSPLL         | None                                  | OSTS               |  |

| (PRI_IDLE mode)               | EC                   | None                                  | 0010               |  |

|                               | INTRC <sup>(1)</sup> |                                       |                    |  |

|                               | XT, HS               | Tost <sup>(3)</sup>                   |                    |  |

| T1OSC or INTRC <sup>(1)</sup> | XTPLL, HSPLL         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS               |  |

| TIOSE OF INTROV               | EC                   | TCSD <sup>(2)</sup>                   | 0313               |  |

|                               | INTRC <sup>(1)</sup> | TIOBST <sup>(4)</sup>                 |                    |  |

|                               | XT, HS               | Tost <sup>(3)</sup>                   |                    |  |

| INTRC <sup>(1)</sup>          | XTPLL, HSPLL         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS               |  |

|                               | EC                   | TCSD <sup>(2)</sup>                   | 0313               |  |

|                               | INTRC <sup>(1)</sup> | None                                  |                    |  |

|                               | XT, HS               | Tost <sup>(3)</sup>                   |                    |  |

| None                          | XTPLL, HSPLL         | Tost + t <sub>rc</sub> <sup>(3)</sup> | - OSTS             |  |

| (Sleep mode)                  | EC                   | TCSD <sup>(2)</sup>                   | 0313               |  |

|                               | INTRC <sup>(1)</sup> | TIOBST <sup>(4)</sup>                 |                    |  |

Note 1: In this instance, refers specifically to the 31 kHz INTRC clock source.

2: TCSD (parameter 38, Table 21-10) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

**3:** TOST is the Oscillator Start-up Timer period (parameter 32, Table 21-10). t<sub>rc</sub> is the PLL lock time-out (parameter F12, Table 21-7); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39, Table 21-10), the INTRC stabilization period.

## 4.4 Brown-out Reset (BOR)

PIC18F2450/4450 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV1:BORV0 and BOREN1:BOREN0 Configuration bits. There are a total of four BOR configurations which are summarized in Table 4-1.

The BOR threshold is set by the BORV1:BORV0 bits. If BOR is enabled (any values of BOREN1:BOREN0 except '00'), any drop of VDD below VBOR (parameter D005, **Section 269 "DC Characteristics: Supply Voltage"**) for greater than TBOR (parameter 35, Table 21-10) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33, Table 21-10). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-on Timer (PWRT) are independently configured. Enabling BOR Reset does not automatically enable the PWRT.

## 4.4.1 SOFTWARE ENABLED BOR

When BOREN1:BOREN0 = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'. Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when BOR is under software control,    |

|-------|---------------------------------------------|

|       | the BOR Reset voltage level is still set by |

|       | the BORV1:BORV0 Configuration bits. It      |

|       | cannot be changed in software.              |

## 4.4.2 DETECTING BOR

When Brown-out Reset is enabled, the BOR bit always resets to '0' on any Brown-out Reset or Power-on Reset event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any Power-on Reset event. IF BOR is '0' while POR is '1', it can be reliably assumed that a Brown-out Reset event has occurred.

## 4.4.3 DISABLING BOR IN SLEEP MODE

When BOREN1:BOREN0 = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | BOR Configuration |                     |                                                                                    |

|---------|-------------------|---------------------|------------------------------------------------------------------------------------|

| BOREN1  | BOREN0            | SBOREN<br>(RCON<6>) | BOR Operation                                                                      |

| 0       | 0                 | Unavailable         | BOR disabled; must be enabled by reprogramming the Configuration bits.             |

| 0       | 1                 | Available           | BOR enabled in software; operation controlled by SBOREN.                           |

| 1       | 0                 | Unavailable         | BOR enabled in hardware in Run and Idle modes, disabled during Sleep mode.         |

| 1       | 1                 | Unavailable         | BOR enabled in hardware; must be disabled by reprogramming the Configuration bits. |

TABLE 4-1:BOR CONFIGURATIONS

## 5.3.5 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM in the data memory space. SFRs start at the top of data memory and extend downward to occupy the top segment of Bank 15, from F60h to FFFh. A list of these registers is given in Table 5-1 and Table 5-2.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the

peripheral functions. The Reset and interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of a peripheral feature are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

## TABLE 5-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F2450/4450 DEVICES

| Address | Name                    | Address | Name                    | Address | Name                  | Address | Name                 | Address | Name  |

|---------|-------------------------|---------|-------------------------|---------|-----------------------|---------|----------------------|---------|-------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | CCPR1H                | F9Fh    | IPR1                 | F7Fh    | UEP15 |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | CCPR1L                | F9Eh    | PIR1                 | F7Eh    | UEP14 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | CCP1CON               | F9Dh    | PIE1                 | F7Dh    | UEP13 |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | (2)                   | F9Ch    | (2)                  | F7Ch    | UEP12 |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | (2)                   | F9Bh    | (2)                  | F7Bh    | UEP11 |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | (2)                   | F9Ah    | (2)                  | F7Ah    | UEP10 |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | (2)                   | F99h    | (2)                  | F79h    | UEP9  |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | BAUDCON               | F98h    | (2)                  | F78h    | UEP8  |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | (2)                   | F97h    | (2)                  | F77h    | UEP7  |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | (2)                   | F96h    | TRISE <sup>(3)</sup> | F76h    | UEP6  |

| FF5h    | TABLAT                  | FD5h    | T0CON                   | FB5h    | (2)                   | F95h    | TRISD <sup>(3)</sup> | F75h    | UEP5  |

| FF4h    | PRODH                   | FD4h    | (2)                     | FB4h    | (2)                   | F94h    | TRISC                | F74h    | UEP4  |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | (2)                   | F93h    | TRISB                | F73h    | UEP3  |

| FF2h    | INTCON                  | FD2h    | HLVDCON                 | FB2h    | (2)                   | F92h    | TRISA                | F72h    | UEP2  |

| FF1h    | INTCON2                 | FD1h    | WDTCON                  | FB1h    | (2)                   | F91h    | (2)                  | F71h    | UEP1  |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRGH                | F90h    | (2)                  | F70h    | UEP0  |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | SPBRG                 | F8Fh    | (2)                  | F6Fh    | UCFG  |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | RCREG                 | F8Eh    | (2)                  | F6Eh    | UADDR |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXREG                 | F8Dh    | LATE <sup>(3)</sup>  | F6Dh    | UCON  |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | TXSTA                 | F8Ch    | LATD <sup>(3)</sup>  | F6Ch    | USTAT |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | RCSTA                 | F8Bh    | LATC                 | F6Bh    | UEIE  |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | (2)                   | F8Ah    | LATB                 | F6Ah    | UEIR  |

| FE9h    | FSR0L                   | FC9h    | (2)                     | FA9h    | (2)                   | F89h    | LATA                 | F69h    | UIE   |

| FE8h    | WREG                    | FC8h    | (2)                     | FA8h    | (2)                   | F88h    | (2)                  | F68h    | UIR   |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | (2)                     | FA7h    | EECON2 <sup>(1)</sup> | F87h    | (2)                  | F67h    | UFRMH |

|         | POSTINC1 <sup>(1)</sup> | FC6h    | (2)                     | FA6h    | EECON1                | F86h    | (2)                  | F66h    | UFRML |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | (2)                     | FA5h    | (2)                   | F85h    | (2)                  | F65h    | (2)   |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | (2)                   | F84h    | PORTE                | F64h    | (2)   |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | (2)                   | F83h    | PORTD <sup>(3)</sup> | F63h    | (2)   |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2                  | F82h    | PORTC                | F62h    | (2)   |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2                  | F81h    | PORTB                | F61h    | (2)   |

| FE0h    | BSR                     | FC0h    | ADCON2                  | FA0h    | PIE2                  | F80h    | PORTA                | F60h    | (2)   |

Note 1: Not a physical register.

2: Unimplemented registers are read as '0'.

3: These registers are implemented only on 40/44-pin devices.

## 6.5 Writing to Flash Program Memory

The minimum programming block is 8 words or 16 bytes. Word or byte programming is not supported.

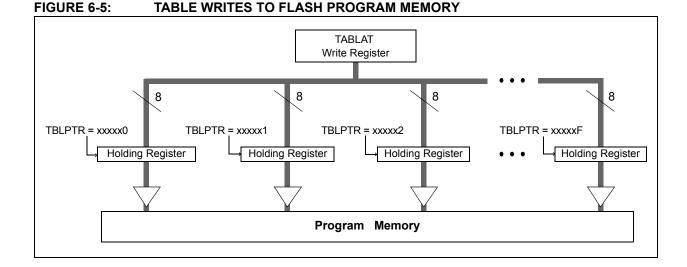

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 16 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 16 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 16 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

Note: The default value of the holding registers on device Resets and after write operations is FFh. A write of FFh to a holding register does not modify that byte. This means that individual bytes of program memory may be modified, provided that the change does not attempt to change any bit from a '0' to a '1'. When modifying individual bytes, it is not necessary to load all 16 holding registers before executing a write operation.

## 6.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the Row Erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write 16 bytes into the holding registers with auto-increment.

- 7. Set the EECON1 register for the write operation:

- clear the CFGS bit to access program memory; set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Repeat steps 6 through 14 once more to write 64 bytes.

- 15. Verify the memory (table read).

This procedure will require about 8 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 6-3.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 16 bytes in the holding register.

## 8.4 **PIE Registers**

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1 and PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

## REGISTER 8-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0 | R/W-0 | R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|--------|-----|--------|--------|--------|

| —     | ADIE  | RCIE  | TXIE — |     | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |        |     |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6          | ADIE: A/D Converter Interrupt Enable bit                                                                                                                                                                                                                                                                                                                      |

|                | 1 = Enables the A/D interrupt                                                                                                                                                                                                                                                                                                                                 |

|                | 0 = Disables the A/D interrupt                                                                                                                                                                                                                                                                                                                                |

| bit 5          | RCIE: EUSART Receive Interrupt Enable bit                                                                                                                                                                                                                                                                                                                     |

|                | <ul><li>1 = Enables the EUSART receive interrupt</li><li>0 = Disables the EUSART receive interrupt</li></ul>                                                                                                                                                                                                                                                  |

| bit 4          | TXIE: EUSART Transmit Interrupt Enable bit                                                                                                                                                                                                                                                                                                                    |

|                | 1 = Enables the EUSART transmit interrupt                                                                                                                                                                                                                                                                                                                     |

|                | 0 = Disables the EUSART transmit interrupt                                                                                                                                                                                                                                                                                                                    |

|                |                                                                                                                                                                                                                                                                                                                                                               |

| bit 3          | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                    |

| bit 3<br>bit 2 | Unimplemented: Read as '0'<br>CCP1IE: CCP1 Interrupt Enable bit                                                                                                                                                                                                                                                                                               |

|                | •                                                                                                                                                                                                                                                                                                                                                             |

|                | CCP1IE: CCP1 Interrupt Enable bit                                                                                                                                                                                                                                                                                                                             |

|                | <b>CCP1IE:</b> CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt                                                                                                                                                                                                                                                                                    |

| bit 2          | <b>CCP1IE:</b> CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt<br>0 = Disables the CCP1 interrupt                                                                                                                                                                                                                                                 |

| bit 2          | <ul> <li>CCP1IE: CCP1 Interrupt Enable bit</li> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> <li>TMR2IE: TMR2 to PR2 Match Interrupt Enable bit</li> </ul>                                                                                                                                                                |

| bit 2          | <ul> <li>CCP1IE: CCP1 Interrupt Enable bit</li> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> <li>TMR2IE: TMR2 to PR2 Match Interrupt Enable bit</li> <li>1 = Enables the TMR2 to PR2 match interrupt</li> </ul>                                                                                                           |

| bit 2<br>bit 1 | <ul> <li>CCP1IE: CCP1 Interrupt Enable bit</li> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> <li>TMR2IE: TMR2 to PR2 Match Interrupt Enable bit</li> <li>1 = Enables the TMR2 to PR2 match interrupt</li> <li>0 = Disables the TMR2 to PR2 match interrupt</li> </ul>                                                     |

| bit 2<br>bit 1 | <ul> <li>CCP1IE: CCP1 Interrupt Enable bit</li> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> <li>TMR2IE: TMR2 to PR2 Match Interrupt Enable bit</li> <li>1 = Enables the TMR2 to PR2 match interrupt</li> <li>0 = Disables the TMR2 to PR2 match interrupt</li> <li>TMR1IE: TMR1 Overflow Interrupt Enable bit</li> </ul> |

When UOWN is set, the user can no longer depend on the values that were written to the BDs. From this point, the SIE updates the BDs as necessary, overwriting the original BD values. The BDnSTAT register is updated by the SIE with the token PID and the transfer count, BDnCNT, is updated.

The BDnSTAT byte of the BDT should always be the last byte updated when preparing to arm an endpoint. The SIE will clear the UOWN bit when a transaction has completed. The only exception to this is when KEN is enabled and/or BSTALL is enabled.

No hardware mechanism exists to block access when the UOWN bit is set. Thus, unexpected behavior can occur if the microcontroller attempts to modify memory when the SIE owns it. Similarly, reading such memory may produce inaccurate data until the USB peripheral returns ownership to the microcontroller.

## 14.4.1.2 BDnSTAT Register (CPU Mode)

When UOWN = 0, the microcontroller core owns the BD. At this point, the other seven bits of the register take on control functions.

The Data Toggle Sync Enable bit, DTSEN (BDnSTAT<3>), controls data toggle parity checking. Setting DTSEN enables data toggle synchronization by the SIE. When enabled, it checks the data packet's parity against the value of DTS (BDnSTAT<6>). If a packet arrives with an incorrect synchronization, the data will essentially be ignored. It will not be written to

the USB RAM and the USB transfer complete interrupt flag will not be set. The SIE will send an ACK token back to the host to Acknowledge receipt, however. The effects of the DTSEN bit on the SIE are summarized in Table 14-3.

The Buffer Stall bit, BSTALL (BDnSTAT<2>), provides support for control transfers, usually one-time stalls on Endpoint 0. It also provides support for the SET\_FEATURE/CLEAR\_FEATURE commands specified in Chapter 9 of the USB specification; typically, continuous STALLs to any endpoint other than the default control endpoint.

The BSTALL bit enables buffer stalls. Setting BSTALL causes the SIE to return a STALL token to the host if a received token would use the BD in that location. The EPSTALL bit in the corresponding UEPn control register is set and a STALL interrupt is generated when a STALL is issued to the host. The UOWN bit remains set and the BDs are not changed unless a SETUP token is received. In this case, the STALL condition is cleared and the ownership of the BD is returned to the microcontroller core.

The BD9:BD8 bits (BDnSTAT<1:0>) store the two most significant digits of the SIE byte count; the lower 8 digits are stored in the corresponding BDnCNT register. See **Section 14.4.2 "BD Byte Count**" for more information.

| OUT Packet         | BDnSTAT | Settings | Device Response after Receiving Packet |      |       |                          |  |

|--------------------|---------|----------|----------------------------------------|------|-------|--------------------------|--|

| from Host          | DTSEN   | DTS      | Handshake                              | UOWN | TRNIF | BDnSTAT and USTAT Status |  |

| DATA0              | 1       | 0        | ACK                                    | 0    | 1     | Updated                  |  |

| DATA1              | 1       | 0        | ACK                                    | 1    | 0     | Not Updated              |  |

| DATA1              | 1       | 1        | ACK                                    | 0    | 1     | Updated                  |  |

| DATA0              | 1       | 1        | ACK                                    | 1    | 0     | Not Updated              |  |

| Either             | 0       | Х        | ACK                                    | 0    | 1     | Updated                  |  |

| Either, with error | х       | Х        | NAK                                    | 1    | 0     | Not Updated              |  |

## TABLE 14-3: EFFECT OF DTSEN BIT ON ODD/EVEN (DATA0/DATA1) PACKET RECEPTION

**Legend:** x = don't care

## 14.6 USB Power Modes

Many USB applications will likely have several different sets of power requirements and configuration. The most common power modes encountered are Bus Power Only, Self-Power Only and Dual Power with Self-Power Dominance. The most common cases are presented here.

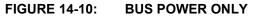

## 14.6.1 BUS POWER ONLY

In Bus Power Only mode, all power for the application is drawn from the USB (Figure 14-10). This is effectively the simplest power method for the device.

In order to meet the inrush current requirements of the USB 2.0 specifications, the total effective capacitance appearing across VBUS and ground must be no more than 10  $\mu$ F; otherwise, some kind of inrush limiting is required. For more details, see Section 7.2.4 of the USB 2.0 specification.

According to the USB 2.0 specification, all USB devices must also support a Low-Power Suspend mode. In the USB Suspend mode, devices must consume no more than 500 A (or 2.5 mA for high-powered devices that are capable of remote wake-up) from the 5V VBUS line of the USB cable.

The host signals the USB device to enter the Suspend mode by stopping all USB traffic to that device for more than 3 ms. This condition will set the IDLEIF bit in the UIR register.

During the USB Suspend mode, the D+ or D- pull-up resistor must remain active, which will consume some of the allowed suspend current: 500A/2.5 mA budget.

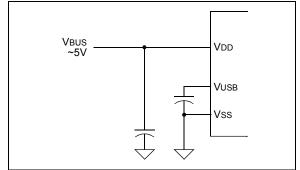

## 14.6.2 SELF-POWER ONLY

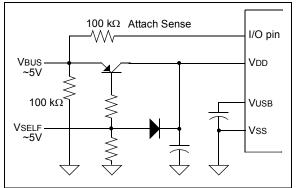

In Self-Power Only mode, the USB application provides its own power, with very little power being pulled from the USB. Figure 14-11 shows an example. Note that an attach indication is added to show when the USB has been connected and the host is actively powering VBUS. In order to meet compliance specifications, the USB module (and the D+ or D- pull-up resistor) should not be enabled until the host actively drives VBUS high. One of the I/O pins may be used for this purpose.

The application should never source any current onto the 5V VBUS pin of the USB cable.

## 14.6.3 DUAL POWER WITH SELF-POWER DOMINANCE

Some applications may require a dual power option. This allows the application to use internal power primarily, but switch to power from the USB when no internal power is available. Figure 14-12 shows a simple Dual Power with Self-Power Dominance example, which automatically switches between Self-Power Only and USB Bus Power Only modes.

## FIGURE 14-12: DUAL POWER EXAMPLE

Dual power devices must also meet all of the special requirements for inrush current and Suspend mode current, and must not enable the USB module until VBUS is driven high. For descriptions of those requirements, see Section 14.6.1 "Bus Power Only" and Section 14.6.2 "Self-Power Only". Additionally, dual power devices must never source current onto the 5V VUSB pin of the USB cable.

Note: Users should keep in mind the limits for devices drawing power from the USB. According to USB Specification 2.0, this cannot exceed 100 mA per low-power device or 500 mA per high-power device.

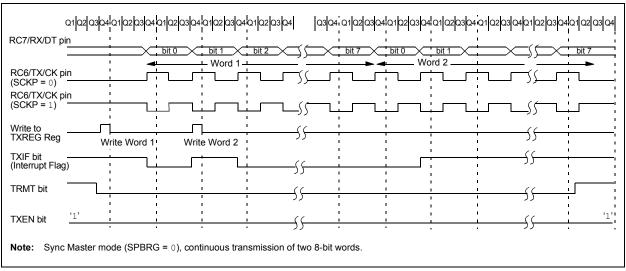

## 15.3 EUSART Synchronous Master Mode

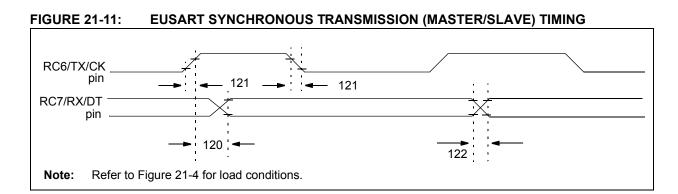

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>). Setting SCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

## 15.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 15-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG register is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user must poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## FIGURE 15-11: SYNCHRONOUS TRANSMISSION

#### EUSART SYNCHRONOUS MASTER 15.3.2 RECEPTION

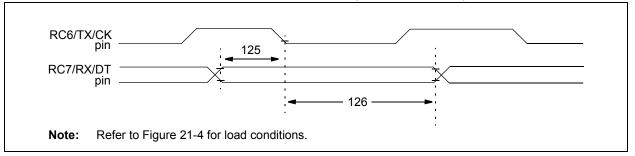

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTA<5>), or the Continuous Receive Enable bit, CREN (RCSTA<4>). Data is sampled on the RX pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- If interrupts are desired, set enable bit, RCIE. 4.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCIE, was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### **FIGURE 15-13:** SYNCHRONOUS RECEPTION (MASTER MODE, SREN) 02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03/04/01/02/03 RC7/RX/DT bit 0 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7 bit 1 pin RC6/TX/CK pin (SCKP = 0)RC6/TX/CK pin (SCKP = 1) Write to SREN bit SREN bit CREN bit '0' 'O' RCIF bit (Interrupt) Read RXREG Note: Timing diagram demonstrates Sync Master mode with SREN bit = 1 and BRGH bit = 0.

#### **TABLE 15-8**: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name      | Bit 7        | Bit 6          | Bit 5         | Bit 4         | Bit 3        | Bit 2     | Bit 1       | Bit 0    | Reset<br>Values<br>on Page: |

|-----------|--------------|----------------|---------------|---------------|--------------|-----------|-------------|----------|-----------------------------|

| INTCON    | GIE/GIEH     | PEIE/GIEL      | TMR0IE        | INT0IE        | RBIE         | TMR0IF    | INT0IF      | RBIF     | 49                          |

| PIR1      |              | ADIF           | RCIF          | TXIF          | _            | CCP1IF    | TMR2IF      | TMR1IF   | 51                          |

| PIE1      | _            | ADIE           | RCIE          | TXIE          | —            | CCP1IE    | TMR2IE      | TMR1IE   | 51                          |

| IPR1      | —            | ADIP           | RCIP          | TXIP          | —            | CCP1IP    | TMR2IP      | TMR1IP   | 51                          |

| RCSTA     | SPEN         | RX9            | SREN          | CREN          | ADDEN        | FERR      | OERR        | RX9D     | 51                          |

| RCREG     | EUSART R     | eceive Registe | r             |               |              |           |             |          | 50                          |

| TXSTA     | CSRC         | TX9            | TXEN          | SYNC          | SENDB        | BRGH      | TRMT        | TX9D     | 51                          |

| BAUDCON   | ABDOVF       | RCIDL          | _             | SCKP          | BRG16        | _         | WUE         | ABDEN    | 51                          |

| SPBRGH    | EUSART B     | aud Rate Gene  | erator Regist | er High Byte  | e            |           |             |          | 51                          |

| SPBRG     | EUSART B     | aud Rate Gene  | erator Regist | er Low Byte   | •            |           |             |          | 50                          |

| Legend: - | _ = unimplei | mented, read a | s '0' Shade   | d cells are n | not used for | synchrono | is master r | ecention |                             |

gend

| R/W-0        | U-0                                           | R/W-0                | R/W-0          | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|--------------|-----------------------------------------------|----------------------|----------------|--------------------------|------------------|-----------------|-------|--|--|--|--|

| ADFM         | _                                             | ACQT2                | ACQT1          | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |  |  |  |  |

| bit 7        |                                               |                      |                |                          |                  |                 | bit ( |  |  |  |  |

|              |                                               |                      |                |                          |                  |                 |       |  |  |  |  |

| Legend:      |                                               |                      |                |                          |                  |                 |       |  |  |  |  |

| R = Readab   | le bit                                        | W = Writable         | bit            | U = Unimplen             | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                         | '1' = Bit is set     |                | '0' = Bit is clea        | ared             | x = Bit is unkr | nown  |  |  |  |  |

| bit 7        | ADFM: A/D F                                   | esult Format S       | Select bit     |                          |                  |                 |       |  |  |  |  |

|              | 1 = Right just<br>0 = Left justifi            |                      |                |                          |                  |                 |       |  |  |  |  |

| bit 6        | Unimplemen                                    | ted: Read as '       | 0'             |                          |                  |                 |       |  |  |  |  |

| bit 5-3      | ACQT2:ACQT0: A/D Acquisition Time Select bits |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 111 <b>= 20 T</b> AD                          |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 110 <b>= 16 Tad</b>                           |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 101 <b>= 12 Tad</b>                           |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 100 <b>= 8 TAD</b>                            |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 011 = 6 TAD                                   |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 010 <b>= 4 TAD</b><br>001 <b>= 2 TAD</b>      |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 001 = 2 TAD<br>000 = 0 TAD <sup>(1</sup>      | )                    |                |                          |                  |                 |       |  |  |  |  |

| bit 2-0      |                                               | <b>S0:</b> A/D Conve | ersion Clock S | elect bits               |                  |                 |       |  |  |  |  |

|              |                                               | ock derived fro      |                |                          |                  |                 |       |  |  |  |  |

|              | 110 = Fosc/6                                  |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 100 - FOSC/04<br>101 = Fosc/16                |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 100 = Fosc/4                                  |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 011 = FRC (cl                                 | ock derived fro      | m A/D RC os    | cillator) <sup>(1)</sup> |                  |                 |       |  |  |  |  |

|              | 010 = Fosc/3                                  | 2                    |                |                          |                  |                 |       |  |  |  |  |

|              | 001 = Fosc/8                                  |                      |                |                          |                  |                 |       |  |  |  |  |

|              | 000 = Fosc/2                                  |                      |                |                          |                  |                 |       |  |  |  |  |

## REGISTER 16-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TcY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

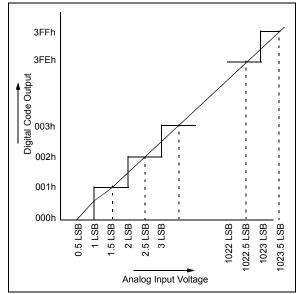

The value in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

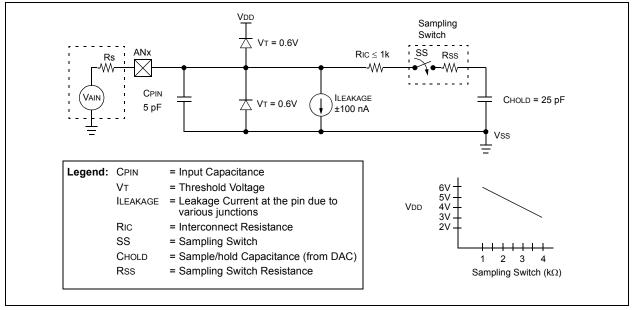

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see **Section 16.1 "A/D Acquisition Requirements"**. After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time <u>can be</u> programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

The following steps should be followed to perform an A/D conversion:

- 1. Configure the A/D module:

- Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON2)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- · Set ADIE bit

- Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

5. Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared

## OR

- · Waiting for the A/D interrupt

- Read A/D Result registers (ADRESH:ADRESL); clear bit, ADIF, if required.

- 7. For next conversion, go to step 1 or step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 3 TAD is required before the next acquisition starts.

## FIGURE 16-2: A/D TRANSFER FUNCTION

## FIGURE 16-3: ANALOG INPUT MODEL

## 16.8 Use of the CCP1 Trigger

An A/D conversion can be started by the Special Event Trigger of the CCP1 module. This requires that the CCP1M3:CCP1M0 bits (CCP1CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D acquisition and conversion, and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH:ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition period is either timed by the user, or an appropriate TACQ time <u>selected</u> before the Special Event Trigger sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the Special Event Trigger will be ignored by the A/D module but will still reset the Timer1 counter.

| Name                 | Bit 7                           | Bit 6                 | Bit 5  | Bit 4  | Bit 3                | Bit 2                 | Bit 1                 | Bit 0                 | Reset<br>Values<br>on Page: |

|----------------------|---------------------------------|-----------------------|--------|--------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------------|

| INTCON               | GIE/GIEH                        | PEIE/GIEL             | TMR0IE | INT0IE | RBIE                 | TMR0IF                | INT0IF                | RBIF                  | 49                          |

| PIR1                 | _                               | ADIF                  | RCIF   | TXIF   | _                    | CCP1IF                | TMR2IF                | TMR1IF                | 51                          |

| PIE1                 | _                               | ADIE                  | RCIE   | TXIE   | _                    | CCP1IE                | TMR2IE                | TMR1IE                | 51                          |

| IPR1                 | _                               | ADIP                  | RCIP   | TXIP   | _                    | CCP1IP                | TMR2IP                | TMR1IP                | 51                          |

| PIR2                 | OSCFIF                          | _                     | USBIF  | _      | _                    | HLVDIF                | _                     | _                     | 51                          |

| PIE2                 | OSCFIE                          | _                     | USBIE  | _      | _                    | HLVDIE                | _                     | _                     | 51                          |

| IPR2                 | OSCFIP                          | —                     | USBIP  | _      | _                    | HLVDIP                | _                     | _                     | 51                          |

| ADRESH               | H A/D Result Register High Byte |                       |        |        |                      |                       |                       |                       | 50                          |

| ADRESL               | A/D Result                      | Register Lov          | w Byte |        |                      |                       |                       |                       | 50                          |

| ADCON0               | _                               | _                     | CHS3   | CHS2   | CHS1                 | CHS0                  | GO/DONE               | ADON                  | 50                          |

| ADCON1               |                                 |                       | VCFG1  | VCFG0  | PCFG3                | PCFG2                 | PCFG1                 | PCFG0                 | 50                          |

| ADCON2               | ADFM                            |                       | ACQT2  | ACQT1  | ACQT0                | ADCS2                 | ADCS1                 | ADCS0                 | 50                          |

| PORTA                | —                               | RA6 <sup>(2)</sup>    | RA5    | RA4    | RA3                  | RA2                   | RA1                   | RA0                   | 51                          |

| TRISA                | _                               | TRISA6 <sup>(2)</sup> | TRISA5 | TRISA4 | TRISA3               | TRISA2                | TRISA1                | TRISA0                | 51                          |

| PORTB                | RB7                             | RB6                   | RB5    | RB4    | RB3                  | RB2                   | RB1                   | RB0                   | 51                          |

| TRISB                | TRISB7                          | TRISB6                | TRISB5 | TRISB4 | TRISB3               | TRISB2                | TRISB1                | TRISB0                | 51                          |

| LATB                 | LATB7                           | LATB6                 | LATB5  | LATB4  | LATB3                | LATB2                 | LATB1                 | LATB0                 | 51                          |

| PORTE                | —                               | —                     | _      | —      | RE3 <sup>(1,3)</sup> | RE2 <sup>(4)</sup>    | RE1 <sup>(4)</sup>    | RE0 <sup>(4)</sup>    | 51                          |

| TRISE <sup>(4)</sup> |                                 | _                     |        |        | _                    | TRISE2 <sup>(4)</sup> | TRISE1 <sup>(4)</sup> | TRISE0 <sup>(4)</sup> | 51                          |

| LATE <sup>(4)</sup>  |                                 |                       |        |        |                      | LATE2 <sup>(4)</sup>  | LATE1 <sup>(4)</sup>  | LATE0 <sup>(4)</sup>  | 51                          |

TABLE 16-2: REGISTERS ASSOCIATED WITH A/D OPERATION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0).

2: RA6 and its associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

3: RE3 port bit is available only as an input pin when the MCLRE Configuration bit is '0'.

4: These registers and/or bits are not implemented on 28-pin devices.

# PIC18F2450/4450

## 17.5 Applications

In many applications, the ability to detect a drop below or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

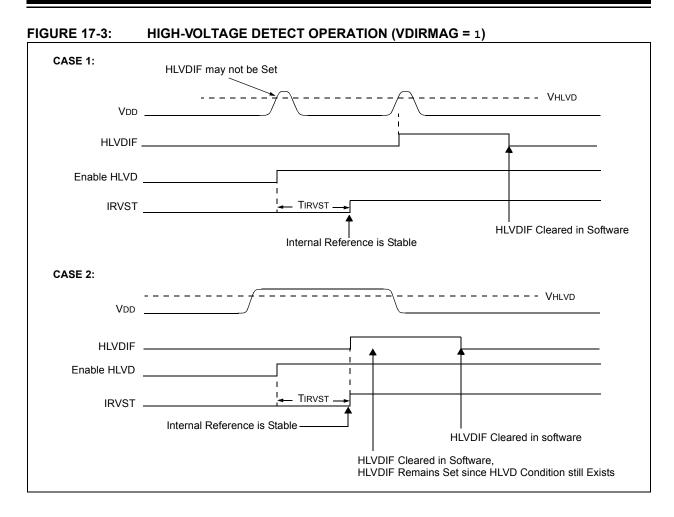

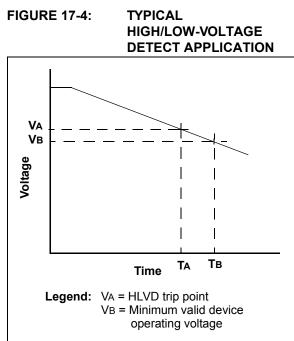

For general battery applications, Figure 17-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

## REGISTER 18-9: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0                                                                 | U-0                                                                   | U-0                                                                     | U-0             | U-0         | U-0             | R/C-1      | R/C-1 |  |  |  |  |

|---------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|-------------|-----------------|------------|-------|--|--|--|--|

| _                                                                   | _                                                                     | —                                                                       | —               | —           | —               | WRT1       | WRT0  |  |  |  |  |

| bit 7                                                               | ·                                                                     |                                                                         |                 |             |                 |            | bit 0 |  |  |  |  |

|                                                                     |                                                                       |                                                                         |                 |             |                 |            |       |  |  |  |  |

| Legend:                                                             |                                                                       |                                                                         |                 |             |                 |            |       |  |  |  |  |

| R = Readab                                                          | R = Readable bit C = Clearable bit U = Unimplemented bit, read as '0' |                                                                         |                 |             |                 |            |       |  |  |  |  |

| -n = Value v                                                        | vhen device is unp                                                    | orogrammed                                                              |                 | u = Unchang | ed from progran | nmed state |       |  |  |  |  |

|                                                                     |                                                                       |                                                                         |                 |             |                 |            |       |  |  |  |  |

| bit 7-2                                                             | Unimplement                                                           | ted: Read as '                                                          | 0'              |             |                 |            |       |  |  |  |  |

| bit 1                                                               | WRT1: Write                                                           | Protection bit                                                          |                 |             |                 |            |       |  |  |  |  |

|                                                                     | 1 = Block 1 (0                                                        | 02000-003FFF                                                            | h) is not write | e-protected |                 |            |       |  |  |  |  |

|                                                                     | 0 = Block 1 (002000-003FFFh) is write-protected                       |                                                                         |                 |             |                 |            |       |  |  |  |  |

| bit 0 WRT0: Write Protection bit                                    |                                                                       |                                                                         |                 |             |                 |            |       |  |  |  |  |

|                                                                     | (                                                                     | 1 = Block 0 (000800-001FFFh) or (001000-001FFFh) is not write-protected |                 |             |                 |            |       |  |  |  |  |

| 0 = Block 0 (000800-001FFFh) or (001000-001FFFh) is write-protected |                                                                       |                                                                         |                 |             |                 |            |       |  |  |  |  |

## REGISTER 18-10: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

| U-0   | R/C-1 | R-1                 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|---------------------|-----|-----|-----|-----|-------|

|       | WRTB  | WRTC <sup>(1)</sup> | _   | _   | —   | —   | —     |

| bit 7 |       |                     |     |     |     |     | bit 0 |

| Legend:                            |                               |                                     |  |  |  |  |

|------------------------------------|-------------------------------|-------------------------------------|--|--|--|--|

| R = Readable bit C = Clearable bit |                               | U = Unimplemented bit, read as '0'  |  |  |  |  |

| -n = Value                         | e when device is unprogrammed | u = Unchanged from programmed state |  |  |  |  |

|                                    |                               |                                     |  |  |  |  |

| bit 7                              | Unimplemented: Read as '0'    |                                     |  |  |  |  |

|         | •                                                                          |

|---------|----------------------------------------------------------------------------|

| bit 6   | WRTB: Boot Block Write Protection bit                                      |

|         | 1 = Boot block (000000-0007FFh) or (000000-000FFFh) is not write-protected |

|         | 0 = Boot block (000000-0007FFh) or (000000-000FFFh) is write-protected     |

| bit 5   | WRTC: Configuration Register Write Protection bit <sup>(1)</sup>           |

|         | 1 = Configuration registers (300000-3000FFh) are not write-protected       |

|         | 0 = Configuration registers (300000-3000FFh) are write-protected           |

| bit 4-0 | Unimplemented: Read as '0'                                                 |

|         |                                                                            |

**Note 1:** This bit is read-only in normal execution mode; it can be written only in Program mode.

#### **FIGURE 19-1: GENERAL FORMAT FOR INSTRUCTIONS** Byte-oriented file register operations **Example Instruction** 15 10 9 8 7 0 ADDWF MYREG, W, B OPCODE f (FILE #) d а d = 0 for result destination to be WREG register d = 1 for result destination to be file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Byte to Byte move operations (2-word) 15 12 11 0 OPCODE f (Source FILE #) MOVFF MYREG1, MYREG2 15 12 11 0 1111 f (Destination FILE #) f = 12-bit file register address Bit-oriented file register operations 987 15 12 11 0 OPCODE b (BIT #) a f (FILE #) BSF MYREG, bit, B b = 3-bit position of bit in file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8-bit file register address Literal operations 15 8 7 0 OPCODE k (literal) MOVLW 7Fh k = 8-bit immediate value **Control** operations CALL, GOTO and Branch operations 15 8 7 0 n<7:0> (literal) GOTO Label OPCODE 15 12 11 0 1111 n<19:8> (literal) n = 20-bit immediate value 15 8 7 0 CALL MYFUNC OPCODE S n<7:0> (literal) 15 12 11 0 n<19:8> (literal) 1111 S = Fast bit 15 0 11 10 OPCODE n<10:0> (literal) BRA MYFUNC 15 8 7 0 BC MYFUNC OPCODE n<7:0> (literal)

# PIC18F2450/4450

| BTG             | Bit Toggle f                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BOV                                                                                         | Branch if Overflow                                                                                                                                                                                                                                              |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:         | BTG f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Syntax:                                                                                     | BOV n                                                                                                                                                                                                                                                           |  |  |  |

| Operands:       | 0 ≤ f ≤ 255                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Operands:                                                                                   | -128 ≤ n ≤ 127                                                                                                                                                                                                                                                  |  |  |  |

| operando.       | $0 \le b \le 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                      | Operation:                                                                                  | if Overflow bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                       |  |  |  |

| Operation:      | $(\overline{f} \overline{b}) \to f} \mathbb{b}$                                                                                                                                                                                                                                                                                                                                                                                                                       | Status Affected:                                                                            | None                                                                                                                                                                                                                                                            |  |  |  |

| Status Affected | d: None                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Encoding:                                                                                   | 1110 0100 nnnn nnnn                                                                                                                                                                                                                                             |  |  |  |

| Encoding:       | 0111 bbba ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Description:                                                                                | If the Overflow bit is '1', then the                                                                                                                                                                                                                            |  |  |  |