Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | UART/USART, USB                                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 23                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2450-i-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

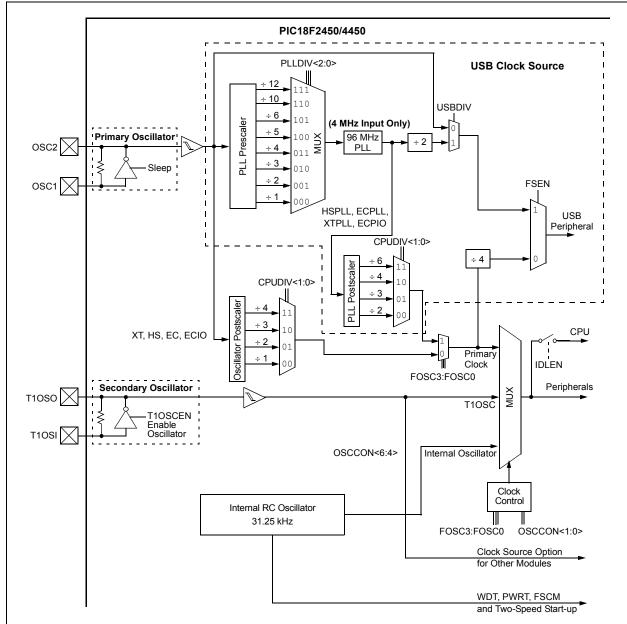

## 2.2.1 OSCILLATOR MODES AND USB OPERATION

Because of the unique requirements of the USB module, a different approach to clock operation is necessary. In previous PIC<sup>®</sup> microcontrollers, all core and peripheral clocks were driven by a single oscillator source; the usual sources were primary, secondary or the internal oscillator. With PIC18F2450/4450 devices, the primary oscillator becomes part of the USB module and cannot be associated to any other clock source. Thus, the USB module must be clocked from the primary clock source; however, the microcontroller core and other peripherals can be separately clocked from the secondary or internal oscillators as before.

Because of the timing requirements imposed by USB, an internal clock of either 6 MHz or 48 MHz is required while the USB module is enabled. Fortunately, the microcontroller and other peripherals are not required to run at this clock speed when using the primary oscillator. There are numerous options to achieve the USB module clock requirement and still provide flexibility for clocking the rest of the device from the primary oscillator source. These are detailed in **Section 2.3 "Oscillator Settings for USB"**.

#### FIGURE 2-1: PIC18F2450/4450 CLOCK DIAGRAM

## 2.5 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. Unless the USB module is enabled, the OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features regardless of the power-managed mode (see Section 18.2 "Watchdog Timer (WDT)", Section 18.3 "Two-Speed Start-up" and Section 18.4 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up).

Regardless of the Run or Idle mode selected, the USB clock source will continue to operate. If the device is operating from a crystal or resonator-based oscillator, that oscillator will continue to clock the USB module. The core and all other modules will switch to the new clock source.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Sleep mode should never be invoked while the USB module is operating and connected. The only exception is when the device has been issued a "Suspend" command over the USB. Once the module has suspended operation and shifted to a low-power state, the microcontroller may be safely put into Sleep mode.

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 21.2 "DC Characteristics: Power-Down and Supply Current".

## 2.6 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 21-10). It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval, TCSD (parameter 38, Table 21-10), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC or internal oscillator modes are used as the primary clock source.

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |  |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|--|

| INTCKO          | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |  |

| INTIO           | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |  |

| ECIO, ECPIO     | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |  |

| EC              | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |  |

| XT and HS       | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |  |

TABLE 2-4: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

| TABLE 4-4: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                                                       |           |                                                                  |                                 |  |  |  |

|------------|---------------------------------------------------------|-------------------------------------------------------|-----------|------------------------------------------------------------------|---------------------------------|--|--|--|

| Register   | Applicabl                                               | Applicable Devices Power-on Reset,<br>Brown-out Reset |           | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |

| UEP9       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP8       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP7       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP6       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP5       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP4       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP3       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP2       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP1       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UEP0       | 2450                                                    | 4450                                                  | 0 0000    | 0 0000                                                           | u uuuu                          |  |  |  |

| UCFG       | 2450                                                    | 4450                                                  | 00-0 0000 | 00-0 0000                                                        | uu-u uuuu                       |  |  |  |

| UADDR      | 2450                                                    | 4450                                                  | -000 0000 | -000 0000                                                        | -uuu uuuu                       |  |  |  |

| UCON       | 2450                                                    | 4450                                                  | -0x0 000- | -0x0 0x0-                                                        | -uuu uuu-                       |  |  |  |

| USTAT      | 2450                                                    | 4450                                                  | -XXX XXX- | -XXX XXX-                                                        | -uuu uuu-                       |  |  |  |

| UEIE       | 2450                                                    | 4450                                                  | 00 0000   | 00 0000                                                          | uu uuuu                         |  |  |  |

| UEIR       | 2450                                                    | 4450                                                  | 00 0000   | 00 0000                                                          | uu uuuu                         |  |  |  |

| UIE        | 2450                                                    | 4450                                                  | -000 0000 | -000 0000                                                        | -uuu uuuu                       |  |  |  |

| UIR        | 2450                                                    | 4450                                                  | -000 0000 | -000 0000                                                        | -uuu uuuu                       |  |  |  |

| UFRMH      | 2450                                                    | 4450                                                  | xxx       | xxx                                                              | uuu                             |  |  |  |

| UFRML      | 2450                                                    | 4450                                                  | XXXX XXXX | XXXX XXXX                                                        | นนนน นนนน                       |  |  |  |

|            |                                                         |                                                       |           |                                                                  |                                 |  |  |  |

## TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

4: See Table 4-3 for Reset value for specific condition.

**5:** PORTA<6>, LATA<6> and TRISA<6> are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

## 5.2 PIC18 Instruction Cycle

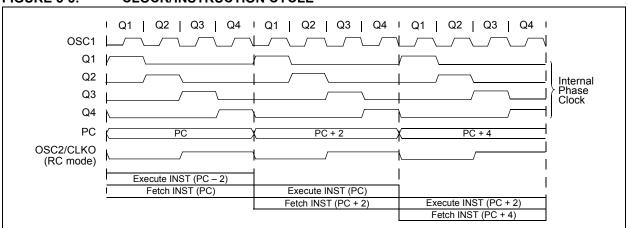

#### 5.2.1 CLOCKING SCHEME

The microcontroller clock input, whether from an internal or external source, is internally divided by four to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the program counter is incremented on every Q1; the instruction is fetched from the program memory and latched into the Instruction Register (IR) during Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 5-3.

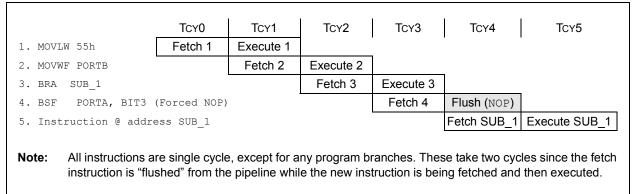

#### 5.2.2 INSTRUCTION FLOW/PIPELINING

An "Instruction Cycle" consists of four Q cycles: Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 5-3).

A fetch cycle begins with the Program Counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 5-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 5-3: INSTRUCTION PIPELINE FLOW

| File Name | Bit 7 | Bit 6              | Bit 5              | Bit 4              | Bit 3    | Bit 2   | Bit 1  | Bit 0   | Value on<br>POR, BOR | Details<br>on Page: |

|-----------|-------|--------------------|--------------------|--------------------|----------|---------|--------|---------|----------------------|---------------------|

| PORTC     | RC7   | RC6                | RC5 <sup>(6)</sup> | RC4 <sup>(6)</sup> | _        | RC2     | RC1    | RC0     | xxxx -xxx            | 51, 106             |

| PORTB     | RB7   | RB6                | RB5                | RB4                | RB3      | RB2     | RB1    | RB0     | XXXX XXXX            | 51, 100             |

| PORTA     | —     | RA6 <sup>(4)</sup> | RA5                | RA4                | RA3      | RA2     | RA1    | RA0     | -x0x 0000            | 51, 100             |

| UEP15     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP14     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP13     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP12     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP11     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP10     | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP9      | _     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP8      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP7      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP6      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP5      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP4      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP3      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP2      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP1      | _     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP0      | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UCFG      | UTEYE | UOEMON             | _                  | UPUEN              | UTRDIS   | FSEN    | PPB1   | PPB0    | 00-0 0000            | 52, 132             |

| UADDR     | —     | ADDR6              | ADDR5              | ADDR4              | ADDR3    | ADDR2   | ADDR1  | ADDR0   | -000 0000            | 52, 136             |

| UCON      | —     | PPBRST             | SE0                | PKTDIS             | USBEN    | RESUME  | SUSPND | —       | -0x0 000-            | 52, 130             |

| USTAT     | —     | ENDP3              | ENDP2              | ENDP1              | ENDP0    | DIR     | PPBI   | —       | -xxx xxx-            | 52, 134             |

| UEIE      | BTSEE | _                  | _                  | BTOEE              | DFN8EE   | CRC16EE | CRC5EE | PIDEE   | 00 0000              | 52, 148             |

| UEIR      | BTSEF | _                  | _                  | BTOEF              | DFN8EF   | CRC16EF | CRC5EF | PIDEF   | 00 0000              | 52, 147             |

| UIE       | _     | SOFIE              | STALLIE            | IDLEIE             | TRNIE    | ACTVIE  | UERRIE | URSTIE  | -000 0000            | 52, 146             |

| UIR       | —     | SOFIF              | STALLIF            | IDLEIF             | TRNIF    | ACTVIF  | UERRIF | URSTIF  | -000 0000            | 52, 144             |

| UFRMH     | —     | —                  | —                  | —                  | —        | FRM10   | FRM9   | FRM8    | xxx                  | 52, 136             |

| UFRML     | FRM7  | FRM6               | FRM5               | FRM4               | FRM3     | FRM2    | FRM1   | FRM0    | XXXX XXXX            | 52, 136             |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.

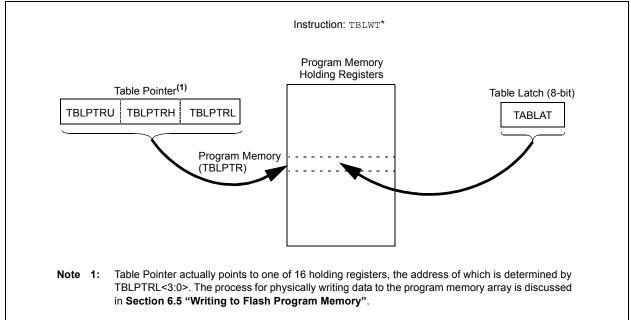

Note 1: Bit 21 of the TBLPTRU allows access to the device Configuration bits.

2: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

3: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

4: RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

### FIGURE 6-2: TABLE WRITE OPERATION

## 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- · EECON2 register

- TABLAT register

- · TBLPTR registers

#### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory. The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared when the internal programming timer expires and the write operation is complete.

| Note: | During normal operation, the WRERR is       |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | read as '1'. This can indicate that a write |  |  |  |  |  |

|       | operation was prematurely terminated by     |  |  |  |  |  |

|       | a Reset or a write operation was            |  |  |  |  |  |

|       | attempted improperly.                       |  |  |  |  |  |

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

| PROGRAM_MEMORY | Y          |                              |                                                           |

|----------------|------------|------------------------------|-----------------------------------------------------------|

|                | BCF<br>BSF | EECON1, CFGS<br>EECON1, WREN | ; access Flash program memory<br>; enable write to memory |

|                |            | ,                            | -                                                         |

|                | BCF        | INTCON, GIE                  | ; disable interrupts                                      |

|                | MOVLW      | 55h                          |                                                           |

| Required       | MOVWF      | EECON2                       | ; write 55h                                               |

| Sequence       | MOVLW      | 0AAh                         |                                                           |

|                | MOVWF      | EECON2                       | ; write OAAh                                              |

|                | BSF        | EECON1, WR                   | ; start program (CPU stall)                               |

|                | DECFSZ     | COUNTER1                     |                                                           |

|                | BRA        | WRITE BUFFER BACK            |                                                           |

|                | BSF        | INTCON, GIE                  | ; re-enable interrupts                                    |

|                | BCF        | EECON1, WREN                 | ; disable write to memory                                 |

#### 6.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 6.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed <u>if needed</u>. If the write operation is interrupted by a MCLR Reset or a WDT time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

#### 6.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 18.0 "Special Features of the CPU" for more detail.

#### 6.6 Flash Program Operation During Code Protection

See Section 18.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| Name    | Bit 7                                                    | Bit 6                                               | Bit 5       | Bit 4        | Bit 3         | Bit 2        | Bit 1        | Bit 0      | Reset<br>Values<br>on Page: |

|---------|----------------------------------------------------------|-----------------------------------------------------|-------------|--------------|---------------|--------------|--------------|------------|-----------------------------|

| TBLPTRU | _                                                        |                                                     | bit 21      | Program Me   | emory Table F | Pointer Uppe | r Byte (TBLP | TR<20:16>) | 49                          |

| TBPLTRH | Program M                                                | emory Table                                         | e Pointer H | igh Byte (TB | LPTR<15:8     | >)           |              |            | 49                          |

| TBLPTRL | Program M                                                | Program Memory Table Pointer Low Byte (TBLPTR<7:0>) |             |              |               | 49           |              |            |                             |

| TABLAT  | Program M                                                | emory Table                                         | e Latch     |              |               |              |              |            | 49                          |

| INTCON  | GIE/GIEH                                                 | PEIE/GIEL                                           | TMR0IE      | INT0IE       | RBIE          | TMR0IF       | INT0IF       | RBIF       | 49                          |

| EECON2  | Data Memory Control Register 2 (not a physical register) |                                                     |             |              | 51            |              |              |            |                             |

| EECON1  | —                                                        | CFGS                                                | —           | FREE         | WRERR         | WREN         | WR           | _          | 51                          |

| IPR2    | OSCFIP                                                   | _                                                   | USBIP       | —            | _             | HLVDIP       | _            | _          | 51                          |

| PIR2    | OSCFIF                                                   | —                                                   | USBIF       | —            | _             | HLVDIF       | _            | _          | 51                          |

| PIE2    | OSCFIE                                                   | _                                                   | USBIE       | —            | _             | HLVDIE       | _            | _          | 51                          |

TABLE 6-2:

REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash access.

## 9.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Output Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

| Note: | On a Power-on Reset, RB4:RB0 are configured as analog inputs by default and read as '0'; RB7:RB5 are configured as digital inputs.      |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|

|       | By programming the Configuration bit,<br>PBADEN (CONFIG3H<1>), RB4:RB0 will<br>alternatively be configured as digital inputs<br>on POR. |

|       |                                                                                                                                         |

Four of the PORTB pins (RB7:RB4) have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur. Any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison. The pins are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

The interrupt-on-change can be used to wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Wait one or more instruction cycles.

- c) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

Pins, RB2 and RB3, are multiplexed with the USB peripheral and serve as the differential signal outputs for an external USB transceiver (TRIS configuration). Refer to **Section 14.2.2.2 "External Transceiver"** for additional information on configuring the USB module for operation with an external transceiver.

|       | -      |                                                              |

|-------|--------|--------------------------------------------------------------|

| CLRF  | PORTB  | ; Initialize PORTB by<br>; clearing output<br>; data latches |

| CLRF  | LATB   | ; Alternate method<br>; to clear output                      |

|       |        | ; data latches                                               |

| MOVLW | OEh    | ; Set RB<4:0> as                                             |

| MOVWF | ADCON1 | ; digital I/O pins                                           |

|       |        | ; (required if config bit<br>; PBADEN is set)                |

| MOVLW | OCFh   | ; Value used to                                              |

|       |        | ; initialize data                                            |

|       |        | ; direction                                                  |

| MOVWF | TRISB  | ; Set RB<3:0> as inputs                                      |

|       |        | ; RB<5:4> as outputs                                         |

|       |        | ; RB<7:6> as inputs                                          |

|       |        |                                                              |

NOTES:

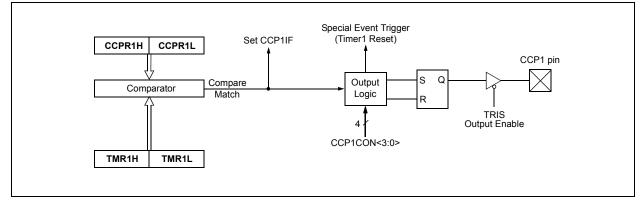

## 13.3 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 pin can be:

- driven high

- driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP1M3:CCP1M0). At the same time, the interrupt flag bit, CCP1IF, is set.

#### 13.3.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCP1CON register will force |

|-------|------------------------------------------|

|       | the RC2 compare output latch to the      |

|       | default low level.                       |

#### 13.3.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 13.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP1M3:CCP1M0 = 1010), the CCP1 pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCP1IE bit is set.

#### 13.3.4 SPECIAL EVENT TRIGGER

The CCP module is equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP1M3:CCP1M0 = 1011).

For the CCP module, the Special Event Trigger resets the Timer1 register pair. This allows the CCPR1 registers to serve as a programmable period register for the Timer1.

The Special Event Trigger for CCP1 can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

### FIGURE 13-2: COMPARE MODE OPERATION BLOCK DIAGRAM

## TABLE 14-4: ASSIGNMENT OF BUFFER DESCRIPTORS FOR THE DIFFERENT BUFFERING MODES

|          |                          |    | BDs Ass      | igned to Endpoi     | int            |                     |

|----------|--------------------------|----|--------------|---------------------|----------------|---------------------|

| Endpoint | Mode 0<br>(No Ping-Pong) |    | Мо           | de 1<br>on EP0 OUT) | Мо             | de 2<br>on all EPs) |

|          | Out                      | In | Out          | In                  | Out            | In                  |

| 0        | 0                        | 1  | 0 (E), 1 (O) | 2                   | 0 (E), 1 (O)   | 2 (E), 3 (O)        |

| 1        | 2                        | 3  | 3            | 4                   | 4 (E), 5 (O)   | 6 (E), 7 (O)        |

| 2        | 4                        | 5  | 5            | 6                   | 8 (E), 9 (O)   | 10 (E), 11 (O)      |

| 3        | 6                        | 7  | 7            | 8                   | 12 (E), 13 (O) | 14 (E), 15 (O)      |

| 4        | 8                        | 9  | 9            | 10                  | 16 (E), 17 (O) | 18 (E), 19 (O)      |

| 5        | 10                       | 11 | 11           | 12                  | 20 (E), 21 (O) | 22 (E), 23 (O)      |

| 6        | 12                       | 13 | 13           | 14                  | 24 (E), 25 (O) | 26 (E), 27 (O)      |

| 7        | 14                       | 15 | 15           | 16                  | 28 (E), 29 (O) | 30 (E), 31 (O)      |

| 8        | 16                       | 17 | 17           | 18                  | 32 (E), 33 (O) | 34 (E), 35 (O)      |

| 9        | 18                       | 19 | 19           | 20                  | 36 (E), 37 (O) | 38 (E), 39 (O)      |

| 10       | 20                       | 21 | 21           | 22                  | 40 (E), 41 (O) | 42 (E), 43 (O)      |

| 11       | 22                       | 23 | 23           | 24                  | 44 (E), 45 (O) | 46 (E), 47 (O)      |

| 12       | 24                       | 25 | 25           | 26                  | 48 (E), 49 (O) | 50 (E), 51 (O)      |

| 13       | 26                       | 27 | 27           | 28                  | 52 (E), 53 (O) | 54 (E), 55 (O)      |

| 14       | 28                       | 29 | 29           | 30                  | 56 (E), 57 (O) | 58 (E), 59 (O)      |

| 15       | 30                       | 31 | 31           | 32                  | 60 (E), 61 (O) | 62 (E), 63 (O)      |

Legend: (E) = EVEN transaction buffer, (O) = ODD transaction buffer

#### TABLE 14-5: SUMMARY OF USB BUFFER DESCRIPTOR TABLE REGISTERS

| Name                   | Bit 7      | Bit 6              | Bit 5               | Bit 4               | Bit 3                                       | Bit 2                                        | Bit 1 | Bit 0 |  |

|------------------------|------------|--------------------|---------------------|---------------------|---------------------------------------------|----------------------------------------------|-------|-------|--|

| BDnSTAT <sup>(1)</sup> | UOWN       | DTS <sup>(4)</sup> | PID3 <sup>(2)</sup> | PID2 <sup>(2)</sup> | PID1 <sup>(2)</sup><br>DTSEN <sup>(3)</sup> | PID0 <sup>(2)</sup><br>BSTALL <sup>(3)</sup> | BC9   | BC8   |  |

| BDnCNT <sup>(1)</sup>  | Byte Count |                    |                     |                     |                                             |                                              |       |       |  |

| BDnADRL <sup>(1)</sup> | Buffer Add | Buffer Address Low |                     |                     |                                             |                                              |       |       |  |

| BDnADRH <sup>(1)</sup> | Buffer Add | ress High          |                     |                     |                                             |                                              |       |       |  |

**Note 1:** For buffer descriptor registers, n may have a value of 0 to 63. For the sake of brevity, all 64 registers are shown as one generic prototype. All registers have indeterminate Reset values (xxxx xxxx).

2: Bits 5 through 2 of the BDnSTAT register are used by the SIE to return PID3:PID0 values once the register is turned over to the SIE (UOWN bit is set). Once the registers have been under SIE control, the values written for DTSEN and BSTALL are no longer valid.

**3:** Prior to turning the buffer descriptor over to the SIE (UOWN bit is cleared), bits 3 and 2 of the BDnSTAT register are used to configure the DTSEN and BSTALL settings.

**4:** This bit is ignored unless DTSEN = 1.

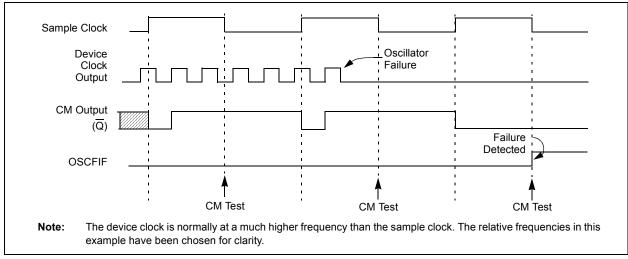

#### 18.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Clock Monitoring of the powermanaged clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTRC. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTRC source.

#### 18.4.4 POR OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is either EC or INTRC, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL or XT), the situation is somewhat different. Since the oscillator may require a start-up time

considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

Note: The same logic that prevents false oscillator failure interrupts on POR or wake from Sleep will also prevent the detection of the oscillator's failure to start at all following these events. This can be avoided by monitoring the OSTS bit and using a timing routine to determine if the oscillator is taking too long to start. Even so, no oscillator failure interrupt will be flagged.

As noted in Section 18.3.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new power-managed mode is selected, the primary clock is disabled.

| SLEEP                   | Enter Sle                                           | ep Mode         |                                                                                                                                                                                                                                                                           | SUBFWB                          | Subtract                   | f from W with                            | Borrow               |  |

|-------------------------|-----------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------|------------------------------------------|----------------------|--|

| Syntax:                 | SLEEP                                               |                 |                                                                                                                                                                                                                                                                           | Syntax:                         | SUBFWE                     | } f {,d {,a}}                            |                      |  |

| Operands:               | None                                                |                 |                                                                                                                                                                                                                                                                           | Operands:                       | $0 \le f \le 258$          | 5                                        |                      |  |

| Operation:              | $00h \rightarrow WE$                                | DT,             |                                                                                                                                                                                                                                                                           |                                 | d ∈ [0,1]                  |                                          |                      |  |

|                         |                                                     | postscaler,     |                                                                                                                                                                                                                                                                           |                                 | a ∈ [0,1]                  |                                          |                      |  |

|                         | $1 \rightarrow \underline{TO}, \\ 0 \rightarrow PD$ |                 |                                                                                                                                                                                                                                                                           | Operation:                      |                            | $(\overline{C}) \rightarrow \text{dest}$ |                      |  |

| Status Affected:        | TO, PD                                              |                 |                                                                                                                                                                                                                                                                           | Status Affected:                | N, OV, C,                  |                                          |                      |  |

| Encoding:               | 0000                                                | 0000 000        | 0 0011                                                                                                                                                                                                                                                                    | Encoding:                       | 0101                       |                                          |                      |  |

| Description:            | Description.                                        | Description:    | Subtract register 'f' and Carry flag<br>(borrow) from W (2's complement<br>method). If 'd' is '0', the result is st<br>in W. If 'd' is '1', the result is store<br>register 'f' (default).<br>If 'a' is '0', the Access Bank is<br>selected. If 'a' is '1', the BSR is us |                                 |                            |                                          |                      |  |

| Words:                  | 1                                                   |                 |                                                                                                                                                                                                                                                                           |                                 |                            | he GPR bank<br>and the extend            |                      |  |

| Cycles:                 | 1                                                   |                 |                                                                                                                                                                                                                                                                           |                                 |                            | bled, this instru                        |                      |  |

| Q Cycle Activity:       |                                                     |                 |                                                                                                                                                                                                                                                                           |                                 | •                          | n Indexed Lite                           |                      |  |

| Q1                      | Q2                                                  | Q3              | Q4                                                                                                                                                                                                                                                                        |                                 |                            | ig mode when<br>h). See <b>Sectio</b>    |                      |  |

| Decode                  | No<br>operation                                     | Process<br>Data | Go to<br>Sleep                                                                                                                                                                                                                                                            |                                 | "Byte-Ori                  | ented and Bit                            |                      |  |

| L                       |                                                     | 1               | ·                                                                                                                                                                                                                                                                         |                                 | Mode" for                  |                                          |                      |  |

| Example:                | SLEEP                                               |                 |                                                                                                                                                                                                                                                                           | Words:                          | 1                          |                                          |                      |  |

| Befor <u>e I</u> nstruc |                                                     |                 |                                                                                                                                                                                                                                                                           | Cycles:                         | 1                          |                                          |                      |  |

| <u>TO</u> =<br>PD =     | ?<br>?                                              |                 |                                                                                                                                                                                                                                                                           | Q Cycle Activity:               |                            |                                          |                      |  |

| After Instructi         | •                                                   |                 |                                                                                                                                                                                                                                                                           | Q1                              | Q2                         | Q3                                       | Q4                   |  |

| $\frac{TO}{PD} =$       | 1†<br>0                                             |                 |                                                                                                                                                                                                                                                                           | Decode                          | Read<br>register 'f'       | Process<br>Data                          | Write to destination |  |

|                         |                                                     | it is also and  |                                                                                                                                                                                                                                                                           | Example 1:                      | SUBFWB                     | REG, 1, 0                                | )                    |  |

| † If WDT causes         | wake-up, this t                                     | dit is cleared. |                                                                                                                                                                                                                                                                           | Before Instruc<br>REG<br>W<br>C | ction<br>= 3<br>= 2<br>= 1 |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | After Instructi<br>REG          | on<br>= FF                 |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | W                               | = 2<br>= 0                 |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | C<br>Z                          | = 0                        |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | N<br>Everanla 2:                |                            | sult is negativ                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | Example 2:<br>Before Instrue    | SUBFWB                     | REG, 0, 0                                |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | REG                             | = 2                        |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | W<br>C                          | = 5<br>= 1                 |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | After Instructi                 |                            |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | REG<br>W                        | = 2<br>= 3                 |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | C<br>Z                          | = 1<br>= 0                 |                                          |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | Ν                               | = 0 ; re                   | sult is positive                         |                      |  |

|                         |                                                     |                 |                                                                                                                                                                                                                                                                           | Example 3:                      | SUBFWB                     | REG, 1, 0                                | )                    |  |

$\begin{array}{rcl} \mathsf{REG} &=& 2\\ \mathsf{W} &=& 3\\ \mathsf{C} &=& 1\\ \mathsf{Z} &=& 0\\ \mathsf{N} &=& 0 \ ; \text{ result is positive}\\ \hline \mathsf{mple 3:} & \mathsf{SUBFWB} & \mathsf{REG}, \ 1, \ 0\\ \hline \\ \text{Before Instruction}\\ & \mathsf{REG} &=& 1\\ \mathsf{W} &=& 2\\ \mathsf{C} &=& 0\\ \hline \\ \text{After Instruction}\\ & \mathsf{REG} &=& 0\\ \mathsf{W} &=& 2\\ \mathsf{C} &=& 1\\ \mathsf{Z} &=& 1\\ \mathsf{Z} &=& 1\\ \mathsf{Z} &=& 1 \end{array}; \text{ result is zero}\\ & \mathsf{N} &=& 0\\ \hline \end{array}$

## 19.2.2 EXTENDED INSTRUCTION SET

| ADD   | FSR                                        | Add Literal to FSR      |                  |      |          |  |  |

|-------|--------------------------------------------|-------------------------|------------------|------|----------|--|--|

| Synta | ax:                                        | ADDFSR                  | ADDFSR f, k      |      |          |  |  |

| Oper  | ands:                                      | $0 \le k \le 63$        | $0 \le k \le 63$ |      |          |  |  |

|       |                                            | $f \in [0, 1, 2]$       |                  |      |          |  |  |

| Oper  | Operation: $FSR(f) + k \rightarrow FSR(f)$ |                         |                  |      |          |  |  |

| Statu | Status Affected: None                      |                         |                  |      |          |  |  |

| Enco  | ding:                                      | 1110                    | 1000             | ffkk | kkkk     |  |  |

| Desc  | ription:                                   | The 6-bit l contents of |                  |      |          |  |  |

| Word  | ls:                                        | 1                       |                  |      |          |  |  |

| Cycle | es:                                        | 1                       |                  |      |          |  |  |

| QC    | ycle Activity:                             |                         |                  |      |          |  |  |

|       | Q1                                         | Q2                      | Q3               |      | Q4       |  |  |

|       | Decode                                     | Read                    | Proces           | SS   | Write to |  |  |

|       |                                            | literal 'k'             | Data             |      | FSR      |  |  |

Example: ADDFSR 2, 23h

Before Instruction FSR2 = 03FFh After Instruction

FSR2 = 0422h

| ADD   | ULNK          | Add Literal to FSR2 and Return                                                                                                |                                                                                                                                                                                                                                                                                                                             |     |                 |  |  |  |

|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|--|--|--|

| Synta | ax:           | ADDULNI                                                                                                                       | ( k                                                                                                                                                                                                                                                                                                                         |     |                 |  |  |  |

| Opera | ands:         | $0 \le k \le 63$                                                                                                              |                                                                                                                                                                                                                                                                                                                             |     |                 |  |  |  |

| Opera | ation:        | FSR2 + k                                                                                                                      | $\rightarrow$ FSR2                                                                                                                                                                                                                                                                                                          | ,   |                 |  |  |  |

|       |               | $(TOS) \rightarrow I$                                                                                                         | PC                                                                                                                                                                                                                                                                                                                          |     |                 |  |  |  |

| Statu | s Affected:   | None                                                                                                                          | None                                                                                                                                                                                                                                                                                                                        |     |                 |  |  |  |

| Enco  | ding:         | 1110                                                                                                                          | 1110 1000 11kk kkkk                                                                                                                                                                                                                                                                                                         |     |                 |  |  |  |

|       | ription:      | contents of<br>executed<br>TOS.<br>The instru<br>execute; a<br>the secon<br>This may<br>case of th<br>where f =<br>only on FS | The 6-bit literal 'k' is added to the contents of FSR2. A RETURN is then executed by loading the PC with the TOS.<br>The instruction takes two cycles to execute; a NOP is performed during the second cycle.<br>This may be thought of as a special case of the ADDFSR instruction, where f = 3 (binary '11'); it operates |     |                 |  |  |  |

| Word  | 0.            | 1                                                                                                                             |                                                                                                                                                                                                                                                                                                                             |     |                 |  |  |  |

| Cycle |               | 2                                                                                                                             |                                                                                                                                                                                                                                                                                                                             |     |                 |  |  |  |

| QC    | cle Activity: |                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |     |                 |  |  |  |

| -     | Q1            | Q2                                                                                                                            | Q3                                                                                                                                                                                                                                                                                                                          |     | Q4              |  |  |  |

|       | Decode        | Read<br>literal 'k'                                                                                                           | Proces<br>Data                                                                                                                                                                                                                                                                                                              |     | Write to<br>FSR |  |  |  |

|       | No            | No                                                                                                                            | No                                                                                                                                                                                                                                                                                                                          |     | No              |  |  |  |

|       | Operation     | Operation                                                                                                                     | Operati                                                                                                                                                                                                                                                                                                                     | ion | Operation       |  |  |  |

|       |               |                                                                                                                               |                                                                                                                                                                                                                                                                                                                             |     |                 |  |  |  |

Example: ADDULNK 23h

| Before Instru  | ction |       |

|----------------|-------|-------|

| FSR2           | =     | 03FFh |

| PC             | =     | 0100h |

| After Instruct | ion   |       |

| FSR2           | =     | 0422h |

| PC             | =     | (TOS) |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

| SUBFSR            | Subtract         | Subtract Literal from FSR |         |            |  |  |  |

|-------------------|------------------|---------------------------|---------|------------|--|--|--|

| Syntax:           | SUBFSR           | f, k                      |         |            |  |  |  |

| Operands:         | $0 \le k \le 63$ | $0 \le k \le 63$          |         |            |  |  |  |

|                   | f ∈ [ 0, 1,      | f ∈ [ 0, 1, 2 ]           |         |            |  |  |  |

| Operation:        | FSRf – k         | $\rightarrow$ FSRf        |         |            |  |  |  |

| Status Affected:  | None             |                           |         |            |  |  |  |

| Encoding:         | 1110             | 1001                      | ffkk    | kkkk       |  |  |  |

| Description:      | The 6-bit        | literal 'k' is            | subtra  | cted from  |  |  |  |

|                   | the conter       | nts of the                | FSR spe | ecified by |  |  |  |

|                   | ʻf'.             |                           |         |            |  |  |  |

| Words:            | 1                | 1                         |         |            |  |  |  |

| Cycles:           | 1                |                           |         |            |  |  |  |

| Q Cycle Activity: |                  |                           |         |            |  |  |  |

| Q1                | Q2               | Q3                        |         | Q4         |  |  |  |

| Decode            | Read             | Proce                     | ss      | Write to   |  |  |  |

|                   | register 'f'     | Data                      | a d     | estination |  |  |  |

|                   |                  |                           |         |            |  |  |  |

| Example:          | SUBFSR           | 2, 23h                    |         |            |  |  |  |

|                   | 00010100, 00 |

|-------------------|--------------|

| Before Instructio | n            |

| FSR2 =            | 03FFh        |

| After Instruction |              |

| FSR2 =            | 03DCh        |

|                   |              |

| Syntax:                           | SUBULNK k                                                                                                                                                                                                                       |                                 |                                                    |                                                 |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------|-------------------------------------------------|--|

| Operands:                         | 0 < k < 63                                                                                                                                                                                                                      |                                 |                                                    |                                                 |  |

| Operation:                        | $FSR2 - k \rightarrow FSR2$                                                                                                                                                                                                     | R2                              |                                                    |                                                 |  |

| operation.                        | $(TOS) \rightarrow PC$                                                                                                                                                                                                          | 112,                            |                                                    |                                                 |  |