Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | UART/USART, USB                                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 23                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2450t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

• PIC18F2450 • PIC18F4450

This family of devices offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Enhanced Flash program memory. In addition to these features, the PIC18F2450/4450 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power sensitive applications.

## 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2450/4450 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal RC oscillator, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-Fly Mode Switching: The powermanaged modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 21.0 "Electrical Characteristics" for values.

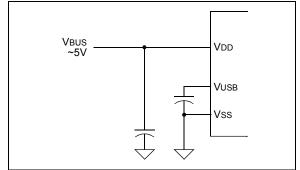

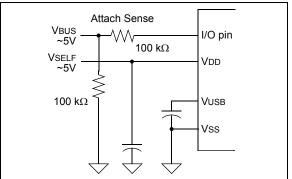

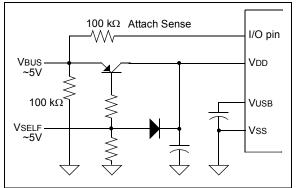

#### 1.1.2 UNIVERSAL SERIAL BUS (USB)

Devices in the PIC18F2450/4450 family incorporate a fully featured Universal Serial Bus communications module that is compliant with the USB Specification Revision 2.0. The module supports both low-speed and full-speed communication for all supported data transfer types. It also incorporates its own on-chip transceiver and 3.3V regulator and supports the use of external transceivers and voltage regulators.

#### 1.1.3 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2450/4450 family offer twelve different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes using crystals or ceramic resonators.

- Four External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- An INTRC source (approximately 31 kHz, stable over temperature and VDD). This option frees an oscillator pin for use as an additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and External Oscillator modes, which allows a wide range of clock speeds from 4 MHz to 48 MHz.

- Asynchronous dual clock operation, allowing the USB module to run from a high-frequency oscillator while the rest of the microcontroller is clocked from an internal low-power oscillator.

The internal oscillator provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

| Input Oscillator<br>Frequency | PLL Division<br>(PLLDIV2:PLLDIV0) | Clock Mode<br>(FOSC3:FOSC0) | MCU Clock Division<br>(CPUDIV1:CPUDIV0) | Microcontroller<br>Clock Frequency |

|-------------------------------|-----------------------------------|-----------------------------|-----------------------------------------|------------------------------------|

|                               |                                   |                             | None (00)                               | 12 MHz                             |

|                               |                                   |                             | ÷2(01)                                  | 6 MHz                              |

|                               |                                   | HS, EC, ECIO                | ÷3 (10)                                 | 4 MHz                              |

| 12 MHz                        | (0,1,0)                           |                             | ÷4 (11)                                 | 3 MHz                              |

| 12 MHZ                        | ÷3 (010)                          |                             | ÷2 (00)                                 | 48 MHz                             |

|                               |                                   | HSPLL, ECPLL, ECPIO         | ÷3(01)                                  | 32 MHz                             |

|                               |                                   | HSPLL, ECPLL, ECPIO         | ÷4 (10)                                 | 24 MHz                             |

|                               |                                   |                             | ÷6 (11)                                 | 16 MHz                             |

|                               |                                   |                             | None (00)                               | 8 MHz                              |

|                               |                                   | HS, EC, ECIO                | ÷2(01)                                  | 4 MHz                              |

|                               | · <b>2</b> (001)                  | по, ec, ecio                | ÷3(10)                                  | 2.67 MHz                           |

| 8 MHz                         |                                   |                             | ÷4 (11)                                 | 2 MHz                              |

|                               | ÷2(001)                           |                             | ÷2 (00)                                 | 48 MHz                             |

|                               |                                   | HSPLL, ECPLL, ECPIO         | ÷3(01)                                  | 32 MHz                             |

|                               |                                   | HOPLL, EUPLL, EUPIU         | ÷4 (10)                                 | 24 MHz                             |

|                               |                                   |                             | ÷6 (11)                                 | 16 MHz                             |

|                               |                                   |                             | None (00)                               | 4 MHz                              |

|                               |                                   |                             | ÷2(01)                                  | 2 MHz                              |

|                               |                                   | XT, HS, EC, ECIO            | ÷3(10)                                  | 1.33 MHz                           |

|                               | .1 (000)                          |                             | ÷4 (11)                                 | 1 MHz                              |

| 4 MHz                         | ÷1 (000)                          |                             | ÷2 (00)                                 | 48 MHz                             |

|                               |                                   | HSPLL, ECPLL, XTPLL,        | ÷3(01)                                  | 32 MHz                             |

|                               |                                   | ECPIO                       | ÷4 (10)                                 | 24 MHz                             |

|                               |                                   |                             | ÷6 (11)                                 | 16 MHz                             |

#### TABLE 2-3: OSCILLATOR CONFIGURATION OPTIONS FOR USB OPERATION (CONTINUED)

Legend: All clock frequencies, except 24 MHz, are exclusively associated with full-speed USB operation (USB clock of 48 MHz). Bold is used to highlight clock selections that are compatible with low-speed USB operation (system clock of 24 MHz, USB clock of 6 MHz).

Note 1: Only valid when the USBDIV Configuration bit is cleared.

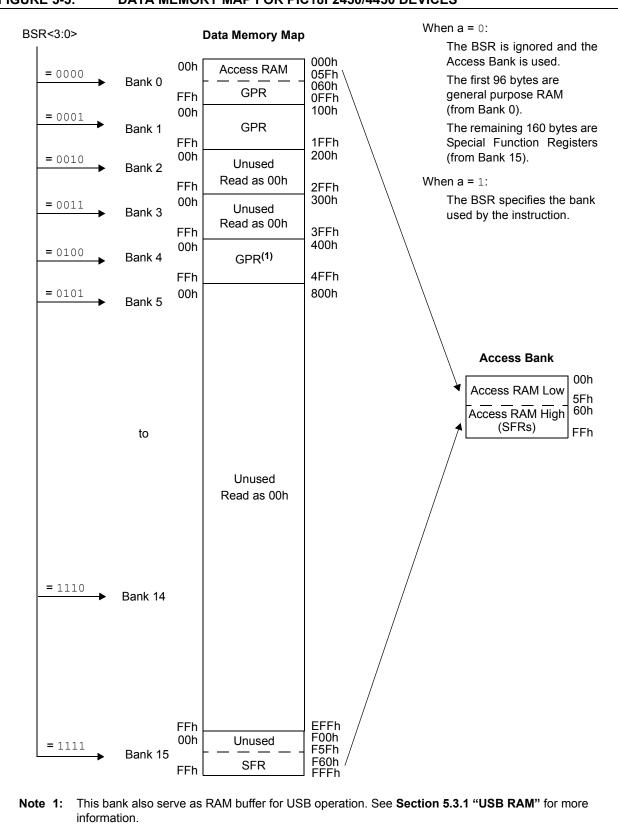

#### FIGURE 5-5: DATA MEMORY MAP FOR PIC18F2450/4450 DEVICES

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function                                                                                  | TRIS<br>Setting | I/O | I/О Туре                                                 | Description                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|-----|----------------------------------------------------------|----------------------------------------------------------------------------------------------|

| RA0/AN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RA0                                                                                       | 0               | OUT | DIG                                                      | LATA<0> data output; not affected by analog input.                                           |

| PinFunctionSettingI/OI/OI/OTypeRA0/AN0RA00OUTDIGLATA<0> data of<br>1AN01INTTLPORTA<0> data of<br>digital output.RA1/AN1RA10OUTDIGLATA<1> data of<br>digital output.RA1/AN1RA10OUTDIGLATA<1> data of<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |                 |     | PORTA<0> data input; disabled when analog input enabled. |                                                                                              |

| Image: |                                                                                           |                 |     |                                                          | A/D input channel 0. Default configuration on POR; does not affect digital output.           |

| RA1/AN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RA1                                                                                       | 0               | OUT | DIG                                                      | LATA<1> data output; not affected by analog input.                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           | 1               | IN  | TTL                                                      | PORTA<1> data input; reads '0' on POR.                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AN1                                                                                       | 1               | IN  | ANA                                                      | A/D input channel 1. Default configuration on POR; does not affect digital output.           |

| RA2/AN2/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RA2                                                                                       | 0               | OUT | DIG                                                      | LATA<2> data output; not affected by analog input.                                           |

| VREF-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AN2     1     IN     ANA     A/D input channel 2. Default configuration of analog output. |                 |     |                                                          |                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AN2                                                                                       | 1               | IN  | ANA                                                      | A/D input channel 2. Default configuration on POR; not affected by analog output.            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A/D voltage reference low input.                                                          |                 |     |                                                          |                                                                                              |

| RA3/AN3/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RA3                                                                                       | 0               | OUT | DIG                                                      | LATA<3> data output; not affected by analog input.                                           |

| VREF+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           | 1               | IN  | TTL                                                      | PORTA<3> data input; disabled when analog input enabled.                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AN3                                                                                       | 1               | IN  | ANA                                                      | A/D input channel 3. Default configuration on POR.                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A/D voltage reference high input.                                                         |                 |     |                                                          |                                                                                              |

| RA4/T0CKI/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RA4                                                                                       | 0               | OUT | DIG                                                      | LATA<4> data output; not affected by analog input.                                           |

| RCV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                           | 1               | IN  | ST                                                       | PORTA<4> data input; disabled when analog input enabled.                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T0CKI                                                                                     | 1               | IN  | ST                                                       | Timer0 clock input.                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RCV                                                                                       | x               | IN  | TTL                                                      | External USB transceiver RCV input.                                                          |

| RA5/AN4/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RA5                                                                                       | 0               | OUT | DIG                                                      | LATA<5> data output; not affected by analog input.                                           |

| HLVDIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                           | 1               | IN  | TTL                                                      | PORTA<5> data input; disabled when analog input enabled.                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AN4                                                                                       | 1               | IN  | ANA                                                      | A/D input channel 4. Default configuration on POR.                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HLVDIN                                                                                    | 1               | IN  | ANA                                                      | High/Low-Voltage Detect external trip point input.                                           |

| OSC2/CLKO/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OSC2                                                                                      | х               | OUT | ANA                                                      | Main oscillator feedback output connection (all XT and HS modes).                            |

| RA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLKO                                                                                      | х               | OUT | DIG                                                      | System cycle clock output (Fosc/4); available in EC, ECPLL and INTCKO modes.                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RA6                                                                                       | 0               | OUT | DIG                                                      | LATA<6> data output. Available only in ECIO, ECPIO and INTIO modes; otherwise, reads as '0'. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                           | 1               | IN  | TTL                                                      | PORTA<6> data input. Available only in ECIO, ECPIO and INTIO modes; otherwise, reads as '0'. |

## TABLE 9-1: PORTA I/O SUMMARY

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

| TABLE 9-2: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTA |

|------------|--------------------------------------------|

|            |                                            |

| Name   | Bit 7 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|--------|-------|-----------------------|--------|--------|--------|--------|--------|--------|-----------------------------|

| PORTA  | _     | RA6 <sup>(1)</sup>    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | 51                          |

| LATA   | —     | LATA6 <sup>(1)</sup>  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | 51                          |

| TRISA  | —     | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 51                          |

| ADCON1 | _     | _                     | VCFG1  | VCFG0  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 50                          |

| UCON   | _     | PPBRST                | SE0    | PKTDIS | USBEN  | RESUME | SUSPND | _      | 52                          |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA6 and its associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

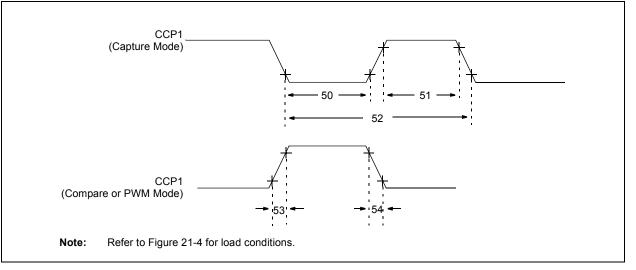

## 13.0 CAPTURE/COMPARE/PWM (CCP) MODULE

PIC18F2450/4450 devices have one CCP (Capture/ Compare/PWM) module. The module contains a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register.

#### REGISTER 13-1: CCP1CON: CAPTURE/COMPARE/PWM CONTROL REGISTER

| U-0   | U-0         | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------------|-------|-------|--------|--------|--------|--------|

| —     | — DC1B1 DC1 |       | DC1B0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

| bit 7 |             |       |       |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-4 | DC1B1:DC1B0: PWM Duty Cycle for CCP Module bits                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

|         | Capture mode:                                                                                                                     |

|         | Unused.                                                                                                                           |

|         | Compare mode:                                                                                                                     |

|         | Unused.                                                                                                                           |

|         | PWM mode:                                                                                                                         |

|         | These bits are the two LSbs (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR1L. |

| bit 3-0 | CCP1M3:CCP1M0: CCP Module Mode Select bits                                                                                        |

|         | 0000 = Capture/Compare/PWM disabled (resets CCP module)                                                                           |

|         | 0001 = Reserved                                                                                                                   |

|         | 0010 = Compare mode: toggle output on match (CCP1IF bit is set)                                                                   |

|         | 0011 = Reserved                                                                                                                   |

|         | 0100 = Capture mode: every falling edge                                                                                           |

|         | 0101 = Capture mode: every rising edge                                                                                            |

|         | 0110 = Capture mode: every 4th rising edge                                                                                        |

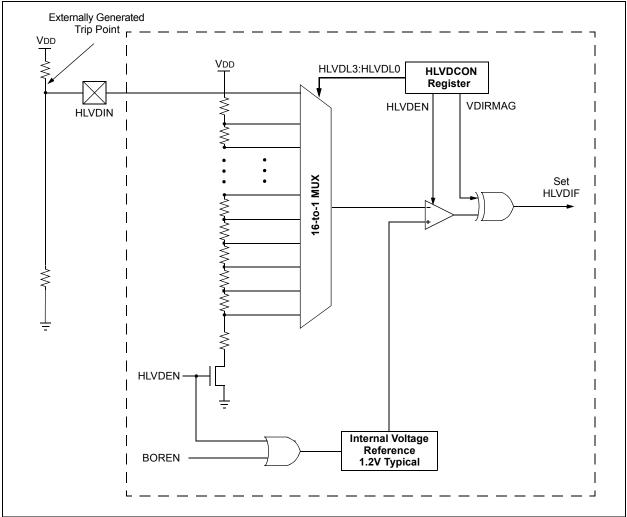

|         | 0111 = Capture mode: every 16th rising edge                                                                                       |