Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | UART/USART, USB                                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 23                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 10x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2450t-i-so |

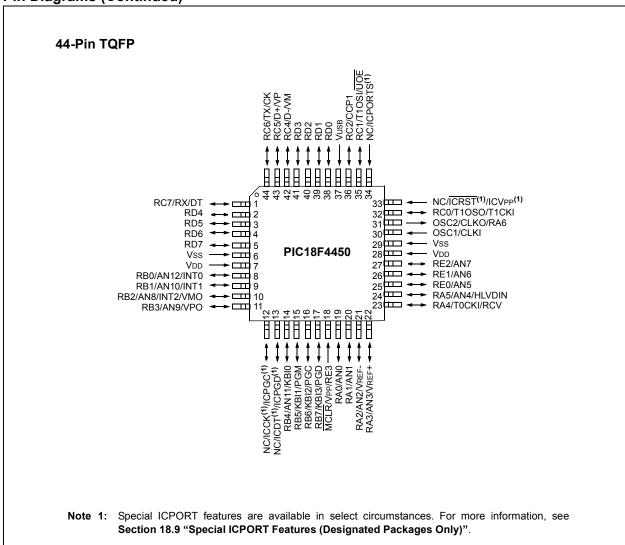

#### Pin Diagrams (Continued)

TABLE 2-3: OSCILLATOR CONFIGURATION OPTIONS FOR USB OPERATION (CONTINUED)

| Input Oscillator<br>Frequency |          |                      | MCU Clock Division (CPUDIV1:CPUDIV0) | Microcontroller<br>Clock Frequency |

|-------------------------------|----------|----------------------|--------------------------------------|------------------------------------|

|                               |          |                      | None (00)                            | 12 MHz                             |

|                               |          | HS, EC, ECIO         | ÷2 (01)                              | 6 MHz                              |

|                               |          | ПЗ, EG, EGIO         | ÷3 (10)                              | 4 MHz                              |

| 12 MHz                        | .2 (010) |                      | ÷4 (11)                              | 3 MHz                              |

| 12 IVITZ                      | ÷3 (010) |                      | ÷2 (00)                              | 48 MHz                             |

|                               |          | HSPLL, ECPLL, ECPIO  | ÷3 (01)                              | 32 MHz                             |

|                               |          | HOPEL, ECPLE, ECPIO  | ÷4 (10)                              | 24 MHz                             |

|                               |          |                      | ÷6 (11)                              | 16 MHz                             |

|                               |          |                      | None (00)                            | 8 MHz                              |

|                               |          | HS, EC, ECIO         | ÷2 (01)                              | 4 MHz                              |

|                               | 2 (0.01) |                      | ÷3 (10)                              | 2.67 MHz                           |

| 8 MHz                         |          |                      | ÷4 (11)                              | 2 MHz                              |

| O IVITZ                       | ÷2 (001) |                      | ÷2 (00)                              | 48 MHz                             |

|                               |          | HSPLL, ECPLL, ECPIO  | ÷3 (01)                              | 32 MHz                             |

|                               |          |                      | ÷4 (10)                              | 24 MHz                             |

|                               |          |                      | ÷6 (11)                              | 16 MHz                             |

|                               |          |                      | None (00)                            | 4 MHz                              |

|                               |          | XT, HS, EC, ECIO     | ÷2 (01)                              | 2 MHz                              |

|                               |          | AI, HO, EU, EUIU     | ÷3 (10)                              | 1.33 MHz                           |

| 4 MHz                         | .1 (000) |                      | ÷4 (11)                              | 1 MHz                              |

| 4 IVI□Z                       | ÷1 (000) |                      | ÷2 (00)                              | 48 MHz                             |

|                               |          | HSPLL, ECPLL, XTPLL, | ÷3 (01)                              | 32 MHz                             |

|                               |          | ECPIO                | ÷4 (10)                              | 24 MHz                             |

|                               |          |                      | ÷6 (11)                              | 16 MHz                             |

Legend: All clock frequencies, except 24 MHz, are exclusively associated with full-speed USB operation (USB clock of 48 MHz).

Bold is used to highlight clock selections that are compatible with low-speed USB operation (system clock of 24 MHz, USB clock of 6 MHz).

Note 1: Only valid when the USBDIV Configuration bit is cleared.

### 2.5 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. Unless the USB module is enabled, the OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features regardless of the power-managed mode (see Section 18.2 "Watchdog Timer (WDT)", Section 18.3 "Two-Speed Start-up" and Section 18.4 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up).

Regardless of the Run or Idle mode selected, the USB clock source will continue to operate. If the device is operating from a crystal or resonator-based oscillator, that oscillator will continue to clock the USB module. The core and all other modules will switch to the new clock source.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Sleep mode should never be invoked while the USB module is operating and connected. The only exception is when the device has been issued a "Suspend" command over the USB. Once the module has suspended operation and shifted to a low-power state, the microcontroller may be safely put into Sleep mode.

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 21.2 "DC Characteristics: Power-Down and Supply Current".

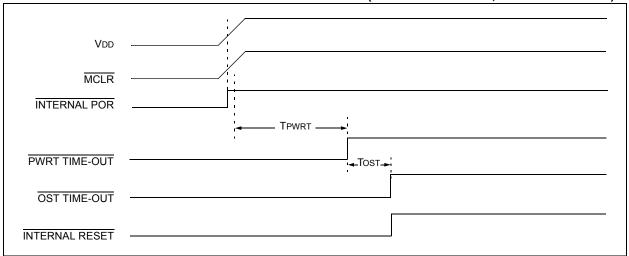

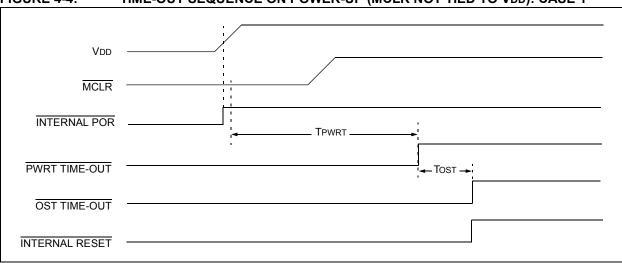

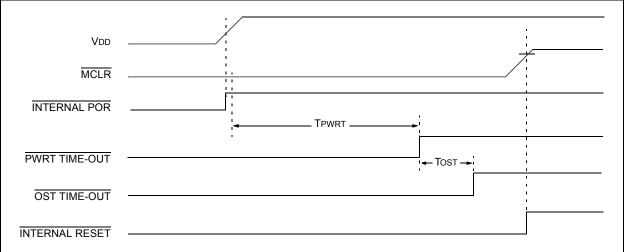

#### 2.6 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 21-10). It is enabled by clearing (=  $^\circ$ ) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval, TCSD (parameter 38, Table 21-10), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC or internal oscillator modes are used as the primary clock source.

TABLE 2-4: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |  |  |  |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|--|--|--|

| INTCKO          | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |  |  |  |

| INTIO           | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |  |  |  |

| ECIO, ECPIO     | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |  |  |  |

| EC              | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |  |  |  |

| XT and HS       | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |  |  |  |

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

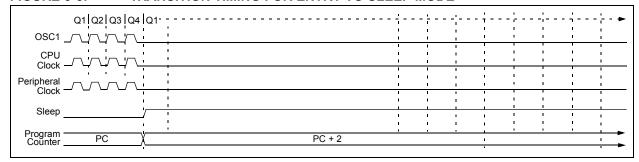

#### 3.3 Sleep Mode

The power-managed Sleep mode in the PIC18F2450/4450 devices is identical to the legacy Sleep mode offered in all other PIC microcontrollers. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 3-5). All clock source status bits are cleared.

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

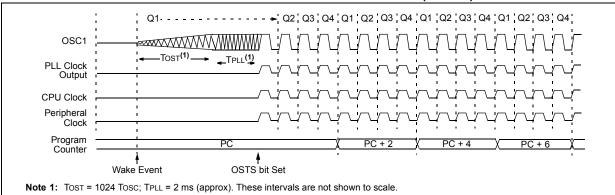

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS1:SCS0 bits becomes ready (see Figure 3-6), or it will be clocked from the internal oscillator if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 18.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

#### 3.4 Idle Modes

The Idle modes allow the controller's CPU to be selectively shut down while the peripherals continue to operate. Selecting a particular Idle mode allows users to further manage power consumption.

If the IDLEN bit is set to '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. The clock source status bits are not affected. Setting IDLEN and executing a SLEEP instruction provides a quick method of switching from a given Run mode to its corresponding Idle mode.

If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run.

Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset. When a wake event occurs, CPU execution is delayed by an interval of TcsD (parameter 38, Table 21-10) while it becomes ready to execute code. When the CPU begins executing code, it resumes with the same clock source for the current Idle mode. For example, when waking from RC\_IDLE mode, the internal oscillator will clock the CPU and peripherals (in other words, RC\_RUN mode). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or Sleep mode, a WDT time-out will result in a WDT wake-up to the Run mode currently specified by the SCS1:SCS0 bits.

FIGURE 3-5: TRANSITION TIMING FOR ENTRY TO SLEEP MODE

FIGURE 3-6: TRANSITION TIMING FOR WAKE FROM SLEEP (HSPLL)

FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

FIGURE 4-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

FIGURE 4-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Applicable Devices |      | pplicable Devices Power-on Reset,<br>Brown-out Reset |           | Wake-up via WDT<br>or Interrupt |  |

|----------|--------------------|------|------------------------------------------------------|-----------|---------------------------------|--|

| UEP9     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP8     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP7     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP6     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP5     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP4     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP3     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP2     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP1     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UEP0     | 2450               | 4450 | 0 0000                                               | 0 0000    | u uuuu                          |  |

| UCFG     | 2450               | 4450 | 00-0 0000                                            | 00-0 0000 | uu-u uuuu                       |  |

| UADDR    | 2450               | 4450 | -000 0000                                            | -000 0000 | -uuu uuuu                       |  |

| UCON     | 2450               | 4450 | -0x0 000-                                            | -0x0 000- | -uuu uuu-                       |  |

| USTAT    | 2450               | 4450 | -xxx xxx-                                            | -xxx xxx- | -uuu uuu-                       |  |

| UEIE     | 2450               | 4450 | 00 0000                                              | 00 0000   | uu uuuu                         |  |

| UEIR     | 2450               | 4450 | 00 0000                                              | 00 0000   | uu uuuu                         |  |

| UIE      | 2450 4450          |      | -000 0000                                            | -000 0000 | -uuu uuuu                       |  |

| UIR      | 2450               | 4450 | -000 0000                                            | -000 0000 | -uuu uuuu                       |  |

| UFRMH    | 2450               | 4450 | XXX                                                  | xxx       | uuu                             |  |

| UFRML    | 2450               | 4450 | XXXX XXXX                                            | xxxx xxxx | uuuu uuuu                       |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- **Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **4:** See Table 4-3 for Reset value for specific condition.

- **5:** PORTA<6>, LATA<6> and TRISA<6> are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

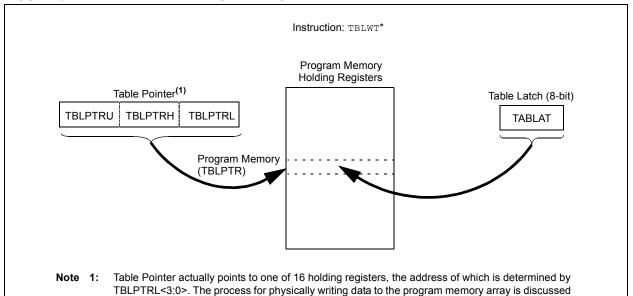

#### FIGURE 6-2: TABLE WRITE OPERATION

in Section 6.5 "Writing to Flash Program Memory".

#### 6.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. These include the:

- EECON1 register

- · EECON2 register

- TABLAT register

- · TBLPTR registers

#### 6.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 6-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The CFGS control bit determines if the access will be to the Configuration/Calibration registers or to program memory.

The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WREN bit is set and cleared when the internal programming timer expires and the write operation is complete.

**Note:** During normal operation, the WRERR is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset or a write operation was attempted improperly.

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software; it is cleared in hardware at the completion of the write operation.

TABLE 9-5: PORTC I/O SUMMARY

| Pin        | Function | TRIS<br>Setting | I/O | I/O Type | Description                                                                                                             |  |  |  |

|------------|----------|-----------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RC0/T1OSO/ | RC0      | 0               | OUT | DIG      | LATC<0> data output.                                                                                                    |  |  |  |

| T1CKI      |          | 1               | IN  | ST       | PORTC<0> data input.                                                                                                    |  |  |  |

|            | T10S0    | х               | OUT | ANA      | Timer1 oscillator output; enabled when Timer1 oscillator enabled. Disables digital I/O.                                 |  |  |  |

|            | T1CKI    | 1               | IN  | ST       | Timer1 counter input.                                                                                                   |  |  |  |

| RC1/T1OSI/ | RC1      | 0               | OUT | DIG      | LATC<1> data output.                                                                                                    |  |  |  |

| UOE        |          | 1               | IN  | ST       | PORTC<1> data input.                                                                                                    |  |  |  |

|            | T10SI    | Х               | IN  | ANA      | Timer1 oscillator input; enabled when Timer1 oscillator enabled. Disables digital I/O.                                  |  |  |  |

|            | UOE      | 0               | OUT | DIG      | External USB transceiver OE output.                                                                                     |  |  |  |

| RC2/CCP1   | RC2      | 0               | OUT | DIG      | LATC<2> data output.                                                                                                    |  |  |  |

|            |          | 1               | IN  | ST       | PORTC<2> data input.                                                                                                    |  |  |  |

|            | CCP1     | 0               | OUT | DIG      | CCP1 Compare and PWM output; takes priority over port data.                                                             |  |  |  |

|            |          | 1               | IN  | ST       | CCP1 Capture input.                                                                                                     |  |  |  |

| RC4/D-/VM  | RC4      | (1)             | IN  | TTL      | PORTC<4> data input; disabled when USB module or on-chip transceiver is enabled.                                        |  |  |  |

|            | D-       | (1)             | OUT | XCVR     | USB bus differential minus line output (internal transceiver).                                                          |  |  |  |

|            |          | (1)             | IN  | XCVR     | USB bus differential minus line input (internal transceiver).                                                           |  |  |  |

|            | VM       | (1)             | IN  | TTL      | External USB transceiver VM input.                                                                                      |  |  |  |

| RC5/D+/VP  | RC5      | (1)             | IN  | TTL      | PORTC<5> data input; disabled when USB module or on-chip transceiver is enabled.                                        |  |  |  |

|            | D+       | (1)             | OUT | XCVR     | USB bus differential plus line output (internal transceiver).                                                           |  |  |  |

|            |          | (1)             | IN  | XCVR     | USB bus differential plus line input (internal transceiver).                                                            |  |  |  |

|            | VP       | (1)             | IN  | TTL      | External USB transceiver VP input.                                                                                      |  |  |  |

| RC6/TX/CK  | RC6      | 0               | OUT | DIG      | LATC<6> data output.                                                                                                    |  |  |  |

|            |          | 1               | IN  | ST       | PORTC<6> data input.                                                                                                    |  |  |  |

|            | TX       | 0               | OUT | DIG      | Asynchronous serial transmit data output (EUSART module); takes priority over port data. User must configure as output. |  |  |  |

|            | CK       | 0               | OUT | DIG      | Synchronous serial clock output (EUSART module); takes priority over port data.                                         |  |  |  |

|            |          | 1               | IN  | ST       | Synchronous serial clock input (EUSART module).                                                                         |  |  |  |

| RC7/RX/DT  | RC7      | 0               | OUT | DIG      | LATC<7> data output.                                                                                                    |  |  |  |

|            |          | 1               | IN  | ST       | PORTC<7> data input.                                                                                                    |  |  |  |

|            | RX       | 1               | IN  | ST       | Asynchronous serial receive data input (EUSART module).                                                                 |  |  |  |

|            | DT       | 1               | OUT | DIG      | Synchronous serial data output (EUSART module).                                                                         |  |  |  |

|            |          | 1               | IN  | ST       | Synchronous serial data input (EUSART module). User must configure as an input.                                         |  |  |  |

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, XCVR = USB Transceiver, x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

Note 1: RC4 and RC5 do not have corresponding TRISC bits. In Port mode, these pins are input only. USB data direction is determined by the USB configuration.

TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name  | Bit 7  | Bit 6  | Bit 5              | Bit 4              | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|-------|--------|--------|--------------------|--------------------|-------|--------|--------|--------|-----------------------------|

| PORTC | RC7    | RC6    | RC5 <sup>(1)</sup> | RC4 <sup>(1)</sup> | _     | RC2    | RC1    | RC0    | 51                          |

| LATC  | LATC7  | LATC6  | _                  | _                  | _     | LATC2  | LATC1  | LATC0  | 51                          |

| TRISC | TRISC7 | TRISC6 | _                  | _                  | _     | TRISC2 | TRISC1 | TRISC0 | 51                          |

| UCON  | _      | PPBRST | SE0                | PKTDIS             | USBEN | RESUME | SUSPND | _      | 52                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTC.

**Note 1:** RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

TABLE 9-9: PORTE I/O SUMMARY

| Pin              | Function | TRIS<br>Setting | I/O | I/O Type | Description                                                                                           |

|------------------|----------|-----------------|-----|----------|-------------------------------------------------------------------------------------------------------|

| RE0/AN5          | RE0      | 0               | OUT | DIG      | LATE<0> data output; not affected by analog input.                                                    |

|                  |          | 1               | IN  | ST       | PORTE<0> data input; disabled when analog input enabled.                                              |

|                  | AN5      | 1               | IN  | ANA      | A/D input channel 5; default configuration on POR.                                                    |

| RE1/AN6          | RE1      | 0               | OUT | DIG      | LATE<1> data output; not affected by analog input.                                                    |

|                  |          | 1               | IN  | ST       | PORTE<1> data input; disabled when analog input enabled.                                              |

|                  | AN6      | 1               | IN  | ANA      | A/D input channel 6; default configuration on POR.                                                    |

| RE2/AN7          | RE2      | 0               | OUT | DIG      | LATE<2> data output; not affected by analog input.                                                    |

|                  |          | 1               | IN  | ST       | PORTE<2> data input; disabled when analog input enabled.                                              |

|                  | AN7      | 1               | IN  | ANA      | A/D input channel 7; default configuration on POR.                                                    |

| MCLR/VPP/<br>RE3 | MCLR     | (1)             | IN  | ST       | External Master Clear input; enabled when MCLRE Configuration bit is set.                             |

|                  | VPP      | (1)             | IN  | ANA      | High-voltage detection, used for ICSP™ mode entry detection. Always available regardless of pin mode. |

|                  | RE3      | (1)             | IN  | ST       | PORTE<3> data input; enabled when MCLRE Configuration bit is clear.                                   |

Legend: OUT = Output, IN = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input.

Note 1: RE3 does not have a corresponding TRISE<3> bit. This pin is always an input regardless of mode.

TABLE 9-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                | Bit 2              | Bit 1              | Bit 0              | Reset<br>Values<br>on Page: |

|----------------------|-------|-------|-------|-------|----------------------|--------------------|--------------------|--------------------|-----------------------------|

| PORTE                | _     | _     | _     | _     | RE3 <sup>(1,2)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | 51                          |

| LATE <sup>(3)</sup>  | _     | _     | _     | _     | _                    | LATE2              | LATE1              | LATE0              | 51                          |

| TRISE <sup>(3)</sup> | _     | _     | _     | _     | _                    | TRISE2             | TRISE1             | TRISE0             | 51                          |

| ADCON1               | _     | _     | VCFG1 | VCFG0 | PCFG3                | PCFG2              | PCFG1              | PCFG0              | 50                          |

**Legend:** — = unimplemented, read as '0'

**Note 1:** Implemented only when Master Clear functionality is disabled (MCLRE Configuration bit = 0); otherwise, read as '0'.

- **2:** RE3 is the only PORTE bit implemented on both 28-pin and 40/44-pin devices. All other bits are implemented only when PORTE is implemented (i.e., 40/44-pin devices).

- 3: These registers and/or bits are unimplemented on 28-pin devices.

NOTES:

#### 14.2.4 **USB ENDPOINT CONTROL**

Each of the 16 possible bidirectional endpoints has its own independent control register, UEPn (where 'n' represents the endpoint number). Each register has an identical complement of control bits. The prototype is shown in Register 14-4.

The EPHSHK bit (UEPn<4>) controls handshaking for the endpoint; setting this bit enables USB handshaking. Typically, this bit is always set except when using isochronous endpoints.

The EPCONDIS bit (UEPn<3>) is used to enable or disable USB control operations (SETUP) through the endpoint. Clearing this bit enables SETUP transactions. Note that the corresponding EPINEN and EPOUTEN bits must be set to enable IN and OUT

transactions. For Endpoint 0, this bit should always be cleared since the USB specifications identify Endpoint 0 as the default control endpoint.

The EPOUTEN bit (UEPn<2>) is used to enable or disable USB OUT transactions from the host. Setting this bit enables OUT transactions. Similarly, the EPINEN bit (UEPn<1>) enables or disables USB IN transactions from the host.

The EPSTALL bit (UEPn<0>) is used to indicate a STALL condition for the endpoint. If a STALL is issued on a particular endpoint, the EPSTALL bit for that endpoint pair will be set by the SIE. This bit remains set until it is cleared through firmware, or until the SIE is reset.

#### REGISTER 14-4: UEPn: USB ENDPOINT n CONTROL REGISTER (UEP0 THROUGH UEP15)

| U-0   | U-0 U-0 |  | -0 U-0 U-0 R/W-0 R/W-0 |          |         |        | R/W-0                  | R/W-0 | R/W-0 |

|-------|---------|--|------------------------|----------|---------|--------|------------------------|-------|-------|

| _     |         |  | EPHSHK                 | EPCONDIS | EPOUTEN | EPINEN | EPSTALL <sup>(1)</sup> |       |       |

| bit 7 |         |  |                        |          |         |        | bit 0                  |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | I as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                                       |

|---------|----------------------------------------------------------------------------------|

| bit 4   | EPHSHK: Endpoint Handshake Enable bit                                            |

|         | 1 = Endpoint handshake enabled                                                   |

|         | 0 = Endpoint handshake disabled (typically used for isochronous endpoints)       |

| bit 3   | EPCONDIS: Bidirectional Endpoint Control bit                                     |

|         | If EPOUTEN = 1 and EPINEN = 1:                                                   |

|         | 1 = Disable Endpoint n from control transfers; only IN and OUT transfers allowed |

|         | 0 = Enable Endpoint n for control (SETUP) transfers; IN and OUT transfers also a |

s also allowed **EPOUTEN:** Endpoint Output Enable bit

bit 2 1 = Endpoint n output enabled

0 = Endpoint n output disabled

bit 1 **EPINEN:** Endpoint Input Enable bit

> 1 = Endpoint n input enabled 0 = Endpoint n input disabled

bit 0 **EPSTALL:** Endpoint Stall Indicator bit

1 = Endpoint n has issued one or more STALL packets

0 = Endpoint n has not issued any STALL packets

| BTFS    | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit Test File, Skip if Clear                          |                                    | BTF       | ss    | Bit Test File, Skip if Set                  |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------|-----------|-------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Synta   | x:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BTFSC f, b                                            | {,a}                               |           | Synta | ax:                                         | BTFSS f, b                                                                                                                                                                                                                      | {,a}                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |  |  |

| Opera   | ands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$ |                                    |           | ≤ 7   |                                             | $0 \le f \le 255$<br>$0 \le b < 7$<br>$a \in [0,1]$                                                                                                                                                                             |                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |  |  |

| Opera   | ation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | skip if (f <b>) = 0</b>                               |                                    |           | Oper  | ation:                                      | skip if (f <b>) = 1</b>                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |  |  |

| Status  | Affected:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | None                                                  |                                    |           | Statu | s Affected:                                 | None                                                                                                                                                                                                                            | ,                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |  |  |

| Encod   | ding:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1011                                                  | bbba ff                            | ff ffff   | Enco  | ding:                                       | 1010                                                                                                                                                                                                                            | bbba ff:                                                                                                                                                                                                                                                                                    | ff ffff                                                                                                                                         |  |  |

| Descr   | scription:  If bit 'b' in register 'f' is '0', then the next instruction is skipped. If bit 'b' is '0', then the next instruction fetched during the current instruction execution is discarded and a NOP is executed instead, making this a two-cycle instruction.  If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the GPR bank (default).  If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh).  See Section 19.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                                                       |                                    |           | Desc  | ription:                                    | instruction is<br>the next instruction and a NOP is<br>this a two-cy<br>If 'a' is '0', the<br>'a' is '1', the<br>GPR bank (of<br>If 'a' is '0' an<br>set is enable<br>in Indexed L<br>mode where<br>See Section<br>Bit-Oriented | gister 'f' is '1', t<br>skipped. If bit<br>ruction fetched<br>uction executio<br>executed instruction.<br>e Access Bank<br>BSR is used to<br>default).<br>d the extended<br>d, this instructi<br>iteral Offset Ad<br>ever f ≤ 95 (5Fh<br>19.2.3 "Byte-<br>d Instructions<br>et Mode" for de | 'b' is '1', then during the n is discarded ead, making is selected. If select the distriction on operates dressing n).  Oriented and in Indexed |  |  |

| Words   | s:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                     |                                    |           | Word  | ls:                                         | 1                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |  |  |

| Cycles  | s:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       | cles if skip and<br>2-word instruc |           | Cycle | es:                                         |                                                                                                                                                                                                                                 | cles if skip and                                                                                                                                                                                                                                                                            |                                                                                                                                                 |  |  |

| Q Cy    | cle Activity:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •                                                     |                                    |           | QC    | ycle Activity:                              | ·                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |  |  |

|         | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q2                                                    | Q3                                 | Q4        |       | Q1                                          | Q2                                                                                                                                                                                                                              | Q3                                                                                                                                                                                                                                                                                          | Q4                                                                                                                                              |  |  |

|         | Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read                                                  | Process                            | No        |       | Decode                                      | Read                                                                                                                                                                                                                            | Process                                                                                                                                                                                                                                                                                     | No                                                                                                                                              |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | register 'f'                                          | Data                               | operation |       |                                             | register 'f'                                                                                                                                                                                                                    | Data                                                                                                                                                                                                                                                                                        | operation                                                                                                                                       |  |  |

| lf skip |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00                                                    | 00                                 | 04        | lf sk | •                                           | 00                                                                                                                                                                                                                              | 00                                                                                                                                                                                                                                                                                          | 0.4                                                                                                                                             |  |  |

| Г       | Q1<br>No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q2<br>No                                              | Q3<br>No                           | Q4<br>No  |       | Q1<br>No                                    | Q2<br>No                                                                                                                                                                                                                        | Q3<br>No                                                                                                                                                                                                                                                                                    | Q4<br>No                                                                                                                                        |  |  |

|         | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | operation                                             | operation                          | operation |       | operation                                   | operation                                                                                                                                                                                                                       | operation                                                                                                                                                                                                                                                                                   | operation                                                                                                                                       |  |  |

| If skip | p and followed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | by 2-word ins                                         |                                    |           | lf sk | ip and followed                             |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |  |  |

|         | Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q2                                                    | Q3                                 | Q4        |       | Q1                                          | Q2                                                                                                                                                                                                                              | Q3                                                                                                                                                                                                                                                                                          | Q4                                                                                                                                              |  |  |

|         | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | No                                                    | No                                 | No        |       | No                                          | No                                                                                                                                                                                                                              | No                                                                                                                                                                                                                                                                                          | No                                                                                                                                              |  |  |

| _       | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | operation                                             | operation                          | operation |       | operation                                   | operation                                                                                                                                                                                                                       | operation                                                                                                                                                                                                                                                                                   | operation                                                                                                                                       |  |  |

|         | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | No                                                    | No                                 | No        |       | No                                          | No                                                                                                                                                                                                                              | No                                                                                                                                                                                                                                                                                          | No                                                                                                                                              |  |  |

| L       | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | operation                                             | operation                          | operation |       | operation                                   | operation                                                                                                                                                                                                                       | operation                                                                                                                                                                                                                                                                                   | operation                                                                                                                                       |  |  |

|         | <u>ple:</u><br>Before Instruct<br>PC<br>After Instructio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FALSE : TRUE : ion = add                              | ress (HERE)                        | , 1, 0    |       | nple:  Before Instruct PC  After Instructio | FALSE : TRUE : tion = add                                                                                                                                                                                                       | ress (HERE)                                                                                                                                                                                                                                                                                 | , 1, 0                                                                                                                                          |  |  |

|         | If FLAG<<br>PC<br>If FLAG<<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1> = 0;<br>= add<br>1> = 1;                           | ress (FALSE)                       |           |       | If FLAG<<br>PC<br>If FLAG<<br>PC            | 1> = 0;<br>= add<br>1> = 1;                                                                                                                                                                                                     | ress (FALSE)                                                                                                                                                                                                                                                                                |                                                                                                                                                 |  |  |

21.2 DC Characteristics: Power-Down and Supply Current

PIC18F2450/4450 (Industrial)

PIC18LF2450/4450 (Industrial) (Continued)

| PIC18LF2450/4450<br>(Industrial)<br>PIC18F2450/4450<br>(Industrial) |                                     | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial |     |       |            |            |                                     |

|---------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|------------|-------------------------------------|

|                                                                     |                                     | Standard Operating Conditions (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for industrial                                         |     |       |            |            |                                     |

| Param<br>No.                                                        | Device                              | Тур                                                                                                                                                      | Max | Units | Conditions |            |                                     |

|                                                                     | Supply Current (IDD) <sup>(2)</sup> |                                                                                                                                                          |     |       |            |            |                                     |

|                                                                     | PIC18LF2450/4450                    | 200                                                                                                                                                      | 500 | μΑ    | -40°C      |            |                                     |

|                                                                     |                                     | 200                                                                                                                                                      | 500 | μΑ    | +25°C      | VDD = 2.0V |                                     |

|                                                                     |                                     | 200                                                                                                                                                      | 500 | μΑ    | +85°C      |            |                                     |

|                                                                     | PIC18LF2450/4450                    | 500                                                                                                                                                      | 650 | μΑ    | -40°C      |            | Fosc = 1 MHz                        |

|                                                                     |                                     | 400                                                                                                                                                      | 650 | μΑ    | +25°C      | VDD = 3.0V | (PRI_RUN,                           |

|                                                                     |                                     | 360                                                                                                                                                      | 650 | μА    | +85°C      |            | EC oscillator)                      |

|                                                                     | All devices                         | 1.0                                                                                                                                                      | 1.6 | mA    | -40°C      |            |                                     |

|                                                                     |                                     | 0.9                                                                                                                                                      | 1.5 | mA    | +25°C      | VDD = 5.0V |                                     |

|                                                                     |                                     | 8.0                                                                                                                                                      | 1.4 | mA    | +85°C      |            |                                     |

|                                                                     | PIC18LF2450/4450                    | 0.53                                                                                                                                                     | 2.0 | mA    | -40°C      |            |                                     |

|                                                                     |                                     | 0.53                                                                                                                                                     | 2.0 | mA    | +25°C      | VDD = 2.0V |                                     |

|                                                                     |                                     | 0.55                                                                                                                                                     | 2.0 | mA    | +85°C      |            |                                     |