Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | UART/USART, USB                                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4450-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

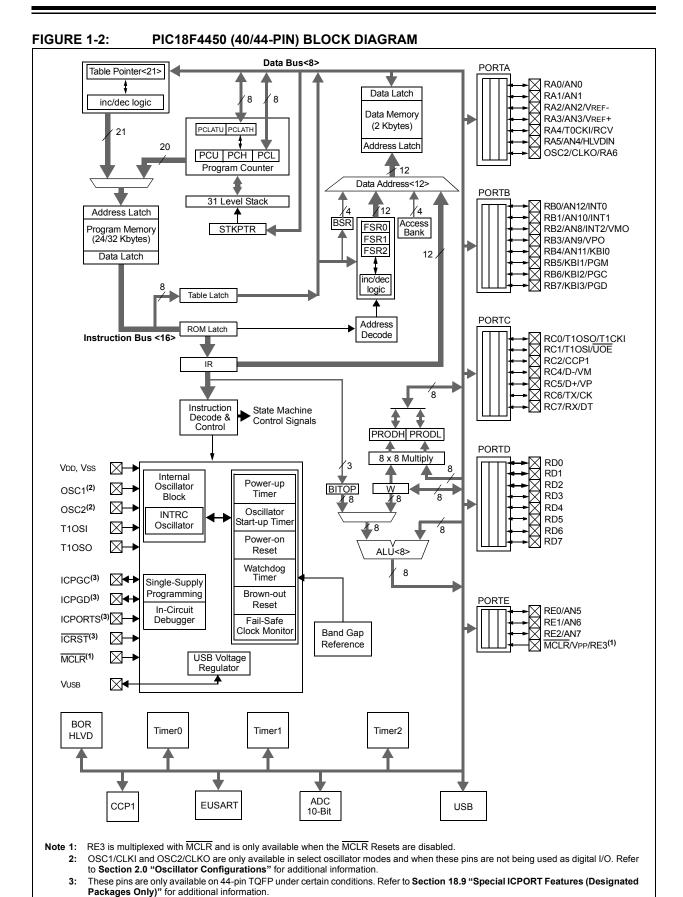

PIC18F2450 (28-PIN) BLOCK DIAGRAM FIGURE 1-1: Data Bus<8> Table Pointer<21> RA0/AN0 Data Latch inc/dec logic 8 8 RA1/AN1 RA2/AN2/VREF-Data Memory RA3/AN3/VREF+ (2 Kbytes) PCLATU PCLATH 21 RA4/T0CKI/RCV 20 Address Latch RA5/AN4/HLVDIN PCU PCH PCL OSC2/CLKO/RA6 Program Counter Data Address<12> 31 Level Stack /12 Address Latch BSR Access FSR0 Program Memory (24/32 Kbytes) STKPTR Bank FSR1 FSR2 Data Latch 12 PORTB RB0/AN12/INT0 inc/dec RB1/AN10/INT1 logic RB2/AN8/INT2/VMO Table Latch RB3/AN9/VPO RB4/AN11/KBI0 Address RB5/KBI1/PGM ROM Latch Instruction Bus <16> Decode RB6/KBI2/PGC RB7/KBI3/PGD IR 8 Instruction State Machine Decode & Control Signals PRODH PRODL PORTC 8 x 8 Multiply RC0/T1OSO/T1CKI RC1/T10SI/UOE OSC1<sup>(2)</sup> Internal RC2/CCP1 Power-up BITOP W Oscillator Timer RC4/D-/VM Block RC5/D+/VP OSC2<sup>(2)</sup> Oscillator RC6/TX/CK INTRC Start-up Time RC7/RX/DT Oscillator T10SI  $\boxtimes$ Power-on Reset ALÚ<8> Watchdog T10SO Timer 8 Brown-out Single-Supply MCLR(1) Reset Programming Fail-Safe In-Circuit VDD, VSS Clock Monitor Debugger Band Gap USB Voltage **VUSB**  $\boxtimes \blacktriangleleft$ Regulator Reference MCLR/VPP/RE3<sup>(1)</sup> **BOR** ADC Timer0 Timer2 HLVD Timer1 10-Bit **EUSART** CCP1 **USB Note 1:** RE3 is multiplexed with  $\overline{MCLR}$  and is only available when the  $\overline{MCLR}$  Resets are disabled. 2: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. Refer to Section 2.0 "Oscillator Configurations" for additional information.

DS39760D-page 10

TABLE 1-2: PIC18F2450 PINOUT I/O DESCRIPTIONS (CONTINUED)

|                | Pin Nu         | mber | Pin Buffei |        |                                     |

|----------------|----------------|------|------------|--------|-------------------------------------|

| Pin Name       | SPDIP,<br>SOIC | QFN  | Type       | Туре   | Description                         |

|                |                |      |            |        | PORTA is a bidirectional I/O port.  |

| RA0/AN0        | 2              | 27   |            |        |                                     |

| RA0            |                |      | I/O        | TTL    | Digital I/O.                        |

| AN0            |                |      | I          | Analog | Analog input 0.                     |

| RA1/AN1        | 3              | 28   |            |        |                                     |

| RA1            |                |      | I/O        | TTL    | Digital I/O.                        |

| AN1            |                |      | I          | Analog | Analog input 1.                     |

| RA2/AN2/VREF-  | 4              | 1    |            |        |                                     |

| RA2            |                |      | I/O        | TTL    | Digital I/O.                        |

| AN2            |                |      | I          | Analog | Analog input 2.                     |

| VREF-          |                |      | I          | Analog | A/D reference voltage (low) input.  |

| RA3/AN3/VREF+  | 5              | 2    |            |        |                                     |

| RA3            |                |      | I/O        | TTL    | Digital I/O.                        |

| AN3            |                |      | I          | Analog | Analog input 3.                     |

| VREF+          |                |      | I          | Analog | A/D reference voltage (high) input. |

| RA4/T0CKI/RCV  | 6              | 3    |            |        |                                     |

| RA4            |                |      | I/O        | ST     | Digital I/O.                        |

| T0CKI          |                |      | I          | ST     | Timer0 external clock input.        |

| RCV            |                |      | I          | TTL    | External USB transceiver RCV input. |

| RA5/AN4/HLVDIN | 7              | 4    |            |        |                                     |

| RA5            |                |      | I/O        | TTL    | Digital I/O.                        |

| AN4            |                |      | I          | Analog | Analog input 4.                     |

| HLVDIN         |                |      | l          | Analog | High/Low-Voltage Detect input.      |

| RA6            |                | _    | _          |        | See the OSC2/CLKO/RA6 pin.          |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

CMOS = CMOS compatible input or output

P = Power

TABLE 1-3: PIC18F4450 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                                      | Pi   | n Num | ber  | Pin                | Buffer                   | Description                                                                                                   |

|-----------------------------------------------|------|-------|------|--------------------|--------------------------|---------------------------------------------------------------------------------------------------------------|

| Pin Name                                      | PDIP | QFN   | TQFP | Туре               | Type                     | Description                                                                                                   |

|                                               |      |       |      |                    |                          | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/AN12/INT0<br>RB0<br>AN12<br>INT0          | 33   | 9     | 8    | I/O<br>I<br>I      | TTL<br>Analog<br>ST      | Digital I/O.<br>Analog input 12.<br>External interrupt 0.                                                     |

| RB1/AN10/INT1<br>RB1<br>AN10<br>INT1          | 34   | 10    | 9    | I/O<br>I<br>I      | TTL<br>Analog<br>ST      | Digital I/O.<br>Analog input 10.<br>External interrupt 1.                                                     |

| RB2/AN8/INT2/VMO<br>RB2<br>AN8<br>INT2<br>VMO | 35   | 11    | 10   | I/O<br>I<br>I<br>O | TTL<br>Analog<br>ST<br>— | Digital I/O. Analog input 8. External interrupt 2. External USB transceiver VMO output.                       |

| RB3/AN9/VPO<br>RB3<br>AN9<br>VPO              | 36   | 12    | 11   | I/O<br>I<br>O      | TTL<br>Analog<br>—       | Digital I/O.<br>Analog input 9.<br>External USB transceiver VPO output.                                       |

| RB4/AN11/KBI0<br>RB4<br>AN11<br>KBI0          | 37   | 14    | 14   | I/O<br>I<br>I      | TTL<br>Analog<br>TTL     | Digital I/O.<br>Analog input 11.<br>Interrupt-on-change pin.                                                  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM            | 38   | 15    | 15   | I/O<br>I<br>I/O    | TTL<br>TTL<br>ST         | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                         |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC            | 39   | 16    | 16   | I/O<br>I<br>I/O    | TTL<br>TTL<br>ST         | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming clock pin.               |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD            | 40   | 17    | 17   | I/O<br>I<br>I/O    | TTL<br>TTL<br>ST         | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

= Input

O = Output

P = Power

Note 1: These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

#### REGISTER 4-1: RCON: RESET CONTROL REGISTER

| R/W-0 | R/W-1 <sup>(1)</sup> | U-0  | R/W-1 | R-1 | R-1 | R/W-0 <sup>(2)</sup> | R/W-0 |

|-------|----------------------|------|-------|-----|-----|----------------------|-------|

| IPEN  | SBOREN               | — RI |       | TO  | PD  | POR                  | BOR   |

| bit 7 |                      |      |       |     |     |                      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 IPEN: Interrupt Priority Enable bit

1 = Enable priority levels on interrupts

0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode)

bit 6 SBOREN: BOR Software Enable bit (1)

If BOREN1:BOREN0 = 01:

1 = BOR is enabled

0 = BOR is disabled

If BOREN1:BOREN0 = 00, 10 or 11:

Bit is disabled and read as '0'.

bit 5 **Unimplemented:** Read as '0'

bit 4 RI: RESET Instruction Flag bit

1 = The RESET instruction was not executed (set by firmware only)

0 = The RESET instruction was executed causing a device Reset (must be set in software after a

Brown-out Reset occurs)

bit 3 **TO:** Watchdog Time-out Flag bit

1 = Set by power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time-out occurred

bit 2 PD: Power-Down Detection Flag bit

1 = Set by power-up or by the CLRWDT instruction

0 = Set by execution of the SLEEP instruction

bit 1 **POR:** Power-on Reset Status bit<sup>(2)</sup>

1 = A Power-on Reset has not occurred (set by firmware only)

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 **BOR**: Brown-out Reset Status bit

1 = A Brown-out Reset has not occurred (set by firmware only)

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

**Note 1:** If SBOREN is enabled, its Reset state is '1'; otherwise, it is '0'.

2: The actual Reset value of POR is determined by the type of device Reset. See the notes following this register and Section 4.6 "Reset State of Registers" for additional information.

**Note 1:** It is recommended that the POR bit be set after a Power-on Reset has been detected so that subsequent Power-on Resets may be detected.

**2:** Brown-out Reset is said to have occurred when  $\overline{\mathsf{BOR}}$  is '0' and  $\overline{\mathsf{POR}}$  is '1' (assuming that  $\overline{\mathsf{POR}}$  was set to '1' by software immediately after a Power-on Rest).

TABLE 5-2: REGISTER FILE SUMMARY (PIC18F2450/4450) (CONTINUED)

| File Name | Bit 7 | Bit 6              | Bit 5              | Bit 4              | Bit 3    | Bit 2   | Bit 1  | Bit 0   | Value on<br>POR, BOR | Details<br>on Page: |

|-----------|-------|--------------------|--------------------|--------------------|----------|---------|--------|---------|----------------------|---------------------|

| PORTC     | RC7   | RC6                | RC5 <sup>(6)</sup> | RC4 <sup>(6)</sup> | _        | RC2     | RC1    | RC0     | xxxx -xxx            | 51, 106             |

| PORTB     | RB7   | RB6                | RB5                | RB4                | RB3      | RB2     | RB1    | RB0     | xxxx xxxx            | 51, 100             |

| PORTA     | _     | RA6 <sup>(4)</sup> | RA5                | RA4                | RA3      | RA2     | RA1    | RA0     | -x0x 0000            | 51, 100             |

| UEP15     | _     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP14     | _     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP13     | _     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP12     | _     | _                  | ı                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP11     | _     | _                  | ı                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP10     | _     | _                  | ı                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP9      | _     | _                  | ı                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP8      | _     | _                  | ı                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP7      | _     | _                  | 1                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP6      | _     | _                  | 1                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP5      | _     | _                  | 1                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP4      | _     | _                  | 1                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP3      | _     | _                  | 1                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP2      | _     | _                  | 1                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP1      | _     | _                  | 1                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP0      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UCFG      | UTEYE | UOEMON             | 1                  | UPUEN              | UTRDIS   | FSEN    | PPB1   | PPB0    | 00-0 0000            | 52, 132             |

| UADDR     | _     | ADDR6              | ADDR5              | ADDR4              | ADDR3    | ADDR2   | ADDR1  | ADDR0   | -000 0000            | 52, 136             |

| UCON      | _     | PPBRST             | SE0                | PKTDIS             | USBEN    | RESUME  | SUSPND | _       | -0x0 000-            | 52, 130             |

| USTAT     | _     | ENDP3              | ENDP2              | ENDP1              | ENDP0    | DIR     | PPBI   | _       | -xxx xxx-            | 52, 134             |

| UEIE      | BTSEE | _                  | 1                  | BTOEE              | DFN8EE   | CRC16EE | CRC5EE | PIDEE   | 00 0000              | 52, 148             |

| UEIR      | BTSEF | _                  | _                  | BTOEF              | DFN8EF   | CRC16EF | CRC5EF | PIDEF   | 00 0000              | 52, 147             |

| UIE       | _     | SOFIE              | STALLIE            | IDLEIE             | TRNIE    | ACTVIE  | UERRIE | URSTIE  | -000 0000            | 52, 146             |

| UIR       |       | SOFIF              | STALLIF            | IDLEIF             | TRNIF    | ACTVIF  | UERRIF | URSTIF  | -000 0000            | 52, 144             |

| UFRMH     | _     | _                  | _                  | _                  | _        | FRM10   | FRM9   | FRM8    | xxx                  | 52, 136             |

| UFRML     | FRM7  | FRM6               | FRM5               | FRM4               | FRM3     | FRM2    | FRM1   | FRM0    | xxxx xxxx            | 52, 136             |

Note 1: Bit 21 of the TBLPTRU allows access to the device Configuration bits.

- 2: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

- 3: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

- 4: RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

- 5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

- **6:** RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3>=0).

#### **EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)**

| PROGRAM_MEMORY | Y      |                   |                               |

|----------------|--------|-------------------|-------------------------------|

|                | BCF    | EECON1, CFGS      | ; access Flash program memory |

|                | BSF    | EECON1, WREN      | ; enable write to memory      |

|                | BCF    | INTCON, GIE       | ; disable interrupts          |

|                | MOVLW  | 55h               |                               |

| Required       | MOVWF  | EECON2            | ; write 55h                   |

| Sequence       | MOVLW  | 0AAh              |                               |

|                | MOVWF  | EECON2            | ; write OAAh                  |

|                | BSF    | EECON1, WR        | ; start program (CPU stall)   |

|                | DECFSZ | COUNTER1          |                               |

|                | BRA    | WRITE_BUFFER_BACK |                               |

|                | BSF    | INTCON, GIE       | ; re-enable interrupts        |

|                | BCF    | EECON1, WREN      | ; disable write to memory     |

#### 6.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 6.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

### 6.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 18.0 "Special Features of the CPU" for more detail.

# 6.6 Flash Program Operation During Code Protection

See Section 18.5 "Program Verification and Code Protection" for details on code protection of Flash program memory.

TABLE 6-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

| Name    | Bit 7                                               | Bit 6                                                 | Bit 5        | Bit 4        | Bit 3         | Bit 2        | Bit 1        | Bit 0      | Reset<br>Values<br>on Page: |  |  |  |

|---------|-----------------------------------------------------|-------------------------------------------------------|--------------|--------------|---------------|--------------|--------------|------------|-----------------------------|--|--|--|

| TBLPTRU |                                                     |                                                       | bit 21       | Program Me   | emory Table F | Pointer Uppe | r Byte (TBLP | TR<20:16>) | 49                          |  |  |  |

| TBPLTRH | Program M                                           | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |              |              |               |              |              |            |                             |  |  |  |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>) |                                                       |              |              |               |              |              |            |                             |  |  |  |

| TABLAT  | Program Memory Table Latch                          |                                                       |              |              |               |              |              |            |                             |  |  |  |

| INTCON  | GIE/GIEH                                            | PEIE/GIEL                                             | TMR0IE       | INT0IE       | RBIE          | TMR0IF       | INT0IF       | RBIF       | 49                          |  |  |  |

| EECON2  | Data Memo                                           | ry Control F                                          | Register 2 ( | not a physic | al register)  |              |              |            | 51                          |  |  |  |

| EECON1  | _                                                   | CFGS                                                  | _            | FREE         | WRERR         | WREN         | WR           | _          | 51                          |  |  |  |

| IPR2    | OSCFIP                                              | _                                                     | USBIP        | _            | _             | HLVDIP       | _            | _          | 51                          |  |  |  |

| PIR2    | OSCFIF                                              | _                                                     | USBIF        | _            | _             | HLVDIF       | _            | _          | 51                          |  |  |  |

| PIE2    | OSCFIE                                              | _                                                     | USBIE        | _            | _             | HLVDIE       | _            | _          | 51                          |  |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash access.

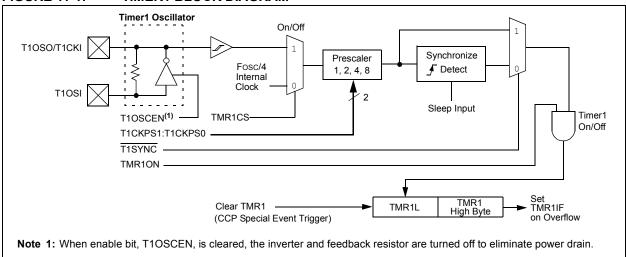

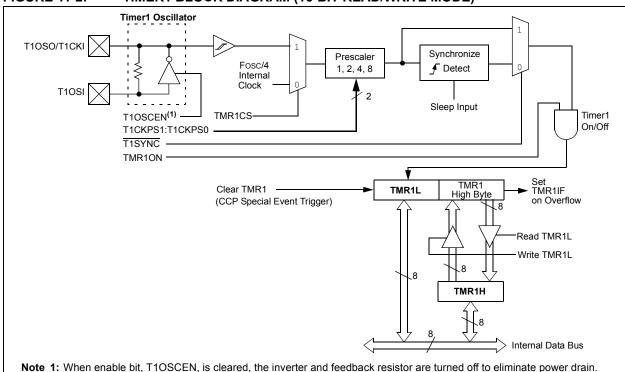

#### 11.1 Timer1 Operation

Timer1 can operate in one of these modes:

- Timer

- · Synchronous Counter

- · Asynchronous Counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>). When TMR1CS is cleared (= 0), Timer1 increments on every internal instruction

cycle (Fosc/4). When the bit is set, Timer1 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

When Timer1 is enabled, the RC1/T1OSI/UOE and RC0/T1OSO/T1CKI pins become inputs. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

#### FIGURE 11-1: TIMER1 BLOCK DIAGRAM

#### FIGURE 11-2: TIMER1 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

# 14.5.1 USB INTERRUPT STATUS REGISTER (UIR)

The USB Interrupt Status register (Register 14-7) contains the flag bits for each of the USB status interrupt sources. Each of these sources has a corresponding interrupt enable bit in the UIE register. All of the USB status flags are ORed together to generate the USBIF interrupt flag for the microcontroller's interrupt funnel.

Once an interrupt bit has been set by the SIE, it must be cleared by software by writing a '0'. The flag bits can also be set in software which can aid in firmware debugging.

When the USB module is in the Low-Power Suspend mode (UCON<1> = 1), the SIE does not get clocked. When in this state, the SIE cannot process packets, and therefore, cannot detect new interrupt conditions other than the Activity Detect Interrupt, Flag ACTVIF. The ACTVIF bit is typically used by USB firmware to detect when the microcontroller should bring the USB module out of the Low-Power Suspend mode (UCON<1> = 0).

x = Bit is unknown

#### REGISTER 14-7: UIR: USB INTERRUPT STATUS REGISTER

W = Writable bit

'1' = Bit is set

| U-0   | R/W-0                                 | R/W-0 | R/W-0                | R/W-0                 | R/W-0                 | R-0    | R/W-0 |

|-------|---------------------------------------|-------|----------------------|-----------------------|-----------------------|--------|-------|

| _     | — SOFIF STALLIF IDLEIF <sup>(1)</sup> |       | TRNIF <sup>(2)</sup> | ACTVIF <sup>(3)</sup> | UERRIF <sup>(4)</sup> | URSTIF |       |

| bit 7 |                                       |       |                      |                       |                       |        | bit 0 |

U = Unimplemented bit, read as '0'

'0' = Bit is cleared

| bit 7 | Unimplemented: Pood as '0'                                                                      |

|-------|-------------------------------------------------------------------------------------------------|

|       | Unimplemented: Read as '0'                                                                      |

| bit 6 | SOFIF: Start-of-Frame Token Interrupt bit                                                       |

|       | 1 = A Start-of-Frame token received by the SIE                                                  |

|       | 0 = No Start-of-Frame token received by the SIE                                                 |

| bit 5 | STALLIF: A STALL Handshake Interrupt bit                                                        |

|       | 1 = A STALL handshake was sent by the SIE                                                       |

|       | 0 = A STALL handshake has not been sent                                                         |

| bit 4 | IDLEIF: Idle Detect Interrupt bit <sup>(1)</sup>                                                |

|       | 1 = Idle condition detected (constant Idle state of 3 ms or more)                               |

|       | 0 = No Idle condition detected                                                                  |

| bit 3 | TRNIF: Transaction Complete Interrupt bit <sup>(2)</sup>                                        |

|       | 1 = Processing of pending transaction is complete; read USTAT register for endpoint information |

|       | 0 = Processing of pending transaction is not complete or no transaction is pending              |

| bit 2 | ACTVIF: Bus Activity Detect Interrupt bit <sup>(3)</sup>                                        |

|       | 1 = Activity on the D+/D- lines was detected                                                    |

|       | 0 = No activity detected on the D+/D- lines                                                     |

| bit 1 | <b>UERRIF:</b> USB Error Condition Interrupt bit <sup>(4)</sup>                                 |

|       | 1 = An unmasked error condition has occurred                                                    |

|       | 0 = No unmasked error condition has occurred.                                                   |

| bit 0 | URSTIF: USB Reset Interrupt bit                                                                 |

|       | 1 = Valid USB Reset occurred; 00h is loaded into UADDR register                                 |

|       | 0 = No USB Reset has occurred                                                                   |

|       |                                                                                                 |

- **Note 1:** Once an Idle state is detected, the user may want to place the USB module in Suspend mode.

- 2: Clearing this bit will cause the USTAT FIFO to advance (valid only for IN, OUT and SETUP tokens).

- 3: This bit is typically unmasked only following the detection of a UIDLE interrupt event.

- **4:** Only error conditions enabled through the UEIE register will set this bit. This bit is a status bit only and cannot be set or cleared by the user.

Legend:

R = Readable bit

-n = Value at POR

TABLE 15-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       |            |                             |                       | SYNC       | = 0, BRGH                   | I = 0, BRG            | <b>316 =</b> 0 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |                |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     | _          | _                           | _                     | _          | _                           | _                     | _              | _                           | _                     | _          | _                           |

| 1.2          | _                     | _          | _                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4          | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6          | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2         | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6         | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | _                     | _          | _                           |

| 115.2        | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           | _                     | _          | _                           |

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |                |     |                       |            |                             |  |  |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|----------------|-----|-----------------------|------------|-----------------------------|--|--|--|--|--|--|

| BAUD<br>RATE | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000      | MHz | Fosc = 1.000 MHz      |            |                             |  |  |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | te Krror value |     | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |  |  |

| 0.3          | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16          | 103 | 0.300                 | -0.16      | 51                          |  |  |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16          | 25  | 1.201                 | -0.16      | 12                          |  |  |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16          | 12  | _                     | _          | _                           |  |  |  |  |  |  |

| 9.6          | 8.929                 | -6.99                         | 6                           | _                     | _              | _   | _                     | _          | _                           |  |  |  |  |  |  |

| 19.2         | 20.833                | 8.51                          | 2                           | _                     | _              | _   | _                     | _          | _                           |  |  |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 0                           | _                     | _              | _   | _                     | _          | _                           |  |  |  |  |  |  |

| 115.2        | 62.500                | -45.75                        | 0                           | _                     | _              | _   | _                     | _          | _                           |  |  |  |  |  |  |

|              |                       |            |                             |                       | SYNC     | = 0, BRGH | l = 1, BRG            | <b>16 =</b> 0 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|----------|-----------|-----------------------|---------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |          |           | Fosc = 10.000 MHz     |               |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | <b>%</b> |           | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     | _          | _                           | _                     | _        | _         | _                     | _             | _                           | _                     | _          | _                           |

| 1.2          | _                     | _          | _                           | _                     | _        | _         | _                     | _             | _                           | _                     | _          | _                           |

| 2.4          | _                     | _          | _                           | _                     | _        | _         | 2.441                 | 1.73          | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16     | 129       | 9.615                 | 0.16          | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16       | 129                         | 19.231                | 0.16     | 64        | 19.531                | 1.73          | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94       | 42                          | 56.818                | -1.36    | 21        | 56.818                | -1.36         | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36      | 21                          | 113.636               | -1.36    | 10        | 125.000               | 8.51          | 4                           | _                     | _          | _                           |

|             |                       |                  | 0                           |                       |                  |                             |                       |                  |                             |  |

|-------------|-----------------------|------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| BAUD        | Fosc                  | Fosc = 4.000 MHz |                             |                       | Fosc = 2.000 MHz |                             |                       | Fosc = 1.000 MHz |                             |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3         | _                     | _                | _                           | 1                     | _                | _                           | 0.300                 | -0.16            | 207                         |  |

| 1.2         | 1.202                 | 0.16             | 207                         | 1.201                 | -0.16            | 103                         | 1.201                 | -0.16            | 51                          |  |

| 2.4         | 2.404                 | 0.16             | 103                         | 2.403                 | -0.16            | 51                          | 2.403                 | -0.16            | 25                          |  |

| 9.6         | 9.615                 | 0.16             | 25                          | 9.615                 | -0.16            | 12                          | _                     | _                | _                           |  |

| 19.2        | 19.231                | 0.16             | 12                          | _                     | _                | _                           | _                     | _                | _                           |  |

| 57.6        | 62.500                | 8.51             | 3                           | _                     | _                | _                           | _                     | _                | _                           |  |

| 115.2       | 125.000               | 8.51             | 1                           | -                     | _                | _                           | _                     | _                | _                           |  |

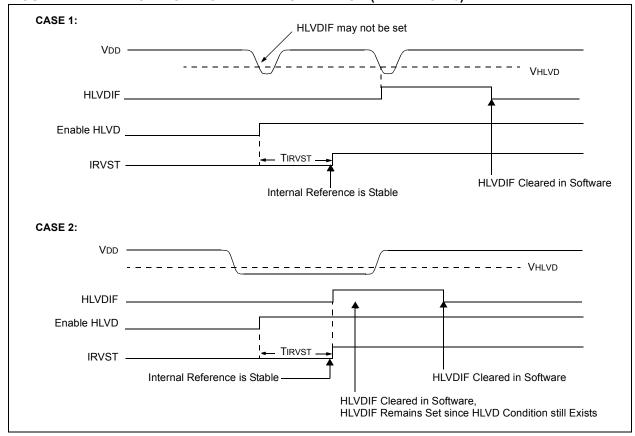

#### 17.2 HLVD Setup

The following steps are needed to set up the HLVD module:

- Disable the module by clearing the HLVDEN bit (HLVDCON<4>).

- 2. Write the value to the HLVDL3:HLVDL0 bits that selects the desired HLVD trip point.

- Set the VDIRMAG bit to detect high voltage (VDIRMAG = 1) or low voltage (VDIRMAG = 0).

- Enable the HLVD module by setting the HLVDEN bit.

- 5. Clear the HLVD Interrupt Flag, HLVDIF (PIR2<2>), which may have been set from a previous interrupt.

- Enable the HLVD interrupt, if interrupts are desired, by setting the HLVDIE and GIE/GIEH bits (PIE2<2> and INTCON<7>). An interrupt will not be generated until the IRVST bit is set.

#### 17.3 Current Consumption

When the module is enabled, the HLVD comparator and voltage divider are enabled and will consume static current. The total current consumption, when enabled, is specified in electrical specification parameter D022 (Section 270 "DC Characteristics").

Depending on the application, the HLVD module does not need to be operating constantly. To decrease the current requirements, the HLVD circuitry may only need to be enabled for short periods where the voltage is checked. After doing the check, the HLVD module may be disabled.

#### 17.4 HLVD Start-up Time

The internal reference voltage of the HLVD module, specified in electrical specification parameter D420 (see Table 21-4 in **Section 21.0 "Electrical Characteristics"**), may be used by other internal circuitry, such as the Programmable Brown-out Reset. If the HLVD or other circuits using the voltage reference are disabled to lower the device's current consumption, the reference voltage circuit will require time to become stable before a low or high-voltage condition can be reliably detected. This start-up time, TIRVST, is an interval that is independent of device clock speed. It is specified in electrical specification parameter 36 (Table 21-10).

The HLVD interrupt flag is not enabled until TIRVST has expired and a stable reference voltage is reached. For this reason, brief excursions beyond the set point may not be detected during this interval. Refer to Figure 17-2 or Figure 17-3.

FIGURE 17-2: LOW-VOLTAGE DETECT OPERATION (VDIRMAG = 0)

#### REGISTER 18-15: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-------|-----|-----|-----|-----|-----|-----|-----------------------|

| _     | _   | _   | _   | _   | _   | _   | SWDTEN <sup>(1)</sup> |

| bit 7 |     |     |     |     |     |     | bit 0                 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-1 **Unimplemented:** Read as '0'

bit 0 **SWDTEN:** Software Controlled Watchdog Timer Enable bit<sup>(1)</sup>

1 = Watchdog Timer is on0 = Watchdog Timer is off

Note 1: This bit has no effect if the Configuration bit, WDTEN, is enabled.

#### TABLE 18-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset<br>Values<br>on Page: |

|--------|-------|-----------------------|-------|-------|-------|-------|-------|--------|-----------------------------|

| RCON   | IPEN  | SBOREN <sup>(1)</sup> | _     | RI    | TO    | PD    | POR   | BOR    | 50                          |

| WDTCON | _     | _                     | _     | _     | _     | _     | _     | SWDTEN | 50                          |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

Note 1: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

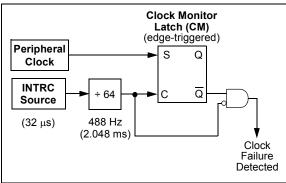

#### 18.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 18-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

FIGURE 18-3: FSCM BLOCK DIAGRAM

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 18-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator (OSCCON is not updated to show the current clock source – this is the fail-safe condition); and

- · the WDT is reset.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator fails, no failure would be detected, nor would any action be possible.

#### 18.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock Monitor events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### 18.4.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTRC provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTRC. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

| COMF             | Compleme                                                                                                                                                                                | nt f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Syntax:          | COMF f                                                                                                                                                                                  | (,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| Operation:       | $(\bar{f}) \rightarrow dest$                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |

| Status Affected: | N, Z                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                       |