Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 48MHz                                                                    |

| Connectivity               | UART/USART, USB                                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                              |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 768 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 13x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

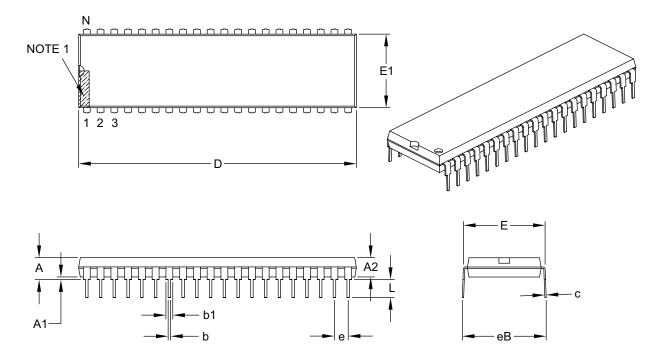

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4450-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F2450/4450

| TABLE 4-4: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |      |                                    |                                                                  |                                 |  |

|------------|---------------------------------------------------------|------|------------------------------------|------------------------------------------------------------------|---------------------------------|--|

| Register   | Applicable Devices                                      |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets,<br>WDT Reset,<br>RESET Instruction,<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

| UEP9       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP8       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP7       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP6       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP5       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP4       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP3       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP2       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP1       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UEP0       | 2450                                                    | 4450 | 0 0000                             | 0 0000                                                           | u uuuu                          |  |

| UCFG       | 2450                                                    | 4450 | 00-0 0000                          | 00-0 0000                                                        | uu-u uuuu                       |  |

| UADDR      | 2450                                                    | 4450 | -000 0000                          | -000 0000                                                        | -uuu uuuu                       |  |

| UCON       | 2450                                                    | 4450 | -0x0 000-                          | -0x0 0x0-                                                        | -uuu uuu-                       |  |

| USTAT      | 2450                                                    | 4450 | -XXX XXX-                          | -XXX XXX-                                                        | -uuu uuu-                       |  |

| UEIE       | 2450                                                    | 4450 | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |

| UEIR       | 2450                                                    | 4450 | 00 0000                            | 00 0000                                                          | uu uuuu                         |  |

| UIE        | 2450                                                    | 4450 | -000 0000                          | -000 0000                                                        | -uuu uuuu                       |  |

| UIR        | 2450                                                    | 4450 | -000 0000                          | -000 0000                                                        | -uuu uuuu                       |  |

| UFRMH      | 2450                                                    | 4450 | xxx                                | xxx                                                              | uuu                             |  |

| UFRML      | 2450                                                    | 4450 | XXXX XXXX                          | XXXX XXXX                                                        | นนนน นนนน                       |  |

|            |                                                         |      |                                    |                                                                  |                                 |  |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

4: See Table 4-3 for Reset value for specific condition.

**5:** PORTA<6>, LATA<6> and TRISA<6> are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

#### 5.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by user software or a Power-on Reset.

#### 5.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. Each stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST   | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|--------------|---------------------------------------------------------|

|      | •            |                                                         |

| SUB1 | •            |                                                         |

|      | RETURN, FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

### 5.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET, W<br>TABLE |

|-------|--------------|--------------------|

|       |              | IADDE              |

| ORG   | nn00h        |                    |

| TABLE | ADDWF        | PCL                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | •            |                    |

|       | •            |                    |

|       | •            |                    |

#### 5.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

| File Name            | Bit 7         | Bit 6                    | Bit 5            | Bit 4            | Bit 3              | Bit 2              | Bit 1              | Bit 0              | Value on<br>POR, BOR | Details<br>on Page: |

|----------------------|---------------|--------------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------|----------------------|---------------------|

| OSCCON               | IDLEN         | _                        | _                | _                | OSTS               | _                  | SCS1               | SCS0               | 0 q-00               | 50, 31              |

| HLVDCON              | VDIRMAG       | _                        | IRVST            | HLVDEN           | HLVDL3             | HLVDL2             | HLVDL1             | HLVDL0             | 0-00 0101            | 50, 185             |

| WDTCON               | _             | —                        | _                | —                | _                  | _                  | _                  | SWDTEN             | 0                    | 50, 204             |

| RCON                 | IPEN          | SBOREN <sup>(2)</sup>    | _                | RI               | TO                 | PD                 | POR                | BOR                | 0q-1 11q0            | 50, 42              |

| TMR1H                | Timer1 Regis  | ter High Byte            |                  | •                |                    |                    |                    |                    | XXXX XXXX            | 50, 120             |

| TMR1L                | Timer1 Regis  | Timer1 Register Low Byte |                  |                  |                    |                    |                    |                    |                      | 50, 120             |

| T1CON                | RD16          | T1RUN                    | T1CKPS1          | T1CKPS0          | T10SCEN            | T1SYNC             | TMR1CS             | TMR10N             | 0000 0000            | 50, 115             |

| TMR2                 | Timer2 Regis  | ter                      |                  | •                |                    |                    |                    |                    | 0000 0000            | 50, 122             |

| PR2                  | Timer2 Period | d Register               |                  |                  |                    |                    |                    |                    | 1111 1111            | 50, 122             |

| T2CON                | —             | T2OUTPS3                 | T2OUTPS2         | T2OUTPS1         | T2OUTPS0           | TMR2ON             | T2CKPS1            | T2CKPS0            | -000 0000            | 50, 121             |

| ADRESH               | A/D Result Re | egister High B           | yte              | •                |                    |                    |                    |                    | XXXX XXXX            | 50, 184             |

| ADRESL               | A/D Result Re | egister Low By           | rte              |                  |                    |                    |                    |                    | XXXX XXXX            | 50, 184             |

| ADCON0               | _             | _                        | CHS3             | CHS2             | CHS1               | CHS0               | GO/DONE            | ADON               | 00 0000              | 50, 175             |

| ADCON1               | _             | _                        | VCFG1            | VCFG0            | PCFG3              | PCFG2              | PCFG1              | PCFG0              | 00 qqqq              | 50, 176             |

| ADCON2               | ADFM          | _                        | ACQT2            | ACQT1            | ACQT0              | ADCS2              | ADCS1              | ADCS0              | 0-00 0000            | 50, 177             |

| CCPR1H               | Capture/Com   | pare/PWM Re              | gister 1 High I  | Byte             |                    |                    |                    |                    | XXXX XXXX            | 50, 124             |

| CCPR1L               | Capture/Com   | pare/PWM Re              | gister 1 Low E   | Byte             |                    |                    |                    |                    | XXXX XXXX            | 50, 124             |

| CCP1CON              | _             | —                        | DC1B1            | DC1B0            | CCP1M3             | CCP1M2             | CCP1M1             | CCP1M0             | 00 0000              | 50, 123,            |

| BAUDCON              | ABDOVF        | RCIDL                    | _                | SCKP             | BRG16              | _                  | WUE                | ABDEN              | 01-0 0-00            | 51, 156,            |

| SPBRGH               | EUSART Bau    | id Rate Gener            | ator Register I  | ligh Byte        |                    |                    |                    |                    | 0000 0000            | 50, 157             |

| SPBRG                | EUSART Bau    | id Rate Gener            | ator Register I  | _ow Byte         |                    |                    |                    |                    | 0000 0000            | 50, 157             |

| RCREG                | EUSART Rec    | eive Register            |                  |                  |                    |                    |                    |                    | 0000 0000            | 50, 165             |

| TXREG                | EUSART Trai   | nsmit Register           |                  |                  |                    |                    |                    |                    | 0000 0000            | 51, 163             |

| TXSTA                | CSRC          | TX9                      | TXEN             | SYNC             | SENDB              | BRGH               | TRMT               | TX9D               | 0000 0010            | 51, 154             |

| RCSTA                | SPEN          | RX9                      | SREN             | CREN             | ADDEN              | FERR               | OERR               | RX9D               | 0000 000x            | 51, 155             |

| EECON2               | Data Memory   | Control Regis            | ster 2 (not a ph | nysical register | .)                 |                    |                    |                    | 0000 0000            | 51, 74              |

| EECON1               | —             | CFGS                     |                  | FREE             | WRERR              | WREN               | WR                 |                    | -x-0 x00-            | 51, 75              |

| IPR2                 | OSCFIP        | _                        | USBIP            | -                | —                  | HLVDIP             | —                  |                    | 1-11                 | 51, 95              |

| PIR2                 | OSCFIF        | _                        | USBIF            | -                | —                  | HLVDIF             | —                  |                    | 0-00                 | 51, 91              |

| PIE2                 | OSCFIE        | —                        | USBIE            | —                | —                  | HLVDIE             | —                  | —                  | 0-00                 | 51, 93              |

| IPR1                 | —             | ADIP                     | RCIP             | TXIP             | _                  | CCP1IP             | TMR2IP             | TMR1IP             | -111 -111            | 51, 94              |

| PIR1                 | _             | ADIF                     | RCIF             | TXIF             | _                  | CCP1IF             | TMR2IF             | TMR1IF             | -000 -000            | 51, 90              |

| PIE1                 | _             | ADIE                     | RCIE             | TXIE             | _                  | CCP1IE             | TMR2IE             | TMR1IE             | -000 -000            | 51, 92              |

| TRISE <sup>(3)</sup> | —             | _                        | _                | _                | _                  | TRISE2             | TRISE1             | TRISE0             | 111                  | 51, 110             |

| TRISD <sup>(3)</sup> | TRISD7        | TRISD6                   | TRISD5           | TRISD4           | TRISD3             | TRISD2             | TRISD1             | TRISD0             | 1111 1111            | 51, 108             |

| TRISC                | TRISC7        | TRISC6                   | _                | _                | _                  | TRISC2             | TRISC1             | TRISC0             | 11111                | 51, 106             |

| TRISB                | TRISB7        | TRISB6                   | TRISB5           | TRISB4           | TRISB3             | TRISB2             | TRISB1             | TRISB0             | 1111 1111            | 51, 103             |

| TRISA                | —             | TRISA6 <sup>(4)</sup>    | TRISA5           | TRISA4           | TRISA3             | TRISA2             | TRISA1             | TRISA0             | -111 1111            | 51, 100             |

| LATE <sup>(3)</sup>  | _             | —                        | _                | _                | _                  | LATE2              | LATE1              | LATE0              | xxx                  | 51, 110             |

| LATD <sup>(3)</sup>  | LATD7         | LATD6                    | LATD5            | LATD4            | LATD3              | LATD2              | LATD1              | LATD0              | XXXX XXXX            | 51, 108             |

| LATC                 | LATC7         | LATC6                    | —                | —                | —                  | LATC2              | LATC1              | LATC0              | xxxxx                | 51, 106             |

| LATB                 | LATB7         | LATB6                    | LATB5            | LATB4            | LATB3              | LATB2              | LATB1              | LATB0              | XXXX XXXX            | 51, 103             |

| LATA                 | —             | LATA6 <sup>(4)</sup>     | LATA5            | LATA4            | LATA3              | LATA2              | LATA1              | LATA0              | -xxx xxxx            | 51, 100             |

| PORTE                | —             | —                        | —                | —                | RE3 <sup>(5)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | x000                 | 51, 109             |

| PORTD <sup>(3)</sup> | RD7           | RD6                      | RD5              | RD4              | RD3                | RD2                | RD1                | RD0                | XXXX XXXX            | 51, 108             |

#### TABLE 5-2 REGISTER FILE SUMMARY (PIC18E2450/4450) (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'. Note

1: Bit 21 of the TBLPTRU allows access to the device Configuration bits.

2: The SBOREN bit is only available when BOREN<1:0> = 0.1; otherwise, the bit reads as '0'.

These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; 3: individual unimplemented bits should be interpreted as '--

RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'. 4:

RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'. 5:

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

#### 8.3 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Request (Flag) registers (PIR1 and PIR2).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

#### REGISTER 8-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| U-0   | R/W-0 | R-0  | R-0  | U-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|------|------|-----|--------|--------|--------|

| —     | ADIF  | RCIF | TXIF | —   | CCP1IF | TMR2IF | TMR1IF |

| bit 7 |       |      |      |     |        |        | bit 0  |

|       |       |      |      |     |        |        |        |

|       |       |      |      |     |        |        |        |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                                                                  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                                                                                                                                      |

| bit 0 | <ul> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                                                           |

| bit 5 | <b>RCIF:</b> EUSART Receive Interrupt Flag bit<br>1 = The EUSART receive buffer, RCREG, is full (cleared when RCREG is read)<br>0 = The EUSART receive buffer is empty                      |

| bit 4 | <b>TXIF:</b> EUSART Transmit Interrupt Flag bit<br>1 = The EUSART transmit buffer, TXREG, is empty (cleared when TXREG is written)<br>0 = The EUSART transmit buffer is full                |

| bit 3 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 2 | <b>CCP1IF:</b> CCP1 Interrupt Flag bit<br><u>Capture mode:</u><br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred               |

|       | <u>Compare mode:</u><br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br><u>PWM mode:</u><br>Unused in this mode. |

| bit 1 | <ul> <li>TMR2IF: TMR2 to PR2 Match Interrupt Flag bit</li> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>           |

| bit 0 | TMR1IF: TMR1 Overflow Interrupt Flag bit <ol> <li>TMR1 register overflowed (must be cleared in software)</li> <li>TMR1 register did not overflow</li> </ol>                                 |

#### 10.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- · Interrupt on overflow

The T0CON register (Register 10-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 10-1. Figure 10-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 10-1: T0CON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR0ON | T08BIT | TOCS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                          |                  |                        |                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------|--------------------|--|

| R = Readal                                                                                                                                                        | ble bit                                                                                                                                                                                                                                                                                                                  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value a                                                                                                                                                      | at POR                                                                                                                                                                                                                                                                                                                   | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

| bit 7                                                                                                                                                             | <b>TMR0ON</b><br>1 = Enabl<br>0 = Stops                                                                                                                                                                                                                                                                                  |                  |                        |                    |  |

| bit 6 <b>T08BIT</b> : Timer0 8-Bit/16-Bit Control bit<br>1 = Timer0 is configured as an 8-bit timer/counter<br>0 = Timer0 is configured as a 16-bit timer/counter |                                                                                                                                                                                                                                                                                                                          |                  |                        |                    |  |

| bit 5                                                                                                                                                             | <b>TOCS</b> : Timer0 Clock Source Select bit<br>1 = Transition on T0CKI pin<br>0 = Internal instruction cycle clock (CLKO)                                                                                                                                                                                               |                  |                        |                    |  |

| bit 4                                                                                                                                                             | <b>T0SE</b> : Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin                                                                                                                                                              |                  |                        |                    |  |

| bit 3                                                                                                                                                             | <ul> <li>PSA: Timer0 Prescaler Assignment bit</li> <li>1 = TImer0 prescaler is not assigned. Timer0 clock input bypasses prescaler.</li> <li>0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.</li> </ul>                                                                                |                  |                        |                    |  |

| bit 2-0                                                                                                                                                           | TOPS2:TOPS0: Timer0 Prescaler Select bits         111 = 1:256 Prescale value         100 = 1:128 Prescale value         101 = 1:64 Prescale value         100 = 1:32 Prescale value         011 = 1:16 Prescale value         010 = 1:8 Prescale value         001 = 1:4 Prescale value         000 = 1:2 Prescale value |                  |                        |                    |  |

#### 11.7 Considerations in Asynchronous Counter Mode

Following a Timer1 interrupt and an update to the TMR1 registers, the Timer1 module uses a falling edge on its clock source to trigger the next register update on the rising edge. If the update is completed after the clock input has fallen, the next rising edge will not be counted.

If the application can reliably update TMR1 before the timer input goes low, no additional action is needed. Otherwise, an adjusted update can be performed

following a later Timer1 increment. This can be done by monitoring TMR1L within the interrupt routine until it increments, and then updating the TMR1H:TMR1L register pair while the clock is low, or one-half of the period of the clock source. Assuming that Timer1 is being used as a Real-Time Clock, the clock source is a 32.768 kHz crystal oscillator. In this case, one-half period of the clock is 15.25  $\mu$ s.

The Real-Time Clock application code in Example 11-1 shows a typical ISR for Timer1, as well as the optional code required if the update cannot be done reliably within the required interval.

EXAMPLE 11-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                                               |

|---------|--------|--------------|---------------------------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                                       |

|         | CLRF   | TMR1L        |                                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator                 |

|         | CLRF   | secs         | ; Initialize timekeeping registers                            |

|         | CLRF   | mins         | ;                                                             |

|         | MOVLW  | .12          |                                                               |

|         | MOVWF  | hours        |                                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                                     |

|         | RETURN |              |                                                               |

| RTCisr  |        |              |                                                               |

|         |        |              | ; Insert the next 4 lines of code when TMR1                   |

|         |        |              | ; cannot be reliably updated before clock pulse goes low      |

|         | BTFSC  | TMR1L,0      | ; wait for TMR1L to become clear                              |

|         | BRA    | \$-2         | ; (may already be clear)                                      |

|         | BTFSS  | TMR1L,0      | ; wait for TMR1L to become set                                |

|         | BRA    | \$-2         | ; TMR1 has just incremented                                   |

|         |        |              | ; If TMR1 update can be completed before clock pulse goes low |

|         |        |              | ; Start ISR here                                              |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                                        |

|         | INCF   | secs, F      | ; Increment seconds                                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                         |

|         | CPFSGT | secs         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | secs         | ; Clear seconds                                               |

|         | INCF   | mins, F      | ; Increment minutes                                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                         |

|         | CPFSGT | mins         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | mins         | ; clear minutes                                               |

|         | INCF   | hours, F     | ; Increment hours                                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                           |

|         | CPFSGT | hours        |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | hours        | ; Reset hours                                                 |

|         | RETURN |              | ; Done                                                        |

|         |        |              |                                                               |

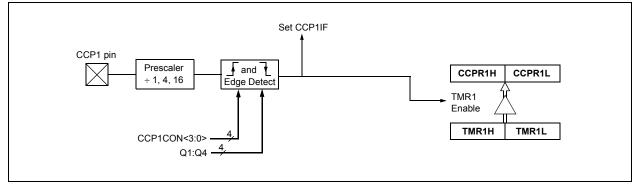

#### 13.1 CCP Module Configuration

The Capture/Compare/PWM module is associated with a control register (generically, CCP1CON) and a data register (CCPR1). The data register, in turn, is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). All registers are both readable and writable.

#### 13.1.1 CCP MODULE AND TIMER RESOURCES

The CCP module utilizes Timer1 or Timer2, depending on the mode selected. Timer1 is available to the module in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

### TABLE 13-1:CCP MODE – TIMERRESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

In Timer1 in Asynchronous Counter mode, the capture operation will not work.

#### 13.2 Capture Mode

In Capture mode, the CCPR1H:CCPR1L register pair captures the 16-bit value of the TMR1 register when an event occurs on the corresponding CCP1 pin. An event is defined as one of the following:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- · every 16th rising edge

The event is selected by the mode select bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF, is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

#### 13.2.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the corresponding TRIS direction bit.

| Note: | If RC2/CCP1 is configured as an output, a |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | write to the port can cause a capture     |  |  |  |  |  |  |  |  |  |

|       | condition.                                |  |  |  |  |  |  |  |  |  |

#### 13.2.2 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCP1IF, should also be cleared following any such change in operating mode.

#### 13.2.3 CCP PRESCALER

There are four prescaler settings in Capture mode. They are specified as part of the operating mode selected by the mode select bits (CCP1M3:CCP1M0). Whenever the CCP module is turned off or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 13-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 13-1: CHANGING BETWEEN CAPTURE PRESCALERS (CCP1 SHOWN)

| CLRF  | CCP1CON     | ; Turn CCP module off |

|-------|-------------|-----------------------|

| MOVLV | NEW_CAPT_PS | ; Load WREG with the  |

|       |             | ; new prescaler mode  |

|       |             | ; value and CCP ON    |

| MOVWE | CCP1CON     | ; Load CCP1CON with   |

|       |             | ; this value          |

|       |             |                       |

#### FIGURE 13-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

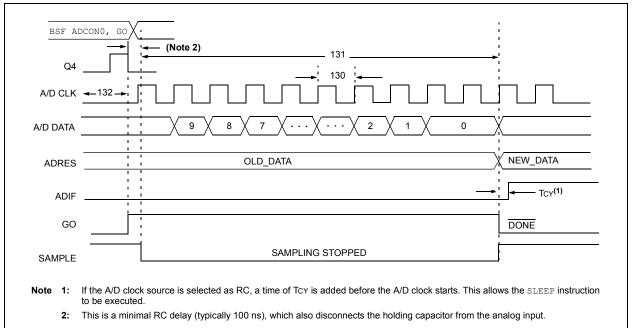

#### 15.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 15-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detection must receive a byte with the value 55h (ASCII "U", which is also the LIN bus Sync character) in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up, using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin, or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH:SPBRG register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCON<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 15-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRG and SPBRGH will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGH register. Refer to Table 15-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. The contents of RCREG should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

#### TABLE 15-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

|       |      |                   |

**Note:** During the ABD sequence, SPBRG and SPBRGH are both used as a 16-bit counter, independent of the BRG16 setting.

#### 15.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREG cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

#### 15.2 EUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTA<4>). In this mode, the EUSART uses the standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is eight bits. An on-chip dedicated 8-bit/16-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator.

The EUSART transmits and receives the LSb first. The EUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate depending on the BRGH and BRG16 bits (TXSTA<2> and BAUDCON<3>). Parity is not supported by the hardware but can be implemented in software and stored as the ninth data bit.

When operating in Asynchronous mode, the EUSART module consists of the following important elements:

- · Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

- · Auto-Wake-up on Sync Break Character

- 12-Bit Break Character Transmit

- Auto-Baud Rate Detection

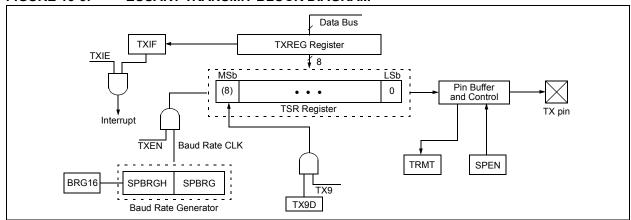

#### 15.2.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART transmitter block diagram is shown in Figure 15-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TcY), the TXREG register is empty and the TXIF flag bit (PIR1<4>) is set. This interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF will be set regardless of the state of TXIE; it cannot be cleared in software. TXIF is also not cleared immediately upon loading TXREG but becomes valid in the second instruction cycle following the load instruction. Polling TXIF immediately following a load of TXREG will return invalid results.

While TXIF indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

Note 1: The TSR register is not mapped in data memory so it is not available to the user.

2: Flag bit, TXIF, is set when enable bit, TXEN, is set.

To set up an Asynchronous Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TXIE.

- If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREG register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 15-3: EUSART TRANSMIT BLOCK DIAGRAM

#### 17.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 17.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| TABLE 17-1: R | REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE |

|---------------|----------------------------------------------------------|

|---------------|----------------------------------------------------------|

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|-----------------------------|

| HLVDCON | VDIRMAG  |           | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 50                          |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 49                          |

| PIR2    | OSCFIF   | —         | USBIF  | —      |        | HLVDIF | —      | _      | 51                          |

| PIE2    | OSCFIE   | —         | USBIE  | —      | —      | HLVDIE |        | —      | 51                          |

| IPR2    | OSCFIP   | _         | USBIP  | _      | _      | HLVDIP |        |        | 51                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

| R/P-0                 | R/P-0                      | U-0                                  | U-0            | R/P-0                | R/P-1                | R/P-1                | R/P-1                |

|-----------------------|----------------------------|--------------------------------------|----------------|----------------------|----------------------|----------------------|----------------------|

| IESO                  | FCMEN                      | —                                    | _              | FOSC3 <sup>(1)</sup> | FOSC2 <sup>(1)</sup> | FOSC1 <sup>(1)</sup> | FOSC0 <sup>(1)</sup> |

| bit 7                 |                            |                                      |                |                      |                      | •                    | bit C                |

|                       |                            |                                      |                |                      |                      |                      |                      |

| Legend:               |                            |                                      |                |                      |                      |                      |                      |

| R = Readable          | e bit                      | P = Programm                         | nable bit      | U = Unimplen         | nented bit, read     | as '0'               |                      |

| -n = Value wh         | nen device is un           | orogrammed                           |                | u = Unchange         | ed from progran      | nmed state           |                      |

|                       |                            |                                      |                |                      |                      |                      |                      |

| bit 7                 | IESO: Interna              | al/External Osci                     | lator Switche  | over bit             |                      |                      |                      |

|                       |                            | Switchover mo                        |                |                      |                      |                      |                      |

|                       |                            | Switchover mo                        |                |                      |                      |                      |                      |

| bit 6                 |                            | -Safe Clock Mo                       |                | bit                  |                      |                      |                      |

|                       |                            | Clock Monitor e                      |                |                      |                      |                      |                      |

| <b>h</b> # <b>F</b> 4 |                            |                                      |                |                      |                      |                      |                      |

| bit 5-4               | •                          | ted: Read as '0                      |                | (1)                  |                      |                      |                      |

| bit 3-0               |                            | C0: Oscillator S                     |                |                      |                      |                      |                      |

|                       | 111x = HS 0<br>110x = HS 0 | scillator, PLL er                    | abled (HSP     | LL)                  |                      |                      |                      |

|                       |                            |                                      | S oscillator u | sed by USB (IN       | THS)                 |                      |                      |

|                       |                            | nal oscillator, XT                   |                |                      |                      |                      |                      |

|                       | 1001 = Interr              | nal oscillator, Cl                   | KO function    | on RA6, ÉC us        | ed by USB (IN        | ГСКО)                |                      |

|                       |                            |                                      |                | n RA6, EC used       | •                    | D)                   |                      |

|                       |                            | •                                    |                | D function on R/     | ( )                  |                      |                      |

|                       |                            | scillator, PLL er<br>scillator, CLKO |                | unction on RA6       | (ECPIO)              |                      |                      |

|                       |                            | scillator, CERO                      |                | · · ·                |                      |                      |                      |

|                       |                            | scillator, PLL en                    |                |                      |                      |                      |                      |

|                       | 000x = XT os               |                                      | \              | ,                    |                      |                      |                      |

**Note 1:** The microcontroller and USB module both use the selected oscillator as their clock source in XT, HS and EC modes. The USB module uses the indicated XT, HS or EC oscillator as its clock source whenever the microcontroller uses the internal oscillator.

#### TABLE 19-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                 |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| a               | RAM access bit                                                                                                                              |  |  |  |  |  |  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                 |  |  |  |  |  |  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                |  |  |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                         |  |  |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                  |  |  |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                              |  |  |  |  |  |  |

| d               | Destination select bit                                                                                                                      |  |  |  |  |  |  |

|                 | d = 0: store result in WREG<br>d = 1: store result in file register f                                                                       |  |  |  |  |  |  |

| dest            | Destination: either the WREG register or the specified register file location.                                                              |  |  |  |  |  |  |

| f               | 8-bit register file address (00h to FFh) or 2-bit FSR designator (0h to 3h).                                                                |  |  |  |  |  |  |

|                 | 12-bit register file address (000h to FFFh). This is the source address.                                                                    |  |  |  |  |  |  |

| f <sub>s</sub>  | 12-bit register file address (000h to FFFh). This is the destination address.                                                               |  |  |  |  |  |  |

| f <sub>d</sub>  | Global Interrupt Enable bit.                                                                                                                |  |  |  |  |  |  |

| GIE             |                                                                                                                                             |  |  |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                   |  |  |  |  |  |  |

| label           | Label name.                                                                                                                                 |  |  |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions: |  |  |  |  |  |  |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                          |  |  |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                        |  |  |  |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                        |  |  |  |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                         |  |  |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for                                     |  |  |  |  |  |  |

| 11              | Call/Branch and Return instructions.                                                                                                        |  |  |  |  |  |  |

| PC              | Program Counter.                                                                                                                            |  |  |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                   |  |  |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                  |  |  |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                            |  |  |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                           |  |  |  |  |  |  |

| PD              | Power-Down bit.                                                                                                                             |  |  |  |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                              |  |  |  |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                               |  |  |  |  |  |  |

| S               | Fast Call/Return mode select bit                                                                                                            |  |  |  |  |  |  |

|                 | s = 0: do not update into/from shadow registers                                                                                             |  |  |  |  |  |  |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                      |  |  |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a program memory location).                                                                                 |  |  |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                          |  |  |  |  |  |  |

| TO              | Time-out bit.                                                                                                                               |  |  |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                               |  |  |  |  |  |  |

| u               | Unused or unchanged.                                                                                                                        |  |  |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                             |  |  |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                             |  |  |  |  |  |  |

| х               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for                              |  |  |  |  |  |  |

|                 | compatibility with all Microchip software tools.                                                                                            |  |  |  |  |  |  |

| ZS              | 7-bit offset value for indirect addressing of register files (source).                                                                      |  |  |  |  |  |  |

| z <sub>d</sub>  | 7-bit offset value for indirect addressing of register files (destination).                                                                 |  |  |  |  |  |  |

| { }             | Optional argument.                                                                                                                          |  |  |  |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                               |  |  |  |  |  |  |

| (text)          | The contents of text.                                                                                                                       |  |  |  |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer, expr.                                                                             |  |  |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                |  |  |  |  |  |  |

| < >             | Register bit field.                                                                                                                         |  |  |  |  |  |  |

| E               | In the set of.                                                                                                                              |  |  |  |  |  |  |

| italics         | User-defined term (font is Courier New).                                                                                                    |  |  |  |  |  |  |

# PIC18F2450/4450

| ADDWFC                         | ADD W an            | d Carry bit to                     | o f                        | ANDLW             | A  |

|--------------------------------|---------------------|------------------------------------|----------------------------|-------------------|----|

| Syntax:                        | ADDWFC              | f {,d {,a}}                        |                            | Syntax:           | A  |

| Operands:                      | $0 \leq f \leq 255$ |                                    |                            | Operands:         | 0  |

|                                | $d \in [0,1]$       |                                    |                            | Operation:        | (\ |

| Operation                      | a ∈ [0,1]           | (C) deat                           |                            | Status Affected:  | N  |

| Operation:<br>Status Affected: | (W) + (f) +         | · · /                              |                            | Encoding:         | Γ  |

|                                | N, OV, C, E         |                                    |                            | Description:      | Т  |

| Encoding:                      | 0010                |                                    | ff ffff                    |                   | 8  |

| Description:                   |                     | If 'd' is '0', the                 | d data memory<br>result is | Words:            | 1  |

|                                |                     | V. If 'd' is '1', t                |                            | Cycles:           | 1  |

|                                |                     | ata memory lo                      |                            | Q Cycle Activity: |    |

|                                | ,                   |                                    | nk is selected.            | Q1                | 1  |

|                                | GPR bank            | (default).                         |                            | Decode            | Re |

|                                |                     |                                    | led instruction            |                   |    |

|                                |                     | led, this instru<br>Literal Offset | ction operates             | Example:          | А  |

|                                |                     | never f $\leq$ 95 (5               | •                          | Before Instruc    |    |

|                                |                     | .2.3 "Byte-O                       |                            | W                 | =  |

|                                |                     | ed Instruction<br>set Mode" for    | ns in Indexed              | After Instructi   | on |

| Words:                         | 1                   |                                    |                            | W                 | =  |

| Cycles:                        | 1                   |                                    |                            |                   |    |

| Q Cycle Activity:              | I                   |                                    |                            |                   |    |

| Q Cycle Activity.<br>Q1        | Q2                  | Q3                                 | Q4                         |                   |    |

| Decode                         | Read                | Process                            | Write to                   |                   |    |

|                                | register 'f'        | Data                               | destination                |                   |    |

|                                |                     |                                    |                            |                   |    |

| Example:                       | ADDWFC              | REG, 0,                            | 1                          |                   |    |

| Before Instruc<br>Carry bit    |                     |                                    |                            |                   |    |

| REG                            | = 02h               |                                    |                            |                   |    |

| W<br>After Instructio          | = 4Dh               |                                    |                            |                   |    |

| Carry bit                      |                     |                                    |                            |                   |    |

| REG                            | = 02h<br>= 50h      |                                    |                            |                   |    |

| vv                             | - 5011              |                                    |                            |                   |    |

|                                |                     |                                    |                            |                   |    |

| ANDLW                      |       | AND Lite                | AND Literal with W |                 |    |            |  |  |  |  |

|----------------------------|-------|-------------------------|--------------------|-----------------|----|------------|--|--|--|--|

| Syntax:                    |       | ANDLW                   | ANDLW k            |                 |    |            |  |  |  |  |

| Operands:                  |       | $0 \le k \le 2$         | 55                 |                 |    |            |  |  |  |  |

| Operation:                 |       | (W) .ANE                | $k \to W$          | /               |    |            |  |  |  |  |

| Status Affecte             | ed:   | N, Z                    |                    |                 |    |            |  |  |  |  |

| Encoding:                  |       | 0000                    | 1011               | . kkl           | kk | kkkk       |  |  |  |  |

| Description:               |       | The cont<br>8-bit liter |                    |                 |    |            |  |  |  |  |

| Words:                     |       | 1                       |                    |                 |    |            |  |  |  |  |

| Cycles:                    |       | 1                       |                    |                 |    |            |  |  |  |  |

| Q Cycle Acti               | vity: |                         |                    |                 |    |            |  |  |  |  |

| Q1                         | I     | Q2                      |                    | Q3              |    | Q4         |  |  |  |  |

| Decode                     |       | Read litera<br>'k'      |                    | Process<br>Data |    | Write to W |  |  |  |  |

| Example:                   |       | ANDLW                   | 05Fh               | 1               |    |            |  |  |  |  |

| Before I<br>W<br>After Ins |       | = A3h                   |                    |                 |    |            |  |  |  |  |

| W                          |       | = 03h                   |                    |                 |    |            |  |  |  |  |

# PIC18F2450/4450