Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

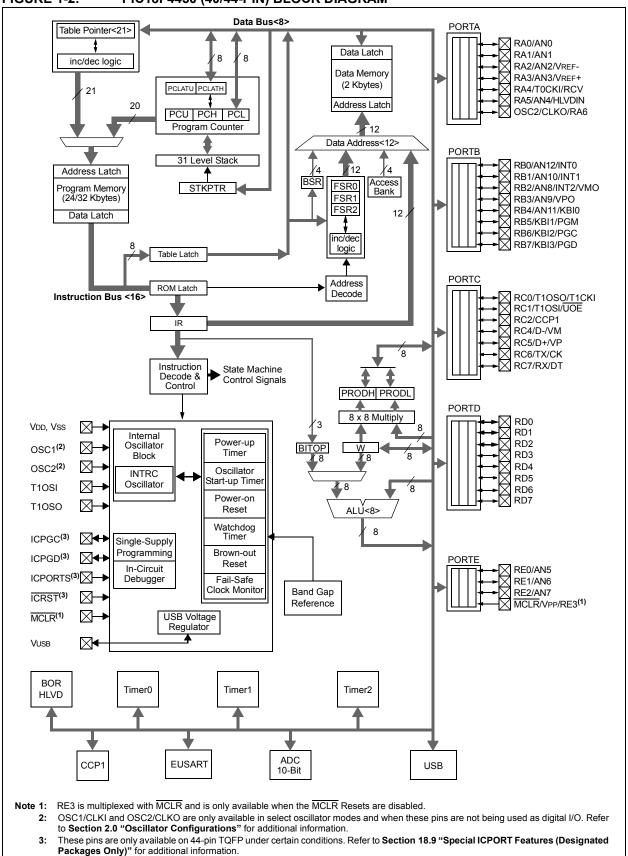

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 48MHz                                                                     |

| Connectivity               | UART/USART, USB                                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 13x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f4450-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-3: PIC18F4450 PINOUT I/O DESCRIPTIONS (CONTINUED) |            |            |           |         |         |                                                      |  |  |

|-----------------------------------------------------------|------------|------------|-----------|---------|---------|------------------------------------------------------|--|--|

| Pin Name                                                  | Pi         | Pin Number |           | Pin     | Buffer  | Description                                          |  |  |

| Fill Naille                                               | PDIP       | QFN        | TQFP      | Туре    | Туре    | Description                                          |  |  |

|                                                           |            |            |           |         |         | PORTD is a bidirectional I/O port.                   |  |  |

| RD0                                                       | 19         | 38         | 38        | I/O     | ST      | Digital I/O.                                         |  |  |

| RD1                                                       | 20         | 39         | 39        | I/O     | ST      | Digital I/O.                                         |  |  |

| RD2                                                       | 21         | 40         | 40        | I/O     | ST      | Digital I/O.                                         |  |  |

| RD3                                                       | 22         | 41         | 41        | I/O     | ST      | Digital I/O.                                         |  |  |

| RD4                                                       | 27         | 2          | 2         | I/O     | ST      | Digital I/O.                                         |  |  |

| RD5                                                       | 28         | 3          | 3         | I/O     | ST      | Digital I/O.                                         |  |  |

| RD6                                                       | 29         | 4          | 4         | I/O     | ST      | Digital I/O.                                         |  |  |

| RD7                                                       | 30         | 5          | 5         | I/O     | ST      | Digital I/O.                                         |  |  |

| Legend: TTL = TT                                          | L compat   | ible inp   | ut        |         | C       | CMOS = CMOS compatible input or output               |  |  |

|                                                           | hmitt Trig | ger inp    | ut with C | MOS le  | evels l | = Input                                              |  |  |

| 0 = Ou                                                    | tput       |            |           |         | F       | P = Power                                            |  |  |

| Note 1: Those pin                                         | ara Na     | Connor     | t unloce  | the ICI |         | figuration bit is set. For NC/ICDOPTS, the pip is No |  |  |

## TABLE 1-3: PIC18F4450 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

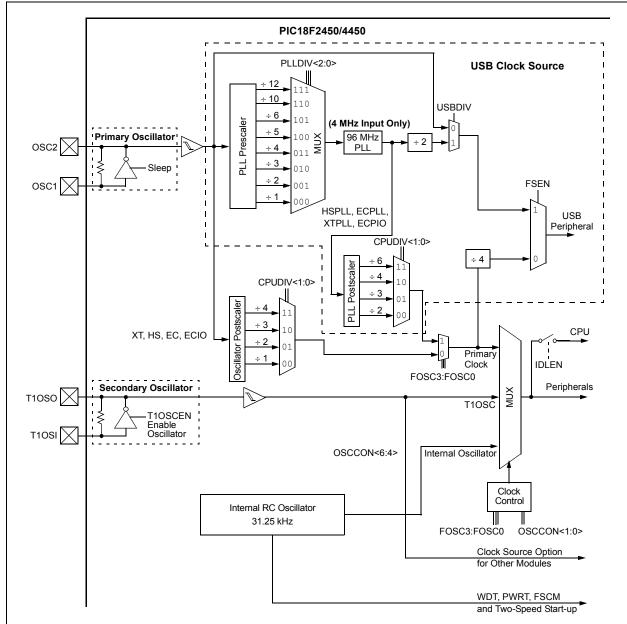

## 2.2.1 OSCILLATOR MODES AND USB OPERATION

Because of the unique requirements of the USB module, a different approach to clock operation is necessary. In previous PIC<sup>®</sup> microcontrollers, all core and peripheral clocks were driven by a single oscillator source; the usual sources were primary, secondary or the internal oscillator. With PIC18F2450/4450 devices, the primary oscillator becomes part of the USB module and cannot be associated to any other clock source. Thus, the USB module must be clocked from the primary clock source; however, the microcontroller core and other peripherals can be separately clocked from the secondary or internal oscillators as before.

Because of the timing requirements imposed by USB, an internal clock of either 6 MHz or 48 MHz is required while the USB module is enabled. Fortunately, the microcontroller and other peripherals are not required to run at this clock speed when using the primary oscillator. There are numerous options to achieve the USB module clock requirement and still provide flexibility for clocking the rest of the device from the primary oscillator source. These are detailed in Section 2.3 "Oscillator Settings for USB".

#### FIGURE 2-1: PIC18F2450/4450 CLOCK DIAGRAM

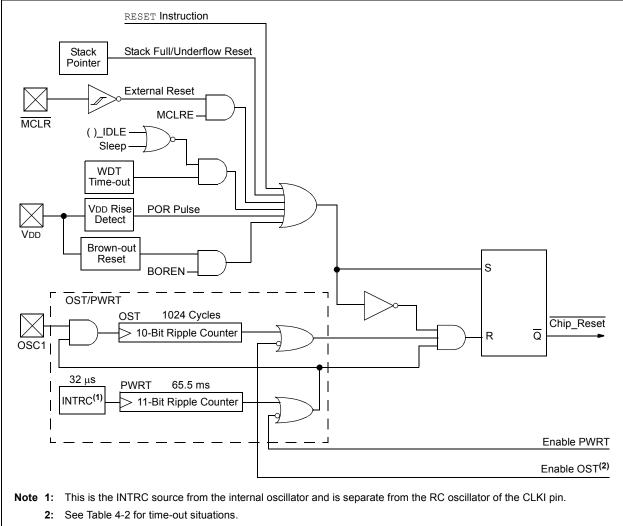

## 4.0 RESET

The PIC18F2450/4450 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by  $\overline{\text{MCLR}}$ , POR and BOR, and covers the operation of the various start-up timers. Stack Reset events are covered in **Section 5.1.2.4** "**Stack Full and Underflow Resets**". WDT Resets are covered in **Section 18.2** "**Watchdog Timer (WDT)**".

A simplified block diagram of the on-chip Reset circuit is shown in Figure 4-1.

## 4.1 RCON Register

Device Reset events are tracked through the RCON register (Register 4-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be cleared by the event and must be set by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 4.6 "Reset State of Registers"**.

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 8.0 "Interrupts". BOR is covered in Section 4.4 "Brown-out Reset (BOR)".

## 4.5 Device Reset Timers

PIC18F2450/4450 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of the PIC18F2450/4450 devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of  $2048 \times 32 \ \mu s = 65.6 \ ms$ . While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip to chip due to temperature and process variation. See DC parameter 33 (Table 21-10) for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33, Table 21-10). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, HS and HSPLL modes and only on Power-on Reset or on exit from most power-managed modes.

## 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR condition has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figure 4-3 through Figure 4-6 also apply to devices operating in XT mode. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator    | Power-up <sup>(2)</sup> an                             | Exit from                       |                                 |  |

|---------------|--------------------------------------------------------|---------------------------------|---------------------------------|--|

| Configuration | <b>PWRTEN</b> = 0                                      | <b>PWRTEN</b> = 1               | Power-Managed Mode              |  |

| HS, XT        | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |  |

| HSPLL, XTPLL  | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup> |  |

| EC, ECIO      | 66 ms <sup>(1)</sup>                                   | —                               | —                               |  |

| ECPLL, ECPIO  | 66 ms <sup>(1)</sup> + 2 ms <sup>(2)</sup>             | 2 ms <sup>(2)</sup>             | 2 ms <sup>(2)</sup>             |  |

| INTIO, INTCKO | 66 ms <sup>(1)</sup>                                   | —                               | —                               |  |

| INTHS, INTXT  | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                       | 1024 Tosc                       |  |

TABLE 4-2:TIME-OUT IN VARIOUS SITUATIONS

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

**2:** 2 ms is the nominal time required for the PLL to lock.

## 8.5 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1 and IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 8-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| U-0                                                     | R/W-1                                                              | R/W-1             | R/W-1            | U-0        | R/W-1  | R/W-1           | R/W-1  |  |  |  |

|---------------------------------------------------------|--------------------------------------------------------------------|-------------------|------------------|------------|--------|-----------------|--------|--|--|--|

| —                                                       | ADIP                                                               | RCIP              | TXIP             | —          | CCP1IP | TMR2IP          | TMR1IP |  |  |  |

| bit 7                                                   |                                                                    |                   |                  |            |        |                 | bit (  |  |  |  |

|                                                         |                                                                    |                   |                  |            |        |                 |        |  |  |  |

| Legend:                                                 |                                                                    |                   |                  |            |        |                 |        |  |  |  |

| R = Readabl                                             | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                   |                  |            |        |                 |        |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |                                                                    |                   |                  |            |        | x = Bit is unkr | nown   |  |  |  |

|                                                         |                                                                    |                   |                  |            |        |                 |        |  |  |  |

| bit 7                                                   | Unimpleme                                                          | nted: Read as '   | 0'               |            |        |                 |        |  |  |  |

| bit 6                                                   |                                                                    | converter Interru | pt Priority bit  |            |        |                 |        |  |  |  |

|                                                         | 1 = High prive                                                     | •                 |                  |            |        |                 |        |  |  |  |

| 6.4 <b>F</b>                                            | 0 = Low price                                                      | •                 |                  | L 14       |        |                 |        |  |  |  |

| bit 5                                                   |                                                                    | RT Receive Int    | errupt Priority  | DIC        |        |                 |        |  |  |  |

|                                                         | 1 = High pri<br>0 = Low pric                                       | ,                 |                  |            |        |                 |        |  |  |  |

| bit 4                                                   | •                                                                  | RT Transmit Int   | errupt Priority  | bit        |        |                 |        |  |  |  |

|                                                         | 1 = High pri                                                       | ority             |                  |            |        |                 |        |  |  |  |

|                                                         | 0 = Low pric                                                       | •                 |                  |            |        |                 |        |  |  |  |

| bit 3                                                   | Unimpleme                                                          | nted: Read as '   | 0'               |            |        |                 |        |  |  |  |

| bit 2                                                   | CCP1IP: CC                                                         | P1 Interrupt Pri  | ority bit        |            |        |                 |        |  |  |  |

|                                                         | 1 = High pri                                                       | ority             |                  |            |        |                 |        |  |  |  |

|                                                         | 0 = Low price                                                      | ority             |                  |            |        |                 |        |  |  |  |

| bit 1                                                   | TMR2IP: TM                                                         | IR2 to PR2 Mate   | ch Interrupt Pr  | iority bit |        |                 |        |  |  |  |

|                                                         | 1 = High pri                                                       | •                 |                  |            |        |                 |        |  |  |  |

|                                                         | 0 = Low price                                                      | •                 |                  |            |        |                 |        |  |  |  |

| bit 0                                                   |                                                                    | IR1 Overflow In   | terrupt Priority | bit        |        |                 |        |  |  |  |

|                                                         | 1 = High prid0 = Low prid                                          | •                 |                  |            |        |                 |        |  |  |  |

|                                                         | 0 - 10  m pro-                                                     | Jiity             |                  |            |        |                 |        |  |  |  |

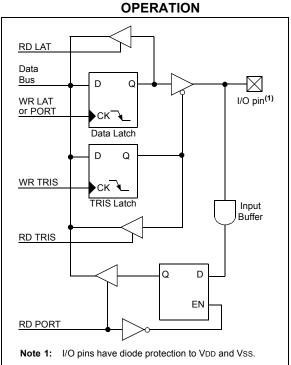

## 9.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Output Latch register)

The Output Latch register (LATA) is useful for readmodify-write operations on the value driven by the I/O pins.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 9-1.

FIGURE 9-1: GENERIC I/O PORT

## 9.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins; writing to it will write to the port latch.

The Output Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA6 pin is multiplexed with the main oscillator pin; it is enabled as an oscillator or I/O pin by the selection of the main oscillator in Configuration Register 1H (see **Section 18.1 "Configuration Bits"** for details). When not used as a port pin, RA6 and its associated TRIS and LAT bits are read as '0'.

RA4 is also multiplexed with the USB module; it serves as a receiver input from an external USB transceiver. For details on configuration of the USB module, see **Section 14.2 "USB Status and Control"**.

Several PORTA pins are multiplexed with analog inputs. The operation of pins RA5 and RA3:RA0 as A/D Converter inputs is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register 1).

| Note: | On a Power-on Reset, RA5 and RA3:RA0          |

|-------|-----------------------------------------------|

|       | are configured as analog inputs and read      |

|       | as '0'. RA4 is configured as a digital input. |

All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

| EXAMPLE  | 9-1:   | INITIALIZING PORTA    |

|----------|--------|-----------------------|

| CLRF PO  | RTA ;  | Initialize PORTA by   |

|          | ;      | clearing output       |

|          | ;      | data latches          |

| CLRF LA  | TA ;   | Alternate method      |

|          | ;      | to clear output       |

|          | ;      | data latches          |

| MOVLW OF | h ;    | Configure A/D         |

| MOVWF AD | CON1 ; | for digital inputs    |

| MOVLW 0C | Fh ;   | Value used to         |

|          | ;      | initialize data       |

|          | ;      | direction             |

| MOVWF TR | ISA ;  | Set RA<3:0> as inputs |

|          | ;      | RA<5:4> as outputs    |

The PPBRST bit (UCON<6>) controls the Reset status when Double-Buffering mode (ping-pong buffering) is used. When the PPBRST bit is set, all Ping-Pong Buffer Pointers are set to the EVEN buffers. PPBRST has to be cleared by firmware. This bit is ignored in buffering modes not using ping-pong buffering.

The PKTDIS bit (UCON<4>) is a flag indicating that the SIE has disabled packet transmission and reception. This bit is set by the SIE when a SETUP token is received to allow setup processing. This bit cannot be set by the microcontroller, only cleared; clearing it allows the SIE to continue transmission and/or reception. Any pending events within the Buffer Descriptor Table will still be available, indicated within the USTAT register's FIFO buffer.

The RESUME bit (UCON<2>) allows the peripheral to perform a remote wake-up by executing Resume signaling. To generate a valid remote wake-up, firmware must set RESUME for 10 ms and then clear the bit. For more information on Resume signaling, see Sections 7.1.7.5, 11.4.4 and 11.9 in the USB 2.0 Specification.

The SUSPND bit (UCON<1>) places the module and supporting circuitry (i.e., voltage regulator) in a lowpower mode. The input clock to the SIE is also disabled. This bit should be set by the software in response to an IDLEIF interrupt. It should be reset by the microcontroller firmware after an ACTVIF interrupt is observed. When this bit is active, the device remains attached to the bus but the transceiver outputs remain Idle. The voltage on the VUSB pin may vary depending on the value of this bit. Setting this bit before a IDLEIF request will result in unpredictable bus behavior.

Note: While in Suspend mode, a typical bus powered USB device is limited to 500 μA of current. This is the complete current drawn by the PIC microcontroller and its supporting circuitry. Care should be taken to assure minimum current draw when the device enters Suspend mode.

## 14.2.2 USB CONFIGURATION REGISTER (UCFG)

Prior to communicating over USB, the module's associated internal and/or external hardware must be configured. Most of the configuration is performed with the UCFG register (Register 14-2). The separate USB voltage regulator (see **Section 14.2.2.8** "Internal **Regulator**") is controlled through the Configuration registers.

The UFCG register contains most of the bits that control the system level behavior of the USB module. These include:

- Bus Speed (full speed versus low speed)

- On-Chip Transceiver Enable

- Ping-Pong Buffer Usage

The UCFG register also contains two bits which aid in module testing, debugging and USB certifications. These bits control output enable state monitoring and eye pattern generation.

**Note:** The USB speed, transceiver and pull-up should only be configured during the module setup phase. It is not recommended to switch these settings while the module is enabled.

#### 14.2.2.1 Internal Transceiver

The USB peripheral has a built-in, USB 2.0, full-speed and low-speed compliant transceiver, internally connected to the SIE. This feature is useful for low-cost, single chip applications. The UTRDIS bit (UCFG<3>) controls the transceiver; it is enabled by default (UTRDIS = 0). The FSEN bit (UCFG<2>) controls the transceiver speed; setting the bit enables full-speed operation. The on-chip USB pull-up resistors are controlled by the UPUEN bit (UCFG<4>). They can only be selected when the on-chip transceiver is enabled.

The USB specification requires 3.3V operation for communications; however, the rest of the chip may be running at a higher voltage. Thus, the transceiver is supplied power from a separate source, VUSB.

#### 14.2.2.2 External Transceiver

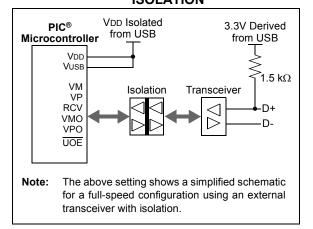

This module provides support for use with an off-chip transceiver. The off-chip transceiver is intended for applications where physical conditions dictate the location of the transceiver to be away from the SIE. For example, applications that require isolation from the USB could use an external transceiver through some isolation to the microcontroller's SIE (Figure 14-2). External transceiver operation is enabled by setting the UTRDIS bit.

#### FIGURE 14-2: TYPICAL EXTERNAL TRANSCEIVER WITH ISOLATION

#### TABLE 14-1: DIFFERENTIAL OUTPUTS TO TRANSCEIVER

| VPO | VMO | Bus State         |  |  |  |  |  |

|-----|-----|-------------------|--|--|--|--|--|

| 0   | 0   | Single-Ended Zero |  |  |  |  |  |

| 0   | 1   | Differential '0'  |  |  |  |  |  |

| 1   | 0   | Differential '1'  |  |  |  |  |  |

| 1   | 1   | Illegal Condition |  |  |  |  |  |

## TABLE 14-2:SINGLE-ENDED INPUTSFROM TRANSCEIVER

| VP | VM | Bus State         |  |  |  |  |  |

|----|----|-------------------|--|--|--|--|--|

| 0  | 0  | Single-Ended Zero |  |  |  |  |  |

| 0  | 1  | Low Speed         |  |  |  |  |  |

| 1  | 0  | High Speed        |  |  |  |  |  |

| 1  | 1  | Error             |  |  |  |  |  |

The  $\overline{\text{UOE}}$  signal toggles the state of the external transceiver. This line is pulled low by the device to enable the transmission of data from the SIE to an external device.

#### 14.2.2.3 Internal Pull-up Resistors

The PIC18F2450/4450 devices have built-in pull-up resistors designed to meet the requirements for low-speed and full-speed USB. The UPUEN bit (UCFG<4>) enables the internal pull-ups. Figure 14-1 shows the pull-ups and their control.

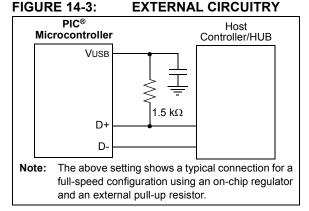

#### 14.2.2.4 Pull-up Resistors

The PIC18F2450/4450 devices require an external pull-up resistor to meet the requirements for low-speed and full-speed USB. Either an external 3.3V supply or the VUSB pin may be used to pull up D+ or D-. The pull-up resistor must be 1.5 k $\Omega$  (±5%) as required by the USB specifications. Figure 14-3 shows an example with the VUSB pin.

## 14.2.2.5 Ping-Pong Buffer Configuration

The usage of ping-pong buffers is configured using the PPB1:PPB0 bits. Refer to **Section 14.4.4 "Ping-Pong Buffering"** for a complete explanation of the ping-pong buffers.

## 14.2.2.6 USB Output Enable Monitor

The USB  $\overline{OE}$  monitor provides indication as to whether the SIE is listening to the bus or actively driving the bus. This is enabled by default when using an external transceiver or when UCFG<6> = 1.

The USB  $\overline{\text{OE}}$  monitoring is useful for initial system debugging, as well as scope triggering during eye pattern generation tests.

## 14.2.2.7 Eye Pattern Test Enable

An automatic eye pattern test can be generated by the module when the UCFG<7> bit is set. The eye pattern output will be observable based on module settings, meaning that the user is first responsible for configuring the SIE clock settings, pull-up resistor and Transceiver mode. In addition, the module has to be enabled.

Once UTEYE is set, the module emulates a switch from a receive to transmit state and will start transmitting a J-K-J-K bit sequence (K-J-K-J for full speed). The sequence will be repeated indefinitely while the Eye Pattern Test mode is enabled.

Note that this bit should never be set while the module is connected to an actual USB system. This test mode is intended for board verification to aid with USB certification tests. It is intended to show a system developer the noise integrity of the USB signals which can be affected by board traces, impedance mismatches and proximity to other system components. It does not properly test the transition from a receive to a transmit state. Although the eye pattern is not meant to replace the more complex USB certification test, it should aid during first order system debugging.

## 14.2.2.8 Internal Regulator

The PIC18F2450/4450 devices have a built-in 3.3V regulator to provide power to the internal transceiver and provide a source for the external pull-ups. An external 220 nF (±20%) capacitor is required for stability.

| Note: | The drive from VUSB is sufficient to only    |

|-------|----------------------------------------------|

|       | drive an external pull-up in addition to the |

|       | internal transceiver.                        |

The regulator is disabled by default and can be enabled through the VREGEN Configuration bit. When enabled, the voltage is visible on pin VUSB. When the regulator is disabled, a 3.3V source must be provided through the VUSB pin for the internal transceiver. If the internal transceiver is disabled, VUSB is not used.

- Note 1: Do not enable the internal regulator if an external regulator is connected to VUSB.

- 2: VDD must be greater than or equal to VUSB at all times, even with the regulator disabled.

#### 14.2.5 USB ADDRESS REGISTER (UADDR)

The USB Address register contains the unique USB address that the peripheral will decode when active. UADDR is reset to 00h when a USB Reset is received, indicated by URSTIF, or when a Reset is received from the microcontroller. The USB address must be written by the microcontroller during the USB setup phase (enumeration) as part of the Microchip USB firmware support.

#### 14.2.6 USB FRAME NUMBER REGISTERS (UFRMH:UFRML)

The Frame Number registers contain the 11-bit frame number. The low-order byte is contained in UFRML, while the three high-order bits are contained in UFRMH. The register pair is updated with the current frame number whenever a SOF token is received. For the microcontroller, these registers are read-only. The Frame Number register is primarily used for isochronous transfers.

## 14.3 USB RAM

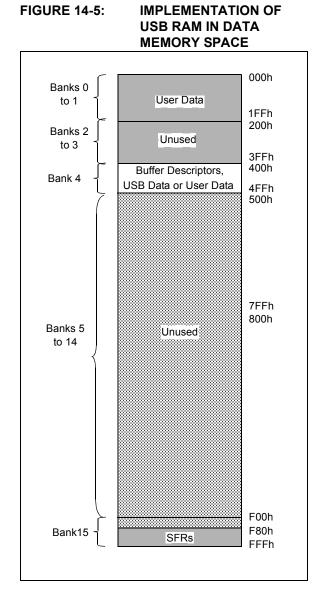

USB data moves between the microcontroller core and the SIE through a memory space known as the USB RAM. This is a special dual port memory that is mapped into the normal data memory space in Bank 4 (400h to 4FFh) for a total of 256 bytes (Figure 14-5).

Some portion of Bank 4 (400h through 4FFh) is used specifically for endpoint buffer control, while the remaining portion is available for USB data. Depending on the type of buffering being used, all but 8 bytes of Bank 4 may also be available for use as USB buffer space.

Although USB RAM is available to the microcontroller as data memory, the sections that are being accessed by the SIE should not be accessed by the microcontroller. A semaphore mechanism is used to determine the access to a particular buffer at any given time. This is discussed in **Section 14.4.1.1 "Buffer Ownership**".

#### 14.5.4 USB ERROR INTERRUPT ENABLE REGISTER (UEIE)

The USB Error Interrupt Enable register (Register 14-10) contains the enable bits for each of the USB error interrupt sources. Setting any of these bits will enable the respective error interrupt source in the UEIR register to propagate into the UERR bit at the top level of the interrupt logic.

As with the UIE register, the enable bits only affect the propagation of an interrupt condition to the microcontroller's interrupt logic. The flag bits are still set by their interrupt conditions, allowing them to be polled and serviced without actually generating an interrupt.

## REGISTER 14-10: UEIE: USB ERROR INTERRUPT ENABLE REGISTER

| R/W-0           | U-0                                   | U-0                              | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |

|-----------------|---------------------------------------|----------------------------------|-----------------|------------------|------------------|-----------------|-------|--|

| BTSEE           | _                                     | —                                | BTOEE           | DFN8EE           | CRC16EE          | CRC5EE          | PIDEE |  |

| bit 7           |                                       |                                  |                 |                  |                  |                 | bit 0 |  |

|                 |                                       |                                  |                 |                  |                  |                 |       |  |

| Legend:         |                                       |                                  |                 |                  |                  |                 |       |  |

| R = Readable    | bit                                   | W = Writable                     | bit             | U = Unimpler     | mented bit, read | l as '0'        |       |  |

| -n = Value at P | POR                                   | '1' = Bit is set                 |                 | '0' = Bit is cle | ared             | x = Bit is unkn | own   |  |

|                 |                                       |                                  |                 |                  |                  |                 |       |  |

| bit 7           | BTSEE: Bit S                          | tuff Error Interr                | upt Enable bit  | t                |                  |                 |       |  |

|                 |                                       | rror interrupt ei                |                 |                  |                  |                 |       |  |

|                 |                                       | rror interrupt di                |                 |                  |                  |                 |       |  |

| bit 6-5         | Unimplemen                            | ted: Read as '                   | 0'              |                  |                  |                 |       |  |

| bit 4           | BTOEE: Bus                            | Turnaround Ti                    | me-out Error I  | nterrupt Enable  | e bit            |                 |       |  |

|                 |                                       | round time-out                   |                 |                  |                  |                 |       |  |

|                 | 0 = Bus turna                         | round time-out                   | error interrup  | t disabled       |                  |                 |       |  |

| bit 3           | DFN8EE: Dat                           | a Field Size Ei                  | ror Interrupt E | Enable bit       |                  |                 |       |  |

|                 |                                       | size error inter                 |                 |                  |                  |                 |       |  |

|                 | 0 = Data field                        | size error inter                 | rrupt disabled  |                  |                  |                 |       |  |

| bit 2           | CRC16EE: C                            | RC16 Failure I                   | nterrupt Enab   | le bit           |                  |                 |       |  |

|                 |                                       | ilure interrupt                  |                 |                  |                  |                 |       |  |

|                 |                                       | ilure interrupt                  |                 |                  |                  |                 |       |  |

| bit 1           |                                       | C5 Host Error                    | •               | ole bit          |                  |                 |       |  |

|                 | 1 = CRC5 host error interrupt enabled |                                  |                 |                  |                  |                 |       |  |

|                 |                                       | st error interrup                |                 |                  |                  |                 |       |  |

| bit 0           |                                       | Check Failure I                  | •               | e bit            |                  |                 |       |  |

|                 |                                       | <pre>&lt; failure interru </pre> |                 |                  |                  |                 |       |  |

|                 |                                       | k failure interru                | pruisabled      |                  |                  |                 |       |  |

|                 |                                       |                                  |                 |                  |                  |                 |       |  |

## REGISTER 18-5: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| R/P-1                                                                    | U-0                                              | U-0                                                                         | U-0 | U-0               | R/P-0           | R/P-1      | U-0   |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------|-----|-------------------|-----------------|------------|-------|--|--|--|

| MCLRE                                                                    | —                                                | —                                                                           | —   | —                 | LPT1OSC         | PBADEN     | —     |  |  |  |

| bit 7                                                                    |                                                  |                                                                             |     |                   |                 |            | bit 0 |  |  |  |

|                                                                          |                                                  |                                                                             |     |                   |                 |            |       |  |  |  |

| Legend:                                                                  |                                                  |                                                                             |     |                   |                 |            |       |  |  |  |

| R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0' |                                                  |                                                                             |     |                   |                 |            |       |  |  |  |

| -n = Value wh                                                            | en device is unp                                 | programmed                                                                  |     | u = Unchang       | ed from progran | nmed state |       |  |  |  |

|                                                                          |                                                  |                                                                             |     |                   |                 |            |       |  |  |  |

| bit 7                                                                    | MCLRE: MCL                                       | R Pin Enable                                                                | bit |                   |                 |            |       |  |  |  |

|                                                                          |                                                  | enabled, RA5                                                                | ·   |                   |                 |            |       |  |  |  |

|                                                                          | •                                                | t pin enabled, N                                                            | •   | bled              |                 |            |       |  |  |  |

| bit 6-3                                                                  | Unimplemented: Read as '0'                       |                                                                             |     |                   |                 |            |       |  |  |  |

| bit 2                                                                    | LPT1OSC: Low-Power Timer1 Oscillator Enable bit  |                                                                             |     |                   |                 |            |       |  |  |  |

|                                                                          | 1 = Timer1 configured for low-power operation    |                                                                             |     |                   |                 |            |       |  |  |  |

|                                                                          | 0 = Timer1 configured for higher power operation |                                                                             |     |                   |                 |            |       |  |  |  |

| bit 1                                                                    |                                                  | ORTB A/D Enat                                                               |     |                   |                 |            |       |  |  |  |

|                                                                          | •                                                | (Affects ADCON1 Reset state. ADCON1 controls PORTB<4:0> pin configuration.) |     |                   |                 |            |       |  |  |  |

|                                                                          |                                                  | •                                                                           | •   | • •               | annels on Rese  | t          |       |  |  |  |

|                                                                          |                                                  | 4:0> pins are co                                                            | •   | ligital I/O on Re | eset            |            |       |  |  |  |

| bit 0                                                                    | Unimplemen                                       | ted: Read as '                                                              | 0'  |                   |                 |            |       |  |  |  |

|                                                                          |                                                  |                                                                             |     |                   |                 |            |       |  |  |  |

## REGISTER 18-7: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-1 | R/C-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | _   | —   | —   | CP1   | CP0   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                   |                   |                                     |

|---------------------------|-------------------|-------------------------------------|

| R = Readable bit          | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is | unprogrammed      | u = Unchanged from programmed state |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | CP1: Code Protection bit                                                                                                                     |

|         | <ul><li>1 = Block 1 (002000-003FFFh) is not code-protected</li><li>0 = Block 1 (002000-003FFFh) is code-protected</li></ul>                  |

| bit 0   | CP0: Code Protection bit                                                                                                                     |

|         | 1 = Block 0 (000800-001FFFh) or (001000-001FFFh) is not code-protected<br>0 = Block 0 (000800-001FFFh) or (001000-001FFFh) is code-protected |

## REGISTER 18-8: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| U-0   | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| —     | СРВ   | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                  |                   |                                     |

|--------------------------|-------------------|-------------------------------------|

| R = Readable bit         | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device i | s unprogrammed    | u = Unchanged from programmed state |

| DIT /   | Unimplemented: Read as 10                                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | CPB: Boot Block Code Protection bit                                                                                                                |

|         | 1 = Boot block (000000-0007FFh) or (000000-000FFFh) is not code-protected<br>0 = Boot block (000000-0007FFh) or (000000-000FFFh) is code-protected |

| bit 5-0 | Unimplemented: Read as '0'                                                                                                                         |

|         |                                                                                                                                                    |

| DAW                           | Decimal A                                                                    | djust W Regis             | ter               | DECF                                       | Decrement                     | f                                 |                |

|-------------------------------|------------------------------------------------------------------------------|---------------------------|-------------------|--------------------------------------------|-------------------------------|-----------------------------------|----------------|

| Syntax:                       | DAW                                                                          |                           |                   | Syntax:                                    | DECF f{,c                     | l {,a}}                           |                |

| Operands:                     | None                                                                         |                           |                   | Operands:                                  | $0 \leq f \leq 255$           |                                   |                |

| Operation:                    | lf [W<3:0>                                                                   | > 9] or [DC = 1           | ] then,           |                                            | d ∈ [0,1]                     |                                   |                |

|                               | , ,                                                                          | $6 \rightarrow W < 3:0>;$ |                   | <b>o</b> "                                 | a ∈ [0,1]                     |                                   |                |

|                               | else,<br>(W<3:0>) –                                                          | × ₩/<3·0>                 |                   | Operation:                                 | $(f) - 1 \rightarrow de$      |                                   |                |

|                               | (11 (0.02)) =                                                                | 7 10 30.02                |                   | Status Affected:                           | C, DC, N, C                   | DV, Z                             |                |

|                               |                                                                              | + DC > 9] or [C           |                   | Encoding:                                  | 0000                          | 01da ff                           | ff ffff        |

|                               | · · ·                                                                        | $6 + DC \rightarrow W <$  | 7:4>;             | Description:                               |                               | register 'f'. If                  |                |

|                               | else,<br>(W<7 <sup>.</sup> 4>) +                                             | $DC \rightarrow W < 7:4$  | >                 |                                            |                               | red in W. If 'd<br>red back in re |                |

| Status Affected:              | C C                                                                          | 50 / 11 / 11              |                   |                                            | (default).                    |                                   | gister i       |

| Encoding: 0000 0000 0000 0111 |                                                                              |                           | Ìf 'a' is '0', tl | If 'a' is '0', the Access Bank is selected |                               |                                   |                |

|                               |                                                                              |                           |                   |                                            |                               | ed to select the                  |                |

| Description:                  | DAW adjusts the 8-bit value in W, resulting from the earlier addition of two |                           |                   |                                            | GPR bank (<br>If 'a' is '0' a | · /                               | ed instruction |

|                               | variables (each in packed BCD format)<br>and produces a correct packed BCD   |                           |                   |                                            |                               | ction operates                    |                |

|                               |                                                                              |                           |                   |                                            | _iteral Offset                | 0                                 |                |

|                               | result.                                                                      |                           |                   |                                            |                               | ever f ≤ 95 (5<br>.2.3 "Byte-Oı   | ,              |

| Words:                        | 1                                                                            |                           |                   |                                            |                               | •                                 | in Indexed     |

| Cycles:                       | 1                                                                            |                           |                   |                                            | Literal Offs                  | et Mode" for                      | details.       |

| Q Cycle Activity:             |                                                                              |                           |                   | Words:                                     | 1                             |                                   |                |

| Q1                            | Q2                                                                           | Q3                        | Q4                | Cycles:                                    | 1                             |                                   |                |

| Decode                        | Read<br>register W                                                           | Process<br>Data           | Write<br>W        | Q Cycle Activity                           | :                             |                                   |                |

|                               | register w                                                                   | Dala                      | vv                | Q1                                         | Q2                            | Q3                                | Q4             |

| Example 1:                    | DAW                                                                          |                           |                   | Decode                                     | Read                          | Process                           | Write to       |

| Before Instru                 |                                                                              |                           |                   |                                            | register 'f'                  | Data                              | destination    |

| W                             | = A5h                                                                        |                           |                   |                                            |                               |                                   |                |

| C<br>DC                       | = 0<br>= 0                                                                   |                           |                   | Example:                                   |                               | CNT, 1, C                         | )              |

| After Instruct                | 0                                                                            |                           |                   | Before Instr                               |                               |                                   |                |

| W                             | = 05h                                                                        |                           |                   | CNT<br>Z                                   | = 01h<br>= 0                  |                                   |                |

| C<br>DC                       | = 1<br>= 0                                                                   |                           |                   | After Instruc                              |                               |                                   |                |

| Example 2:                    |                                                                              |                           |                   | CNT<br>Z                                   | = 00h<br>= 1                  |                                   |                |

| Before Instru                 | ction                                                                        |                           |                   | <i>L</i>                                   | •                             |                                   |                |

| W                             | = CEh                                                                        |                           |                   |                                            |                               |                                   |                |

| C<br>DC                       | = 0<br>= 0                                                                   |                           |                   |                                            |                               |                                   |                |

| After Instruct                | •                                                                            |                           |                   |                                            |                               |                                   |                |

| W                             | = 34h                                                                        |                           |                   |                                            |                               |                                   |                |

| C<br>DC                       | = 1<br>= 0                                                                   |                           |                   |                                            |                               |                                   |                |

| 50                            | Ū                                                                            |                           |                   |                                            |                               |                                   |                |

| INCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SZ                     | Increment                                                                          | Increment f, Skip if 0                            |                      |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------|---------------------------------------------------|----------------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ax:                    | INCFSZ f                                                                           | {,d {,a}}                                         |                      |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ands:                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ | d ∈ [0,1]                                         |                      |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ation:                 | .,                                                                                 | (f) + 1 $\rightarrow$ dest,<br>skip if result = 0 |                      |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | s Affected:            | None                                                                               |                                                   |                      |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ding:                  | 0011                                                                               | 11da ffi                                          | ff ffff              |  |  |  |  |

| Description:<br>The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. (default)<br>If the result is '0', the next instruction,<br>which is already fetched, is discarded<br>and a NOP is executed instead, making<br>it a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See<br>Section 19.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                        |                                                                                    |                                                   |                      |  |  |  |  |

| Mara                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        | 1                                                                                  |                                                   | actails.             |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        | -                                                                                  |                                                   |                      |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ycle Activity:         | •                                                                                  | cles if skip and<br>2-word instruc                |                      |  |  |  |  |

| QU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q1                     | Q2                                                                                 | Q3                                                | Q4                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Decode                 | Read<br>register 'f'                                                               | Process<br>Data                                   | Write to destination |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ip:                    |                                                                                    |                                                   |                      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q1                     | Q2                                                                                 | Q3                                                | Q4                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No                     | No                                                                                 | No                                                | No                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | operation              | operation                                                                          | operation                                         | operation            |  |  |  |  |

| It sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                        | d by 2-word ins                                                                    |                                                   | <i></i>              |  |  |  |  |