Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | UART/USART, USB                                                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 23                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

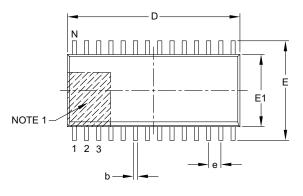

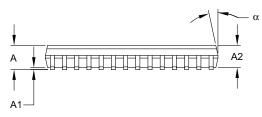

| Mounting Type              | Surface Mount                                                               |

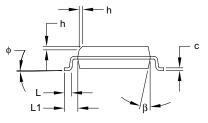

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2450t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mnufacture of development systems is ISO 9001:2000 certified.

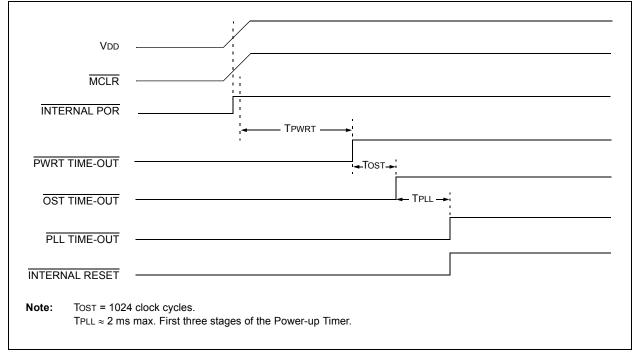

#### FIGURE 4-7: TIME-OUT SEQUENCE ON POR w/PLL ENABLED (MCLR TIED TO VDD)

#### 5.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by user software or a Power-on Reset.

#### 5.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. Each stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST   | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|--------------|---------------------------------------------------------|

|      | •            |                                                         |

| SUB1 | •            |                                                         |

|      | RETURN, FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

### 5.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET, W<br>TABLE |

|-------|--------------|--------------------|

|       |              | IADDE              |

| ORG   | nn00h        |                    |

| TABLE | ADDWF        | PCL                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | •            |                    |

|       | •            |                    |

|       | •            |                    |

#### 5.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

#### 5.3.6 STATUS REGISTER

The STATUS register, shown in Register 5-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu'). It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in Table 19-2 and Table 19-3.

Note: The C and DC bits operate as the Borrow and Digit Borrow bits, respectively, in subtraction.

| U-0                 | U-0                                      | U-0                          | R/W-x           | R/W-x              | R/W-x            | R/W-x             | R/W-x            |

|---------------------|------------------------------------------|------------------------------|-----------------|--------------------|------------------|-------------------|------------------|

| _                   | _                                        | —                            | N               | OV                 | Z                | DC <sup>(1)</sup> | C <sup>(2)</sup> |

| bit 7               | •                                        |                              |                 |                    |                  | -<br>-            | bit 0            |

| 1                   |                                          |                              |                 |                    |                  |                   |                  |

| Legend:<br>R = Read | labla bit                                | W = Writable                 | hit             | II – Unimplo       | mented bit, rea  | d ac '0'          |                  |

|                     | e at POR                                 | '1' = Bit is set             |                 | '0' = Bit is cle   |                  | x = Bit is unkr   | NOW/D            |

|                     |                                          | 1 - Dit 13 301               |                 |                    |                  |                   |                  |

| bit 7-5             | Unimplemer                               | nted: Read as '              | 0'              |                    |                  |                   |                  |

| bit 4               | N: Negative I                            | bit                          |                 |                    |                  |                   |                  |

|                     |                                          | •                            | rithmetic (2's  | complement). I     | t indicates whe  | ther the result w | /as              |

|                     | negative (AL                             | ,                            |                 |                    |                  |                   |                  |

|                     | 1 = Result wa<br>0 = Result wa           | •                            |                 |                    |                  |                   |                  |

| bit 3               | OV: Overflow                             | •                            |                 |                    |                  |                   |                  |

|                     |                                          |                              | rithmetic (2's  | complement). I     | t indicates an o | verflow of the 7  | -bit             |

|                     | -                                        |                              | •               | -                  | to change state  |                   |                  |

|                     | 1 = Overflow<br>0 = No overfl            |                              | gned arithme    | tic (in this arith | metic operation  | )                 |                  |

| bit 2               | 0 – No overní<br><b>Z:</b> Zero bit      |                              |                 |                    |                  |                   |                  |

|                     |                                          | It of an arithme             | tic or logic on | eration is zero    |                  |                   |                  |

|                     |                                          | It of an arithme             |                 |                    | ero              |                   |                  |

| bit 1               | DC: Digit Car                            | rry/Borrow bit <sup>(1</sup> | )               |                    |                  |                   |                  |

|                     |                                          | DDLW, SUBLW a                |                 |                    |                  |                   |                  |

|                     |                                          | out from the 4th             |                 |                    | curred           |                   |                  |

| bit 0               | 0 = No carry-<br><b>C:</b> Carry/Bor     | out from the 4t              | n Iow-order D   | it of the result   |                  |                   |                  |

| DILU                | ,                                        | IDW DIL<br>IDDLW, SUBLW 8    | and SUBWF ins   | structions:        |                  |                   |                  |

|                     |                                          | out from the Mo              |                 |                    | occurred         |                   |                  |

|                     |                                          | out from the M               |                 |                    |                  |                   |                  |

| Note 1:             | ,                                        |                              |                 |                    |                  |                   |                  |

|                     | operand. For rotat                       |                              |                 |                    |                  |                   | -                |

| 2:                  | For borrow, the po<br>operand. For rotat |                              |                 |                    |                  |                   |                  |

|                     | source register.                         | .• (nnr, klr) III            |                 |                    |                  | ingri or iow-orde |                  |

#### REGISTER 5-2: STATUS REGISTER

| R/W-0           | U-0                                                                                                                 | R/W-0              | U-0           | U-0              | R/W-0            | U-0             | U-0   |

|-----------------|---------------------------------------------------------------------------------------------------------------------|--------------------|---------------|------------------|------------------|-----------------|-------|

| OSCFIE          | —                                                                                                                   | USBIE              | —             | —                | HLVDIE           | —               | —     |

| bit 7           |                                                                                                                     |                    |               |                  |                  |                 | bit 0 |

|                 |                                                                                                                     |                    |               |                  |                  |                 |       |

| Legend:         |                                                                                                                     |                    |               |                  |                  |                 |       |

| R = Readable    | bit                                                                                                                 | W = Writable       | bit           | U = Unimpler     | mented bit, read | as '0'          |       |

| -n = Value at F | POR                                                                                                                 | '1' = Bit is set   |               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

| bit 7           |                                                                                                                     | illator Fail Inter | rupt Enable b | vit              |                  |                 |       |

|                 | <ul><li>1 = Enabled</li><li>0 = Disabled</li></ul>                                                                  |                    |               |                  |                  |                 |       |

| bit 6           | Unimplemen                                                                                                          | ted: Read as '     | כי            |                  |                  |                 |       |

| bit 5           | USBIE: USB                                                                                                          | Interrupt Enabl    | e bit         |                  |                  |                 |       |

|                 | 1 = Enabled<br>0 = Disabled                                                                                         |                    |               |                  |                  |                 |       |

| bit 4-3         | Unimplemen                                                                                                          | ted: Read as '     | D'            |                  |                  |                 |       |

| bit 2           | <ul> <li>HLVDIE: High/Low-Voltage Detect Interrupt Enable bit</li> <li>1 = Enabled</li> <li>0 = Disabled</li> </ul> |                    |               |                  |                  |                 |       |

| bit 1-0         | Unimplemen                                                                                                          | ted: Read as '     | כי            |                  |                  |                 |       |

|                 |                                                                                                                     |                    |               |                  |                  |                 |       |

#### REGISTER 8-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| Pin | Function | TRIS<br>Setting | I/O | I/О Туре | Description          |

|-----|----------|-----------------|-----|----------|----------------------|

| RD0 | RD0      | 0               | OUT | DIG      | LATD<0> data output. |

|     |          | 1               | IN  | ST       | PORTD<0> data input. |

| RD1 | RD1      | 0               | OUT | DIG      | LATD<1> data output. |

|     |          | 1               | IN  | ST       | PORTD<1> data input. |

| RD2 | RD2      | 0               | OUT | DIG      | LATD<2> data output. |

|     |          | 1               | IN  | ST       | PORTD<2> data input. |

| RD3 | RD3      | 0               | OUT | DIG      | LATD<3> data output. |

|     |          | 1               | IN  | ST       | PORTD<3> data input. |

| RD4 | RD4      | 0               | OUT | DIG      | LATD<4> data output. |

|     |          | 1               | IN  | ST       | PORTD<4> data input. |

| RD5 | RD5      | 0               | OUT | DIG      | LATD<5> data output  |

|     |          | 1               | IN  | ST       | PORTD<5> data input  |

| RD6 | RD6      | 0               | OUT | DIG      | LATD<6> data output. |

|     |          | 1               | IN  | ST       | PORTD<6> data input. |

| RD7 | RD7      | 0               | OUT | DIG      | LATD<7> data output. |

|     |          | 1               | IN  | ST       | PORTD<7> data input. |

#### TABLE 9-7: PORTD I/O SUMMARY

**Legend:** OUT = Output, IN = Input, DIG = Digital Output, ST = Schmitt Buffer Input

| Name                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------------------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------------------|

| PORTD <sup>(1)</sup> | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | 51                          |

| LATD <sup>(1)</sup>  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 51                          |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 51                          |

Note 1: These registers and/or bits are unimplemented on 28-pin devices.

#### 10.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS2:T0PS0 bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256, in power-of-2 increments, are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

#### 10.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

#### 10.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

TABLE 10-1:REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7                                                    | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|--------|----------------------------------------------------------|-----------------------|--------|--------|--------|--------|--------|--------|-----------------------------|

| TMR0L  | Timer0 Register Low Byte                                 |                       |        |        |        |        |        | 50     |                             |

| TMR0H  | Timer0 Register High Byte                                |                       |        |        |        |        |        |        | 50                          |

| INTCON | GIE/GIEH PEIE/GIEL TMROIE INTOIE RBIE TMROIF INTOIF RBIF |                       |        |        |        |        |        | RBIF   | 49                          |

| T0CON  | TMR0ON                                                   | T08BIT                | TOCS   | T0SE   | PSA    | T0PS2  | T0PS1  | T0PS0  | 50                          |

| TRISA  | —                                                        | TRISA6 <sup>(1)</sup> | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 51                          |

Legend: — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

#### 11.7 Considerations in Asynchronous Counter Mode

Following a Timer1 interrupt and an update to the TMR1 registers, the Timer1 module uses a falling edge on its clock source to trigger the next register update on the rising edge. If the update is completed after the clock input has fallen, the next rising edge will not be counted.

If the application can reliably update TMR1 before the timer input goes low, no additional action is needed. Otherwise, an adjusted update can be performed

following a later Timer1 increment. This can be done by monitoring TMR1L within the interrupt routine until it increments, and then updating the TMR1H:TMR1L register pair while the clock is low, or one-half of the period of the clock source. Assuming that Timer1 is being used as a Real-Time Clock, the clock source is a 32.768 kHz crystal oscillator. In this case, one-half period of the clock is 15.25  $\mu$ s.

The Real-Time Clock application code in Example 11-1 shows a typical ISR for Timer1, as well as the optional code required if the update cannot be done reliably within the required interval.

EXAMPLE 11-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                                               |

|---------|--------|--------------|---------------------------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                                       |

|         | CLRF   | TMR1L        |                                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator                 |

|         | CLRF   | secs         | ; Initialize timekeeping registers                            |

|         | CLRF   | mins         | ;                                                             |

|         | MOVLW  | .12          |                                                               |

|         | MOVWF  | hours        |                                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                                     |

|         | RETURN |              |                                                               |

| RTCisr  |        |              |                                                               |

|         |        |              | ; Insert the next 4 lines of code when TMR1                   |

|         |        |              | ; cannot be reliably updated before clock pulse goes low      |

|         | BTFSC  | TMR1L,0      | ; wait for TMR1L to become clear                              |

|         | BRA    | \$-2         | ; (may already be clear)                                      |

|         | BTFSS  | TMR1L,0      | ; wait for TMR1L to become set                                |

|         | BRA    | \$-2         | ; TMR1 has just incremented                                   |

|         |        |              | ; If TMR1 update can be completed before clock pulse goes low |

|         |        |              | ; Start ISR here                                              |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                                        |

|         | INCF   | secs, F      | ; Increment seconds                                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                         |

|         | CPFSGT | secs         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | secs         | ; Clear seconds                                               |

|         | INCF   | mins, F      | ; Increment minutes                                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                         |

|         | CPFSGT | mins         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | mins         | ; clear minutes                                               |

|         | INCF   | hours, F     | ; Increment hours                                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                           |

|         | CPFSGT | hours        |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | hours        | ; Reset hours                                                 |

|         | RETURN |              | ; Done                                                        |

|         |        |              |                                                               |

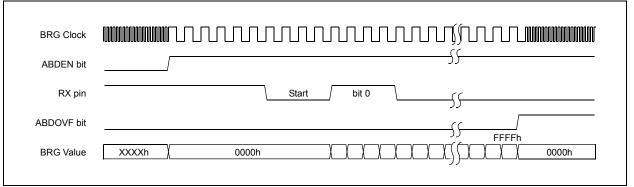

#### 15.1 Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free-running timer. In Asynchronous mode, bits BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 15-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 15-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 15-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 15-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH:SPBRG registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

### 15.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

#### 15.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

| Co   | onfiguration B | its  |                     | David Data Carmula |

|------|----------------|------|---------------------|--------------------|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Baud Rate Formula  |

| 0    | 0              | 0    | 8-Bit/Asynchronous  | Fosc/[64 (n + 1)]  |

| 0    | 0              | 1    | 8-Bit/Asynchronous  |                    |

| 0    | 1              | 0    | 16-Bit/Asynchronous | Fosc/[16 (n + 1)]  |

| 0    | 1              | 1    | 16-Bit/Asynchronous |                    |

| 1    | 0              | X    | 8-Bit/Synchronous   | Fosc/[4 (n + 1)]   |

| 1    | 1              | х    | 16-Bit/Synchronous  |                    |

**Legend:** x = Don't care, n = Value of SPBRGH:SPBRG register pair

| BRG Value               | XXXXh         | 0000h   |                                                                                                   | 001Ch        |

|-------------------------|---------------|---------|---------------------------------------------------------------------------------------------------|--------------|

| RX pin                  |               | Start   | _Edge #1 _Edge #2 _Edge #3 _Edge #4<br>bit 0 _ bit 1 _ bit 2 _ bit 3 _ bit 4 _ bit 5 _ bit 6 _ bi | Edge #5      |

| RG Clock                |               | huuuuuu | ,                                                                                                 |              |

| ABDEN bit               | Set by User — |         |                                                                                                   | Auto-Cleared |

| RCIF bit<br>(Interrupt) |               |         |                                                                                                   |              |

| Read<br>RCREG           |               |         | -<br>                                                                                             |              |

| SPBRG                   |               |         | · XXXXh                                                                                           | ) 1Ch        |

| SPBRGH                  |               |         | XXXXh                                                                                             | 00h          |

#### FIGURE 15-1: AUTOMATIC BAUD RATE CALCULATION

#### FIGURE 15-2: BRG OVERFLOW SEQUENCE

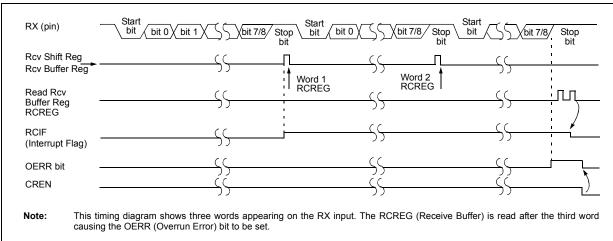

#### FIGURE 15-7: ASYNCHRONOUS RECEPTION

#### TABLE 15-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name    | Bit 7    | Bit 6        | Bit 5       | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|----------|--------------|-------------|-------------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH | PEIE/GIEL    | TMR0IE      | INT0IE      | RBIE  | TMR0IF | INT0IF | RBIF   | 49                          |

| PIR1    | —        | ADIF         | RCIF        | TXIF        | —     | CCP1IF | TMR2IF | TMR1IF | 51                          |

| PIE1    | _        | ADIE         | RCIE        | TXIE        | —     | CCP1IE | TMR2IE | TMR1IE | 51                          |

| IPR1    | —        | ADIP         | RCIP        | TXIP        | —     | CCP1IP | TMR2IP | TMR1IP | 51                          |

| RCSTA   | SPEN     | RX9          | SREN        | CREN        | ADDEN | FERR   | OERR   | RX9D   | 51                          |

| RCREG   | EUSART F | Receive Regi | ster        |             |       |        |        |        | 50                          |

| TXSTA   | CSRC     | TX9          | TXEN        | SYNC        | SENDB | BRGH   | TRMT   | TX9D   | 51                          |

| BAUDCON | ABDOVF   | RCIDL        | _           | SCKP        | BRG16 | —      | WUE    | ABDEN  | 51                          |

| SPBRGH  | EUSART E | aud Rate G   | enerator Re | gister High | Byte  |        |        |        | 50                          |

| SPBRG   | EUSART B | aud Rate G   | enerator Re | gister Low  | Byte  |        |        |        | 50                          |

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

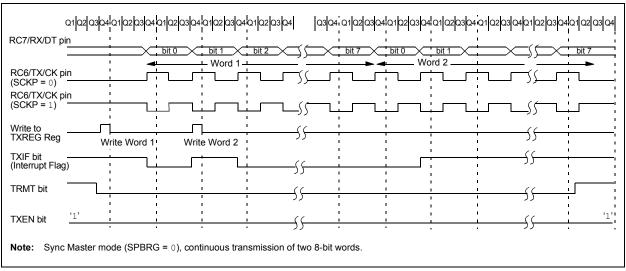

#### 15.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the TX and RX pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCON<4>). Setting SCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 15.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 15-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG register is empty and the TXIF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXIE (PIE1<4>). TXIF is set regardless of the state of enable bit, TXIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user must poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 15-11: SYNCHRONOUS TRANSMISSION

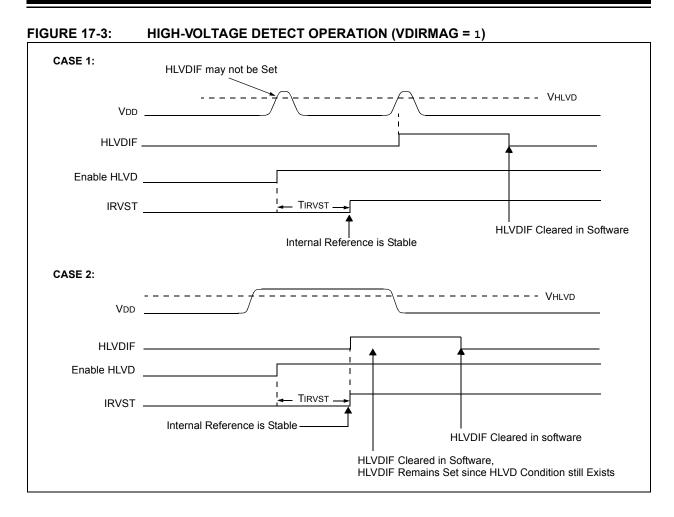

#### 17.5 Applications

In many applications, the ability to detect a drop below or rise above a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

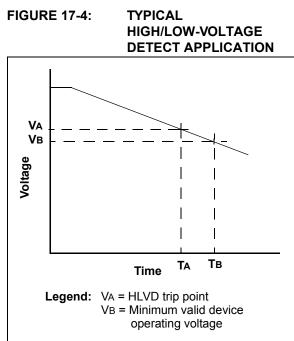

For general battery applications, Figure 17-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

### 18.5 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other  $\text{PIC}^{\textcircled{R}}$  microcontrollers.

The user program memory is divided into three blocks. One of these is a boot block of 1 or 2 Kbytes. The remainder of the memory is divided into two blocks on binary boundaries. Each of the three blocks has three code protection bits associated with them. They are:

- Code-Protect bit (CPx)

- Write-Protect bit (WRTx)

- External Block Table Read bit (EBTRx)

Figure 18-5 shows the program memory organization for 24 and 32-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 18-3.

#### FIGURE 18-5: CODE-PROTECTED PROGRAM MEMORY FOR PIC18F2450/4450

| MEMORY SIZE/DEVICE<br>16 Kbytes<br>(PIC18F2450/4450) | Address<br>Range              | Block Code Protection<br>Controlled By: |

|------------------------------------------------------|-------------------------------|-----------------------------------------|

| Boot Block                                           | 000000h<br>0007FFh<br>000FFFh | CPB, WRTB, EBTRB                        |

| Block 0                                              | 001000h<br>001FFFh            | CP0, WRT0, EBTR0                        |

| Block 1                                              | 002000h<br>003FFFh            | CP1, WRT1, EBTR1                        |

| Unimplemented<br>Read '0's                           |                               |                                         |

| Unimplemented<br>Read '0's                           |                               |                                         |

| Unimplemented<br>Read '0's                           |                               | (Unimplemented Memory Space)            |

|                                                      | 1FFFFFh                       |                                         |

#### TABLE 18-3: SUMMARY OF CODE PROTECTION REGISTERS

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 300008h | CONFIG5L | _     |       | _     |       |       | _     | CP1   | CP0   |

| 300009h | CONFIG5H | _     | CPB   | _     | _     | _     | _     | _     | —     |

| 30000Ah | CONFIG6L | _     | —     | _     | _     | _     | _     | WRT1  | WRT0  |

| 30000Bh | CONFIG6H | _     | WRTB  | WRTC  | —     | —     | _     | _     | —     |

| 30000Ch | CONFIG7L | _     | —     | _     | _     | _     | _     | EBTR1 | EBTR0 |

| 30000Dh | CONFIG7H | _     | EBTRB | _     | —     | —     |       |       |       |

Legend: Shaded cells are unimplemented.

| сом   | IF               | Compleme                                                                                                                                                                                  | ent f     |                                                                                                                                                                          | CPF         | SEQ                     | Compare f                                                                                                                                                                                                                               | with W, Skip                                                                                                                                 | if f = W                                                                                                                                                                                    |

|-------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synta | ax:              | COMF f                                                                                                                                                                                    | {,d {,a}} |                                                                                                                                                                          | Synt        | ax:                     | CPFSEQ                                                                                                                                                                                                                                  | f {,a}                                                                                                                                       |                                                                                                                                                                                             |

| Oper  | ands:            | 0 ≤ f ≤ 255                                                                                                                                                                               |           |                                                                                                                                                                          | Oper        | rands:                  | $0 \leq f \leq 255$                                                                                                                                                                                                                     |                                                                                                                                              |                                                                                                                                                                                             |

|       |                  | d ∈ [0,1]                                                                                                                                                                                 |           |                                                                                                                                                                          |             |                         | a ∈ [0,1]                                                                                                                                                                                                                               |                                                                                                                                              |                                                                                                                                                                                             |

|       |                  | a ∈ [0,1]                                                                                                                                                                                 |           |                                                                                                                                                                          | Oper        | ration:                 | (f) – (W),                                                                                                                                                                                                                              |                                                                                                                                              |                                                                                                                                                                                             |

| Oper  | ation:           | $(\overline{f}) \rightarrow dest$                                                                                                                                                         |           |                                                                                                                                                                          |             |                         | skip if (f) = (<br>(unsigned c                                                                                                                                                                                                          | · /                                                                                                                                          |                                                                                                                                                                                             |

| Statu | s Affected:      | N, Z                                                                                                                                                                                      |           |                                                                                                                                                                          | Statu       | us Affected:            | None                                                                                                                                                                                                                                    | . ,                                                                                                                                          |                                                                                                                                                                                             |

| Enco  | ding:            | 0001                                                                                                                                                                                      | 11da ff:  | ff ffff                                                                                                                                                                  |             | oding:                  | 0110                                                                                                                                                                                                                                    | 001a ffi                                                                                                                                     | f ffff                                                                                                                                                                                      |

| Word  |                  | complement<br>stored in W<br>stored back<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank<br>If 'a' is '0' a<br>set is enablin<br>in Indexed<br>mode when<br>Section 19<br>Bit-Oriente |           | , the result is<br>e result is<br>(default).<br>hk is selected.<br>d to select the<br>ed instruction<br>operates<br>addressing<br>Fh). See<br>iented and<br>s in Indexed | -           | cription:               | Compares t<br>location 'f t<br>performing<br>If 'f' = W, th<br>discarded a<br>instruction.<br>If 'a' is '0', tl<br>If 'a' is '0', tl<br>GPR bank (<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when<br><b>Section 19</b> | the contents of<br>o the contents<br>an unsigned s<br>en the fetched<br>ind a NOP is ex<br>king this a two<br>he Access Bar<br>he BSR is use | data memory<br>of W by<br>ubtraction.<br>instruction is<br>ecuted<br>cycle<br>hk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>addressing<br>Fh). See<br>ented and |

| ,     |                  | 1                                                                                                                                                                                         |           |                                                                                                                                                                          |             |                         | Literal Offs                                                                                                                                                                                                                            | set Mode" for                                                                                                                                | details.                                                                                                                                                                                    |

| QC    | ycle Activity:   |                                                                                                                                                                                           |           |                                                                                                                                                                          | Word        | ds:                     | 1                                                                                                                                                                                                                                       |                                                                                                                                              |                                                                                                                                                                                             |

|       | Q1               | Q2                                                                                                                                                                                        | Q3        | Q4                                                                                                                                                                       | Cycle       | es:                     | 1(2)                                                                                                                                                                                                                                    |                                                                                                                                              |                                                                                                                                                                                             |

|       | Decode           | Read                                                                                                                                                                                      | Process   | Write to                                                                                                                                                                 |             |                         | Note: 3 cy                                                                                                                                                                                                                              | cles if skip an                                                                                                                              | d followed                                                                                                                                                                                  |

|       |                  | register 'f'                                                                                                                                                                              | Data      | destination                                                                                                                                                              | l           |                         | by a                                                                                                                                                                                                                                    | a 2-word instru                                                                                                                              | iction.                                                                                                                                                                                     |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          | QC          | ycle Activity:          |                                                                                                                                                                                                                                         |                                                                                                                                              |                                                                                                                                                                                             |

| Exan  | nple:            | COMF                                                                                                                                                                                      | REG, 0, 0 |                                                                                                                                                                          |             | Q1                      | Q2                                                                                                                                                                                                                                      | Q3                                                                                                                                           | Q4                                                                                                                                                                                          |

|       | Before Instruct  | tion                                                                                                                                                                                      |           |                                                                                                                                                                          |             | Decode                  | Read                                                                                                                                                                                                                                    | Process                                                                                                                                      | No                                                                                                                                                                                          |

|       | REG              | = 13h                                                                                                                                                                                     |           |                                                                                                                                                                          |             |                         | register 'f'                                                                                                                                                                                                                            | Data                                                                                                                                         | operation                                                                                                                                                                                   |

|       | After Instructio |                                                                                                                                                                                           |           |                                                                                                                                                                          | lf sk       | •                       |                                                                                                                                                                                                                                         |                                                                                                                                              |                                                                                                                                                                                             |

|       | REG<br>W         | = 13h<br>= ECh                                                                                                                                                                            |           |                                                                                                                                                                          |             | Q1                      | Q2                                                                                                                                                                                                                                      | Q3                                                                                                                                           | Q4                                                                                                                                                                                          |

|       | ••               | Lon                                                                                                                                                                                       |           |                                                                                                                                                                          |             | No                      | No                                                                                                                                                                                                                                      | No                                                                                                                                           | No                                                                                                                                                                                          |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          | 16 - 1      | operation               | operation                                                                                                                                                                                                                               | operation                                                                                                                                    | operation                                                                                                                                                                                   |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          | IT SK       | kip and followe         | ,                                                                                                                                                                                                                                       |                                                                                                                                              | 04                                                                                                                                                                                          |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          |             | Q1<br>No                | Q2<br>No                                                                                                                                                                                                                                | Q3<br>No                                                                                                                                     | Q4<br>No                                                                                                                                                                                    |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          |             | operation               | operation                                                                                                                                                                                                                               | operation                                                                                                                                    | operation                                                                                                                                                                                   |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          |             | No                      | No                                                                                                                                                                                                                                      | No                                                                                                                                           | No                                                                                                                                                                                          |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          |             | operation               | operation                                                                                                                                                                                                                               | operation                                                                                                                                    | operation                                                                                                                                                                                   |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          | <u>Exar</u> | nple:<br>Before Instruc | HERE<br>NEQUAL<br>EQUAL                                                                                                                                                                                                                 | CPFSEQ REG<br>:<br>:                                                                                                                         | , 0                                                                                                                                                                                         |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          |             | PC Addr                 |                                                                                                                                                                                                                                         | RE                                                                                                                                           |                                                                                                                                                                                             |

|       |                  |                                                                                                                                                                                           |           |                                                                                                                                                                          |             | W                       | = ?                                                                                                                                                                                                                                     | 1/11                                                                                                                                         |                                                                                                                                                                                             |

| W                 | = | ?       |          |

|-------------------|---|---------|----------|

| REG               | = | ?       |          |

| After Instruction |   |         |          |

| If REG            | = | W;      |          |