Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

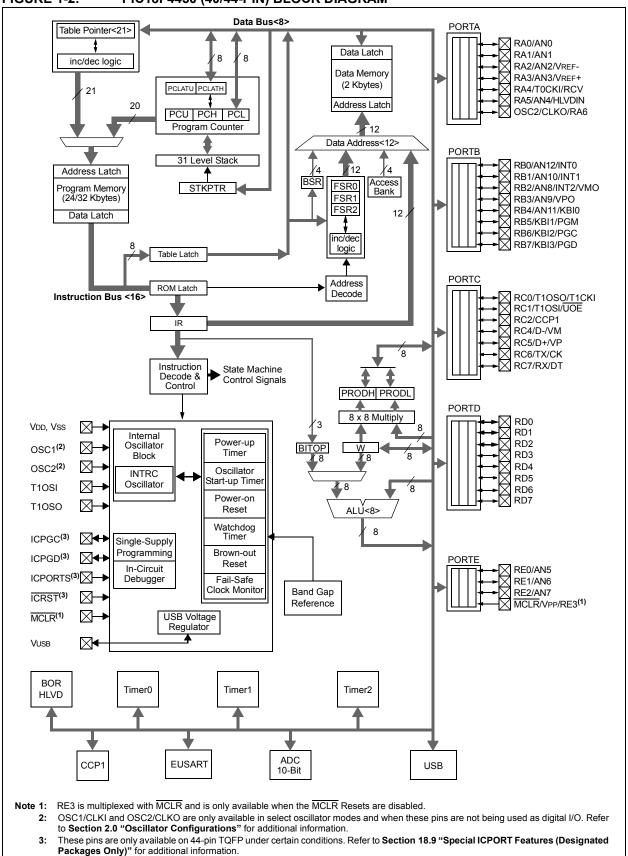

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | UART/USART, USB                                                            |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 13x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

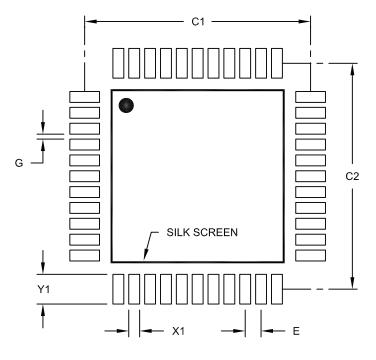

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4450-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                  | Pin Nu                     | mber  | Pin         | Duffer         |                                                                                            |  |  |

|----------------------------------|----------------------------|-------|-------------|----------------|--------------------------------------------------------------------------------------------|--|--|

| Pin Name                         | SPDIP,<br>SOIC             | QFN   | Ріп<br>Туре | Buffer<br>Type | Description                                                                                |  |  |

|                                  |                            |       |             |                | PORTC is a bidirectional I/O port.                                                         |  |  |

| RC0/T1OSO/T1CKI                  | 11                         | 8     |             |                |                                                                                            |  |  |

| RC0                              |                            | -     | I/O         | ST             | Digital I/O.                                                                               |  |  |

| T10S0                            |                            |       | 0           |                | Timer1 oscillator output.                                                                  |  |  |

| T1CKI                            |                            |       | I           | ST             | Timer1external clock input.                                                                |  |  |

| RC1/T1OSI/UOE                    | 12                         | 9     |             |                |                                                                                            |  |  |

| RC1                              | 12                         | 9     | I/O         | ST             | Digital I/O.                                                                               |  |  |

| TIOSI                            |                            |       | "U          | CMOS           | Timer1 oscillator input.                                                                   |  |  |

| UOE                              |                            |       | Ö           |                | External USB transceiver $\overline{OE}$ output.                                           |  |  |

|                                  | 10                         | 10    | 0           |                |                                                                                            |  |  |

| RC2/CCP1                         | 13                         | 10    |             | от             |                                                                                            |  |  |

| RC2                              |                            |       | I/O         | ST             | Digital I/O.                                                                               |  |  |

| CCP1                             |                            |       | I/O         | ST             | Capture 1 input/Compare 1 output/PWM1 output.                                              |  |  |

| RC4/D-/VM                        | 15                         | 12    |             |                |                                                                                            |  |  |

| RC4                              |                            |       | I           | TTL            | Digital input.                                                                             |  |  |

| D-                               |                            |       | I/O         | _              | USB differential minus line (input/output).                                                |  |  |

| VM                               |                            |       | Ι           | TTL            | External USB transceiver VM input.                                                         |  |  |

| RC5/D+/VP                        | 16                         | 13    |             |                |                                                                                            |  |  |

| RC5                              |                            |       | I           | TTL            | Digital input.                                                                             |  |  |

| D+                               |                            |       | I/O         | —              | USB differential plus line (input/output).                                                 |  |  |

| VP                               |                            |       | 0           | TTL            | External USB transceiver VP input.                                                         |  |  |

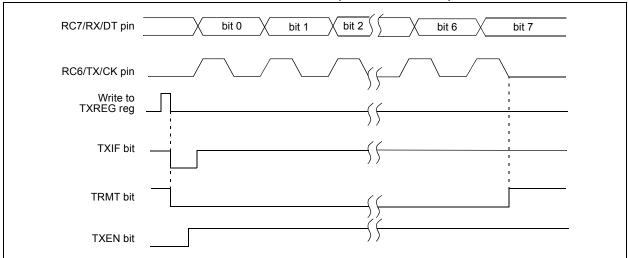

| RC6/TX/CK                        | 17                         | 14    |             |                |                                                                                            |  |  |

| RC6                              |                            |       | I/O         | ST             | Digital I/O.                                                                               |  |  |

| ТΧ                               |                            |       | 0           |                | EUSART asynchronous transmit.                                                              |  |  |

| СК                               |                            |       | I/O         | ST             | EUSART synchronous clock (see RX/DT).                                                      |  |  |

| RC7/RX/DT                        | 18                         | 15    |             |                | - , ,                                                                                      |  |  |

| RC7                              |                            | 10    | I/O         | ST             | Digital I/O.                                                                               |  |  |

| RX                               |                            |       | "U          | ST             | EUSART asynchronous receive.                                                               |  |  |

| DT                               |                            |       | I/O         | ST             | EUSART synchronous data (see TX/CK).                                                       |  |  |

| RE3                              | <u> </u>                   |       |             | _              | See MCLR/VPP/RE3 pin.                                                                      |  |  |

| VUSB                             | 14                         | 11    | Р           | —              | Internal USB 3.3V voltage regulator. Output, positive supply for internal USB transceiver. |  |  |

| Vss                              | 8, 19                      | 5, 16 | Р           |                | Ground reference for logic and I/O pins.                                                   |  |  |

| Vdd                              | 20                         | 17    | Р           | —              | Positive supply for logic and I/O pins.                                                    |  |  |

| Legend: TTL = TTL c<br>ST = Schm | compatible<br>nitt Trigger |       | /ith CM     | IOS level      | CMOS = CMOS compatible input or output                                                     |  |  |

Ρ

0 = Output = Power

| Pin Name             | Pi                   | n Num    | ber       | Pin    | Buffer  | Description                                  |  |  |  |  |

|----------------------|----------------------|----------|-----------|--------|---------|----------------------------------------------|--|--|--|--|

| Pin Name             | PDIP                 | QFN      | TQFP      | Туре   | Туре    | Description                                  |  |  |  |  |

|                      |                      |          |           |        |         | PORTA is a bidirectional I/O port.           |  |  |  |  |

| RA0/AN0              | 2                    | 19       | 19        |        |         |                                              |  |  |  |  |

| RA0                  |                      |          |           | I/O    | TTL     | Digital I/O.                                 |  |  |  |  |

| AN0                  |                      |          |           | I      | Analog  | Analog input 0.                              |  |  |  |  |

| RA1/AN1              | 3                    | 20       | 20        |        |         |                                              |  |  |  |  |

| RA1                  |                      |          |           | I/O    | TTL     | Digital I/O.                                 |  |  |  |  |

| AN1                  |                      |          |           | I      | Analog  | Analog input 1.                              |  |  |  |  |

| RA2/AN2/VREF-        | 4                    | 21       | 21        |        |         |                                              |  |  |  |  |

| RA2                  |                      |          |           | I/O    | TTL     | Digital I/O.                                 |  |  |  |  |

| AN2                  |                      |          |           | I      | Analog  | Analog input 2.                              |  |  |  |  |

| VREF-                |                      |          |           | I      | Analog  | A/D reference voltage (low) input.           |  |  |  |  |

| RA3/AN3/VREF+        | 5                    | 22       | 22        |        |         |                                              |  |  |  |  |

| RA3                  |                      |          |           | I/O    | TTL     | Digital I/O.                                 |  |  |  |  |

| AN3                  |                      |          |           |        | Analog  | Analog input 3.                              |  |  |  |  |

| VREF+                |                      |          |           | 1      | Analog  | A/D reference voltage (high) input.          |  |  |  |  |

| RA4/T0CKI/RCV<br>RA4 | 6                    | 23       | 23        | I/O    | ST      |                                              |  |  |  |  |

| T0CKI                |                      |          |           | 1/0    | ST      | Digital I/O.<br>Timer0 external clock input. |  |  |  |  |

| RCV                  |                      |          |           |        | TTL     | External USB transceiver RCV input.          |  |  |  |  |

| RA5/AN4/HLVDIN       | 7                    | 24       | 24        |        |         |                                              |  |  |  |  |

| RA5                  | '                    | 24       | 24        | I/O    | TTL     | Digital I/O.                                 |  |  |  |  |

| AN4                  |                      |          |           | 1      | Analog  | Analog input 4.                              |  |  |  |  |

| HLVDIN               |                      |          |           | Ì      | Analog  | High/Low-Voltage Detect input.               |  |  |  |  |

| RA6                  | _                    | _        | _         | _      | _       | See the OSC2/CLKO/RA6 pin.                   |  |  |  |  |

| Legend: TTL = TTL    | compat               | ible inp | ut        | 1      | C       | CMOS = CMOS compatible input or output       |  |  |  |  |

|                      | nitt Trig            | ger inpl | ut with C | MOS le | evels l | = Input                                      |  |  |  |  |

| O = Outp             | O = Output P = Power |          |           |        |         |                                              |  |  |  |  |

| TABLE 1-3: PIC18F4450 PINOUT I/O DESCRIPTIONS (CONTINUED) | TABLE 1-3: | PIC18F4450 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|-----------------------------------------------------------|------------|------------------------------------------------|

|-----------------------------------------------------------|------------|------------------------------------------------|

**Note 1:** These pins are No Connect unless the ICPRT Configuration bit is set. For NC/ICPORTS, the pin is No Connect unless ICPRT is set and the DEBUG Configuration bit is cleared.

# 2.0 OSCILLATOR CONFIGURATIONS

# 2.1 Overview

Devices in the PIC18F2450/4450 family incorporate a different oscillator and microcontroller clock system than the non-USB PIC18F devices. The addition of the USB module, with its unique requirements for a stable clock source, make it necessary to provide a separate clock source that is compliant with both USB low-speed and full-speed specifications.

To accommodate these requirements, PIC18F2450/ 4450 devices include a new clock branch to provide a 48 MHz clock for full-speed USB operation. Since it is driven from the primary clock source, an additional system of prescalers and postscalers has been added to accommodate a wide range of oscillator frequencies. An overview of the oscillator structure is shown in Figure 2-1.

Other oscillator features used in PIC18 enhanced microcontrollers, such as the internal RC oscillator and clock switching, remain the same. They are discussed later in this chapter.

# 2.1.1 OSCILLATOR CONTROL

The operation of the oscillator in PIC18F2450/4450 devices is controlled through two Configuration registers and two control registers. Configuration registers, CONFIG1L and CONFIG1H, select the oscillator mode and USB prescaler/postscaler options. As Configuration bits, these are set when the device is programmed and left in that configuration until the device is reprogrammed.

The OSCCON register (Register 2-1) selects the Active Clock mode; it is primarily used in controlling clock switching in power-managed modes. Its use is discussed in **Section 2.4.1** "**Oscillator Control Register**".

# 2.2 Oscillator Types

PIC18F2450/4450 devices can be operated in twelve distinct oscillator modes. In contrast with the non-USB PIC18 enhanced microcontrollers, four of these modes involve the use of two oscillator types at once. Users can program the FOSC3:FOSC0 Configuration bits to select one of these modes:

- 1. XT Crystal/Resonator

- 2. XTPLL Crystal/Resonator with PLL Enabled

- 3. HS High-Speed Crystal/Resonator

- 4. HSPLL High-Speed Crystal/Resonator with PLL Enabled

- 5. EC External Clock with Fosc/4 Output

- 6. ECIO External Clock with I/O on RA6

- 7. ECPLL External Clock with PLL Enabled and Fosc/4 Output on RA6

- 8. ECPIO External Clock with PLL Enabled, I/O on RA6

- 9. INTHS Internal Oscillator used as Microcontroller Clock Source, HS Oscillator used as USB Clock Source

- 10. INTXT Internal Oscillator used as Microcontroller Clock Source, XT Oscillator used as USB Clock Source

- 11. INTIO Internal Oscillator used as Microcontroller Clock Source, EC Oscillator used as USB Clock Source, Digital I/O on RA6

- 12. INTCKO Internal Oscillator used as Microcontroller Clock Source, EC Oscillator used as USB Clock Source, Fosc/4 Output on RA6

### 2.5 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. Unless the USB module is enabled, the OSC1 pin (and OSC2 pin if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features regardless of the power-managed mode (see Section 18.2 "Watchdog Timer (WDT)", Section 18.3 "Two-Speed Start-up" and Section 18.4 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up).

Regardless of the Run or Idle mode selected, the USB clock source will continue to operate. If the device is operating from a crystal or resonator-based oscillator, that oscillator will continue to clock the USB module. The core and all other modules will switch to the new clock source.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Sleep mode should never be invoked while the USB module is operating and connected. The only exception is when the device has been issued a "Suspend" command over the USB. Once the module has suspended operation and shifted to a low-power state, the microcontroller may be safely put into Sleep mode.

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 21.2 "DC Characteristics: Power-Down and Supply Current".

# 2.6 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 21-10). It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval, TCSD (parameter 38, Table 21-10), following POR, while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC or internal oscillator modes are used as the primary clock source.

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|

| INTCKO          | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| INTIO           | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| ECIO, ECPIO     | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC              | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| XT and HS       | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

TABLE 2-4: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

Note: See Table 4-2 in Section 4.0 "Reset" for time-outs due to Sleep and MCLR Reset.

# 3.1.3 CLOCK TRANSITIONS AND STATUS INDICATORS

The length of the transition between clock sources is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Two bits indicate the current clock source and its status. They are:

- OSTS (OSCCON<3>)

- T1RUN (T1CON<6>)

In general, only one of these bits will be set while in a given power-managed mode. When the OSTS bit is set, the primary clock is providing the device clock. When the T1RUN bit is set, the Timer1 oscillator is providing the clock.

Note: Executing a SLEEP instruction does not necessarily place the device into Sleep mode. It acts as the trigger to place the controller into either the Sleep mode, or one of the Idle modes, depending on the setting of the IDLEN bit.

#### 3.1.4 MULTIPLE SLEEP COMMANDS

The power-managed mode that is invoked with the SLEEP instruction is determined by the setting of the IDLEN bit at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power-managed mode specified by IDLEN at that time. If IDLEN has changed, the device will enter the new power-managed mode specified by the new setting.

#### 3.2 Run Modes

In the Run modes, clocks to both the core and peripherals are active. The difference between these modes is the clock source.

# 3.2.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal, full-power execution mode of the microcontroller. This is also the default mode upon a device Reset unless Two-Speed Start-up is enabled (see **Section 18.3 "Two-Speed Start-up"** for details). In this mode, the OSTS bit is set.

#### 3.2.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC\_RUN mode is entered by setting the SCS1:SCS0 bits to '01'. The device clock source is switched to the Timer1 oscillator (see Figure 3-1), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

| Note: | The Timer1 oscillator should already be         |

|-------|-------------------------------------------------|

|       | running prior to entering SEC_RUN mode.         |

|       | If the T1OSCEN bit is not set when the          |

|       | SCS1:SCS0 bits are set to '01', entry to        |

|       | SEC_RUN mode will not occur. If the             |

|       | Timer1 oscillator is enabled but not yet        |

|       | running, device clocks will be delayed until    |

|       | the oscillator has started. In such             |

|       | situations, initial oscillator operation is far |

|       | from stable and unpredictable operation         |

|       | may result.                                     |

# 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator, INTRC. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTRC, the primary oscillator is shut down and the OSTS bit is cleared.

When a wake event occurs, the peripherals continue to be clocked from the INTRC. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTRC. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode, or the Sleep mode, to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/ GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see **Section 8.0 "Interrupts"**). A fixed delay of interval, TCSD, following the wake event, is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 18.2 "Watchdog Timer (WDT)").

#### 3.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 3-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 18.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 18.4 "Fail-Safe Clock Monitor"**) is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTRC driven by the internal oscillator. Execution is clocked by the internal oscillator until either the primary clock becomes ready or a powermanaged mode is entered before the primary clock becomes ready; the primary clock is then shut down.

#### 5.1.2.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit but not cause a device Reset. The STKFUL or STKUNF bits are cleared by user software or a Power-on Reset.

#### 5.1.3 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. Each stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into their associated registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST   | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|--------------|---------------------------------------------------------|

|      | •            |                                                         |

| SUB1 | •            |                                                         |

|      | RETURN, FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

# 5.1.4 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.4.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF<br>CALL | OFFSET, W<br>TABLE |

|-------|--------------|--------------------|

|       |              | IADDE              |

| ORG   | nn00h        |                    |

| TABLE | ADDWF        | PCL                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | RETLW        | nnh                |

|       | •            |                    |

|       | •            |                    |

|       | •            |                    |

#### 5.1.4.2 Table Reads and Table Writes

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to or from program memory one byte at a time.

Table read and table write operations are discussed further in Section 6.1 "Table Reads and Table Writes".

| File Name | Bit 7 | Bit 6              | Bit 5              | Bit 4              | Bit 3    | Bit 2   | Bit 1  | Bit 0   | Value on<br>POR, BOR | Details<br>on Page: |

|-----------|-------|--------------------|--------------------|--------------------|----------|---------|--------|---------|----------------------|---------------------|

| PORTC     | RC7   | RC6                | RC5 <sup>(6)</sup> | RC4 <sup>(6)</sup> | _        | RC2     | RC1    | RC0     | xxxx -xxx            | 51, 106             |

| PORTB     | RB7   | RB6                | RB5                | RB4                | RB3      | RB2     | RB1    | RB0     | XXXX XXXX            | 51, 100             |

| PORTA     | —     | RA6 <sup>(4)</sup> | RA5                | RA4                | RA3      | RA2     | RA1    | RA0     | -x0x 0000            | 51, 100             |

| UEP15     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP14     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP13     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP12     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP11     | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP10     | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 51, 135             |

| UEP9      | _     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP8      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP7      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP6      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP5      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP4      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP3      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP2      | _     | _                  |                    | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP1      | _     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UEP0      | —     | _                  | _                  | EPHSHK             | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 52, 135             |

| UCFG      | UTEYE | UOEMON             | _                  | UPUEN              | UTRDIS   | FSEN    | PPB1   | PPB0    | 00-0 0000            | 52, 132             |

| UADDR     | —     | ADDR6              | ADDR5              | ADDR4              | ADDR3    | ADDR2   | ADDR1  | ADDR0   | -000 0000            | 52, 136             |

| UCON      | —     | PPBRST             | SE0                | PKTDIS             | USBEN    | RESUME  | SUSPND | —       | -0x0 000-            | 52, 130             |

| USTAT     | —     | ENDP3              | ENDP2              | ENDP1              | ENDP0    | DIR     | PPBI   | —       | -xxx xxx-            | 52, 134             |

| UEIE      | BTSEE | _                  | _                  | BTOEE              | DFN8EE   | CRC16EE | CRC5EE | PIDEE   | 00 0000              | 52, 148             |

| UEIR      | BTSEF | _                  | _                  | BTOEF              | DFN8EF   | CRC16EF | CRC5EF | PIDEF   | 00 0000              | 52, 147             |

| UIE       | _     | SOFIE              | STALLIE            | IDLEIE             | TRNIE    | ACTVIE  | UERRIE | URSTIE  | -000 0000            | 52, 146             |

| UIR       | —     | SOFIF              | STALLIF            | IDLEIF             | TRNIF    | ACTVIF  | UERRIF | URSTIF  | -000 0000            | 52, 144             |

| UFRMH     | —     | —                  | —                  | —                  | —        | FRM10   | FRM9   | FRM8    | xxx                  | 52, 136             |

| UFRML     | FRM7  | FRM6               | FRM5               | FRM4               | FRM3     | FRM2    | FRM1   | FRM0    | XXXX XXXX            | 52, 136             |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.

Note 1: Bit 21 of the TBLPTRU allows access to the device Configuration bits.

2: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

3: These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'.

4: RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

#### 5.3.6 STATUS REGISTER

The STATUS register, shown in Register 5-2, contains the arithmetic status of the ALU. As with any other SFR, it can be the operand for any instruction.

If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, the results of the instruction are not written; instead, the STATUS register is updated according to the instruction performed. Therefore, the result of an instruction with the STATUS register as its destination may be different than intended. As an example, CLRF STATUS will set the Z bit and leave the remaining Status bits unchanged ('000u u1uu'). It is recommended that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions that do not affect Status bits, see the instruction set summaries in Table 19-2 and Table 19-3.

Note: The C and DC bits operate as the Borrow and Digit Borrow bits, respectively, in subtraction.

| U-0                 | U-0                                      | U-0                                                                                                                              | R/W-x           | R/W-x            | R/W-x           | R/W-x              | R/W-x            |  |  |  |  |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|--------------------|------------------|--|--|--|--|

| _                   | _                                        | —                                                                                                                                | N               | OV               | Z               | DC <sup>(1)</sup>  | C <sup>(2)</sup> |  |  |  |  |

| bit 7               | •                                        |                                                                                                                                  |                 |                  |                 | -<br>-             | bit 0            |  |  |  |  |

| 1                   |                                          |                                                                                                                                  |                 |                  |                 |                    |                  |  |  |  |  |

| Legend:<br>R = Read | labla bit                                | W = Writable                                                                                                                     | hit             | II – Unimplo     | mented bit, rea | d ac '0'           |                  |  |  |  |  |

|                     | e at POR                                 | '1' = Bit is set                                                                                                                 |                 | '0' = Bit is cle |                 | x = Bit is unknown |                  |  |  |  |  |

|                     |                                          | 1 - Dit 13 301                                                                                                                   |                 |                  |                 |                    |                  |  |  |  |  |

| bit 7-5             | Unimplemer                               | nted: Read as '                                                                                                                  | 0'              |                  |                 |                    |                  |  |  |  |  |

| bit 4               | N: Negative I                            | bit                                                                                                                              |                 |                  |                 |                    |                  |  |  |  |  |

|                     |                                          | •                                                                                                                                | rithmetic (2's  | complement). I   | t indicates whe | ther the result w  | /as              |  |  |  |  |

|                     | negative (AL                             | ,                                                                                                                                |                 |                  |                 |                    |                  |  |  |  |  |

|                     |                                          | 1 = Result was negative<br>0 = Result was positive                                                                               |                 |                  |                 |                    |                  |  |  |  |  |

| bit 3               | OV: Overflow                             | •                                                                                                                                |                 |                  |                 |                    |                  |  |  |  |  |

|                     |                                          | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the 7-bit                                   |                 |                  |                 |                    |                  |  |  |  |  |

|                     | -                                        |                                                                                                                                  | •               | -                | to change state |                    |                  |  |  |  |  |

|                     |                                          | <ul> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul> |                 |                  |                 |                    |                  |  |  |  |  |

| bit 2               | 0 – No overní<br><b>Z:</b> Zero bit      |                                                                                                                                  |                 |                  |                 |                    |                  |  |  |  |  |

|                     |                                          | It of an arithme                                                                                                                 | tic or logic on | eration is zero  |                 |                    |                  |  |  |  |  |

|                     |                                          | It of an arithmetic or logic operation is zero<br>It of an arithmetic or logic operation is not zero                             |                 |                  |                 |                    |                  |  |  |  |  |

| bit 1               | DC: Digit Car                            | rry/Borrow bit <sup>(1</sup>                                                                                                     | )               |                  |                 |                    |                  |  |  |  |  |

|                     |                                          | DDLW, SUBLW a                                                                                                                    |                 |                  |                 |                    |                  |  |  |  |  |

|                     |                                          | out from the 4th                                                                                                                 |                 |                  | curred          |                    |                  |  |  |  |  |

| bit 0               | 0 = No carry-<br><b>C:</b> Carry/Bor     | out from the 4t                                                                                                                  | n Iow-order D   | it of the result |                 |                    |                  |  |  |  |  |

| DILU                | ,                                        |                                                                                                                                  | and SUBWF ins   | structions:      |                 |                    |                  |  |  |  |  |

|                     |                                          | or ADDWF, ADDLW, SUBLW and SUBWF instructions:<br>= A carry-out from the Most Significant bit of the result occurred             |                 |                  |                 |                    |                  |  |  |  |  |

|                     |                                          | out from the M                                                                                                                   |                 |                  |                 |                    |                  |  |  |  |  |

| Note 1:             | ,                                        |                                                                                                                                  |                 |                  |                 |                    |                  |  |  |  |  |

|                     | operand. For rotat                       |                                                                                                                                  |                 |                  |                 |                    | -                |  |  |  |  |

| 2:                  | For borrow, the po<br>operand. For rotat |                                                                                                                                  |                 |                  |                 |                    |                  |  |  |  |  |

|                     | source register.                         | (nne, kle) III                                                                                                                   |                 |                  |                 | ingri or iow-orde  |                  |  |  |  |  |

# REGISTER 5-2: STATUS REGISTER

#### 10.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable; its value is set by the PSA and T0PS2:T0PS0 bits (T0CON<3:0>) which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256, in power-of-2 increments, are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count but will not change the prescaler assignment.

#### 10.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

# 10.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before reenabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine.

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

TABLE 10-1:REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7      | Bit 6                     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|--------|------------|---------------------------|--------|--------|--------|--------|--------|--------|-----------------------------|

| TMR0L  | Timer0 Reg | Timer0 Register Low Byte  |        |        |        |        |        |        | 50                          |

| TMR0H  | Timer0 Reg | Timer0 Register High Byte |        |        |        |        |        | 50     |                             |

| INTCON | GIE/GIEH   | PEIE/GIEL                 | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 49                          |

| T0CON  | TMR0ON     | T08BIT                    | TOCS   | T0SE   | PSA    | T0PS2  | T0PS1  | T0PS0  | 50                          |

| TRISA  | —          | TRISA6 <sup>(1)</sup>     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 51                          |

Legend: — = unimplemented locations, read as '0'. Shaded cells are not used by Timer0.

**Note 1:** RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'.

#### 11.7 Considerations in Asynchronous Counter Mode

Following a Timer1 interrupt and an update to the TMR1 registers, the Timer1 module uses a falling edge on its clock source to trigger the next register update on the rising edge. If the update is completed after the clock input has fallen, the next rising edge will not be counted.

If the application can reliably update TMR1 before the timer input goes low, no additional action is needed. Otherwise, an adjusted update can be performed

following a later Timer1 increment. This can be done by monitoring TMR1L within the interrupt routine until it increments, and then updating the TMR1H:TMR1L register pair while the clock is low, or one-half of the period of the clock source. Assuming that Timer1 is being used as a Real-Time Clock, the clock source is a 32.768 kHz crystal oscillator. In this case, one-half period of the clock is 15.25  $\mu$ s.

The Real-Time Clock application code in Example 11-1 shows a typical ISR for Timer1, as well as the optional code required if the update cannot be done reliably within the required interval.

EXAMPLE 11-1: IMPLEMENTING A REAL-TIME CLOCK USING A TIMER1 INTERRUPT SERVICE

| RTCinit |        |              |                                                               |

|---------|--------|--------------|---------------------------------------------------------------|

|         | MOVLW  | 80h          | ; Preload TMR1 register pair                                  |

|         | MOVWF  | TMR1H        | ; for 1 second overflow                                       |

|         | CLRF   | TMR1L        |                                                               |

|         | MOVLW  | b'00001111'  | ; Configure for external clock,                               |

|         | MOVWF  | T1CON        | ; Asynchronous operation, external oscillator                 |

|         | CLRF   | secs         | ; Initialize timekeeping registers                            |

|         | CLRF   | mins         | ;                                                             |

|         | MOVLW  | .12          |                                                               |

|         | MOVWF  | hours        |                                                               |

|         | BSF    | PIE1, TMR1IE | ; Enable Timer1 interrupt                                     |

|         | RETURN |              |                                                               |

| RTCisr  |        |              |                                                               |

|         |        |              | ; Insert the next 4 lines of code when TMR1                   |

|         |        |              | ; cannot be reliably updated before clock pulse goes low      |

|         | BTFSC  | TMR1L,0      | ; wait for TMR1L to become clear                              |

|         | BRA    | \$-2         | ; (may already be clear)                                      |

|         | BTFSS  | TMR1L,0      | ; wait for TMR1L to become set                                |

|         | BRA    | \$-2         | ; TMR1 has just incremented                                   |

|         |        |              | ; If TMR1 update can be completed before clock pulse goes low |

|         |        |              | ; Start ISR here                                              |

|         | BSF    | TMR1H, 7     | ; Preload for 1 sec overflow                                  |

|         | BCF    | PIR1, TMR1IF | ; Clear interrupt flag                                        |

|         | INCF   | secs, F      | ; Increment seconds                                           |

|         | MOVLW  | .59          | ; 60 seconds elapsed?                                         |

|         | CPFSGT | secs         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | secs         | ; Clear seconds                                               |

|         | INCF   | mins, F      | ; Increment minutes                                           |

|         | MOVLW  | .59          | ; 60 minutes elapsed?                                         |

|         | CPFSGT | mins         |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | mins         | ; clear minutes                                               |

|         | INCF   | hours, F     | ; Increment hours                                             |

|         | MOVLW  | .23          | ; 24 hours elapsed?                                           |

|         | CPFSGT | hours        |                                                               |

|         | RETURN |              | ; No, done                                                    |

|         | CLRF   | hours        | ; Reset hours                                                 |

|         | RETURN |              | ; Done                                                        |

|         | KETUKN |              | ; Done                                                        |

#### 14.5.2 USB INTERRUPT ENABLE REGISTER (UIE)

The USB Interrupt Enable register (Register 14-8) contains the enable bits for the USB status interrupt sources. Setting any of these bits will enable the respective interrupt source in the UIR register.

The values in this register only affect the propagation of an interrupt condition to the microcontroller's interrupt logic. The flag bits are still set by their interrupt conditions, allowing them to be polled and serviced without actually generating an interrupt.

### REGISTER 14-8: UIE: USB INTERRUPT ENABLE REGISTER

| U-0   | R/W-0 | R/W-0   | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|--------|-------|--------|--------|--------|

| —     | SOFIE | STALLIE | IDLEIE | TRNIE | ACTVIE | UERRIE | URSTIE |

| bit 7 |       |         |        |       |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                          |

|-------|---------------------------------------------------------------------------------------------------------------------|

| bit 6 | SOFIE: Start-of-Frame Token Interrupt Enable bit                                                                    |

|       | <ol> <li>1 = Start-of-Frame token interrupt enabled</li> <li>0 = Start-of-Frame token interrupt disabled</li> </ol> |

| bit 5 | STALLIE: STALL Handshake Interrupt Enable bit                                                                       |

|       | 1 = STALL interrupt enabled                                                                                         |

|       | 0 = STALL interrupt disabled                                                                                        |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                                                                            |

|       | 1 = Idle detect interrupt enabled                                                                                   |

|       | 0 = Idle detect interrupt disabled                                                                                  |

| bit 3 | TRNIE: Transaction Complete Interrupt Enable bit                                                                    |

|       | 1 = Transaction interrupt enabled                                                                                   |

|       | 0 = Transaction interrupt disabled                                                                                  |

| bit 2 | ACTVIE: Bus Activity Detect Interrupt Enable bit                                                                    |

|       | 1 = Bus activity detect interrupt enabled                                                                           |

|       | 0 = Bus activity detect interrupt disabled                                                                          |

| bit 1 | UERRIE: USB Error Interrupt Enable bit                                                                              |

|       | 1 = USB error interrupt enabled                                                                                     |

|       | 0 = USB error interrupt disabled                                                                                    |

| bit 0 | URSTIE: USB Reset Interrupt Enable bit                                                                              |

|       | 1 = USB Reset interrupt enabled                                                                                     |

|       | 0 = USB Reset interrupt disabled                                                                                    |

# 15.1 Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit (BAUDCON<3>) selects 16-bit mode.

The SPBRGH:SPBRG register pair controls the period of a free-running timer. In Asynchronous mode, bits BRGH (TXSTA<2>) and BRG16 (BAUDCON<3>) also control the baud rate. In Synchronous mode, BRGH is ignored. Table 15-1 shows the formula for computation of the baud rate for different EUSART modes which only apply in Master mode (internally generated clock).

Given the desired baud rate and FOSC, the nearest integer value for the SPBRGH:SPBRG registers can be calculated using the formulas in Table 15-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 15-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 15-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGH:SPBRG registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

# 15.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG register pair.

#### 15.1.2 SAMPLING

The data on the RX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

| Configuration Bits |       |      |                     | Boud Boto Formula        |  |

|--------------------|-------|------|---------------------|--------------------------|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART Mode     | Baud Rate Formula        |  |

| 0                  | 0     | 0    | 8-Bit/Asynchronous  | Fosc/[64 (n + 1)]        |  |

| 0                  | 0     | 1    | 8-Bit/Asynchronous  | $\Gamma_{000}/[16(n+1)]$ |  |

| 0                  | 1     | 0    | 16-Bit/Asynchronous | Fosc/[16 (n + 1)]        |  |

| 0                  | 1     | 1    | 16-Bit/Asynchronous |                          |  |

| 1                  | 0     | Х    | 8-Bit/Synchronous   | Fosc/[4 (n + 1)]         |  |

| 1                  | 1     | х    | 16-Bit/Synchronous  |                          |  |

**Legend:** x = Don't care, n = Value of SPBRGH:SPBRG register pair

# PIC18F2450/4450

# FIGURE 15-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

# TABLE 15-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                                         | Bit 6       | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|-----------------------------------------------|-------------|-------------|------------|-------|--------|--------|--------|-----------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL   | TMR0IE      | INT0IE     | RBIE  | TMR0IF | INT0IF | RBIF   | 49                          |

| PIR1    | —                                             | ADIF        | RCIF        | TXIF       | _     | CCP1IF | TMR2IF | TMR1IF | 51                          |

| PIE1    | —                                             | ADIE        | RCIE        | TXIE       | _     | CCP1IE | TMR2IE | TMR1IE | 51                          |

| IPR1    | —                                             | ADIP        | RCIP        | TXIP       | _     | CCP1IP | TMR2IP | TMR1IP | 51                          |

| RCSTA   | SPEN                                          | RX9         | SREN        | CREN       | ADDEN | FERR   | OERR   | RX9D   | 51                          |

| TXREG   | EUSART T                                      | ransmit Reg | ister       |            |       |        |        |        | 51                          |

| TXSTA   | CSRC                                          | TX9         | TXEN        | SYNC       | SENDB | BRGH   | TRMT   | TX9D   | 51                          |

| BAUDCON | ABDOVF                                        | RCIDL       | _           | SCKP       | BRG16 | —      | WUE    | ABDEN  | 51                          |

| SPBRGH  | EUSART Baud Rate Generator Register High Byte |             |             |            |       |        |        | 50     |                             |

| SPBRG   | EUSART E                                      | Baud Rate G | enerator Re | gister Low | Byte  |        |        |        | 50                          |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

| R/W-0        | U-0                                         | R/W-0                | R/W-0          | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |  |  |  |

|--------------|---------------------------------------------|----------------------|----------------|--------------------------|------------------|-----------------|-------|--|--|--|

| ADFM         | _                                           | ACQT2                | ACQT1          | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |  |  |  |

| bit 7        |                                             |                      |                |                          |                  |                 | bit ( |  |  |  |

|              |                                             |                      |                |                          |                  |                 |       |  |  |  |

| Legend:      |                                             |                      |                |                          |                  |                 |       |  |  |  |

| R = Readab   | le bit                                      | W = Writable         | bit            | U = Unimplen             | nented bit, read | d as '0'        |       |  |  |  |

| -n = Value a | t POR                                       | '1' = Bit is set     |                | '0' = Bit is clea        | ared             | x = Bit is unkr | nown  |  |  |  |

| bit 7        | ADFM: A/D F                                 | esult Format S       | Select bit     |                          |                  |                 |       |  |  |  |

|              | 1 = Right justified<br>0 = Left justified   |                      |                |                          |                  |                 |       |  |  |  |

| bit 6        | Unimplemen                                  | ted: Read as '       | 0'             |                          |                  |                 |       |  |  |  |

| bit 5-3      | ACQT2:ACQ                                   | T0: A/D Acquis       | sition Time Se | lect bits                |                  |                 |       |  |  |  |

|              | 111 <b>= 20 T</b> AD                        |                      |                |                          |                  |                 |       |  |  |  |

|              | 110 <b>= 16 Tad</b>                         |                      |                |                          |                  |                 |       |  |  |  |

|              | 101 <b>= 12 Tad</b>                         |                      |                |                          |                  |                 |       |  |  |  |

|              | 100 <b>= 8 TAD</b>                          |                      |                |                          |                  |                 |       |  |  |  |

|              | 011 = 6 TAD                                 |                      |                |                          |                  |                 |       |  |  |  |

|              | 010 = 4 TAD                                 |                      |                |                          |                  |                 |       |  |  |  |

|              | 001 = 2  TAD<br>$000 = 0 \text{ TAD}^{(1)}$ |                      |                |                          |                  |                 |       |  |  |  |

| bit 2-0      |                                             | <b>S0:</b> A/D Conve | ersion Clock S | elect bits               |                  |                 |       |  |  |  |

|              |                                             | ock derived fro      |                |                          |                  |                 |       |  |  |  |

|              | 110 = Fosc/6                                |                      |                |                          |                  |                 |       |  |  |  |

|              | 101 = Fosc/16                               |                      |                |                          |                  |                 |       |  |  |  |

|              | 100 <b>= Fosc/4</b>                         |                      |                |                          |                  |                 |       |  |  |  |

|              | 011 = FRC (cl                               | ock derived fro      | m A/D RC os    | cillator) <sup>(1)</sup> |                  |                 |       |  |  |  |

|              | 010 = Fosc/3                                | 2                    |                |                          |                  |                 |       |  |  |  |

|              | 001 = Fosc/8                                |                      |                |                          |                  |                 |       |  |  |  |

|              | 000 = Fosc/2                                |                      |                |                          |                  |                 |       |  |  |  |

#### REGISTER 16-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TcY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

# REGISTER 18-7: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/C-1 | R/C-1 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | _   | —   | —   | CP1   | CP0   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                   |                   |                                     |

|---------------------------|-------------------|-------------------------------------|

| R = Readable bit          | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is | unprogrammed      | u = Unchanged from programmed state |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | CP1: Code Protection bit                                                                                                                     |

|         | <ul><li>1 = Block 1 (002000-003FFFh) is not code-protected</li><li>0 = Block 1 (002000-003FFFh) is code-protected</li></ul>                  |

| bit 0   | CP0: Code Protection bit                                                                                                                     |

|         | 1 = Block 0 (000800-001FFFh) or (001000-001FFFh) is not code-protected<br>0 = Block 0 (000800-001FFFh) or (001000-001FFFh) is code-protected |

# REGISTER 18-8: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| U-0   | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| —     | СРВ   | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:                                |                   |                                     |

|----------------------------------------|-------------------|-------------------------------------|

| R = Readable bit                       | C = Clearable bit | U = Unimplemented bit, read as '0'  |

| -n = Value when device is unprogrammed |                   | u = Unchanged from programmed state |

| DIT /   | Unimplemented: Read as 10                                                                                                                          |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | CPB: Boot Block Code Protection bit                                                                                                                |

|         | 1 = Boot block (000000-0007FFh) or (000000-000FFFh) is not code-protected<br>0 = Boot block (000000-0007FFh) or (000000-000FFFh) is code-protected |

| bit 5-0 | Unimplemented: Read as '0'                                                                                                                         |

|         |                                                                                                                                                    |

### REGISTER 18-9: CONFIG6L: CONFIGURATION REGISTER 6 LOW (BYTE ADDRESS 30000Ah)

| U-0                                                                     | U-0                                                                 | U-0            | U-0             | U-0          | U-0              | R/C-1      | R/C-1 |  |  |  |