Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | UART/USART, USB                                                             |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

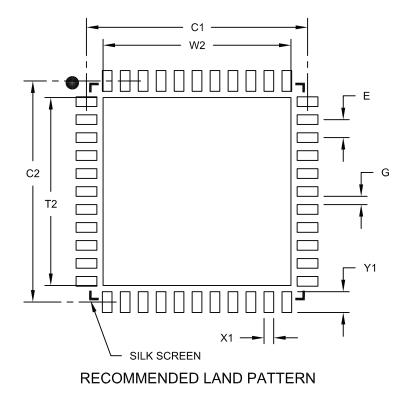

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4450t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2008, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

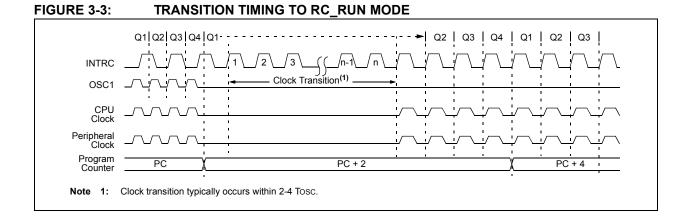

# 3.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator; the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator (INTRC), there are no distinguishable differences between the PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator, the use of RC\_RUN mode is not recommended.

This mode is entered by setting SCS1 to '1'. Although it is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTRC (see Figure 3-3), the primary oscillator is shut down and the OSTS bit is cleared.

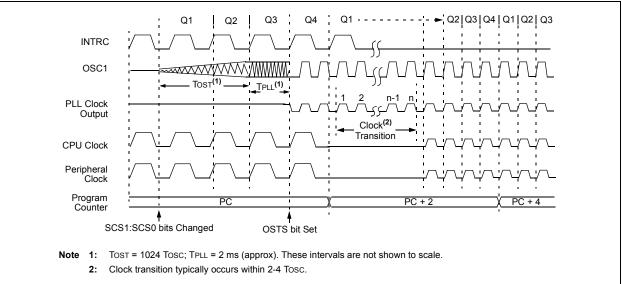

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTRC while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 3-4). When the clock switch is complete, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- The primary clock source is not any of the XT or HS modes

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (EC and any internal oscillator modes). However, a fixed delay of interval TCSD following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

# TABLE 3-2:EXIT DELAY ON WAKE-UP BY RESET FROM SLEEP MODE OR ANY IDLE MODE<br/>(BY CLOCK SOURCES)

| Microcontroller               | · Clock Source       | Exit Dolov                            | Clock Ready Status |

|-------------------------------|----------------------|---------------------------------------|--------------------|

| Before Wake-up                | After Wake-up        | Exit Delay                            | Bit (OSCCON)       |

|                               | XT, HS               |                                       |                    |

| Primary Device Clock          | XTPLL, HSPLL         | None                                  | OSTS               |

| (PRI_IDLE mode)               | EC                   | None                                  | 0010               |

|                               | INTRC <sup>(1)</sup> |                                       |                    |

|                               | XT, HS               | Tost <sup>(3)</sup>                   |                    |

| T1OSC or INTRC <sup>(1)</sup> | XTPLL, HSPLL         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS               |

| TIOSE OF INTROV               | EC                   | TCSD <sup>(2)</sup>                   | 0313               |

|                               | INTRC <sup>(1)</sup> | TIOBST <sup>(4)</sup>                 |                    |

|                               | XT, HS               | Tost <sup>(3)</sup>                   |                    |

| INTRC <sup>(1)</sup>          | XTPLL, HSPLL         | Tost + t <sub>rc</sub> <sup>(3)</sup> | OSTS               |

|                               | EC                   | TCSD <sup>(2)</sup>                   | 0313               |

|                               | INTRC <sup>(1)</sup> | None                                  |                    |

|                               | XT, HS               | Tost <sup>(3)</sup>                   |                    |

| None                          | XTPLL, HSPLL         | Tost + t <sub>rc</sub> <sup>(3)</sup> | - OSTS             |

| (Sleep mode)                  | EC                   | TCSD <sup>(2)</sup>                   | 0313               |

|                               | INTRC <sup>(1)</sup> | TIOBST <sup>(4)</sup>                 |                    |

Note 1: In this instance, refers specifically to the 31 kHz INTRC clock source.

2: TCSD (parameter 38, Table 21-10) is a required delay when waking from Sleep and all Idle modes and runs concurrently with any other required delays (see Section 3.4 "Idle Modes").

**3:** TOST is the Oscillator Start-up Timer period (parameter 32, Table 21-10). t<sub>rc</sub> is the PLL lock time-out (parameter F12, Table 21-7); it is also designated as TPLL.

4: Execution continues during TIOBST (parameter 39, Table 21-10), the INTRC stabilization period.

#### 5.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSb will always read '0' (see Section 5.1.1 "Program Counter").

Figure 5-4 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 5-4 shows how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 19.0 "Instruction Set Summary" provides further details of the instruction set.

|                |            |                    | <b>LSB =</b> 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|----------------|---------|---------------------------|

|                | Program N  |                    |                |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |                |         | 000002h                   |

|                |            |                    |                |         | 000004h                   |

|                |            |                    |                |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh            | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 0006h              | EFh            | 03h     | 00000Ah                   |

|                |            | -                  | F0h            | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456h         | C1h            | 23h     | 00000Eh                   |

|                |            | -                  | F4h            | 56h     | 000010h                   |

|                |            | -                  |                |         | 000012h                   |

|                |            | -                  |                |         | 000014h                   |

# FIGURE 5-4: INSTRUCTIONS IN PROGRAM MEMORY

#### 5.2.4 TWO-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence, immediately after the first word, the data in the second word is accessed and

used by the instruction sequence. If the first word is skipped for some reason and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 5-4 shows how this works.

| Note: | See Section 5.5 "Program Memory and        |

|-------|--------------------------------------------|

|       | the Extended Instruction Set" for          |

|       | information on two-word instruction in the |

|       | extended instruction set.                  |

| EXAMPLE 5-4: | <b>TWO-WORD INSTRUCTIONS</b> |

|--------------|------------------------------|

|--------------|------------------------------|

| CASE 1:             |                  |                              |  |  |  |  |

|---------------------|------------------|------------------------------|--|--|--|--|

| Object Code         | Source Code      |                              |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; No, skip this word         |  |  |  |  |

| 1111 0100 0101 0110 |                  | ; Execute this word as a NOP |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |  |  |  |  |

| CASE 2:             |                  |                              |  |  |  |  |

| Object Code         | Source Code      |                              |  |  |  |  |

| 0110 0110 0000 0000 | TSTFSZ REG1      | ; is RAM location 0?         |  |  |  |  |

| 1100 0001 0010 0011 | MOVFF REG1, REG2 | ; Yes, execute this word     |  |  |  |  |

| 1111 0100 0101 0110 |                  | ; 2nd word of instruction    |  |  |  |  |

| 0010 0100 0000 0000 | ADDWF REG3       | ; continue code              |  |  |  |  |

| TOSU     |                                                                                                                                                                                                                                              |                                                     |                       |                |                |                |                 |              | POR, BOR  | on Page: |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------------|----------------|----------------|----------------|-----------------|--------------|-----------|----------|

| тоец     | —                                                                                                                                                                                                                                            | _                                                   | _                     | Top-of-Stack   | Upper Byte (T  | OS<20:16>)     |                 |              | 0 0000    | 49, 54   |

| TOSH     | Top-of-Stack H                                                                                                                                                                                                                               | High Byte (TO                                       | S<15:8>)              | •              |                |                |                 |              | 0000 0000 | 49, 54   |

| TOSL     | Top-of-Stack L                                                                                                                                                                                                                               | _ow Byte (TOS                                       | 6<7:0>)               |                |                |                |                 |              | 0000 0000 | 49, 54   |

| STKPTR   | STKFUL                                                                                                                                                                                                                                       | STKUNF                                              | _                     | SP4            | SP3            | SP2            | SP1             | SP0          | 00-0 0000 | 49, 55   |

| PCLATU   | _                                                                                                                                                                                                                                            | _                                                   | _                     | Holding Regi   | ster for PC<20 | :16>           | •               | •            | 0 0000    | 49, 54   |

| PCLATH   | Holding Regis                                                                                                                                                                                                                                | ster for PC<15                                      | :8>                   |                |                |                |                 |              | 0000 0000 | 49, 54   |

| PCL      | PC Low Byte                                                                                                                                                                                                                                  | (PC<7:0>)                                           |                       |                |                |                |                 |              | 0000 0000 | 49, 54   |

| TBLPTRU  | _                                                                                                                                                                                                                                            | _                                                   | bit 21 <sup>(1)</sup> | Program Mer    | mory Table Poi | nter Upper By  | te (TBLPTR<2    | 20:16>)      | 00 0000   | 49, 76   |

| TBLPTRH  | Program Memory Table Pointer High Byte (TBLPTR<15:8>)                                                                                                                                                                                        |                                                     |                       |                |                |                |                 | 0000 0000    | 49, 76    |          |

| TBLPTRL  | Program Merr                                                                                                                                                                                                                                 | Program Memory Table Pointer Low Byte (TBLPTR<7:0>) |                       |                |                |                |                 |              | 0000 0000 | 49, 76   |

| TABLAT   | Program Merr                                                                                                                                                                                                                                 | nory Table Late                                     | ch                    |                |                |                |                 |              | 0000 0000 | 49, 76   |

| PRODH    | Product Regis                                                                                                                                                                                                                                | ster High Byte                                      |                       |                |                |                |                 |              | XXXX XXXX | 49, 83   |

| PRODL    | Product Regis                                                                                                                                                                                                                                | ster Low Byte                                       |                       |                |                |                |                 |              | XXXX XXXX | 49, 83   |

| INTCON   | GIE/GIEH                                                                                                                                                                                                                                     | PEIE/GIEL                                           | TMR0IE                | INT0IE         | RBIE           | TMR0IF         | <b>INT0IF</b>   | RBIF         | 0000 000x | 49, 87   |

| INTCON2  | RBPU                                                                                                                                                                                                                                         | INTEDG0                                             | INTEDG1               | INTEDG2        | _              | TMR0IP         | _               | RBIP         | 1111 -1-1 | 49, 88   |

| INTCON3  | INT2IP                                                                                                                                                                                                                                       | INT1IP                                              | _                     | INT2IE         | INT1IE         | _              | INT2IF          | INT1IF       | 11-0 0-00 | 49, 89   |

| INDF0    | Uses contents                                                                                                                                                                                                                                | s of FSR0 to a                                      | ddress data n         | nemory – value | e of FSR0 not  | changed (not a | a physical regi | ster)        | N/A       | 49, 68   |

|          |                                                                                                                                                                                                                                              |                                                     |                       |                | e of FSR0 post |                |                 |              | N/A       | 49, 69   |

|          |                                                                                                                                                                                                                                              |                                                     |                       |                | e of FSR0 post |                |                 |              | N/A       | 49, 69   |

| 1        |                                                                                                                                                                                                                                              |                                                     |                       |                |                |                |                 |              | N/A       | 49, 69   |

| PLUSW0   | Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register)<br>Uses contents of FSR0 to address data memory – value of FSR0 pre-incremented (not a physical register) – value of FSR0 offset by W |                                                     |                       |                |                |                |                 |              | N/A       | 49, 69   |

| FSR0H    | _                                                                                                                                                                                                                                            | _                                                   | _                     | _              | Indirect Data  | Memory Addre   | ess Pointer 0 H | ligh Byte    | 0000      | 49, 68   |

| FSR0L    | Indirect Data I                                                                                                                                                                                                                              | Memory Addre                                        | ess Pointer 0         | Low Byte       |                |                |                 |              | XXXX XXXX | 49, 68   |

| WREG     | Working Regi                                                                                                                                                                                                                                 | ster                                                |                       |                |                |                |                 |              | XXXX XXXX | 49,      |

| INDF1    | Uses contents                                                                                                                                                                                                                                | s of FSR1 to a                                      | ddress data n         | nemory – value | e of FSR1 not  | changed (not a | a physical regi | ster)        | N/A       | 49, 68   |

| POSTINC1 | Uses contents                                                                                                                                                                                                                                | s of FSR1 to a                                      | ddress data n         | nemory – value | e of FSR1 post | -incremented   | (not a physica  | l register)  | N/A       | 49, 69   |

| POSTDEC1 | Uses contents                                                                                                                                                                                                                                | s of FSR1 to a                                      | ddress data n         | nemory – value | e of FSR1 post | -decremented   | (not a physica  | al register) | N/A       | 49, 69   |

| PREINC1  | Uses contents                                                                                                                                                                                                                                | s of FSR1 to a                                      | ddress data n         | nemory – value | e of FSR1 pre- | incremented (  | not a physical  | register)    | N/A       | 49, 69   |

|          | Uses contents value of FSR1                                                                                                                                                                                                                  |                                                     | ddress data n         | nemory – value | e of FSR1 pre- | incremented (  | not a physical  | register) –  | N/A       | 49, 69   |

| FSR1H    | _                                                                                                                                                                                                                                            | -                                                   | _                     | _              | Indirect Data  | Memory Addre   | ess Pointer 1 H | High Byte    | 0000      | 49, 68   |

| FSR1L    | Indirect Data I                                                                                                                                                                                                                              | Memory Addre                                        | ess Pointer 1         | Low Byte       |                |                |                 |              | XXXX XXXX | 49, 68   |

| BSR      | _                                                                                                                                                                                                                                            | _                                                   | _                     | _              | Bank Select F  | Register       |                 |              | 0000      | 49, 59   |

| INDF2    | Uses contents                                                                                                                                                                                                                                | s of FSR2 to a                                      | ddress data n         | nemory – value | e of FSR2 not  | changed (not a | a physical regi | ster)        | N/A       | 50, 68   |

| POSTINC2 | Uses contents                                                                                                                                                                                                                                | s of FSR2 to a                                      | ddress data n         | nemory – value | e of FSR2 post | -incremented   | (not a physica  | l register)  | N/A       | 50, 69   |

| POSTDEC2 | Uses contents                                                                                                                                                                                                                                | s of FSR2 to a                                      | ddress data n         | nemory – value | e of FSR2 post | -decremented   | (not a physica  | al register) | N/A       | 50, 69   |

| PREINC2  | Uses contents                                                                                                                                                                                                                                | s of FSR2 to a                                      | ddress data n         | nemory – value | e of FSR2 pre- | incremented (  | not a physical  | register)    | N/A       | 50, 69   |

|          |                                                                                                                                                                                                                                              |                                                     |                       |                |                |                |                 | N/A          | 50, 69    |          |

| FSR2H    | —                                                                                                                                                                                                                                            | _                                                   | —                     | _              | Indirect Data  | Memory Addre   | ess Pointer 2 I | ligh Byte    | 0000      | 50, 68   |

| FSR2L    | Indirect Data I                                                                                                                                                                                                                              | Memory Addre                                        | ess Pointer 2         | Low Byte       |                |                |                 |              | XXXX XXXX | 50, 68   |

| STATUS   | _                                                                                                                                                                                                                                            | _                                                   | —                     | N              | OV             | Z              | DC              | С            | x xxxx    | 50, 66   |

| TMR0H    | Timer0 Regist                                                                                                                                                                                                                                | ter High Byte                                       |                       | •              |                |                | •               |              | 0000 0000 | 50, 113  |

|          |                                                                                                                                                                                                                                              |                                                     |                       |                |                |                |                 |              |           | 50, 113  |

| TMR0L    | Timer0 Regist                                                                                                                                                                                                                                | lei Low Byte                                        |                       |                |                |                |                 |              | XXXX XXXX | 50, 115  |

Bit 21 of the TBLPTRU allows access to the device Configuration bits. Note 1:

2: The SBOREN bit is only available when BOREN<1:0> = 01; otherwise, the bit reads as '0'.

These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; individual unimplemented bits should be interpreted as '-'. 3:

RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'. 4:

5: RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'.

RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0). 6:

| File Name            | Bit 7                  | Bit 6                 | Bit 5            | Bit 4            | Bit 3              | Bit 2              | Bit 1              | Bit 0              | Value on<br>POR, BOR | Details<br>on Page: |

|----------------------|------------------------|-----------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------|----------------------|---------------------|

| OSCCON               | IDLEN                  | _                     | _                | _                | OSTS               | _                  | SCS1               | SCS0               | 0 q-00               | 50, 31              |

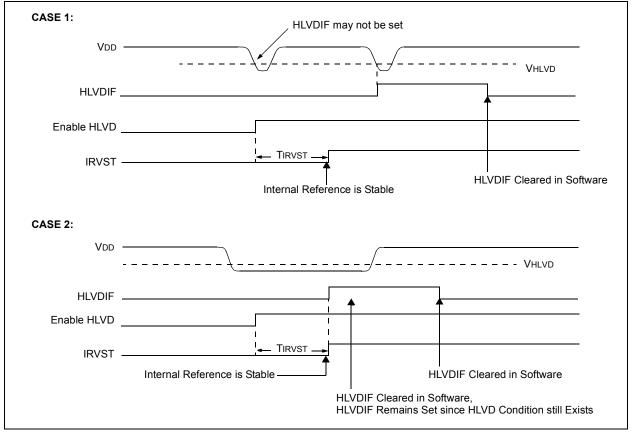

| HLVDCON              | VDIRMAG                | _                     | IRVST            | HLVDEN           | HLVDL3             | HLVDL2             | HLVDL1             | HLVDL0             | 0-00 0101            | 50, 185             |

| WDTCON               | _                      | _                     | _                | —                | _                  | _                  | _                  | SWDTEN             | 0                    | 50, 204             |

| RCON                 | IPEN                   | SBOREN <sup>(2)</sup> | _                | RI               | TO                 | PD                 | POR                | BOR                | 0q-1 11q0            | 50, 42              |

| TMR1H                | Timer1 Regis           | ter High Byte         |                  | •                |                    |                    |                    |                    | XXXX XXXX            | 50, 120             |

| TMR1L                | Timer1 Regis           | ter Low Byte          |                  |                  |                    |                    |                    |                    | XXXX XXXX            | 50, 120             |

| T1CON                | RD16                   | T1RUN                 | T1CKPS1          | T1CKPS0          | T10SCEN            | T1SYNC             | TMR1CS             | TMR10N             | 0000 0000            | 50, 115             |

| TMR2                 | Timer2 Regis           | ter                   |                  | •                |                    |                    |                    |                    | 0000 0000            | 50, 122             |

| PR2                  | Timer2 Period Register |                       |                  |                  |                    |                    |                    |                    | 1111 1111            | 50, 122             |

| T2CON                | —                      | T2OUTPS3              | T2OUTPS2         | T2OUTPS1         | T2OUTPS0           | TMR2ON             | T2CKPS1            | T2CKPS0            | -000 0000            | 50, 121             |

| ADRESH               | A/D Result Re          | egister High B        | yte              | •                |                    |                    |                    |                    | XXXX XXXX            | 50, 184             |

| ADRESL               | A/D Result Re          | egister Low By        | rte              |                  |                    |                    |                    |                    | XXXX XXXX            | 50, 184             |

| ADCON0               | _                      | _                     | CHS3             | CHS2             | CHS1               | CHS0               | GO/DONE            | ADON               | 00 0000              | 50, 175             |

| ADCON1               | _                      | _                     | VCFG1            | VCFG0            | PCFG3              | PCFG2              | PCFG1              | PCFG0              | 00 qqqq              | 50, 176             |

| ADCON2               | ADFM                   | —                     | ACQT2            | ACQT1            | ACQT0              | ADCS2              | ADCS1              | ADCS0              | 0-00 0000            | 50, 177             |

| CCPR1H               | Capture/Com            | pare/PWM Re           | gister 1 High I  | Byte             |                    |                    |                    |                    | XXXX XXXX            | 50, 124             |

| CCPR1L               | Capture/Com            | pare/PWM Re           | gister 1 Low E   | Byte             |                    |                    |                    |                    | XXXX XXXX            | 50, 124             |

| CCP1CON              | _                      | —                     | DC1B1            | DC1B0            | CCP1M3             | CCP1M2             | CCP1M1             | CCP1M0             | 00 0000              | 50, 123,            |

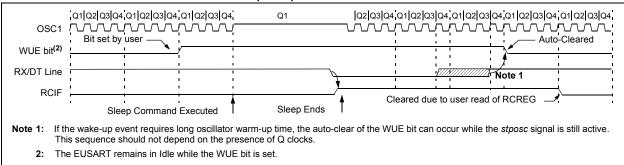

| BAUDCON              | ABDOVF                 | RCIDL                 | _                | SCKP             | BRG16              | _                  | WUE                | ABDEN              | 01-0 0-00            | 51, 156,            |

| SPBRGH               | EUSART Bau             | id Rate Gener         | ator Register I  | ligh Byte        |                    |                    |                    |                    | 0000 0000            | 50, 157             |

| SPBRG                | EUSART Bau             | id Rate Gener         | ator Register I  | _ow Byte         |                    |                    |                    |                    | 0000 0000            | 50, 157             |

| RCREG                | EUSART Rec             | eive Register         |                  |                  |                    |                    |                    |                    | 0000 0000            | 50, 165             |

| TXREG                | EUSART Trai            | nsmit Register        |                  |                  |                    |                    |                    |                    | 0000 0000            | 51, 163             |

| TXSTA                | CSRC                   | TX9                   | TXEN             | SYNC             | SENDB              | BRGH               | TRMT               | TX9D               | 0000 0010            | 51, 154             |

| RCSTA                | SPEN                   | RX9                   | SREN             | CREN             | ADDEN              | FERR               | OERR               | RX9D               | 0000 000x            | 51, 155             |

| EECON2               | Data Memory            | Control Regis         | ster 2 (not a ph | nysical register | .)                 |                    |                    |                    | 0000 0000            | 51, 74              |

| EECON1               | —                      | CFGS                  |                  | FREE             | WRERR              | WREN               | WR                 |                    | -x-0 x00-            | 51, 75              |

| IPR2                 | OSCFIP                 | _                     | USBIP            | -                | —                  | HLVDIP             | —                  |                    | 1-11                 | 51, 95              |

| PIR2                 | OSCFIF                 | _                     | USBIF            | -                | —                  | HLVDIF             | —                  |                    | 0-00                 | 51, 91              |

| PIE2                 | OSCFIE                 | —                     | USBIE            | —                | —                  | HLVDIE             | —                  | —                  | 0-00                 | 51, 93              |

| IPR1                 | —                      | ADIP                  | RCIP             | TXIP             | _                  | CCP1IP             | TMR2IP             | TMR1IP             | -111 -111            | 51, 94              |

| PIR1                 | _                      | ADIF                  | RCIF             | TXIF             | _                  | CCP1IF             | TMR2IF             | TMR1IF             | -000 -000            | 51, 90              |

| PIE1                 | _                      | ADIE                  | RCIE             | TXIE             | _                  | CCP1IE             | TMR2IE             | TMR1IE             | -000 -000            | 51, 92              |

| TRISE <sup>(3)</sup> | —                      | _                     | _                | _                | _                  | TRISE2             | TRISE1             | TRISE0             | 111                  | 51, 110             |

| TRISD <sup>(3)</sup> | TRISD7                 | TRISD6                | TRISD5           | TRISD4           | TRISD3             | TRISD2             | TRISD1             | TRISD0             | 1111 1111            | 51, 108             |

| TRISC                | TRISC7                 | TRISC6                | _                | _                | _                  | TRISC2             | TRISC1             | TRISC0             | 11111                | 51, 106             |

| TRISB                | TRISB7                 | TRISB6                | TRISB5           | TRISB4           | TRISB3             | TRISB2             | TRISB1             | TRISB0             | 1111 1111            | 51, 103             |

| TRISA                | —                      | TRISA6 <sup>(4)</sup> | TRISA5           | TRISA4           | TRISA3             | TRISA2             | TRISA1             | TRISA0             | -111 1111            | 51, 100             |

| LATE <sup>(3)</sup>  | _                      | —                     | _                | _                | _                  | LATE2              | LATE1              | LATE0              | xxx                  | 51, 110             |

| LATD <sup>(3)</sup>  | LATD7                  | LATD6                 | LATD5            | LATD4            | LATD3              | LATD2              | LATD1              | LATD0              | XXXX XXXX            | 51, 108             |

| LATC                 | LATC7                  | LATC6                 | —                | —                | —                  | LATC2              | LATC1              | LATC0              | xxxxx                | 51, 106             |

| LATB                 | LATB7                  | LATB6                 | LATB5            | LATB4            | LATB3              | LATB2              | LATB1              | LATB0              | XXXX XXXX            | 51, 103             |

| LATA                 | —                      | LATA6 <sup>(4)</sup>  | LATA5            | LATA4            | LATA3              | LATA2              | LATA1              | LATA0              | -xxx xxxx            | 51, 100             |

| PORTE                | —                      | —                     | —                | —                | RE3 <sup>(5)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> | x000                 | 51, 109             |

| PORTD <sup>(3)</sup> | RD7                    | RD6                   | RD5              | RD4              | RD3                | RD2                | RD1                | RD0                | XXXX XXXX            | 51, 108             |

#### TABLE 5-2 REGISTER FILE SUMMARY (PIC18E2450/4450) (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'. Note

1: Bit 21 of the TBLPTRU allows access to the device Configuration bits.

2: The SBOREN bit is only available when BOREN<1:0> = 0.1; otherwise, the bit reads as '0'.

These registers and/or bits are not implemented on 28-pin devices and are read as '0'. Reset values are shown for 40/44-pin devices; 3: individual unimplemented bits should be interpreted as '--

RA6 is configured as a port pin based on various primary oscillator modes. When the port pin is disabled, all of the associated bits read '0'. 4:

RE3 is only available as a port pin when the MCLRE Configuration bit is clear; otherwise, the bit reads as '0'. 5:

6: RC5 and RC4 are only available as port pins when the USB module is disabled (UCON<3> = 0).

# 5.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds eight additional two-word commands to the existing PIC18 instruction set: ADDFSR, ADDULNK, CALLW, MOVSF, MOVSS, PUSHL, SUBFSR and SUBULNK. These instructions are executed as described in Section 5.2.4 "Two-Word Instructions".

# 5.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different. This is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

#### 5.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset or Indexed Literal Offset mode. When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

## 5.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byteoriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1') or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled in shown in Figure 5-8.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 19.2.1** "Extended Instruction Syntax".

# 6.3 Reading the Flash Program Memory

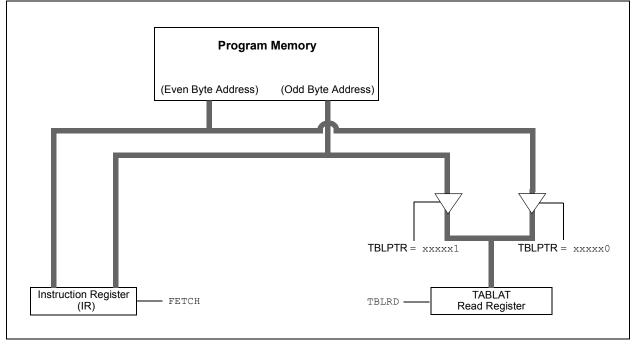

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

# FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

| READ WORD | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF  | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL |    | Load TBLPTR with the base<br>address of the word                                         |

|-----------|-----------------------------------------------------|-------------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------|

|           | TBLRD*+<br>MOVF<br>MOVWF<br>TBLRD*+<br>MOVF<br>MOVF | TABLAT, W<br>WORD_EVEN<br>TABLAT, W<br>WORD_ODD                                     | ;; | read into TABLAT and increment<br>get data<br>read into TABLAT and increment<br>get data |

| R/W-1                          | R/W-1                                                         | R/W-1            | R/W-1            | U-0              | R/W-1            | U-0             | R/W-1  |  |  |  |

|--------------------------------|---------------------------------------------------------------|------------------|------------------|------------------|------------------|-----------------|--------|--|--|--|

| RBPU                           | INTEDG0                                                       | INTEDG1          | INTEDG2          | —                | TMR0IP           | _               | RBIP   |  |  |  |

| bit 7                          |                                                               |                  |                  |                  |                  |                 | bit    |  |  |  |

|                                |                                                               |                  |                  |                  |                  |                 |        |  |  |  |

| <b>Legend:</b><br>R = Readable | bit                                                           | W = Writable     | hit              | II – I Inimplei  | mented bit, read | as '0'          |        |  |  |  |

| -n = Value at l                |                                                               | '1' = Bit is set |                  | 0' = Bit is cle  |                  | x = Bit is unki | nwn    |  |  |  |

|                                |                                                               |                  |                  |                  | arcu             |                 | 100011 |  |  |  |

| bit 7                          | RBPU: PORT                                                    | B Pull-up Ena    | ble bit          |                  |                  |                 |        |  |  |  |

|                                | 1 = All PORT                                                  | B pull-ups are   | disabled         |                  |                  |                 |        |  |  |  |

|                                | 0 = PORTB                                                     | oull-ups are en  | abled by indiv   | idual port latch | values           |                 |        |  |  |  |

| bit 6                          | INTEDG0: E>                                                   | ternal Interrup  | t 0 Edge Seleo   | ct bit           |                  |                 |        |  |  |  |

|                                | 1 = Interrupt on rising edge                                  |                  |                  |                  |                  |                 |        |  |  |  |

|                                | 0 = Interrupt on falling edge                                 |                  |                  |                  |                  |                 |        |  |  |  |

| bit 5                          | INTEDG1: External Interrupt 1 Edge Select bit                 |                  |                  |                  |                  |                 |        |  |  |  |

|                                | 1 = Interrupt on rising edge<br>0 = Interrupt on falling edge |                  |                  |                  |                  |                 |        |  |  |  |

| bit 4                          | INTEDG2: External Interrupt 2 Edge Select bit                 |                  |                  |                  |                  |                 |        |  |  |  |

|                                | 1 = Interrupt on rising edge                                  |                  |                  |                  |                  |                 |        |  |  |  |

|                                | 0 = Interrupt on falling edge                                 |                  |                  |                  |                  |                 |        |  |  |  |

| bit 3                          | Unimplemen                                                    | ted: Read as '   | 0'               |                  |                  |                 |        |  |  |  |

| bit 2                          | TMR0IP: TMI                                                   | R0 Overflow In   | terrupt Priority | / bit            |                  |                 |        |  |  |  |

|                                | 1 = High priority                                             |                  |                  |                  |                  |                 |        |  |  |  |

| 1.11.4                         | 0 = Low prior                                                 | •                | o.1              |                  |                  |                 |        |  |  |  |

| bit 1                          | Unimplemented: Read as '0'                                    |                  |                  |                  |                  |                 |        |  |  |  |

| bit 0                          | <b>RBIP:</b> RB Port Change Interrupt Priority bit            |                  |                  |                  |                  |                 |        |  |  |  |

|                                | 1 = High prio<br>0 = Low prior                                |                  |                  |                  |                  |                 |        |  |  |  |

|                                | 5 Low prior                                                   | ,                |                  |                  |                  |                 |        |  |  |  |

## REGISTER 8-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

| R/W-0           | U-0                                                                                       | R/W-0            | U-0   | U-0              | R/W-0            | U-0             | U-0   |  |  |

|-----------------|-------------------------------------------------------------------------------------------|------------------|-------|------------------|------------------|-----------------|-------|--|--|

| OSCFIE          | —                                                                                         | USBIE            | —     | —                | HLVDIE           | —               | —     |  |  |

| bit 7           |                                                                                           |                  |       |                  |                  |                 | bit 0 |  |  |

|                 |                                                                                           |                  |       |                  |                  |                 |       |  |  |

| Legend:         |                                                                                           |                  |       |                  |                  |                 |       |  |  |

| R = Readable    | bit                                                                                       | W = Writable     | bit   | U = Unimpler     | mented bit, read | as '0'          |       |  |  |

| -n = Value at F | POR                                                                                       | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

| bit 7           | bit 7 OSCFIE: Oscillator Fail Interrupt Enable bit                                        |                  |       |                  |                  |                 |       |  |  |

|                 | <ul><li>1 = Enabled</li><li>0 = Disabled</li></ul>                                        |                  |       |                  |                  |                 |       |  |  |

| bit 6           | Unimplemen                                                                                | ted: Read as '   | כי    |                  |                  |                 |       |  |  |

| bit 5           | USBIE: USB                                                                                | Interrupt Enabl  | e bit |                  |                  |                 |       |  |  |

|                 | 1 = Enabled<br>0 = Disabled                                                               |                  |       |                  |                  |                 |       |  |  |

| bit 4-3         | Unimplemen                                                                                | ted: Read as '   | D'    |                  |                  |                 |       |  |  |

| bit 2           | bit 2 HLVDIE: High/Low-Voltage Detect Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |                  |       |                  |                  |                 |       |  |  |

| bit 1-0         | Unimplemen                                                                                | ted: Read as '   | כי    |                  |                  |                 |       |  |  |

|                 |                                                                                           |                  |       |                  |                  |                 |       |  |  |

# REGISTER 8-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

# 14.0 UNIVERSAL SERIAL BUS (USB)

This section describes the details of the USB peripheral. Because of the very specific nature of the module, knowledge of USB is expected. Some high-level USB information is provided in **Section 14.9 "Overview of USB**" only for application design reference. Designers are encouraged to refer to the official specification published by the USB Implementers Forum (USB-IF) for the latest information. USB Specification Revision 2.0 is the most current specification at the time of publication of this document.

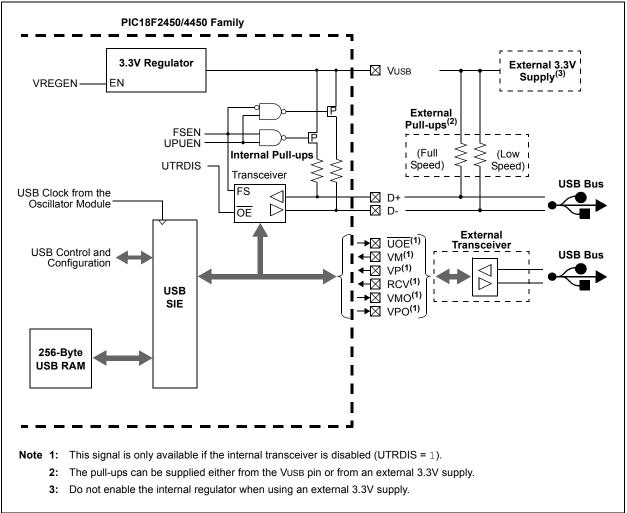

# 14.1 Overview of the USB Peripheral

The PIC18F2450/4450 device family contains a fullspeed and low-speed, compatible USB Serial Interface Engine (SIE) that allows fast communication between any USB host and the PIC<sup>®</sup> microcontroller. The SIE can be interfaced directly to the USB, utilizing the internal transceiver, or it can be connected through an external transceiver. An internal 3.3V regulator is also available to power the internal transceiver in 5V applications.

Some special hardware features have been included to improve performance. Dual port memory in the device's data memory space (USB RAM) has been supplied to share direct memory access between the microcontroller core and the SIE. Buffer descriptors are also provided, allowing users to freely program endpoint memory usage within the USB RAM space.

Figure 14-1 presents a general overview of the USB peripheral and its features.

FIGURE 14-1: USB PERIPHERAL AND OPTIONS

#### TABLE 14-1: DIFFERENTIAL OUTPUTS TO TRANSCEIVER

| VPO | VMO | Bus State         |  |  |  |

|-----|-----|-------------------|--|--|--|

| 0   | 0   | Single-Ended Zero |  |  |  |

| 0   | 1   | Differential '0'  |  |  |  |

| 1   | 0   | Differential '1'  |  |  |  |

| 1   | 1   | Illegal Condition |  |  |  |

# TABLE 14-2:SINGLE-ENDED INPUTSFROM TRANSCEIVER

| VP | VM | Bus State         |  |  |  |

|----|----|-------------------|--|--|--|

| 0  | 0  | Single-Ended Zero |  |  |  |

| 0  | 1  | Low Speed         |  |  |  |

| 1  | 0  | High Speed        |  |  |  |

| 1  | 1  | Error             |  |  |  |

The  $\overline{\text{UOE}}$  signal toggles the state of the external transceiver. This line is pulled low by the device to enable the transmission of data from the SIE to an external device.

### 14.2.2.3 Internal Pull-up Resistors

The PIC18F2450/4450 devices have built-in pull-up resistors designed to meet the requirements for low-speed and full-speed USB. The UPUEN bit (UCFG<4>) enables the internal pull-ups. Figure 14-1 shows the pull-ups and their control.

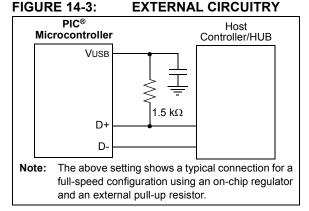

#### 14.2.2.4 Pull-up Resistors

The PIC18F2450/4450 devices require an external pull-up resistor to meet the requirements for low-speed and full-speed USB. Either an external 3.3V supply or the VUSB pin may be used to pull up D+ or D-. The pull-up resistor must be 1.5 k $\Omega$  (±5%) as required by the USB specifications. Figure 14-3 shows an example with the VUSB pin.

# 14.2.2.5 Ping-Pong Buffer Configuration

The usage of ping-pong buffers is configured using the PPB1:PPB0 bits. Refer to **Section 14.4.4 "Ping-Pong Buffering"** for a complete explanation of the ping-pong buffers.

# 14.2.2.6 USB Output Enable Monitor

The USB  $\overline{OE}$  monitor provides indication as to whether the SIE is listening to the bus or actively driving the bus. This is enabled by default when using an external transceiver or when UCFG<6> = 1.

The USB  $\overline{\text{OE}}$  monitoring is useful for initial system debugging, as well as scope triggering during eye pattern generation tests.

# 14.2.2.7 Eye Pattern Test Enable

An automatic eye pattern test can be generated by the module when the UCFG<7> bit is set. The eye pattern output will be observable based on module settings, meaning that the user is first responsible for configuring the SIE clock settings, pull-up resistor and Transceiver mode. In addition, the module has to be enabled.

Once UTEYE is set, the module emulates a switch from a receive to transmit state and will start transmitting a J-K-J-K bit sequence (K-J-K-J for full speed). The sequence will be repeated indefinitely while the Eye Pattern Test mode is enabled.

Note that this bit should never be set while the module is connected to an actual USB system. This test mode is intended for board verification to aid with USB certification tests. It is intended to show a system developer the noise integrity of the USB signals which can be affected by board traces, impedance mismatches and proximity to other system components. It does not properly test the transition from a receive to a transmit state. Although the eye pattern is not meant to replace the more complex USB certification test, it should aid during first order system debugging.

# 14.2.2.8 Internal Regulator

The PIC18F2450/4450 devices have a built-in 3.3V regulator to provide power to the internal transceiver and provide a source for the external pull-ups. An external 220 nF (±20%) capacitor is required for stability.

| Note: | The drive from VUSB is sufficient to only    |

|-------|----------------------------------------------|

|       | drive an external pull-up in addition to the |

|       | internal transceiver.                        |

The regulator is disabled by default and can be enabled through the VREGEN Configuration bit. When enabled, the voltage is visible on pin VUSB. When the regulator is disabled, a 3.3V source must be provided through the VUSB pin for the internal transceiver. If the internal transceiver is disabled, VUSB is not used.

- Note 1: Do not enable the internal regulator if an external regulator is connected to VUSB.

- VDD must be greater than or equal to VUSB at all times, even with the regulator disabled.

### 14.2.4 USB ENDPOINT CONTROL

Each of the 16 possible bidirectional endpoints has its own independent control register, UEPn (where 'n' represents the endpoint number). Each register has an identical complement of control bits. The prototype is shown in Register 14-4.

The EPHSHK bit (UEPn<4>) controls handshaking for the endpoint; setting this bit enables USB handshaking. Typically, this bit is always set except when using isochronous endpoints.

The EPCONDIS bit (UEPn<3>) is used to enable or disable USB control operations (SETUP) through the endpoint. Clearing this bit enables SETUP transactions. Note that the corresponding EPINEN and EPOUTEN bits must be set to enable IN and OUT transactions. For Endpoint 0, this bit should always be cleared since the USB specifications identify Endpoint 0 as the default control endpoint.

The EPOUTEN bit (UEPn<2>) is used to enable or disable USB OUT transactions from the host. Setting this bit enables OUT transactions. Similarly, the EPINEN bit (UEPn<1>) enables or disables USB IN transactions from the host.

The EPSTALL bit (UEPn<0>) is used to indicate a STALL condition for the endpoint. If a STALL is issued on a particular endpoint, the EPSTALL bit for that endpoint pair will be set by the SIE. This bit remains set until it is cleared through firmware, or until the SIE is reset.

| U-0   | U-0 | U-0 | R/W-0  | R/W-0    | R/W-0   | R/W-0  | R/W-0                  |

|-------|-----|-----|--------|----------|---------|--------|------------------------|

| —     | —   | -   | EPHSHK | EPCONDIS | EPOUTEN | EPINEN | EPSTALL <sup>(1)</sup> |

| bit 7 |     |     |        |          |         |        | bit 0                  |

|       |     |     |        |          |         |        |                        |

# REGISTER 14-4: UEPn: USB ENDPOINT n CONTROL REGISTER (UEP0 THROUGH UEP15)

| Legend:    |                  |                                      |                                |                        |  |  |  |

|------------|------------------|--------------------------------------|--------------------------------|------------------------|--|--|--|

| R = Reada  | ble bit          | W = Writable bit                     | U = Unimplemented bit          | , read as '0'          |  |  |  |

| -n = Value | at POR           | '1' = Bit is set                     | '0' = Bit is cleared           | x = Bit is unknown     |  |  |  |

| bit 7-5    | Unimple          | mantad Daad as '0'                   |                                |                        |  |  |  |

|            | •                | emented: Read as '0'                 |                                |                        |  |  |  |

| bit 4      |                  | K: Endpoint Handshake Enablight      | ble bit                        |                        |  |  |  |

|            |                  | point handshake enabled              |                                |                        |  |  |  |

|            | 0 <b>= End</b> j | ooint handshake disabled (ty         | pically used for isochronous e | ndpoints)              |  |  |  |

| bit 3      | EPCON            | DIS: Bidirectional Endpoint C        | control bit                    |                        |  |  |  |

|            | <u>If EPOU</u>   | EN = 1 and EPINEN = 1:               |                                |                        |  |  |  |

|            | 1 <b>= Disa</b>  | ble Endpoint n from control ti       | ransfers; only IN and OUT trai | nsfers allowed         |  |  |  |

|            | 0 <b>= Ena</b> l | ole Endpoint n for control (SE       | TUP) transfers; IN and OUT     | transfers also allowed |  |  |  |

| bit 2      | EPOUTI           | EN: Endpoint Output Enable           | bit                            |                        |  |  |  |

|            | 1 = End          | point n output enabled               |                                |                        |  |  |  |

|            | 0 = End          | point n output disabled              |                                |                        |  |  |  |

| bit 1      | EPINEN           | : Endpoint Input Enable bit          |                                |                        |  |  |  |

|            | 1 = Endi         | point n input enabled                |                                |                        |  |  |  |

|            |                  | point n input disabled               |                                |                        |  |  |  |

| bit 0      | -                | PSTALL: Endpoint Stall Indicator bit |                                |                        |  |  |  |

|            | 1 = End          | point n has issued one or mo         | re STALL packets               |                        |  |  |  |

|            |                  | point n has not issued any ST        | •                              |                        |  |  |  |

### 14.4.1.3 BDnSTAT Register (SIE Mode)

When the BD and its buffer are owned by the SIE, most of the bits in BDnSTAT take on a different meaning. The configuration is shown in Register 14-6. Once UOWN is set, any data or control settings previously written there by the user will be overwritten with data from the SIE.

The BDnSTAT register is updated by the SIE with the token Packet Identifier (PID) which is stored in BDnSTAT<5:3>. The transfer count in the corresponding BDnCNT register is updated. Values that overflow the 8-bit register carry over to the two most significant digits of the count, stored in BDnSTAT<1:0>.

#### 14.4.2 BD BYTE COUNT

The byte count represents the total number of bytes that will be transmitted during an IN transfer. After an IN transfer, the SIE will return the number of bytes sent to the host.

For an OUT transfer, the byte count represents the maximum number of bytes that can be received and stored in USB RAM. After an OUT transfer, the SIE will return the actual number of bytes received. If the number of bytes received exceeds the corresponding

byte count, the data packet will be rejected and a NAK handshake will be generated. When this happens, the byte count will not be updated.

The 10-bit byte count is distributed over two registers. The lower 8 bits of the count reside in the BDnCNT register. The upper two bits reside in BDnSTAT<1:0>. This represents a valid byte range of 0 to 1023.

### 14.4.3 BD ADDRESS VALIDATION

The BD Address register pair contains the starting RAM address location for the corresponding endpoint buffer. For an endpoint starting location to be valid, it must fall in the range of the USB RAM, 400h to 4FFh. No mechanism is available in hardware to validate the BD address.

If the value of the BD address does not point to an address in the USB RAM, or if it points to an address within another endpoint's buffer, data is likely to be lost or overwritten. Similarly, overlapping a receive buffer (OUT endpoint) with a BD location in use can yield unexpected results. When developing USB applications, the user may want to consider the inclusion of software-based address validation in their code.

#### REGISTER 14-6: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER (BD0STAT THROUGH BD63STAT), SIE MODE (DATA RETURNED BY THE SIDE TO THE MICROCONTROLLER)

| R/W-x | U-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| UOWN  | —   | PID3  | PID2  | PID1  | PID0  | BC9   | BC8   |