# E·XFL

Welcome to E-XFL.COM

Understanding <u>Embedded - Microcontroller,</u> <u>Microprocessor, FPGA Modules</u>

Embedded - Microcontroller, Microprocessor, and FPGA Modules are fundamental components in modern electronic systems, offering a wide range of functionalities and capabilities. Microcontrollers are compact integrated circuits designed to execute specific control tasks within an embedded system. They typically include a processor, memory, and input/output peripherals on a single chip. Microprocessors, on the other hand, are more powerful processing units used in complex computing tasks, often requiring external memory and peripherals. FPGAs (Field Programmable Gate Arrays) are highly flexible devices that can be configured by the user to perform specific logic functions, making them invaluable in applications requiring customization and adaptability.

Applications of Embedded - Microcontroller,

#### Details

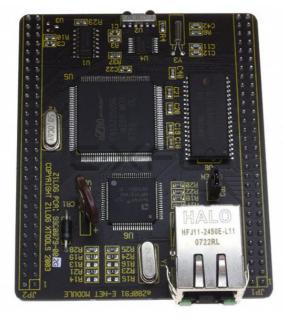

| Product Status        | Obsolete                                                   |

|-----------------------|------------------------------------------------------------|

| Module/Board Type     | MCU, Ethernet Core                                         |

| Core Processor        | eZ80F91                                                    |

| Co-Processor          | -                                                          |

| Speed                 | 50MHz                                                      |

| Flash Size            | 256KB (Internal), 1MB (External)                           |

| RAM Size              | 8KB (Internal), 512KB (External)                           |

| Connector Type        | Header 2x30                                                |

| Size / Dimension      | 2.5" x 3.1" (63.5mm x 78.7mm)                              |

| Operating Temperature | 0°C ~ 70°C                                                 |

| Purchase URL          | https://www.e-xfl.com/product-detail/zilog/ez80f915050modg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog <sub>13</sub>

|         |     |                |    |     |         |        | (a)         |

|---------|-----|----------------|----|-----|---------|--------|-------------|

| Table 2 | Pin | Identification | on | the | e/80+91 | Device | (Continued) |

|         |     | lacintinoution |    | the |         | Device | (Continued) |

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function                             | Signal Direction  | Description                                                                                                                                                                                                                                                                                  |

|----------------|---------------|-----------------|--------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 78             | K12           | PD5             | GPIO Port D                          | Bidirectional     | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually a<br>an interrupt input. Each Port D pin,<br>when programmed as output is<br>selected to be an open-drain or oper<br>source output. Port D is multiplexed<br>with one UART.  |

|                |               | DSRO            | Data Set<br>Ready                    | Input, Active Lov | <ul> <li>Modematus signal to the UART.</li> <li>This signal is multiplexed with PD5.</li> </ul>                                                                                                                                                                                              |

| 79             | K11           | PD6             | GPIO Port D                          | Bidirectional     | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port D pin,<br>when programmed as output is<br>selected to be an open-drain or open<br>source output. Port D is multiplexed<br>with one UART. |

|                |               | DCDO            | Data Carrier<br>Detect               | Input, Active Lov | <ul> <li>Modematus signal to the UART.</li> <li>This signal is multiplexed with PD6.</li> </ul>                                                                                                                                                                                              |

| 80             | H8            | PD7             | GPIO Port D                          | Bidirectional     | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port D pin,<br>when programmed as output is<br>selected to be an open-drain or open<br>source output. Port D is multiplexed<br>with one UART. |

|                |               | RIO             | Ring Indicator                       | Input, Active Lo  | ow Modem status signal to the UART.<br>This signal is multiplexed with PD7.                                                                                                                                                                                                                  |

| 81             | J11           | V <sub>DD</sub> | Power Supply                         |                   | Power Supply.                                                                                                                                                                                                                                                                                |

| 82             | J12           | Vss             | Ground                               |                   | Ground.                                                                                                                                                                                                                                                                                      |

| 83             | J10           | LOOP_FILT       | PLL Loop Filter                      | Analog            | Loop Filter pin for the Analog PLL.                                                                                                                                                                                                                                                          |

| 84             | G7            | $PLL_V_{SS}$    | Ground                               |                   | Ground for Analog PLL.                                                                                                                                                                                                                                                                       |

| 85             | H12           | Хоит            | System Clock<br>Oscillator<br>Output | Output            | This pin is the output of the onboar crystal oscillator. We used, a crystal must be connected between Xand $X_{OUT}$ .                                                                                                                                                                       |

| Address<br>(hex) | Mnemonic     | Name                                              | Reset<br>(hex) | CPU<br>Access | Page<br>No |

|------------------|--------------|---------------------------------------------------|----------------|---------------|------------|

| 003F             | EMAC_FIAD    | EMAC PHY Unit Select Address<br>Register          | 00             | R/W           | 316        |

| 0040             | EMAC_PTMR    | EMAC TransmiPolling Timer Register                | 00             | R/W           | 316        |

| 0041             | EMAC_RST     | EMAC Reset Control Register                       | 20             | R/W           | 317        |

| 0042             | EMAC_TLBP_L  | EMAC Transmit Lower Boundary<br>Pointer Low Byte  | 00             | R/W           | 318        |

| 0043             | EMAC_TLBP_H  | EMAC Transmit Lower Boundary<br>Pointer High Byte | 00             | R/W           | 318        |

| 0044             | EMAC_BP_L    | EMAC BoundaryPointer Low Byte                     | 00             | R/W           | 319        |

| 0045             | EMAC_BP_H    | EMAC BoundaryPointer High Byte                    | CO             | R/W           | 319        |

| 0046             | EMAC_BP_U    | EMAC BoundaryPointer Upper Byte                   | FF             | R/W           | 319        |

| 0047             | EMAC_RHBP_L  | EMAC Receive High Boundary<br>Pointer Low Byte    | 00             | R/W           | 320        |

| 0048             | EMAC_RHBP_H  | EMAC Receive High Boundary<br>Pointer High Byte   | 00             | R/W           | 321        |

| 0049             | EMAC_RRP_L   | EMAC Receive Read<br>Pointer Low Byte             | 00             | R/W           | 321        |

| 004A             | EMAC_RRP_H   | EMAC Receive Read<br>Pointer High Byte            | 00             | R/W           | 322        |

| 004B             | EMAC_BUFSZ   | EMAC Buffer Size Register                         | 00             | R/W           | 322        |

| 004C             | EMAC_IEN     | EMAC Interrupt Enable Register                    | 00             | R/W           | 323        |

| 004D             | EMAC_ISTAT   | EMAC Interrupt Status Register                    | 00             | R/W           | 325        |

| 004E             | EMAC_PRSD_L  | EMAC PHY Read Status<br>Data Low Byte             | 00             | R/W           | 326        |

| 004F             | EMAC_PRSD_H  | EMAC PHY Read Status<br>Data High Byte            | 00             | R/W           | 327        |

| 0050             | EMAC_MIISTAT | EMAC MII Status Register                          | 00             | R/W           | 327        |

| 0051             | EMAC_RWP_L   | EMAC Receive Write<br>Pointer Low Byte            | 00             | R/W           | 328        |

| 0052             | EMAC_RWP_H   | EMAC Receive Write<br>Pointer High Byte           | 00             | R/W           | 329        |

| 0053             | EMAC_TRP_L   | EMAC Transmit Read<br>Pointer Low Byte            | 00             | R/W           | 329        |

### Table 3. Register Map (Continued)

ilog

42

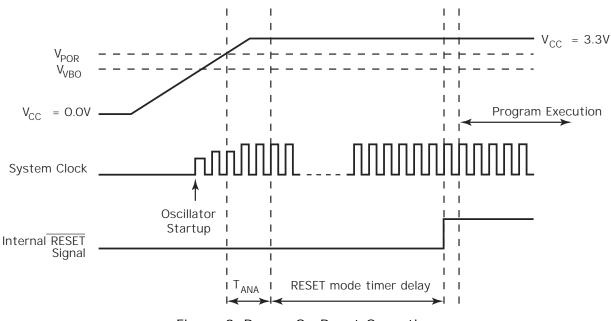

#### Power-On Reset

A POR occurs every time the supply voltage he part rises from below the Voltage Brownout threshold ( $\bigvee_{BO}$ ) to above the POR voltage threshold ( $\bigotimes_{O}$ ). The internal bandgap-referenced voltage exterior sends a continuous **ER**ET signal to the Reset controller until the supply voltage ( $\bigotimes_{O}$ ) exceeds the POR voltage threshold. After Vises above  $\bigvee_{OR}$  an on-chip analog delay element by efficient ains the RESET signal to the Reset controller. After this analog delay element by efficient out, the Reset controller holds the eZ80F91 in RESET until the RESET mode time prices. POR operation is displayed in Figure 3 The signals in Figure 3 are not drawn to scale but for displaying purposes only.

Figure 3. Power-On Reset Operation

### Voltage Brownout Reset

If the supply voltage ( $\&_C$ ) drops below the  $\bigvee_{BO}$  after program execution begins, the eZ80F91 device resets. The VBO protection uitry detects the low supply voltage and initiates a RESET via the Reset controller eZ80F91 remains in RESET until the supply voltage again returns above the POR voltage threshold wind the Reset controller releases the internal RESET signal. The VBO uitry rejects short negative brown-out pulses to prevent spurious RESET events.

VBO operation is displayed Frigure 4on page 43. The signals in the figure are not drawn to scale but for illustration purposes only.

ilog <sub>61</sub>

#### Bit INT\_PO Reset 0\* 0\* INT\_P1 Reset INT\_P2 Reset INT\_P3 Reset INT\_P4 Reset INT\_P5 Reset R/W R/W R/W R/W R/W R/W R/W R/W CPU Access

Note: X = Undefined; R/W = Read/Write, \*Unused.

| PositionValueDescription70Default Interrupt Priority |  |

|------------------------------------------------------|--|

| 7 O Default Interrupt Priority                       |  |

|                                                      |  |

| INT_PX 1 Level One Interupt Priority                 |  |

| 6 0 Default Interrupt Priority                       |  |

| INT_PX 1 Level One Interupt Priority                 |  |

| 5 0 Default Interrupt Priority                       |  |

| INT_PX 1 Level One Interupt Priority                 |  |

| 4 O Default Interrupt Priority                       |  |

| INT_PX 1 Level One Interupt Priority                 |  |

| 3 0 Default Interrupt Priority                       |  |

| INT_PX 1 Level One Interupt Priority                 |  |

| 2 0 Default Interrupt Priority                       |  |

| INT_PX 1 Level One Interupt Priority                 |  |

| 1 0 Default Interrupt Priority                       |  |

| INT_PX 1 Level One Interupt Priority                 |  |

| 0 0 Default Interrupt Priority                       |  |

| INT_PX 1 Level One Interupt Priority                 |  |

# = OO13h, $INT_P4 = OO14h$ , $INT_P5 = OO15h$ )

Table 14. Interrupt Priority Registers(INT\_PO = 0010h, INT\_P1 = 0011h, INT\_P2 = 0012h, INT\_P3

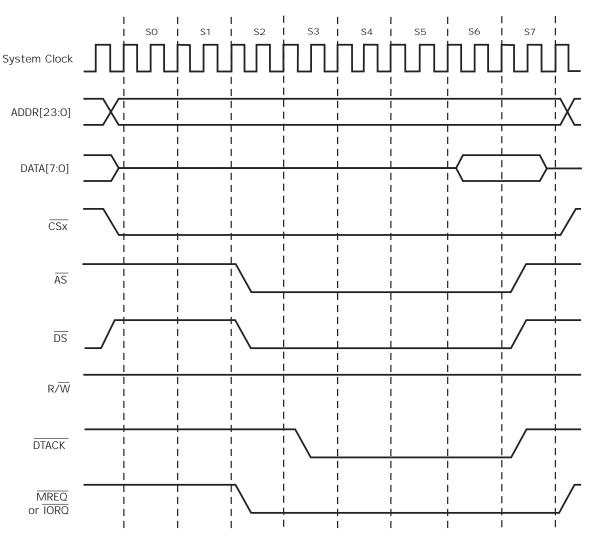

Figure 18. Example: Motorola Bus Mode Read Timing

#### 96

#### MBIST Control

There are two Memory Built-In Self-Test (MST) controllers for the RAM blocks on the eZ80F91. MBIST\_GPR is for General Bose RAM and MBIST\_EMR is for EMAC RAM. Writing a 1 to MBIST\_ON starts the MBIST testing. Writing a 0 to MBIST\_ON stops the MBIST testing. On completion the MBIST testing, MBIST\_ON is automatically reset to 0. If RAM passes MBISE sting, MBIST\_PASS is 1. The value in MBIST\_PASS is only valid when MBIST\_DONE is High. Starbole 34

Table 34. MBIST Control Register(MBIST\_GPR = 00B6h, MBIST\_EMR = 00B7h)

| Bit                                    | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------------|-----|---|---|---|---|---|---|---|

| Reset                                  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access                             | R/W | R | R | R | R | R | R | R |

| Note: R/W = Read/Write; R = Read Only. |     |   |   |   |   |   |   |   |

| Bit Position | Value | Description                           |

|--------------|-------|---------------------------------------|

| 7            | 0     | MBIST Testing of the RAM is disabled. |

| MBIST_ON     | 1     | MBIST Testing of the RAM is enabled.  |

| 6            | 0     | MBIST Testing has not completed.      |

| MBIST_DONE   | 1     | MBIST Testing has completed.          |

| 5            | 0     | MBIST Testing has failed.             |

| MBIST_PASS   | 1     | MBIST Testing has passed.             |

| [4:0]        | 00000 | Reserved.                             |

ilog <sub>124</sub>

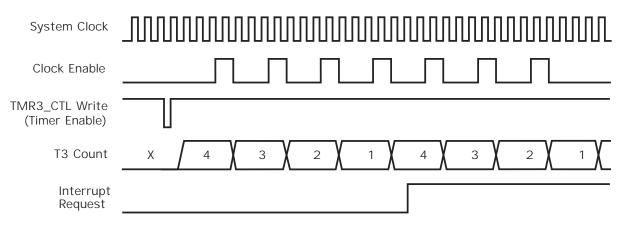

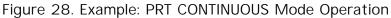

TMRx\_RR\_H and TMRx\_RR\_L. Downcounting continues on the next clock edge and the timer continues to countril disabled. An example of the timer operating in CONTINUOUS mode is displayed Frigure 28 Timer register information is listed in Table 51

| Table 5 | 1. Example: | PRT | CONTINUOUS | Mode | Parameters |

|---------|-------------|-----|------------|------|------------|

|---------|-------------|-----|------------|------|------------|

| Parameter                     | Control Register(s)     | Value |

|-------------------------------|-------------------------|-------|

| Timer Enable                  | TMRx_CTL[TIM_EN]        | 1     |

| Reload                        | TMRx_CTL[RLD]           | 1     |

| Prescaler Divider = 4         | TMXR_CTL[CLK_DIV]       | OOb   |

| CONTINUOUS Mode               | TMR x_CTL[TIM_CONT]     | 1     |

| End of Count Interrupt Enable | TIMERER[IRQ_EOC_EN]     | 1     |

| Timer Reload Value            | {TMRx_RR_H, TMR x_RR_L} | 0004h |

#### Timer Interrupts

The terminal count flag (TMR\_IIR[EOC]) is set to 1 whenever the timer reachesooh, its end-of-count value in SINGLE PASS mode when the timer reloads the start value in CONTINUOUS mode. The terminal count flaggonly set when the timer reachesooh (or reloads) from 001h. The timer interrupt flag is not step 1 when the timer is loaded with the value0000h, which selects the main mum time-out period.

The CPU is programmed to poll the EOC bitther time-out event. Alteratively, an interrupt service request signal is step the CPU by setting the TMREIER[EOC] bit to 1.

#### Timer Data Register High Byte

The Timerx Data Register—High Byte returns theigh byte of the count value of the selected timer as it existed at the time thatLow byte was read. The Timer Data Register—High Byte (seTeable 58) is read when the timer is operation. Reading the current count value does notifiect timer operation. Toread the 16-bit data of the current count value, {TMR\_DR\_H[7:0], TMRx\_DR\_L[7:0]}, first read the Timer Data Register—Low Byte followed by the TimeData Register—High Byte. The Timer Data Register—High Byte value is latched intorner storage when a Read of the Timer Data Register—Low Byte occurs.

This register shares its address with dorresponding timer reload register.

Table 58. Timer Data Register High Byte (TMRO\_DR\_H = 0064h, TMR1\_DR\_H = 0069h, TMR2\_DR\_H = 0073h, TMR3\_DR\_H = 0078h)

| Bit                | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|---|---|---|---|---|---|---|---|

| Reset              | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access         | R | R | R | R | R | R | R | R |

| Note: D. Deed only |   |   |   |   |   |   |   |   |

Note: R = Read only.

| Bit<br>Position   | Value   | Description                                                                                                                                                                                               |

|-------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>TMR_DR_H | 00h FFh | These bits represent the High byte of the 2-byte timer data value, {TMRx_DR_H[7:0], TMRx_DR_L[7:0]}. Bit 7 is bit 15 (msb) of the 16-bit timer data value. Bit 0 is bit 8 of the 16-bit timer data value. |

141

Timer Input Capture Value A Register High Byte

The Timer x Input Capture Value A Register—High Byte (Sadale 63) stores the High byte of the capture value for external input For Timer 1, the external input is ICO. For Timer 3, it is IC2.

Table 63. Timer Input Capture Value Register A High Byte (TMR1\_CAPA\_H = 006Ch, TMR3\_CAPA\_H = 007Dh)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read only. |   |   |   |   |   |   |   |   |

| Bit<br>Position      | Value   | Description                                                                                                                                                                                          |

|----------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>TMRx_CAPA_H | 00h FFh | These bits represent the High byte of the 2-byte capture value, {TMRx_CAPA_H[7:0], TMRx_CAPA_L[7:0]}. Bit 7 is bit 15 (msb) of the 16-bit data value. Bit 0 is bit 8 of the 16-bit timer data value. |

Timer Input Capture Value B Register Low Byte

The Timer x Input Capture Value B Register—Low Byte (**Sede**le 64) stores the Low byte of the capture value for external input Hor Timer 1, the exteent input is IC1. For Timer 3, it is IC3.

Table 64. Timer Input Capture Value Register B Low Byte (TMR1\_CAPB\_L = 006Dh, TMR3\_CAPB\_L = 007Eh)

| Bit                               |             | 7     | 6                                                                                                                                                                                                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------------------------------|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

| Reset                             | eset C      |       | 0                                                                                                                                                                                                  | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| CPU Access                        | PU Access R |       | R                                                                                                                                                                                                  | R | R | R | R | R | R |  |  |  |

| Note: R = Read only.              |             |       |                                                                                                                                                                                                    |   |   |   |   |   |   |  |  |  |

| Bit<br>Position Value Description |             |       |                                                                                                                                                                                                    |   |   |   |   |   |   |  |  |  |

| [7:0]<br>TMRx_CAPB_L              | 00h         | FFh b | These bits represent the Low byte of the 2-byte capture value, {TMRx_CAPB_H[7:0], TMRx_CAPB_L[7:0]}. Bit 7 is bit 7 of the 16-bit data value. Bit 0 is bit 0 (lsb) of the 16-bit timer data value. |   |   |   |   |   |   |  |  |  |

ilog

# 201

# Serial Peripheral Interface

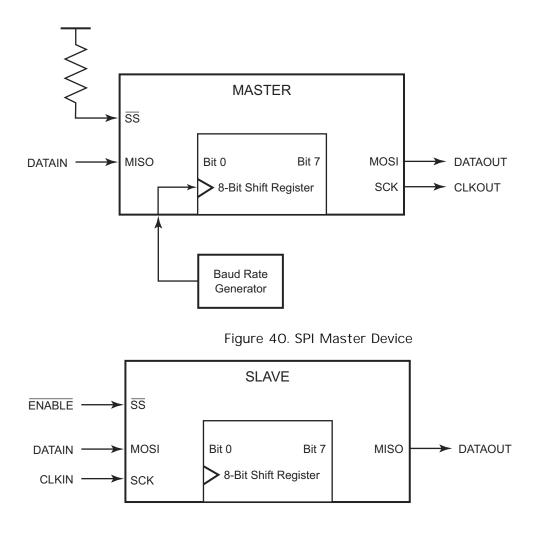

The Serial Peripheral Interface (SPI) is **acty**ronous interface allowing several SPI-type devices to be interconnected. The SPI fisladuplex, synchronous, character-oriented communication channel that employs a four-wire interface. The SPI block consists of a transmitter, receiver, baud rate generator, condrol unit. During an SPI transfer, data is sent and received simultaneously by block master and the slave SPI devices.

In a serial peripheral interface, separate signed required for data and clock. The SPI is configured either as a master or as a slable.connection of two SPI devices (one master and one slave) and the direction of data transfer is displayFeigure 40andFigure 41

Figure 41. SPI Slave Device

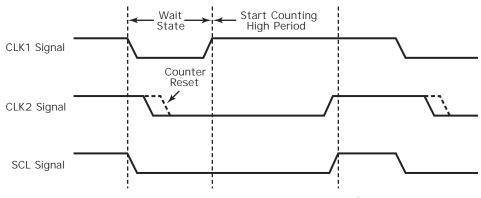

Figure 47. Clock Synchronization In <sup>2</sup>C Protocol

#### Arbitration

Any master initiates a transfer if the busiries. As a result, multiple masters each generates a START condition if the bus is freighin a minimum period. If multiple masters generate a START condition, a START is definiter the bus. Howevearbitration defines which MASTER controls the bus. Arbitrationakes place on the SDA line. As mentioned, START conditions are initiated only while the SOne is held High. If during this period, a master (M1) initiates a High-to-Low traition—that is, a START condition—while a second master (M2) transmits a Low signative line, then the first master, M1, cannot take control of the bus. As a resulte to a output stage for M1 is disabled.

Arbitration continues for many bits. Its firstage is comparison of the address bits. If the masters are each trying to address the same ederbitration continues with a comparison of the data. Because address and data information of Ctbest is used for arbitration, no information is lost uring this process. A master that loses the arbitration generates clock pulses until the end of the master in which it loses the arbitration.

If a master also incorporates a slave function dit loses arbitration during the addressing stage, it is possible that the winning masterrying to address it. The losing master must switch over immediately to its slave receiver modegure 47 displays the arbitration procedure for two masters. Of course, more present an be involved, depending on how many masters are connected to the bus. The mothent is a difference between the internal data level of the master generating DATA to the actual level of the SDA line, its data output is switched off, which means that a Hightput level is the connected to the bus. As a result, the data transfer initiated by thinning master is not affected. Because control of the fC bus is decided solely on the addressed data sent by competing masters, there is no central master, nor any order of priority on the bus.

Special attention must beaid if, during a serial transfethe arbitration procedure is still in progress at the moment when a repeated RT condition or a STOP condition is transmitted to the fC bus. If it is possible for such a sation to occur, the masters involved

ilog

227

| Bit<br>Position | Value | Description                                         |  |  |  |  |

|-----------------|-------|-----------------------------------------------------|--|--|--|--|

| 5               | 0     | Master mode START condition is sent.                |  |  |  |  |

| STA             | 1     | Master mode start-trans®TiART condition on the bus. |  |  |  |  |

| 4               | 0     | Master mode STOP condition is sent.                 |  |  |  |  |

| STP             | 1     | Master mode stop-transmit STOP condition on the bus |  |  |  |  |

| 3               | 0     | <sup>2</sup> C interrupt flag is not set.           |  |  |  |  |

| IFLG            | 1     | I <sup>2</sup> C interrupt flag is set.             |  |  |  |  |

| 2               | 0     | Not Acknowledge.                                    |  |  |  |  |

| ААК             | 1     | Acknowledge.                                        |  |  |  |  |

| [1:0]           | 00    | Reserved.                                           |  |  |  |  |

I<sup>2</sup>C Status Register

The  $f^2C\_SR$  register is a Read Only register **trat**tains a 5-bit status code in the five MSbs; the three LSbs are always 0. The **Ready** I2C\_SR registers share the same I/ O addresses as the Write Only I2C\_CCR registers**Table** 128

| Table 128. PC Status Registers(I2C_SR = 00CCh) |

|------------------------------------------------|

|------------------------------------------------|

| -                    |       | r    |                        |         |      |   |   |   |   |  |  |

|----------------------|-------|------|------------------------|---------|------|---|---|---|---|--|--|

| Bit                  |       | 7    | 6                      | 5       | 4    | 3 | 2 | 1 | 0 |  |  |

| Reset 1              |       |      | 1                      | 1       | 1    | 1 | 0 | 0 | 0 |  |  |

| CPU Access R         |       |      | R                      | R       | R    | R | R | R | R |  |  |

| Note: R = Read only. |       |      |                        |         |      |   |   |   |   |  |  |

|                      |       |      |                        |         |      |   |   |   |   |  |  |

| Bit                  |       |      |                        |         |      |   |   |   |   |  |  |

| Position             | Value | e De | escriptio              | n       |      |   |   |   |   |  |  |

| [7:3]                | 000   | 00 5 | -bit <sup>2</sup> 1C s | tatus c | ode. |   |   |   |   |  |  |

| STAT                 | 1111  | 1    |                        |         |      |   |   |   |   |  |  |

| [2:0]                | 000   | )    | Reserve                | d.      |      |   |   |   |   |  |  |

There are 29 possible status codes, as listed bite 129 When the  $C_SR$  register contains the status codeh, no relevant status information available, no interrupt is generated, and the LG bit in the  $C_CTL$  register is not set. All other status codes correspond to a defined state of the I

ilog <sub>240</sub>

| ZDI Address | ZDI Register Name | ZDI Register Function       | Reset<br>Value |

|-------------|-------------------|-----------------------------|----------------|

| 08h         | ZDI_ADDR2_L       | Address Match 2 Low Byte    | XXh            |

| 09h         | ZDI_ADDR2_H       | Address Match 2 High Byte   | XXh            |

| OAh         | ZDI_ADDR2_U       | Address Match 2 Upper Byte  | XXh            |

| OCh         | ZDI_ADDR3_L       | Address Match 3 Low Byte    | XXh            |

| ODh         | ZDI_ADDR3_H       | Address Match 3 High Byte   | XXh            |

| OEh         | ZDI_ADDR3_U       | Address Match 4 Upper Byte  | XXh            |

| 10h         | ZDI_BRK_CTL       | Break Control Register      | 00h            |

| 11h         | ZDI_MASTER_CTL    | Master Control Register     | 00h            |

| 13h         | ZDI_WR_DATA_L     | Write Data Low Byte         | XXh            |

| 14h         | ZDI_WR_DATA_H     | Write Data High Byte        | XXh            |

| 15h         | ZDI_WR_DATA_U     | Write Data Upper Byte       | XXh            |

| 16h         | ZDI_RW_CTL        | Read/Write Control Register | OOh            |

| 17h         | ZDI_BUS_CTL       | Bus Control Register        | 00h            |

| 21h         | ZDI_IS4           | Instruction Store 4         | XXh            |

| 22h         | ZDI_IS3           | Instruction Store 3         | XXh            |

| 23h         | ZDI_IS2           | Instruction Store 2         | XXh            |

| 24h         | ZDI_IS1           | Instruction Store 1         | XXh            |

| 25h         | ZDI_ISO           | Instruction Store 0         | XXh            |

| 30h         | ZDI_WR_MEM        | Write Memory Register       | XXh            |

Table 133. ZDI Write Only Registers (Continued)

## ZDI Read Only Registers

Table 134lists the ZDI Read Only registers. Maof the ZDI Read Only addresses are shared with ZDI Write Only registers.

Table 134. ZDI Read Only Registers

| ZDI Address | ZDI Register Name | ZDI Register Function                           | Reset<br>Value |

|-------------|-------------------|-------------------------------------------------|----------------|

| 00h         | ZDI_ID_L          | eZ80 <sup>fi</sup> Product ID Low Byte Register | 08h            |

| 01h         | ZDI_ID_H          | eZ80 Product ID High Byte Register              | 00h            |

| 02h         | ZDI_ID_REV        | eZ80 Product ID Revision Register               | XXh            |

> ilog 283

#### Table 170. Opcode Map Second Opcode After OEDh

Legend Lower Nibble of 2nd Opcode ¥

2

Upper Nibble of Second Opcode

4 SBC HL,BC Mnemonic

First Operand Second Operand

|   |          |           | _           | _            |          | _       |      | .ower Ni    |          |           |       | _            |          | _     | _       |            |

|---|----------|-----------|-------------|--------------|----------|---------|------|-------------|----------|-----------|-------|--------------|----------|-------|---------|------------|

| 0 | 0<br>INO | 1<br>OUTO | 2<br>LEA    | 3<br>LEA     | 4<br>TST | 5       | 6    | 7<br>LD BC, | 8<br>INO | 9<br>OUTO | A     | В            | C<br>TST | D     | E       | LD         |

| 0 | B,(n)    | (n),B     | BC,<br>IX+d | BC,<br>IY+d  | A,B      |         |      | (HL)        | C,(n)    | (n),C     |       |              | A,C      |       |         | (HL<br>BC  |

| 1 | INO      | OUTO      | LEA         | LEA          | TST      |         |      | LD DE,      | INO      | OUTO      |       |              | TST      |       |         | LD(F       |

|   | D,(n)    | (n),D     | DE,<br>IX+d | DE,<br>IY+d  | A,D      |         |      | (HL)        | E,(n)    | (n),E     |       |              | A,E      |       |         | DE         |

| 2 | INO      |           | LEA HL      |              | TST      |         |      | LD HL,      | INO      | OUTO      |       |              | TST      |       |         | LC         |

|   | H,(n)    | (n),H     | ,IX+d       | ,IY+d        | A,H      |         |      | (HL)        | L,(n)    | (n),L     |       |              | A,L      |       |         | (HL<br>HI  |

| 3 |          | LD IY,    |             |              | TST      |         |      | LD IX,      | INO      | OUTO      |       |              | TST      |       | LD      |            |

|   |          | (HL)      | ,IX+d       | ,IY+d        | A,(HL)   |         |      | (HL)        | A,(n)    | (n),A     |       |              | A,A      |       | (HL),IY | (HI)<br>IX |

| 4 | IN       | OUT       | SBC         | LD           | NEG      | RETN    | IM 0 | LD          | IN       | OUT       | ADC   | LD           | MLT      | RETI  |         | LD         |

| _ | B,(BC)   | (BC),B    |             | (Mmn),<br>BC |          |         |      | I,A         | C,(C)    | (C),C     | HL,BC | BC,<br>(Mmn) |          |       |         | R,         |

| 5 | IN       | OUT       | SBC         |              | LEA IX,  | LEA IY, | IM 1 | LD          | IN       | OUT       | ADC   | LD           | MLT      |       | IM 2    | L          |

|   | D,(BC)   | (BC),D    |             | (Mmn),<br>DE |          | IX+d    |      | A,I         | E,(C)    | (C),E     | HL,DE | DE,<br>(Mmn) |          |       |         | A,I        |

| 6 | IBN      | OUT       | SBC         | LD           | TST      | PEA     | PEA  | RRD         | IN       | OUT       | ADC   | LD           | MLT      | LD    | LD      | RL         |

|   | H,(C)    | (BC),H    |             | (Mmn),<br>HL | A,n      | IX+d    | IY+d |             | L,(C)    | (C),L     | HL,HL | HL,<br>(Mmn) |          | MB,A  | A,MB    |            |

| 7 |          |           | SBC         | LD           | TSTIO    |         | SLP  |             | IN       | OUT       | ADC   | LD           | MLT      | STMIX | RSMIX   |            |

|   |          |           | HL,SP       | (Mmn),<br>SP | n        |         |      |             | A,(C)    | (C),A     | HL,SP | SP,<br>(Mmn) |          |       |         |            |

| 8 |          |           | INIM        | ΟΤΙΜ         | INI2     |         |      |             |          |           | INDM  |              |          |       |         |            |

| 9 |          |           | INIMR       | OTIMR        | INI2R    |         |      |             |          |           | INDMR | OTDMR        | IND2R    |       |         |            |

| А | LDI      | CPI       | INI         | OUTI         | OUTI2    |         |      |             | LDD      | CPD       | IND ( | OUTD O       | UTD2     |       |         |            |

| В | LDIR     | CPIR      | INIR        | OTIR (       | DTI2R    |         |      | l           | DDR C    | PDR II    | NDR O | TDR OTI      | D2R      |       |         |            |

| С |          |           | INIRX       | OTIRX        |          |         |      | LD          |          |           | INDRX | OTDRX        |          |       |         |            |

| D |          |           |             |              |          |         |      | I,HL<br>LD  |          |           |       |              |          |       |         |            |

| E |          |           |             |              |          |         |      | HL,I        |          |           |       |              |          |       |         |            |

|   |          |           |             |              |          |         |      |             |          |           |       |              |          |       |         |            |

| F |          | n = 8     |             |              |          |         |      |             |          |           |       |              |          |       |         |            |

Note: n = 8-bit data; Mmn = 16- or 24-bit addataod = 8-bit two s-complement displacement.

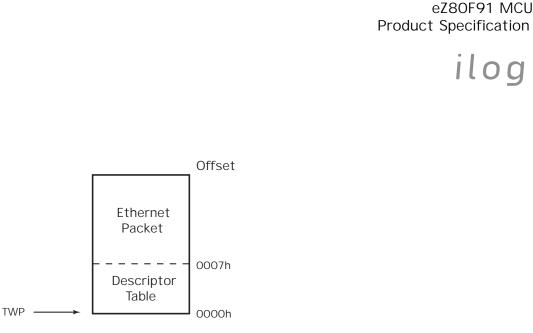

Note: For an official description of an Ethecket, pefer to IEEE 802.3 specification, Figure 3-1.

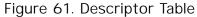

The descriptor table contains three entribe:next pointer (NP), the packet size (Pkt\_Size), and the packet status (Stat), as display Figure 62

Figure 62. Descriptor Table Entries

NP is a 24-bit pointer to the start of the next cket. Pkt\_Size contains the number of bytes of data in the Ethernet packet, including four CRC bytes, budoes not contain the seven descriptor table bytes. Stat containstances of the packet. Stat differs for Transmit and Receive packets. Statel 1780n page 295 and able 1790n page 295.

294

ilog

316

#### EMAC PHY Unit Select Address Register

The EMAC PHY Unit Select Address Registeriows the selection of nultiple connected external PHY devices. Selected 202

Table 202. EMAC PHY Unit Select Address Register(EMAC\_FIAD = 003Fh)

| Bit                                    |        | 7      | 6       | 5        | 4       | 3        | 2       | 1      | 0       |  |

|----------------------------------------|--------|--------|---------|----------|---------|----------|---------|--------|---------|--|

| Reset                                  |        | 0      | 0       | 0        | 0       | 0        | 0       | 0      | 0       |  |

| CPU Access                             |        | R      | R       | R        | R/W     | R/W      | R/W     | R/W    | R/W     |  |

| Note: R = Read Only; R/W = Read/Write. |        |        |         |          |         |          |         |        |         |  |

| Bit                                    |        |        |         |          |         |          |         |        |         |  |

| Position                               | Value  | Desc   | ription |          |         |          |         |        |         |  |

| [7:5]                                  | 000    | Res    | served. |          |         |          |         |        |         |  |

| [4:0]<br>FIAD                          | 00h 1F | h Prog | rammal  | ole 5-bi | t value | that sel | ects an | extern | al PHY. |  |

EMAC Transmit Polling Timer Register

This register sets the Transmit Polling **Beri**n increments of PTMR = SYSCLK  $\div$  256. Whenever this register is written, the statistic Transmit Buffer Descriptor is checked to determine if the EMAC owns the Transmitflet It then rechecks this status every TPTMR (calculated by TPTMR x EMAC\_PTR[7:0]). The Transmit Polling Timer is disabled if this register is set tooh (which also disables the transmitting of packets). If a transmission is in progressment EMAC\_PTMR is set tooh, the transmission will complete. See Table 203

Table 203. EMAC Transmit Polling Timer Register (EMAC\_PTMR = 0040h)

| Bit                                                     |     | 7   | 6   | 5     | 4     | 3 | 2 | 1 | 0 |  |  |

|---------------------------------------------------------|-----|-----|-----|-------|-------|---|---|---|---|--|--|

| Reset                                                   | 0   | 0   | 0   | 0     | 0     | 0 | 0 | 0 |   |  |  |

| CPU Access                                              | R/W | R/W | R/W | / R/W | / R/W |   |   |   |   |  |  |

| Note: R/W = Read/Write.                                 |     |     |     |       |       |   |   |   |   |  |  |

| Bit<br>Position Value Description                       |     |     |     |       |       |   |   |   |   |  |  |

| [7:0] OOh FFh The Transmit polling period.<br>EMAC_PTMR |     |     |     |       |       |   |   |   |   |  |  |

# ilog <sub>327</sub>

| Bit                               | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------------------------------|---|---|---|---|---|---|---|---|--|--|--|

| Reset                             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| CPU Access                        | R | R | R | R | R | R | R | R |  |  |  |

| Note: R = Read Only.              |   |   |   |   |   |   |   |   |  |  |  |

| Bit<br>Position Value Description |   |   |   |   |   |   |   |   |  |  |  |

| [7:0] O<br>EMAC_PRSD_H            |   |   |   |   |   |   |   |   |  |  |  |

Table 218. EMAC PHY Read Status Data Register High Byte (EMAC\_PRSD\_H = 004Fh)

EMAC MII Status Register

The EMAC MII Status Register is used to the current state of the external PHY device. Set able 219

Table 219. EMAC MII Status Registe(EMAC\_MIISTAT = 0050h)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read Only. |   |   |   |   |   |   |   |   |

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>BUSY       | 1     | MII management operation in progress Busy. This status bit<br>goes busy whenever the LCTLD (PHY Write) or the RSTAT<br>(PHY Read) is set in the EMAC_MIIMGT register. It is<br>negated when the Write or Read operation to the PHY has<br>completed. In SCANmode, the BUSY will be asserted until<br>the SCAN is disabled. Us the EmacIStat[MGTDONE]<br>interrupt status bot determine whethe data is valid. |

|                 | 0     | Not Busy.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6               | 1     | Local copy of PHY Link fail bit.                                                                                                                                                                                                                                                                                                                                                                             |

| MIILF           | 0     | PHY Link OK.                                                                                                                                                                                                                                                                                                                                                                                                 |

# ilog <sub>336</sub>

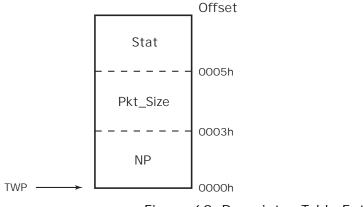

Figure 63. Recommended Crystal Oscillator Configuration 50 MHz Operation

### Table 229. Recommended Crystal Oscillator Specifications 1 MHz Operation

| Parameter              | Frequency<br>Dependent Value | Units | Comments |

|------------------------|------------------------------|-------|----------|

| Frequency              | 1                            | MHz   |          |

| Resonance              | Parallel                     |       |          |

| Mode                   | Fundamental                  |       |          |

| Series Resistance (Rg) | 750                          | Ohms  | Maximum  |

| Load Capacitance (C)   | 13                           | рF    | Maximum  |

ilog

# Table 229. Recommended Crystal Oscillator Specifications 1 MHz Operation (Continued)

| Parameter           | Frequency<br>Dependent Value | Units | Comments |

|---------------------|------------------------------|-------|----------|

| Shunt Capacitance 😡 | 7                            | pF    | Maximum  |

| Drive Level         | 1                            | mW    | Maximum  |

#### Table 230. Recommended Crystal Oscillator Specifications 10 MHz Operation

| Frequency       |                                                              | Commente                          |

|-----------------|--------------------------------------------------------------|-----------------------------------|

| Dependent value | Units                                                        | Comments                          |

| 10              | MHz                                                          |                                   |

| Parallel        |                                                              |                                   |

| Fundamental     |                                                              |                                   |

| 35              | Ohms                                                         | Maximum                           |

| 30              | pF                                                           | Maximum                           |

| 7               | рF                                                           | Maximum                           |

| 1               | mW                                                           | Maximum                           |

|                 | Dependent Value<br>10<br>Parallel<br>Fundamental<br>35<br>30 | Dependent ValueUnits10MHzParallel |

### 32 kHz Real-Time Clock Crystal Oscillator Operation

Figure 64on page 338 displays a recommended configuration for connecting the Real-Time Clock oscillator with an external 32 kH undamental mode, parallel-resonant crystal. The recommended crystal spit fications are provided in able 23 to page 338. A printed circuit board layout must not add more related pF of stray capacitance to either the RTC\_X<sub>IN</sub> or RTC\_X<sub>OUT</sub> pins. If oscillation does not occure duce the values of capacitors C<sub>1</sub> and C<sub>2</sub> to decrease loading.

An on-chip MOS resistor sets the crystal/drcurrent limit. This configuration does not require an external bias resistor acrossctly et al. An on-chip MOS resistor provides the biasing.

ilog

341

|                       |                                                                         | $T_A = 40 \ "C \text{ to } 105 \ "C$ |      |         |      |                            |

|-----------------------|-------------------------------------------------------------------------|--------------------------------------|------|---------|------|----------------------------|

| Symbol                | Parameter                                                               | Minimum                              | Тур  | Maximum | Unit | Conditions                 |

| V <sub>VBO</sub>      | VBO Voltage Threshold                                                   | 2.45                                 | 2.65 | 2.90    | ١    | $V_{CQ} = V_{VBO}$         |

| V <sub>POR</sub>      | POR Voltage Threshold                                                   | 2.55                                 | 2.75 | 2.95    | ١    | $V_{C} = V_{POR}$          |

| V <sub>HYST</sub>     | POR/VBO Hysteresis                                                      | 30                                   | 100  | 120     | m    | V                          |

| T <sub>ANA</sub>      | POR/VBO analog RESET duration                                           | 40                                   |      | 100     | PS   |                            |

| T <sub>VBO_MIN</sub>  | VBO pulse reject period                                                 |                                      | 10   |         | PS   |                            |

| I <sub>POR_VBO</sub>  | POR/VBO DC current consumption                                          | า                                    | 40   | 50      | PA   |                            |

| IS <sub>POR_VBO</sub> | POR/VBO DC SLEEP mode current consumption                               |                                      | 120  | 150     | PA   | VBO_OFF=0<br>(VBO enabled) |

| VCC RAMP              | V <sub>CC</sub> ramp rate requirements to guarantee proper RESET occurs | 0.1                                  |      | 100     | V/m  | 6                          |

#### Table 234. POR and VBO Electrical Characteristics

### Flash Memory Characteristics

Table 235 lists the Flash memory characteristic the eZ80F91 device. For Flash programming and erase timing information, **Etas**h Memoryon page 97.

#### Table 235. Flash Memory Electrical Characteristics and Timing

|                            | 3.6 V;<br>105 "C |         |         |       |       |

|----------------------------|------------------|---------|---------|-------|-------|

| Symbol                     | Minimum          | Typical | Maximum | Units | Notes |

| Flash Byte Read Cycle Time | 78               |         |         | ns    |       |

### Current Consumption Under Various Operating Conditions

Figure 65on page 342 displays the typical current consumption of the eZ80F91 device versus Vdd while operating **25** °C, with zero Wait states, and with either a 10 MHz, 20 MHz, or 50 MHz system clock.