Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ80                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 50MHz                                                     |

| Connectivity               | Ethernet, I <sup>2</sup> C, IrDA, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 256KB (256K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 16K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 144-LQFP                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f91az050ec |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog |,

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function      | Signal Direction      | Description                                                                                                                           |  |  |  |

|----------------|---------------|-----------------|---------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 17             | F1            | ADDR12          | Address Bus   | Bidirectional         | Configured as an output in normal                                                                                                     |  |  |  |

| 18             | F2            | ADDR13          | Address Bus   | Bidirectional         | operation. The address bus selects a<br>location in memory or I/O space to be                                                         |  |  |  |

| 19             | F3            | ADDR14          | Address Bus   | Bidirectional         | read or written. Configured as an input                                                                                               |  |  |  |

| 20             | F4            | ADDR15          | Address Bus   | Bidirectional         | during bus acknowledge cyclesDrives the Chip Select/Wait State                                                                        |  |  |  |

| 21             | G1            | ADDR16          | Address Bus   | Bidirectional         | Generator block to generate Chip<br>Selects.                                                                                          |  |  |  |

| 22             | G2            | V <sub>DD</sub> | Power Supply  |                       | Power Supply.                                                                                                                         |  |  |  |

| 23             | G3            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                                                               |  |  |  |

| 24             | F5            | ADDR17          | Address Bus   | Bidirectional         | Configured as an output in normal                                                                                                     |  |  |  |

| 25             | H1            | ADDR18          | Address Bus   | Bidirectional         | operation. The address bus selects a location in memory or I/O space to be                                                            |  |  |  |

| 26             | H2            | ADDR19          | Address Bus   | Bidirectional         | read or written. Configured as an input                                                                                               |  |  |  |

| 27             | G4            | ADDR20          | Address Bus   | Bidirectional         | during bus acknowledge cyclesDrives the Chip Select/Wait State                                                                        |  |  |  |

| 28             | H3            | ADDR21          | Address Bus   | Bidirectional         | Generator block to generate Chip                                                                                                      |  |  |  |

| 29             | J1            | ADDR22          | Address Bus   | Bidirectional         | <sup>-</sup> Selects.                                                                                                                 |  |  |  |

| 30             | G5            | ADDR23          | Address Bus   | Bidirectional         | -                                                                                                                                     |  |  |  |

| 31             | J2            | V <sub>DD</sub> | Power Supply  |                       | Power Supply.                                                                                                                         |  |  |  |

| 32             | H4            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                                                               |  |  |  |

| 33             | J3            | CS0             | Chip Select 0 | Output, Active<br>Low | $\overline{\text{CS0}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS0}}$ memory or I/O address space. |  |  |  |

| 34             | K1            | CS1             | Chip Select 1 | Output, Active<br>Low | CS1 Low indicates that an access is occurring in the defined CS1 memory or I/O address space.                                         |  |  |  |

| 35             | K2            | CS2             | Chip Select 2 | Output, Active<br>Low | $\overline{\text{CS2}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS2}}$ memory or I/O address space. |  |  |  |

| 36             | L1            | CS3             | Chip Select 3 | Output, Active<br>Low | $\overline{\text{CS3}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS3}}$ memory or I/O address space. |  |  |  |

| 37             | M1            | V <sub>DD</sub> | Power Supply  |                       | Power Supply.                                                                                                                         |  |  |  |

| 38             | M2            | V <sub>SS</sub> | Ground        |                       | Ground.                                                                                                                               |  |  |  |

## Table 2. Pin Identification on the eZ80F91 Device (Continued)

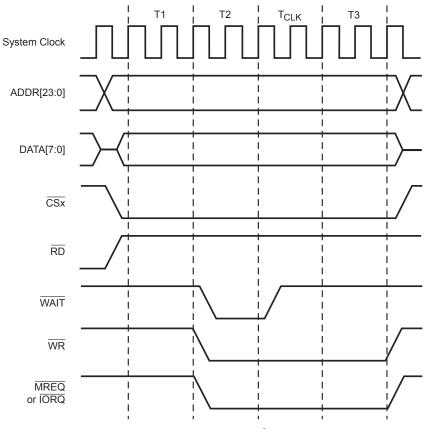

Figure 11. Example: Z80<sup>®</sup> Bus Mode Write Timing

## **Intel Bus Mode**

Chip selects configured for Intel bus mode modify the CPU bus signals to duplicate a four-state memory transfer similar to that found on Intel-style microcontrollers. The bus signals and eZ80F91 pins are mapped as displayed in Figure 12 on page 74. In Intel bus mode, you select either multiplexed or nonmultiplexed address and data buses. In nonmultiplexed operation, the address and data buses are separate. In multiplexed operation, the lower byte of the address, ADDR[7:0], also appears on the data bus, DATA[7:0], during State T1 of the Intel bus mode cycle.

ilog

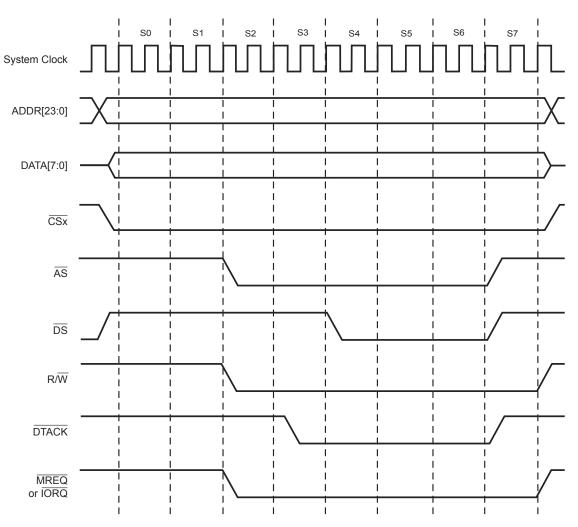

Figure 19. Example: Motorola Bus Mode Write Timing

#### Switching Between Bus Modes

When switching bus modes between Intel<sup>TM</sup> to Motorola, Motorola to Intel<sup>TM</sup>, eZ80<sup>®</sup> to Motorola, or eZ80 to Intel<sup>TM</sup>, there is one extra SCLK cycle added to the bus access. An extra clock cycle is not required for repeated access in any of the bus modes (for example, Intel<sup>TM</sup> to Intel<sup>TM</sup>). An extra clock cycle is not required for Intel<sup>TM</sup> (or Motorola) to eZ80 bus mode (under normal operation). The extra clock cycle is not shown in the timing examples. Due to the asynchronous nature of these bus protocols, the extra delay does not impact peripheral communication.

## 108

| Bit Position | Value | Description                                            |

|--------------|-------|--------------------------------------------------------|

| [1]          | 0     | Disable Write/Erase Protect on block 08000h to 0FFFFh. |

| BLK1_PROT    | 1     | Enable Write/Erase Protect on block 08000h to 0FFFFh.  |

| [0]          | 0     | Disable Write/Erase Protect on block 00000h to 07FFFh. |

| BLK0_PROT    | 1     | Enable Write/Erase Protect on block 00000h to 07FFFh.  |

**Note:** The lower 32 KB block (0000h to 07FFFh—BLK0) is called the Boot block and is protected using the external WP pin.

#### Flash Interrupt Control Register

There are two sources of interrupts from the Flash controller. These two sources are:

- Page Erase, Mass Erase, or Row Program completed successfully.

- An error condition occurred.

Either or both of these two interrupt sources are enabled by setting the appropriate bits in the Flash Interrupt Control register.

The Flash Interrupt Control register contains four status bits to indicate the following error conditions:

**Row Program Time-Out**—This bit signals a time-out during Row Programming. If the current row program operation does not complete within 4864 Flash controller clocks, the Flash controller terminates the row program operation by clearing bit 2 of the Flash Program Control Register and sets the RP\_TM0 error bit to 1.

**Write Violation**—This bit indicates an attempt to write to a protected block of Flash memory (the Write was not performed).

**Page Erase Violation**—This bit indicates an attempt to erase a protected block of Flash memory (the requested page was not erased).

**Mass Erase Violation**—This bit indicates an attempt to MASS ERASE when there are one or more protected blocks in Flash memory (the MASS ERASE was not performed).

If the error condition interrupt is enabled, any of these four error conditions result in an interrupt request being sent to the eZ80F91device's interrupt controller. Reading the Flash Interrupt Control register clears all error condition flags and the DONE flag. See Table 42 on page 109.

ilog | 131

- TMR3\_OC\_CTL2

- Compare Value Registers

- TMR3\_OC3\_H

- TMR3\_OC3\_L

- TMR3\_OC2\_H

- TMR3\_OC2\_L

- TMR3\_OC1\_H

- TMR3\_OC1\_L

- TMR3\_OC0\_H

- TMR3\_OC0\_L

Multiple PWM mode uses the following 19 registers:

- PWM Control Registers

- TMR3\_PWM\_CTL1

- TMR3\_PWM\_CTL2

- TMR3\_PWM\_CTL3

- PWM Rising Edge Values

- TMR3\_PWM3R\_H

- TMR3\_PWM3R\_L

- TMR3\_PWM2R\_H

- TMR3\_PWM2R\_L

- TMR3\_PWM1R\_H

- $TMRx_PWM1R_L$

- TMR3\_PWM0R\_H

- TMR3\_PWM0R\_L

- PWM Falling Edge Values

- TMR3\_PWM3F\_H

- TMR*x*\_PWM3F\_L

- TMR3\_PWM2F\_H

- TMR3\_PWM2F\_L

- TMR3\_PWM1F\_H

- TMR3\_PWM1F\_L

- TMR3\_PWM0F\_H

- TMR3\_PWM0F\_L

158

## Pulse-Width Modulation Falling Edge—Low Byte

A parallel 16-bit Write of {TMR3\_PWMxF\_H[7–0], TMR3\_PWMxF\_L[7–0]} occurs when software initiates a Write to TMR3\_PWMxF\_L. The register is listed in Table 78.

# Table 78. PWMx Falling-Edge Register—Low Byte (TMR3\_PWM0F\_L = 0084h, TMR3\_PWM1F\_L = 0086h, TMR3\_PWM2F\_L = 0088h, TMR3\_PWM3F\_L = 008Ah)

| Reset 0 0 0 0 0 0 0 0                  |           |

|----------------------------------------|-----------|

|                                        | eset      |

| CPU Access R/W R/W R/W R/W R/W R/W R/W | PU Access |

**Note:** R/W = Read/Write.

| Bit<br>Position  | Value   | Description                                                                                                                                                                                                                                       |

|------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PWMXF_L | 00h–FFh | These bits represent the Low byte of the 16-bit value to set the falling edge COMPARE value for PWMx, {TMR3_PWMXF_H[7:0], TMR3_PWMXF_L[7:0]}. Bit 7 is bit 7 of the 16-bit timer data value. Bit 0 is bit 0 (lsb) of the 16-bit timer data value. |

## Pulse-Width Modulation Falling Edge—High Byte

Writing to TMR3\_PWMxF\_H stores the value in a temporary holding register. A parallel 16-bit Write of {TMR3\_PWMxF\_H[7–0], TMR3\_PWMxF\_L[7–0]} occurs when software initiates a Write to TMR3\_PWMxF\_L. The register is listed in Table 79.

# Table 79. PWMx Falling-Edge Register—High Byte (TMR3\_PWM0F\_H = 0085h, TMR3\_PWM1F\_H = 0087h, TMR3\_PWM2F\_H = 0089h, TMR3\_PWM3F\_H = 008Bh)

| Bit                            | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access                     | R/W |

| <b>Note:</b> R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position  | Value   | Description                                                                                                                                                                                                                                         |

|------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PWMXF_H | 00h–FFh | These bits represent the High byte of the 16-bit value to set the falling edge COMPARE value for PWMx, {TMR3_PWMXF_H[7:0], TMR3_PWMXF_L[7:0]}. Bit 7 is bit 15 (msb) of the 16-bit timer data value. Bit 0 is bit 8 of the 16-bit timer data value. |

- Write values to the RTC count registers to set the current time

- Write values to the RTC alarm registers to set the appropriate alarm conditions

- Write to RTC\_CTRL to clear RTC\_UNLOCK; clearing the RTC\_UNLOCK bit resets and enables the clock divider

## **Real-Time Clock Registers**

The RTC registers are accessed via the address and data buses using I/O instructions. The RTC\_UNLOCK control bit controls access to the RTC count registers. When unlocked (RTC\_UNLOCK = 1), the RTC count is disabled and the count registers are Read/Write. When locked (RTC\_UNLOCK = 0), the RTC count is enabled and the count registers are Read Only. The default at RESET is for the RTC to be locked.

### **Real-Time Clock Seconds Register**

This register contains the current seconds count. The value in the RTC\_SEC register is unchanged by a RESET. The current setting of BCD\_EN determines whether the values in this register are binary (BCD\_EN = 0) or binary-coded decimal (BCD\_EN = 1). Access to this register is Read Only if the RTC is locked, and Read/Write if the RTC is unlocked. See Table 80.

#### Table 80. Real-Time Clock Seconds Register (RTC\_SEC = 00E0h)

| Bit        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------|------|------|------|------|------|------|------|------|

| Reset      | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access | R/W* |

**Note:** X = Unchanged by RESET; R/W\* = Read Only if RTC locked, Read/Write if RTC unlocked.

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| Bit Position     | Value | Description                                  |

|------------------|-------|----------------------------------------------|

| [7:4]<br>TEN_SEC | 0–5   | The tens digit of the current seconds count. |

| [3:0]<br>SEC     | 0–9   | The ones digit of the current seconds count. |

#### Binary Operation (BCD\_EN = 0)

| Bit Position | Value   | Description                |

|--------------|---------|----------------------------|

| [7:0]<br>SEC | 00h–3Bh | The current seconds count. |

ilog <sub>164</sub>

#### Real-Time Clock Day-of-the-Week Register

This register contains the current day-of-the-week count. The RTC\_DOW register begins counting at 01h. The value in the RTC\_DOW register is unchanged by a RESET. The current setting of BCD\_EN determines whether the value in this register is binary (BCD\_EN = 0) or binary-coded decimal (BCD\_EN = 1). Access to this register is Read Only if the RTC is locked and Read/Write if the RTC is unlocked. See Table 83.

#### Table 83. Real-Time Clock Day-of-the-Week Register (RTC\_DOW = 00E3h)

| Bit        | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|------------|---|---|---|---|------|------|------|------|

| Reset      | 0 | 0 | 0 | 0 | Х    | Х    | Х    | Х    |

| CPU Access | R | R | R | R | R/W* | R/W* | R/W* | R/W* |

**Note:** X = Unchanged by RESET; R = Read Only; R/W\* = Read Only if RTC locked, Read/Write if RTC unlocked.

#### Binary-Coded Decimal Operation (BCD\_EN = 1)

| Bit Position | Value | Description                        |

|--------------|-------|------------------------------------|

| [7:4]        | 0000  | Reserved.                          |

| [3:0]<br>DOW | 1–7   | The current day-of-the-week.count. |

#### Binary Operation (BCD\_EN = 0)

| Bit Position | Value   | Description                        |

|--------------|---------|------------------------------------|

| [7:4]        | 0000    | Reserved.                          |

| [3:0]<br>DOW | 01h–07h | The current day-of-the-week count. |

ilog <sub>165</sub>

#### Real-Time Clock Day-of-the-Month Register

This register contains the current day-of-the-month count. The RTC\_DOM register begins counting at 01h. The value in the RTC\_DOM register is unchanged by a RESET. The current setting of BCD\_EN determines whether the values in this register are binary  $(BCD_EN = 0)$  or binary-coded decimal  $(BCD_EN = 1)$ . Access to this register is Read Only if the RTC is locked, and Read/Write if the RTC is unlocked. See Table 84.

Table 84. Real-Time Clock Day-of-the-Month Register (RTC\_DOM = 00E4h)

| Bit        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------|------|------|------|------|------|------|------|------|

| Reset      | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access | R/W* |

**Note:** X = Unchanged by RESET; R/W\* = Read Only if RTC locked, Read/Write if RTC unlocked.

#### Binary-Coded Decimal Operation (BCD\_EN = 1)

| Bit Position      | Value | Description                                           |  |  |  |  |

|-------------------|-------|-------------------------------------------------------|--|--|--|--|

| [7:4]<br>TENS_DOM | 0–3   | The tens digit of the current day-of-the-month count. |  |  |  |  |

| [3:0]<br>DOM      | 0—9   | The ones digit of the current day-of-the-month count. |  |  |  |  |

|                   |       |                                                       |  |  |  |  |

#### Binary Operation (BCD\_EN = 0)

| Bit Position | Value   | Description                         |

|--------------|---------|-------------------------------------|

| [7:0]<br>DOM | 01h–1Fh | The current day-of-the-month count. |

ilog <sub>189</sub>

| Bit<br>Position | Value   | Description                                                                                                                                                                                                                                                                                            |

|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FOSILION        | value   | •                                                                                                                                                                                                                                                                                                      |

| 4<br>EPS        | 0       | Even Parity Select.<br>Use odd parity for transmit and receive. The total number of 1 bits in the transmit<br>data plus parity bit is odd. Used as SPACE bit in Multidrop Mode. See Table 104 on<br>page 189 for parity select definitions. Note: Receive Parity is set to SPACE in<br>multidrop mode. |

|                 | 1       | Use even parity for transmit and receive. The total number of 1 bits in the transmit data plus parity bit is even. Used as MARK bit in Multidrop Mode. See Table 104 on page 189 for parity select definitions.                                                                                        |

|                 | 0       | Parity bit transmit and receive is disabled.                                                                                                                                                                                                                                                           |

| 3<br>PEN        | 1       | Parity bit transmit and receive is enabled. For transmit, a parity bit is generated and transmitted with every data character. For receive, the parity is checked for every incoming data character. In Multidrop Mode, receive parity is checked for space parity.                                    |

| [2:0]<br>CHAR   | 000–111 | UART Character Parameter Selection.<br>See Table 103 on page 189 for a description of the values.                                                                                                                                                                                                      |

## Table 103. UART Character Parameter Definition

| CHAR[2:0] | Character Length (Tx/Rx Data Bits) | Stop Bits (Tx Stop Bits) |

|-----------|------------------------------------|--------------------------|

| 000       | 5                                  | 1                        |

| 001       | 6                                  | 1                        |

| 010       | 7                                  | 1                        |

| 011       | 8                                  | 1                        |

| 100       | 5                                  | 2                        |

| 101       | 6                                  | 2                        |

| 110       | 7                                  | 2                        |

| 111       | 8                                  | 2                        |

ilog

196

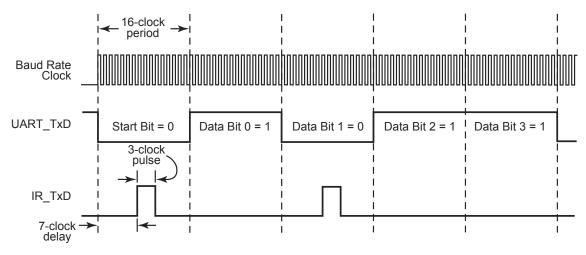

IrDA specifications. The UART must be enabled to use the endec. For more information on the UART and its BRG, see Universal Asynchronous Receiver/Transmitter on page 175.

## Transmit

The data to be transmitted via the IR transceiver is the data sent to UART0. The UART transmit signal, TxD, and Baud Rate Clock are used by the endec to generate the modulation signal, IR\_TxD, that drives the infrared transceiver. Each UART bit is 16 clocks wide. If the data to be transmitted is a logical 1 (High), the IR\_TxD signal remains Low (0) for the full 16-clock period. If the data to be transmitted is a logical 0, a 3-clock High (1) pulse is output following a 7-clock Low (0) period. Following the 3-clock High pulse, a 6-clock Low pulse completes the full 16-clock data period. Data transmission is displayed in Figure 38. During data transmission, the IR receive function must be disabled by clearing the IR\_RxEN bit in the IR\_CTL reg to 0 to prevent transmitter-to-receiver crosstalk.

## Receive

Data received from the IR transceiver via the IR\_RxD signal is decoded by the endec and passed to the UART. The IR\_RxEN bit in the IR\_CTL register must be set to enable the receiver decoder. The IrDA serial infrared (SIR) data format uses half duplex communication. Therefore, the UART must not be allowed to transmit while the receiver decoder is enabled. The UART Baud Rate Clock is used by the endec to generate the demodulated signal, RxD, that drives the UART. Each UART bit is 16 clocks wide. If the data to be received is a logical 1 (High), the IR\_RxD signal remains High (1) for the full 16-clock

ilog <sub>207</sub>

## Table 112. SPI Baud Rate Generator Register—Low Byte (SPI\_BRG\_L = 00B8h)

| Bit                |                         | 7                                                                                                                                        | 6   | 5   | 4   | 3   | 2   | 1   | 0 |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|---|

| Reset              |                         | 0                                                                                                                                        | 0   | 0   | 0   | 0   | 0   | 1   | 0 |

| CPU Access         | R/W                     | R/W                                                                                                                                      | R/W | R/W | R/W | R/W | R/W | R/W |   |

| Note: R/W = Re     | Note: R/W = Read/Write. |                                                                                                                                          |     |     |     |     | 1   |     |   |

| Bit                |                         |                                                                                                                                          |     |     |     |     |     |     |   |

| Position           | Value                   | Description                                                                                                                              |     |     |     |     |     |     |   |

| [7:0]<br>SPI_BRG_L | 00h–<br>FFh             | These bits represent the Low byte of the 16-bit BRG divider value. The complete BRG divisor value is returned by {SPI_BRG_H, SPI_BRG_L}. |     |     |     |     |     |     |   |

## Table 113. SPI Baud Rate Generator Register—High Byte (SPI\_BRG\_H = 00B9h)

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position    | Value   | Description                                                                                                                               |

|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>SPI_BRG_H | 00h–FFh | These bits represent the High byte of the 16-bit BRG divider value. The complete BRG divisor value is returned by {SPI_BRG_H, SPI_BRG_L}. |

ilog <sub>244</sub>

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                            |  |  |

|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2<br>ign_low_1  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If brk_addr1 is set to 1, ZDI initiates<br>a break when the entire 24-bit address, ADDR[23:0],<br>matches the 3-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H, ZDI_ADDR1_L}.                                                                    |  |  |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is enabled. If brk_addr1 is set to 1, ZDI initiates<br>a break when only the upper 2 bytes of the 24-bit address,<br>ADDR[23:8], match the 2-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H}. As a result, a break occurs anywhere<br>within a 256-byte page. |  |  |

| 1<br>ign_low_0  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If brk_addr0 is set to 1, ZDI initiates<br>a break when the entire 24-bit address, ADDR[23:0],<br>matches the 3-byte value {ZDI_ADDR0_U,<br>ZDI_ADDR0_H, ZDI_ADDR0_L}.                                                                    |  |  |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Ma<br>1 registers is enabled. If the brk_addr1 is set to 0, ZDI<br>initiates a break when only the upper 2 bytes of the 24-<br>address, ADDR[23:8], match the 2 bytes value<br>{ZDI_ADDR0_U, ZDI_ADDR0_H}. As a result, a break<br>occurs anywhere within a 256-byte page.  |  |  |

| 0               | 0     | ZDI single step mode is disabled.                                                                                                                                                                                                                                                                                                      |  |  |

| single_step     | 1     | ZDI single step mode is enabled. ZDI asserts a break following execution of each instruction.                                                                                                                                                                                                                                          |  |  |

273

| Symbol                                  | Parameter                                                            | Test Condition                                                                                                                             | Min  | Тур | Max | Units     |

|-----------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-----------|

| F <sub>vco</sub>                        | VCO frequency                                                        | Recommended operating conditions                                                                                                           |      | 50  |     | MHz       |

| G <sub>vco</sub>                        | VCO Gain                                                             | Recommended operating conditions                                                                                                           | 36   |     | 120 | MHz/<br>V |

| D1                                      | SCLK Duty Cycle from PLL or<br>XTALOSC source                        | Recommended operating conditions                                                                                                           | 45   | 50  | 55  | %         |

| T1A                                     | PLL Clock Jitter                                                     | F <sub>VCO</sub> = 50 MHz. XTALOSC<br>= 10 MHz                                                                                             |      | 350 | 500 | ps        |

| Lock2                                   | PLL Lock-Time                                                        | F <sub>VCO</sub> = 50 MHz. XTALOSC<br>= 3.579 MHz<br>C <sub>pll1</sub> = 220 pF, R <sub>pll</sub> = 499 ¾,<br>C <sub>pll2</sub> = 0.056 μF |      |     |     | S         |

| I <sub>oH1</sub><br>(XTL)               | High-level Output Current for XTAL2 pin                              | V <sub>oH</sub> = V <sub>DD</sub> –0.4 V<br>PLL_CTL0[5:4] = 01                                                                             | -0.3 |     |     | mA        |

| I <sub>oL1</sub><br>(XTL)               | Low-level Output Current for XTAL2 pin                               | V <sub>oL</sub> = 0.4 V<br>PLL_CTL0[5:4] = 01                                                                                              | 0.6  |     |     | mA        |

| I <sub>oH2</sub><br>(XTL)               | High-level Output Current for XTAL2 pin                              | V <sub>oH</sub> = V <sub>DD</sub> –0.4 V<br>PLL_CTL0[5:4] = 11                                                                             |      |     |     | mA        |

| I <sub>oL2</sub><br>(XTL)               | Low-level Output Current for<br>XTAL2 pin                            | V <sub>oL</sub> = 0.4 V<br>PLL_CTL0[5:4] = 11                                                                                              |      |     |     | mA        |

| V <sub>PP3M</sub><br>(XTL)              | Peak-to-peak voltage under<br>oscillator conditions for<br>XTAL2 pin | F <sub>OSC</sub> = 3.579 MHz<br>Cx1 = 10 pF<br>Cx2 = 10 pF                                                                                 |      |     |     | V         |

| V <sub>PP10M</sub><br>(XTL)             | Peak-to-peak voltage under<br>oscillator conditions for<br>XTAL2 pin | F <sub>OSC</sub> = 10 MHz<br>Cx1 = 10 pF<br>Cx2 = 10 pF                                                                                    |      |     |     | V         |

| C <sub>xtal1</sub><br>(package<br>type) | Capacitance measured from XTAL1 pin to GND                           | T = 25 °C                                                                                                                                  |      |     |     | pF        |

| C <sub>xtal2</sub><br>(package<br>type) | Capacitance measured from XTAL2 pin to GND                           | T = 25 °C                                                                                                                                  |      |     |     | pF        |

| C <sub>loop</sub><br>(package<br>type)  | Capacitance measured from loop filter pin to GND                     | T = 25 °C                                                                                                                                  |      |     |     | pF        |

## Table 156. PLL Characteristics (Continued)

293

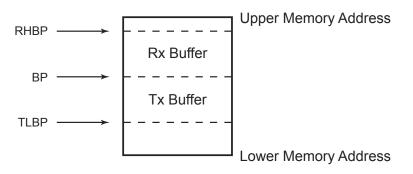

• Receive High Boundary Pointer (RHBP)—this register points to the end of the Receive buffer + 1.

Figure 60 displays the internal Ethernet shared memory.

The Transmit and Receive buffers are subdivided into packet buffers of 32, 64, 128, or 256 bytes in size. The packet buffer size is set in bits 7 and 6 of the EmacBufSize register. An Ethernet packet accommodate multiple packet buffers. First, however, a brief listing of the contents of a typical Ethernet packet is in order. See Table 177.

| Table 177 | . Ethernet | Packet | Contents |

|-----------|------------|--------|----------|

|-----------|------------|--------|----------|

| Byte Range        | Contents                 |

|-------------------|--------------------------|

| Bytes 0–5         | MAC destination address. |

| Bytes 6–11        | MAC source address.      |

| Bytes 12–13       | Length/Type field.       |

| Bytes 14–n        | MAC Client Data.         |

| Bytes (n+1)–(n+4) | Frame Check Sequence.    |

At the start of each packet is a descriptor table that describes the packet. Each actual Ethernet packet follows the descriptor table as displayed in Figure 61 on page 294.

ilog <sub>299</sub>

## **EMAC Configuration Register 1**

The EMAC Configuration Register 1 allows control of the padding, autodetection, cyclic redundancy checking (CRC) control, full-duplex, field length checking, maximum packet ignores, and proprietary header options. See Table 181.

Table 181. EMAC Configuration Register 1 (EMAC\_CFG1 = 0021h)

| Bit           | 7           | 6                                                                                                                                                                                      | 5                                                                                                                                                                     | 4   | 3   | 2   | 1   | 0   |     |  |  |  |

|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Reset         | 0           | 0                                                                                                                                                                                      | 0                                                                                                                                                                     | 0   | 0   | 0   | 0   | 0   |     |  |  |  |

| CPU Access    | 5           | R/W                                                                                                                                                                                    | R/W                                                                                                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| Note: R/W = I | Read/Write. |                                                                                                                                                                                        |                                                                                                                                                                       |     |     |     |     |     |     |  |  |  |

| Bit           |             |                                                                                                                                                                                        |                                                                                                                                                                       |     |     |     |     |     |     |  |  |  |

| Position      | Value       | Descr                                                                                                                                                                                  | iption                                                                                                                                                                |     |     |     |     |     |     |  |  |  |

| 7<br>PADEN    | 0           | -                                                                                                                                                                                      | No padding. Assume all frames presented to EMAC have proper length.                                                                                                   |     |     |     |     |     |     |  |  |  |

|               | 1           | data fi                                                                                                                                                                                | EMAC pads all short frames by adding zeroes to the end of the data field. This bit is used in conjunction with ADPADN and VLPAD.                                      |     |     |     |     |     |     |  |  |  |

| 6<br>ADPADN   | 0           | Disabl                                                                                                                                                                                 | Disable autodetection.                                                                                                                                                |     |     |     |     |     |     |  |  |  |

|               | 1           | Enable frame detection by comparing the two bytes following<br>the source address with 0x8100 (VLAN Protocol ID) and pad<br>accordingly. This bit is ignored if PADEN is cleared to 0. |                                                                                                                                                                       |     |     |     |     |     |     |  |  |  |

| 5<br>VLPAD    | 0           | Do not                                                                                                                                                                                 | Do not pad all short frames.                                                                                                                                          |     |     |     |     |     |     |  |  |  |

|               | 1           | EMAC pads all short frames to 64 bytes and append a valid CRC. This bit is ignored if PADEN is cleared to 0.                                                                           |                                                                                                                                                                       |     |     |     |     |     |     |  |  |  |

| 4             | 0           | Do not                                                                                                                                                                                 | Do not append CRC.                                                                                                                                                    |     |     |     |     |     |     |  |  |  |

| CRCEN         | 1           | Appen                                                                                                                                                                                  | Append CRC to every frame regardless of padding options.                                                                                                              |     |     |     |     |     |     |  |  |  |

| 3             | 0           | HALF-                                                                                                                                                                                  | HALF-DUPLEX mode. CSMA/CD is enabled.                                                                                                                                 |     |     |     |     |     |     |  |  |  |

| FULLD         | 1           | Enable FULL-DUPLEX mode. CSMA/CD is disabled.                                                                                                                                          |                                                                                                                                                                       |     |     |     |     |     |     |  |  |  |

| 2             | 0           | Ignore the length field within Transmit/Receive frames.                                                                                                                                |                                                                                                                                                                       |     |     |     |     |     |     |  |  |  |

| FLCHK         | 1           | length                                                                                                                                                                                 | Both Transmit and Receive frame lengths are compared to the length/type field. If the length/type field represents a length then the frame length check is performed. |     |     |     |     |     |     |  |  |  |

| 1<br>HUGEN    | 0           |                                                                                                                                                                                        | Limit the Receive frame-size to the number of bytes specified in the MAXF[15:0] field.                                                                                |     |     |     |     |     |     |  |  |  |

|               | 1           | Allow unlimited sized frames to be received. Ignore the MAXF[15:0] field.                                                                                                              |                                                                                                                                                                       |     |     |     |     |     |     |  |  |  |

ilog <sub>30</sub>

| MII, RMII/SMII, PMD<br>(100 Mbps)<br>Clock Period = 40 ns |                    | •               | /II/SMII<br>/Ibps) | ENDEC Mode<br>(10 Mbps)<br>Clock Period = 100 ns |                    |  |  |

|-----------------------------------------------------------|--------------------|-----------------|--------------------|--------------------------------------------------|--------------------|--|--|

|                                                           |                    | Clock Perio     | od = 400 ns        |                                                  |                    |  |  |

| IPGR2[6:0]                                                | Interpacket<br>Gap | IPGR2[6:0]      | Interpacket<br>Gap | IPGR2[6:0]                                       | Interpacket<br>Gap |  |  |

| 00h                                                       | 0.24 µs            | 00h             | 2.4 µs             | 00h                                              | 0.6 µs             |  |  |

| 10h                                                       | 0.88 µs            | 10h             | 8.8 µs             | 10h                                              | 2.2 µs             |  |  |

| *12h                                                      | 0.96 µs            | 12h             | 9.6 µs             | 20h                                              | 3.8 µs             |  |  |

| 20h                                                       | 1.52 µs            | 20h             | 15.2 µs            | 40h                                              | 7.0 µs             |  |  |

| 40h                                                       | 2.80 µs            | 40h             | 28.0 µs            | 5Ah                                              | 9.6 µs             |  |  |

| 7Fh                                                       | 5.32 µs            | 7Fh             | 53.2 µs            | 7Fh                                              | 13.3 µs            |  |  |

| ote: *The IEE                                             | E 802.3, 802.3(u   | ) minimum value | s are shaded.      |                                                  |                    |  |  |

Table 190. EMAC\_IPGT Non-Back-to-Back Settings for Full- /Half-Duplex Modes

A non-back-to-back Transmit IPG is determined by the following formula:

(6 clocks + IPGR2 clocks) \* clock period = IPG

The difference in values between Table 189 on page 306 and Table 190 is due to the asynchronous nature of the Carrier Sense (CRS). The CRS must undergo a 2-clock synchronization before the internal Tx state machine detects it. This synchronization equates to a 6-clock intrinsic delay between packets instead of the 3-clock intrinsic delay in the back-to-back packet mode. More information covering this topic is found in the IEEE 802.3/4.2.3.2.1 Carrier Deference section.

## **EMAC Interpacket Gap Register**

The EMAC Interpacket Gap (IPG) is a programmable field representing the IPG between back-to-back packets. It is the IPG parameter used in FULL-DUPLEX and HALF-DUPLEX modes between back-to-back packets. Set this field to the appropriate number of IPG bytes. The default setting of 15h represents the minimum IPG of 0.96  $\mu$ s (at 100 Mbps) or 9.6  $\mu$ s (at 10 Mbps). See Table 191.

Table 191. EMAC Interpacket Gap Register (EMAC\_IPGT = 002Dh)

| Bit                      | 7        | 6      | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------------|----------|--------|-----|-----|-----|-----|-----|-----|

| Reset                    | 0        | 0      | 0   | 1   | 0   | 1   | 0   | 1   |

| CPU Access               | R        | R/W    | R/W | R/W | R/W | R/W | R/W | R/W |

| Note: R = Read Only; R/W | / = Read | /Write |     |     |     |     |     |     |

# ilog <sub>322</sub>

| Bit                 |                                        | 7   | 6                                                                                                                                                                                                                                     | 5 | 4   | 3   | 2   | 1   | 0   |  |

|---------------------|----------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|-----|-----|--|

| Reset               |                                        | 0   | 0                                                                                                                                                                                                                                     | 0 | 0   | 0   | 0   | 0   | 0   |  |

| CPU Access          |                                        | R   | R                                                                                                                                                                                                                                     | R | R/W | R/W | R/W | R/W | R/W |  |

| Note: R = Read C    | Note: R = Read Only, R/W = Read/Write. |     |                                                                                                                                                                                                                                       |   |     |     |     |     |     |  |

| Bit<br>Position     | Value                                  | Des | cription                                                                                                                                                                                                                              |   |     |     |     |     |     |  |

| [7:0]<br>EMAC_RRP_H | 00h-FFI                                | Rec | These bits represent the High byte of the 2-byte EMAC<br>Receive Read Pointer value, {EMAC_RRP_H,<br>EMAC_RRP_L}. Bit 7 is bit 15 (msb) of the 16-bit value. Bits<br>7:5 default to 000 on reset; bit 0 is bit 8 of the 16-bit value. |   |     |     |     |     |     |  |

#### Table 213. EMAC Receive Read Pointer Register—High Byte (EMAC\_RRP\_H = 004Ah)

#### **EMAC Buffer Size Register**

The lower six bits of this register set the level at which the EMAC either transmits a pause control frame or jams the Ethernet bus, depending on the mode selected. When each of these bits contain a zero, this feature is disabled.

In FULL-DUPLEX mode, a Pause Control Frame is transmitted as a One-shot operation. The software must free up a number of Rx buffers so that the number of buffers remaining, EmacBlksLeft, is greater than TCPF\_LEV.

In HALF-DUPLEX mode, the EMAC jams the Ethernet by sending a continuous stream of hexadecimal 5s (5fh). When the software frees up the Rx buffers and the number of buffers remaining, EmacBlksLeft, is greater than TCPF\_LEV, the EMAC stops jamming.

ilog <sub>363</sub>

DATA58 **DATA6 8 DATA78** DC Characteristics 339 DCD 190, 193 DCD0 13, 198 DCD1 16 **DCTS 193 DDCD 193** DDSR 193 Divider, PLL 266 divisor count 206 divisor count, 16-bit 182 DSR 191, 193 DSR0 13, 198 **DSR1** 16 DTACK 81, 82 DTR 191, 193 DTR0 12, 198 DTR1 15

# Ε

EC0 17, 127, 129, 132 EC1 22, 127, 129, 132 edge-selectable interrupts 55 **Edge-Triggered Interrupts 54** EI, Op Code Map 280 EMAC 287 EMAC Address Filter Register 311 EMAC Boundary Pointer Register-Low and High Bytes 319 EMAC Boundary Pointer Register—Upper Byte 319 EMAC Buffer Size Register 322 EMAC Configuration Register 1 299 EMAC Configuration Register 2 301 EMAC Configuration Register 3 302 EMAC Configuration Register 4 303 EMAC FIFO Data Register—Low and High Bytes 332 **EMAC FIFO Flags Register 333** EMAC Functional Description 288 EMAC Hash Table Register 312

EMAC Interpacket Gap 306 EMAC Interpacket Gap Overview 306 EMAC Interpacket Gap Register 307 EMAC Interrupt Enable Register 323 EMAC Interrupt Status Register 325 EMAC Interrupts 292 EMAC Maximum Frame Length Register-Low and High Bytes 309 EMAC memory 288, 289 EMAC MII Management Register 313 EMAC MII Status Register 327 EMAC Non-Back-To-Back IPG Register—Part 1 308 EMAC Non-Back-To-Back IPG Register—Part 2 308 EMAC PHY Address Register 315 EMAC PHY Configuration Data Register-Low Byte 314 EMAC PHY Read Status Data Register-Low and High Bytes 326 EMAC PHY Unit Select Address Register 316 EMAC RAM 93, 94, 95, 96 EMAC Receive Blocks Left Register-Low and High Bytes 330 EMAC Receive High Boundary Pointer Register-Low and High Bytes 320 EMAC Receive Read Pointer Register-Low and High Bytes 321 EMAC Receive Write Pointer Register—High Byte 329 EMAC Receive Write Pointer Register—Low Byte 328 **EMAC Receiver Interrupts 292** EMAC Registers 297 EMAC Reset Control Register 317 EMAC Shared Memory Organization 292 EMAC Station Address Register 304 EMAC System Interrupts 292 EMAC Test Register 298 EMAC Transmit Lower Boundary Pointer Register-Low and High Bytes 318 EMAC Transmit Pause Timer Value Register-Low and High Bytes 305 EMAC Transmit Polling Timer Register 316

ilog | 365

GPIO Overview 49 GPIO port pins 41, 49, 55, 354

## Η

HALT 10, 253, 277 HALT instruction 45 HALT Mode 45 HALT mode 1, 46, 245, 253 HALT, Op-Code Map 280 HALT\_SLP 10, 253, 260 Handshake 216 handshake 175, 177 hash table 311

## I

I/O Chip Select Operation 68 I/O Chip Selects, External 27 I/O Read 99 I/O space 6, 8, 65, 68 I2C Acknowledge bit 226 I2C bus 211, 214, 215 I2C bus clock 211 I2C bus protocol 212 I2C Clock Control Register 229 I2C control bit 217, 218, 220 I2C Control Register 225 I2C Data Register 225 I2C Extended Slave Address Register 224 I2C Registers 223 I2C Software Reset Register 230 I2C Status Register 227 IC0 17, 127, 129, 134, 135, 139, 140, 141, 142, 152, 156 IC1 17, 127, 129, 134, 135, 139, 141, 152, 156 IC2 18, 127, 129, 134, 135, 139, 140, 141, 152, 156 IC3 18, 127, 129, 134, 135, 139, 141, 142, 152, 156 IEEE 1149.1 specification 259, 264 IEEE 802.3 311 IEEE 802.3 frames 300 IEEE 802.3 specification 301, 302

IEEE 802.3, 802.3(u) minimum values 306 IEEE 802.3/4.2.3.2.1 Carrier Deference 307, 308 IEEE Standard 1149.1 257, 258 IEF1 59, 125, 253 **IEF2 59** IFLG bit 211, 216, 219, 221, 222, 223, 226, 229 IM 0, Op Code Map 283 IM 1, Op Code Map 283 IM 2, Op Code Map 283 Information Page Characteristics 102 Infrared Encoder/Decoder 195 Infrared Encoder/Decoder Register 199 Infrared Encoder/Decoder Signal Pins 198 Input Capture 128 INPUT capture mode 130 Input capture mode 128 input capture mode 127, 134 **INSTRD 9 Instruction Store 4** 0 Registers 249 Intel-70 Intel Bus Mode 73 Intel Bus Mode (Separate Address and Data Buses) 74 internal pull-up 50 Internal RC oscillator 115 internal RC oscillator 118 internal system clock 69 Interpacket Gap 306, 307 Interpacket gap 306 interpacket gap 296, 308 Interrupt Controller 57 interrupt enable 9 Interrupt Enable bit 225 interrupt enable bit 160, 178 Interrupt Enable Flag 253 interrupt enable flag 125 Interrupt Input 198 interrupt input 11, 12, 13, 14, 15, 16 Interrupt Priority 61, 63 interrupt priority 63 interrupt priority levels 60 Interrupt Priority Registers 60 Interrupt request 133, 134