Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                  |

| Core Processor             | eZ80                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 50MHz                                                     |

| Connectivity               | Ethernet, I <sup>2</sup> C, IrDA, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 256KB (256K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 16K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 144-LQFP                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f91az050sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog

16

| LQFP   | BGA    |                 |                        |                                                |                                                                                                                                                                                                                                                                                               |

|--------|--------|-----------------|------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No | Pin No | Symbol          | Function               | Signal Direction                               | Description                                                                                                                                                                                                                                                                                   |

| 95     |        |                 | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port C pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. Port C is multiplexed<br>with one UART. |

|        |        | DSR1            | Data Set<br>Ready      | Schmitt-trigger<br>input, Active Low           | Modem status signal to the UART.<br>This signal is multiplexed with PC5.                                                                                                                                                                                                                      |

| 96     | G8     | PC6             | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port C pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. Port C is multiplexed<br>with one UART. |

|        |        | DCD1            | Data Carrier<br>Detect | Schmitt-trigger input, Active Low              | Modem status signal to the UART.<br>This signal is multiplexed with PC6.                                                                                                                                                                                                                      |

| 97     |        |                 | GPIO Port C            | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port C pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. Port C is multiplexed<br>with one UART. |

|        |        | RI1             | Ring Indicator         | Schmitt-trigger input, Active Low              | Modem status signal to the UART.<br>This signal is multiplexed with PC7.                                                                                                                                                                                                                      |

| 98     | E11    | V <sub>DD</sub> | Power Supply           |                                                | Power Supply.                                                                                                                                                                                                                                                                                 |

| 99     | F9     | V <sub>SS</sub> | Ground                 |                                                | Ground.                                                                                                                                                                                                                                                                                       |

# Table 2. Pin Identification on the eZ80F91 Device (Continued)

ilog

# **Low-Power Modes**

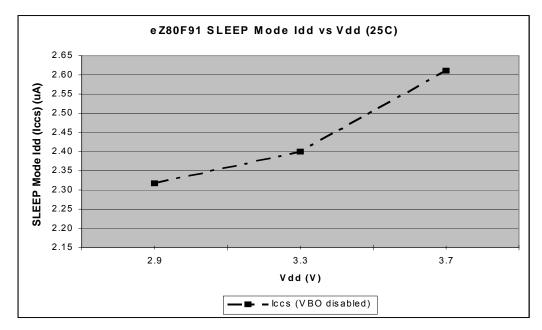

The eZ80F91 device provides a range of power-saving features. The highest level of power reduction is provided by SLEEP mode with all peripherals disabled, including VBO. The next level of power reduction is provided by the HALT instruction. The most basic level of power reduction is provided by the clock peripheral power-down registers.

# SLEEP Mode

Execution of the CPU's SLP instruction puts the eZ80F91 device into SLEEP mode. In SLEEP mode, the operating characteristics are:

- The primary crystal oscillator is disabled.

- The system clock is disabled.

- The CPU is idle.

- The Program Counter (PC) stops incrementing.

- The 32 kHz crystal oscillator continues to operate and drives the real-time clock and WDT (if WDT is configured to operate from the 32 kHz oscillator).

The CPU is brought out of SLEEP mode by any of the following operations:

- A RESET via the external  $\overline{\text{RESET}}$  pin driven Low.

- A RESET via a real-time clock alarm.

- A RESET via a WDT time-out (if running out of the 32 kHz oscillator and configured to generate a RESET on time-out).

- A RESET via execution of a Debug RESET command.

- A RESET via the Low-Voltage Brownout (VBO) detection circuit, if enabled.

After exiting SLEEP mode, the standard RESET delay occurs to allow the primary crystal oscillator to stabilize. For more information, see Figure 4 on page 43.

# HALT Mode

Execution of the CPU's HALT instruction puts the eZ80F91 device into HALT mode. In HALT mode, the operating characteristics are:

- The primary crystal oscillator is enabled and continues to operate.

- The system clock is enabled and continues to operate.

- The CPU is idle.

ilog

87

#### **Chip Select x Control Register**

The Chip Select x Control register (see Table 29) enables the chip selects, specifies the type of chip select, and sets the number of wait states. The reset state for the Chip Select 0 Control register is E8h when the reset state for three other Chip Select Control registers is 00h.

# Table 29. Chip Select x Control Register (CS0\_CTL = 00AAh, CS1\_CTL = 00ADh, CS2\_CTL = 00B0h, CS3\_CTL = 00B3h)

| Bit                                    | 7   | 6   | 5   | 4   | 3   | 2 | 1 | 0 |  |  |

|----------------------------------------|-----|-----|-----|-----|-----|---|---|---|--|--|

| CS0_CTL Reset                          | 1   | 1   | 1   | 0   | 1   | 0 | 0 | 0 |  |  |

| CS1_CTL Reset                          | 0   | 0   | 0   | 0   | 0   | 0 | 0 | 0 |  |  |

| CS2_CTL Reset                          | 0   | 0   | 0   | 0   | 0   | 0 | 0 | 0 |  |  |

| CS3_CTL Reset                          | 0   | 0   | 0   | 0   | 0   | 0 | 0 | 0 |  |  |

| CPU Access                             | R/W | R/W | R/W | R/W | R/W | R | R | R |  |  |

| Note: R/W = Read/Write; R = Read Only. |     |     |     |     |     |   |   |   |  |  |

| Bit      |       | 5                                                           |

|----------|-------|-------------------------------------------------------------|

| Position | Value | Description                                                 |

| [7:5]    | 000   | 0 wait states are asserted when this chip select is active. |

| CSX_WAIT | 001   | 1 wait state is asserted when this chip select is active.   |

|          | 010   | 2 wait states are asserted when this chip select is active. |

|          | 011   | 3 wait states are asserted when this chip select is active. |

|          | 100   | 4 wait states are asserted when this chip select is active. |

|          | 101   | 5 wait states are asserted when this chip select is active. |

|          | 110   | 6 wait states are asserted when this chip select is active. |

|          | 111   | 7 wait states are asserted when this chip select is active. |

| 4        | 0     | Chip select is configured as a memory chip select.          |

| CSX_IO   | 1     | Chip select is configured as an I/O chip select.            |

| 3        | 0     | Chip select is disabled.                                    |

| CSX_EN   | 1     | Chip select is enabled.                                     |

| [2:0]    | 000   | Reserved.                                                   |

|          |       |                                                             |

ilog

94

select address space, the memory chip select is not activated. On-chip RAM is not accessible to external devices during bus acknowledge cycles.

# **RAM Control Registers**

#### **RAM Control Register**

Internal general-purpose RAM is disabled by clearing the GPRAM\_EN bit. The default on RESET is for general-purpose RAM to be enabled. See Table 32.

## Table 32. RAM Control Register (RAM\_CTL=00B4h)

| Bit                                    | 7   | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------------------------------------|-----|-----|---|---|---|---|---|---|--|--|

| Reset                                  | 1   | 1   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

| CPU Access                             | R/W | R/W | R | R | R | R | R | R |  |  |

| Note: R/W = Read/Write; R = Read Only. |     |     |   |   |   |   |   |   |  |  |

| Bit      |        |                                          |

|----------|--------|------------------------------------------|

| Position | Value  | Description                              |

| 7        | 0      | On-chip general-purpose RAM is disabled. |

| GPRAM_EN | 1      | On-chip general-purpose RAM is enabled.  |

| 6        | 0      | On-chip EMAC RAM is disabled.            |

| ERAM_EN  | 1      | On-chip EMAC RAM is enabled.             |

| [5:0]    | 000000 | Reserved.                                |

ilog

101

without first erasing it. Otherwise, the burden is on software to ensure that the 31 ms maximum cumulative programming time between erases is not exceeded for a row.

#### **Memory Write**

A single-byte memory Write operation uses the address bus and data bus of the eZ80F91 device for programming a single data byte to Flash memory. While the CPU executes a Load instruction, the Flash controller asserts the internal WAIT signal to stall the CPU until the Write is complete. A single-byte Write takes between 66  $\mu$ s and 85 $\mu$ s to complete. Programming an entire row using memory Writes therefore takes no more than 21.8 ms. This duration of time does not include time required by the CPU to transfer data to the registers, which is a function of the instructions employed and the system clock frequency.

The memory Write function does not support multibyte row programming. Because memory Writes are self-timed, they are performed back-to-back without requiring polling or interrupts.

## **Erasing Flash Memory**

Erasing bytes in Flash memory returns them to a value of FFh. Both the MASS and PAGE ERASE operations are self-timed by the Flash controller, leaving the CPU free to execute other operations in parallel. The DONE status bit in the Flash Interrupt Control Register are polled by software or used as an interrupt source to signal completion of an Erase operation. If the CPU attempts to access Flash memory while an erase is in progress, the Flash controller forces a wait state until the Erase operation is completed.

#### **Mass Erase**

Performing a MASS ERASE operation on Flash memory erases all bits contained in the main Flash memory array. The information page remains unaffected unless the FLASH\_PAGE register bit 7(INFO\_EN) is set. This self-timed operation takes approximately 200 ms to complete.

#### **Page Erase**

The smallest erasable unit in Flash memory is a page. The pages to be erased, whether they are the 128 main Flash memory pages or the information page, are determined by the setting of the FLASH\_PAGE register. This self-timed operation takes approximately 10 ms to complete.

ilog

104

## Flash Address Upper Byte Register

The FLASH\_ADDR\_U register defines the upper 6 bits of the Flash memory address space. Changing the value of FLASH\_ADDR\_U allows on-chip 256 KB Flash memory to be mapped to any location within the 16 MB linear address space of the eZ80F91 device. If on-chip Flash memory is enabled, the Flash address assumes priority over any external Chip Selects. The external Chip Select signals are not asserted if the corresponding Flash address is enabled. Internal Flash memory does not hold priority over internal SRAM. See Table 37.

| Bit                                    | 7   | 6   | 5   | 4   | 3   | 2   | 1 | 0 |  |  |

|----------------------------------------|-----|-----|-----|-----|-----|-----|---|---|--|--|

| Reset                                  | 0   | 0   | 0   | 0   | 0   | 0   | 0 | 0 |  |  |

| CPU Access                             | R/W | R/W | R/W | R/W | R/W | R/W | R | R |  |  |

| Note: R/W = Read/Write; R = Read Only. |     |     |     |     |     |     |   |   |  |  |

## Table 37. Flash Address Upper Byte Register (FLASH\_ADDR\_U = 00F7h)

| Bit Position          | Value   | Description                                                                                                                                                                                                                     |

|-----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]<br>FLASH_ADDR_U | 00h–FCh | These bits define the upper byte of the Flash address.<br>When on-chip Flash is enabled, the Flash address space<br>begins at address {FLASH_ADDR_U, 00b, 0000h}. On-chip<br>Flash has priority over all external Chip Selects. |

| [1:0]                 | 00      | Reserved (enforces alignment on a 256 KB boundary).                                                                                                                                                                             |

ilog <sub>168</sub>

#### **Real-Time Clock Century Register**

This register contains the current century count. The value in the RTC\_CEN register is unchanged by a RESET. The current setting of BCD\_EN determines whether the values in this register are binary (BCD\_EN = 0) or binary-coded decimal (BCD\_EN = 1). Access to this register is Read Only if the RTC is locked, and Read/Write if the RTC is unlocked. See Table 87.

#### Table 87. Real-Time Clock Century Register (RTC\_CEN = 00E7h)

| Bit        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------|------|------|------|------|------|------|------|------|

| Reset      | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access | R/W* |

**Note:** X = Unchanged by RESET; R/W\* = Read Only if RTC locked, Read/Write if RTC unlocked.

#### Binary-Coded-Decimal Operation (BCD\_EN = 1)

| Bit Position      | Value | Description                                  |

|-------------------|-------|----------------------------------------------|

| [7:4]<br>TENS_CEN | 0—9   | The tens digit of the current century count. |

| [3:0]<br>CEN      | 0–9   | The ones digit of the current century count. |

|                   |       |                                              |

#### Binary Operation (BCD\_EN = 0)

| Bit Position | Value   | Description                |

|--------------|---------|----------------------------|

| [7:0]<br>CEN | 00h–63h | The current century count. |

ilog <sub>169</sub>

#### **Real-Time Clock Alarm Seconds Register**

This register contains the alarm seconds value. The value in the RTC\_ASEC register is unchanged by a RESET. The current setting of BCD\_EN determines whether the values in this register are binary (BCD\_EN = 0) or binary-coded decimal (BCD\_EN = 1). See Table 88.

### Table 88. Real-Time Clock Alarm Seconds Register (RTC\_ASEC = 00E8h)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| CPU Access | R/W |

**Note:** X = Unchanged by RESET; R/W = Read/Write.

#### Binary-Coded Decimal Operation (BCD\_EN = 1)

| Bit Position      | Value                         | Description                                |  |  |  |

|-------------------|-------------------------------|--------------------------------------------|--|--|--|

| [7:4]<br>ATEN_SEC | 0–5                           | The tens digit of the alarm seconds value. |  |  |  |

| [3:0]<br>ASEC     | 0–9                           | The ones digit of the alarm seconds value. |  |  |  |

| Binary Operat     | Binary Operation (BCD_EN = 0) |                                            |  |  |  |

| Bit Position      | Value                         | Description                                |  |  |  |

| [7:0]             | 00h–3B                        | 3h The alarm seconds value.                |  |  |  |

ilog

171

#### Real-Time Clock Alarm Hours Register

This register contains the alarm hours value. The value in the RTC\_AHRS register is unchanged by a RESET. The current setting of BCD\_EN determines whether the values in this register are binary (BCD\_EN = 0) or binary-coded decimal (BCD\_EN = 1). See Table 90.

### Table 90. Real-Time Clock Alarm Hours Register (RTC\_AHRS = 00EAh)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| CPU Access | R/W |

**Note:** X = Unchanged by RESET; R/W = Read/Write.

#### Binary-Coded Decimal Operation (BCD\_EN = 1)

| Bit Position      | Value     | Description                              |  |

|-------------------|-----------|------------------------------------------|--|

| [7:4]<br>ATEN_HRS | 0–2       | The tens digit of the alarm hours value. |  |

| [3:0]<br>AHRS     | 0–9       | The ones digit of the alarm hours value. |  |

| Binary Operat     | ion (BCD_ | EN = 0)                                  |  |

| Bit Position      | Value     | Description                              |  |

| [7:0]<br>AHRS     | 00h–17h   | The alarm hours value.                   |  |

ilog | 180

completed transmission. When the application makes this determination, it writes the transmit data bytes to the UARTx\_THR register. The number of bytes that the application writes depends on whether or not the FIFO is enabled. If the FIFO is enabled, the application writes 16 bytes at a time. If not, the application writes one byte at a time. As a result of the first Write, the interrupt is deactivated. The CPU then waits for the next interrupt. When the interrupt is raised by the UART module, the CPU repeats the same process until it exhausts all of the data for transmission.

To control and check the modem status, the application sets up the modem by writing to the UARTx\_MCTL register and reading the UARTx\_MCTL register before starting the process described above.

In RS485 multidrop mode, the first byte of the message is the station address and the rest of the message contains the data for that station. You must set the Even Parity Select (EPS bit 4) and Parity Enable (PEN bit 3) in the UARTx\_LCTL before sending the station address. We recommend that in your UART initialization routine set up the UARTx\_LCTL register for your data transfer format and set the Parity Enable (PEN bit 3) bit. Each time you want to send a new message you must perform these three steps:

- Since the UART automatically clears the Even Parity Select (EPS bit 4) bit in the UARTx\_LCTL after a byte is sent, before starting a new message you have to wait for the transmitter to go idle. The Transmit Empty (TEMT bit 6) of the UARTx\_LSR will be set. If you set the EPS bit of the UARTx\_LCTL before the last byte of the previous message is transmitted, the EPS bit will be cleared and the new station address will be sent as data instead of being used as an address.

- 2. Set the Even Parity Select (EPS bit 4) bit in the UARTx\_LCTL register being careful not to alter the other bits in the register sets the address mark. Write station address to the UARTx\_THR. The UART will automatically clear the EPS bit after the station address byte is transmitted.

- 3. Send the rest of the message. Write data to the UART Transmit Holding Register UARTx\_THR whenever the Transmit Holding Register Empty (THRE bit 5) in the UARTx\_LSR is set.

In multidrop mode, during receiving start address marks, you will see a receive line interrupt (INSTS bits[3:1]) in the IIR register. Read the LSR and check for receive errors only and ignore any parity errors. The parity is only used for address marks in this multidrop mode.

**Receive**—The receiver is always enabled, and it continually checks for the start bit on the RxD input signal. When an interrupt is raised by the UART module, the application reads the UARTx\_IIR register and determines the cause for the interrupt. If the cause is a line status interrupt, the application reads the UARTx\_LSR register, reads the data byte and then discards the byte or take other appropriate action. If the interrupt is caused by a receive-data-ready condition, the application alternately reads the UARTx\_LSR and UARTx\_RBR registers and removes all of the received data bytes. It reads the

ilog <sub>203</sub>

divide-by-two clock divider. In MASTER mode, the SPI serial clock is one-half the frequency of the clock signal created by the SPI's Baud Rate Generator.

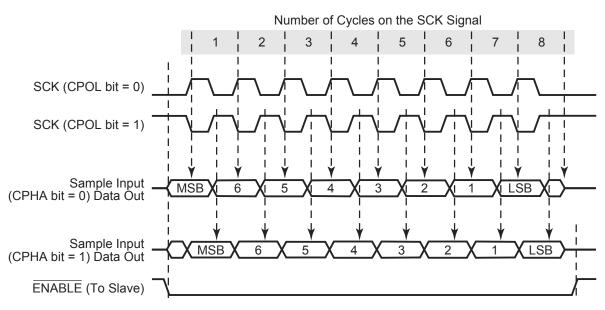

As displayed in Figure 42 and Table 111, four possible timing relations are chosen by using the clock polarity (CPOL) and clock phase CPHA control bits in the SPI Control register. See SPI Control Register on page 208. Both the master and slave must operate with the identical timing, CPOL, and CPHA. The master device always places data on the MOSI line a half-cycle before the clock edge (SCK signal), for the slave device to latch the data.

Figure 42. SPI Timing

#### Table 111. SPI Clock Phase and Clock Polarity Operation

| СРНА | CPOL | SCK<br>Transmit<br>Edge | SCK<br>Receive<br>Edge | SCK<br>Idle<br>State | SS High<br>Between<br>Characters? |

|------|------|-------------------------|------------------------|----------------------|-----------------------------------|

| 0    | 0    | Falling                 | Rising                 | Low                  | Yes                               |

| 0    | 1    | Rising                  | Falling                | High                 | Yes                               |

| 1    | 0    | Rising                  | Falling                | Low                  | No                                |

| 1    | 1    | Falling                 | Rising                 | High                 | No                                |

ilog <sub>220</sub>

| Code | I <sup>2</sup> C State                                                 | Microcontroller Response                                                    | Next I <sup>2</sup> C Action        |  |  |

|------|------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------|--|--|

| 40h  | Addr + R transmitted,<br>ACK received                                  | For a 7-bit address,<br>clear IFLG, AAK = 0 <sup>1</sup>                    | Receive data byte,<br>transmit NACK |  |  |

|      |                                                                        | Or clear IFLG, AAK = 1                                                      | Receive data byte,<br>transmit ACK  |  |  |

|      |                                                                        | For a 10-bit address<br>Write extended address<br>byte to data, clear IFLG  | Transmit extended address byte      |  |  |

| 48h  | Addr + R transmitted,<br>ACK not received <sup>2</sup>                 | For a 7-bit address:<br>Set STA, clear IFLG                                 | Transmit repeated START             |  |  |

|      |                                                                        | Or set STP, clear IFLG                                                      | Transmit STOP                       |  |  |

|      |                                                                        | Or set STA & STP,<br>clear IFLG                                             | Transmit STOP then START            |  |  |

|      |                                                                        | For a 10-bit address:<br>Write extended address byte to data,<br>clear IFLG | Transmit extended address byte      |  |  |

| 38h  | Arbitration lost                                                       | Clear IFLG                                                                  | Return to idle                      |  |  |

|      |                                                                        | Or set STA, clear IFLG                                                      | Transmit START when bus is free     |  |  |

| 68h  | Arbitration lost,<br>SLA+W received,                                   | Clear IFLG, clear AAK = 0                                                   | Receive data byte,<br>transmit NACK |  |  |

|      | ACK transmitted <sup>3</sup>                                           | Or clear IFLG, set AAK = 1                                                  | Receive data byte,<br>transmit ACK  |  |  |

| 78h  | Arbitration lost,<br>General call addr<br>received, ACK<br>transmitted | Same as code 68h                                                            | Same as code 68h                    |  |  |

| B0h  | Arbitration lost,<br>SLA+R received,                                   | Write byte to DATA,<br>clear IFLG, clear AAK = 0                            | Transmit last byte,<br>receive ACK  |  |  |

|      | ACK transmitted                                                        | Or write byte to DATA,<br>clear IFLG, set AAK = 1                           | Transmit data byte,<br>receive ACK  |  |  |

### Table 121. I<sup>2</sup>C Master Receive Status Codes

#### Notes

1. AAK is an I<sup>2</sup>C control bit that identifies which ACK signal to transmit.

2. R is defined as the Read bit; that is, the lsb is set to 1.

3. W is defined as the Write bit; that is, the lsb is cleared to 0.

If 10-bit addressing is being used, the slave is first addressed using the full 10-bit address, plus the Write bit. The master then issues a restart followed by the first part of the 10-bit

ilog

223

contains the two status codes 88h or 98h if SLAVE RECEIVE mode is entered with the general call address. The  $I^2C$  returns to an idle state when the IFLG bit is cleared to 0.

# I<sup>2</sup>C Registers

The section that follows describes each of the eZ80F91 MCU's Inter-Integrated Circuit  $(I^2C)$  registers.

### Addressing

The CPU interface provides access to seven 8-bit registers: four Read/Write registers, one Read Only register and two Write Only registers, as listed in Table 123.

Table 123. I<sup>2</sup>C Register Descriptions

| Register | Description                          |

|----------|--------------------------------------|

| I2C_SAR  | Slave address register               |

| I2C_XSAR | Extended slave address register      |

| I2C_DR   | Data byte register                   |

| I2C_CTL  | Control register                     |

| I2C_SR   | Status register (Read Only)          |

| I2C_CCR  | Clock Control register (Write Only)  |

| I2C_SRR  | Software reset register (Write Only) |

# **Resetting the I<sup>2</sup>C Registers**

Hardware Reset—When the I<sup>2</sup>C is reset by a hardware reset of the eZ80F91 device, the I<sup>2</sup>C\_SAR, I<sup>2</sup>C\_XSAR, I2C\_DR, and I<sup>2</sup>C\_CTL registers are cleared to 00h; while the I<sup>2</sup>C\_SR register is set to F8h.

**Software Reset**—Perform a software reset by writing any value to the  $I^2C$  Software Reset Register ( $I^2C\_SRR$ ). A software reset clears the STP, STA, and IFLG bits of the  $I^2C\_CTL$  register to 0 and sets the  $I^2C$  back to an idle state.

# I<sup>2</sup>C Slave Address Register

The I<sup>2</sup>C\_SAR register provides the 7-bit address of the I<sup>2</sup>C when in SLAVE mode and allows 10-bit addressing in conjunction with the I<sup>2</sup>C\_XSAR register. I<sup>2</sup>C\_SAR[7:1] = SLA[6:0] is the 7-bit address of the I<sup>2</sup>C when in 7-bit SLAVE mode. When the I<sup>2</sup>C receives this address after a START condition, it enters SLAVE mode. I<sup>2</sup>C\_SAR[7] corresponds to the first bit received from the I<sup>2</sup>C bus.

When the register receives an address starting with F7h to F0h ( $I^2C\_SAR[7:3] = 11110b$ ), the  $I^2C$  recognizes that a 10-bit slave addressing mode is being selected. The  $I^2C$  sends an ACK after receiving the  $I^2C\_SAR$  byte (the device does not generate an interrupt at this

ilog <sub>240</sub>

| BhZDI_ADDR2_LAddress Match 2 Low ByteXXhBhZDI_ADDR2_HAddress Match 2 High ByteXXhAhZDI_ADDR2_UAddress Match 2 Upper ByteXXhAhZDI_ADDR3_LAddress Match 3 Low ByteXXhChZDI_ADDR3_LAddress Match 3 Low ByteXXhDhZDI_ADDR3_HAddress Match 3 High ByteXXhDhZDI_ADDR3_UAddress Match 4 Upper ByteXXhDhZDI_BRK_CTLBreak Control Register00hIhZDI_MASTER_CTLMaster Control Register00hBhZDI_WR_DATA_LWrite Data Low ByteXXhShZDI_WR_DATA_UWrite Data Upper ByteXXhShZDI_RW_CTLRead/Write Control Register00hThZDI_BUS_CTLBus Control Register00hXhZDI_IS4Instruction Store 4XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |                   | 7DI De vieten Function      | Reset |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|-----------------------------|-------|

| ZDI_ADDR2_HAddress Match 2 High ByteXXRAhZDI_ADDR2_UAddress Match 2 Upper ByteXXRChZDI_ADDR3_LAddress Match 3 Low ByteXXRChZDI_ADDR3_HAddress Match 3 High ByteXXRChZDI_ADDR3_UAddress Match 4 Upper ByteXXRChZDI_ADDR3_UAddress Match 4 Upper ByteXXRChZDI_ADDR3_UAddress Match 4 Upper ByteXXRChZDI_BRK_CTLBreak Control Register00hChZDI_BRK_CTLWrite Data Low ByteXXRChZDI_WR_DATA_LWrite Data Low ByteXXRChZDI_WR_DATA_HWrite Data Upper ByteXXRChZDI_WR_DATA_UWrite Data Upper ByteXXRChZDI_WR_DATA_UWrite Data Upper ByteXXRChZDI_RW_CTLRead/Write Control Register00hChZDI_BUS_CTLBus Control Register00hChZDI_IS4Instruction Store 4XXR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ZDI Address | ZDI Register Name | ZDI Register Function       | Value |

| AhZDI_ADDR2_UAddress Match 2 Upper ByteXXtChZDI_ADDR3_LAddress Match 3 Low ByteXXtDhZDI_ADDR3_HAddress Match 3 High ByteXXtEhZDI_ADDR3_UAddress Match 4 Upper ByteXXtDhZDI_BRK_CTLBreak Control Register00hIhZDI_MASTER_CTLMaster Control Register00hBhZDI_WR_DATA_LWrite Data Low ByteXXtShZDI_WR_DATA_HWrite Data Upper ByteXXtShZDI_WR_DATA_UWrite Data Upper ByteXXtShZDI_RW_CTLRead/Write Control Register00hIhZDI_RW_CTLRead/Write Control Register00hXtZDI_BUS_CTLBus Control Register00hXtZDI_BUS_CTLBus Control Register00hXtZDI_IS4Instruction Store 4XXt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 08h         | ZDI_ADDR2_L       | Address Match 2 Low Byte    | XXh   |

| ChZDI_ADDR3_LAddress Match 3 Low ByteXXrDhZDI_ADDR3_HAddress Match 3 High ByteXXrEhZDI_ADDR3_UAddress Match 4 Upper ByteXXrDhZDI_BRK_CTLBreak Control Register00hIhZDI_MASTER_CTLMaster Control Register00hBhZDI_WR_DATA_LWrite Data Low ByteXXrAhZDI_WR_DATA_HWrite Data High ByteXXrAhZDI_WR_DATA_UWrite Data Upper ByteXXrAhZDI_RW_CTLRead/Write Control Register00hAhZDI_BUS_CTLBus Control Register00hAhZDI_IS4Instruction Store 4XXr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 09h         | ZDI_ADDR2_H       | Address Match 2 High Byte   | XXh   |

| DhZDI_ADDR3_HAddress Match 3 High ByteXXrEhZDI_ADDR3_UAddress Match 4 Upper ByteXXrDhZDI_BRK_CTLBreak Control Register00hIhZDI_MASTER_CTLMaster Control Register00hBhZDI_WR_DATA_LWrite Data Low ByteXXrIhZDI_WR_DATA_HWrite Data High ByteXXrIhZDI_WR_DATA_HWrite Data Upper ByteXXrIhZDI_WR_DATA_UWrite Data Upper ByteXXrIhZDI_RW_CTLRead/Write Control Register00hIhZDI_BUS_CTLBus Control Register00hIhZDI_IS4Instruction Store 4XXr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0Ah         | ZDI_ADDR2_U       | Address Match 2 Upper Byte  | XXh   |

| EhZDI_ADDR3_UAddress Match 4 Upper ByteXXhDhZDI_BRK_CTLBreak Control Register00hIhZDI_MASTER_CTLMaster Control Register00hBhZDI_WR_DATA_LWrite Data Low ByteXXhKhZDI_WR_DATA_HWrite Data High ByteXXhShZDI_WR_DATA_UWrite Data Upper ByteXXhShZDI_RW_CTLRead/Write Control Register00hIhZDI_BUS_CTLBus Control Register00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0Ch         | ZDI_ADDR3_L       | Address Match 3 Low Byte    | XXh   |

| DhZDI_BRK_CTLBreak Control Register00hIhZDI_MASTER_CTLMaster Control Register00hBhZDI_WR_DATA_LWrite Data Low ByteXXtKhZDI_WR_DATA_HWrite Data High ByteXXtShZDI_WR_DATA_UWrite Data Upper ByteXXtShZDI_RW_CTLRead/Write Control Register00hThZDI_BUS_CTLBus Control Register00hIhZDI_IS4Instruction Store 4XXt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0Dh         | ZDI_ADDR3_H       | Address Match 3 High Byte   | XXh   |

| IhZDI_MASTER_CTLMaster Control Register00hBhZDI_WR_DATA_LWrite Data Low ByteXXrWhZDI_WR_DATA_HWrite Data High ByteXXrShZDI_WR_DATA_UWrite Data Upper ByteXXrShZDI_RW_CTLRead/Write Control Register00hThZDI_BUS_CTLBus Control Register00hIhZDI_IS4Instruction Store 4XXr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0Eh         | ZDI_ADDR3_U       | Address Match 4 Upper Byte  | XXh   |

| ZDI_WR_DATA_LWrite Data Low ByteXXtXhZDI_WR_DATA_HWrite Data High ByteXXtXhZDI_WR_DATA_UWrite Data Upper ByteXXtXhZDI_RW_CTLRead/Write Control Register00hYhZDI_BUS_CTLBus Control Register00hIhZDI_IS4Instruction Store 4XXt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10h         | ZDI_BRK_CTL       | Break Control Register      | 00h   |

| InImage: Control RegisterImage: Control Register | 11h         | ZDI_MASTER_CTL    | Master Control Register     | 00h   |

| ZDI_WR_DATA_U       Write Data Upper Byte       XXt         Sh       ZDI_RW_CTL       Read/Write Control Register       00h         7h       ZDI_BUS_CTL       Bus Control Register       00h         Ih       ZDI_IS4       Instruction Store 4       XXt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13h         | ZDI_WR_DATA_L     | Write Data Low Byte         | XXh   |

| Sh       ZDI_RW_CTL       Read/Write Control Register       00h         7h       ZDI_BUS_CTL       Bus Control Register       00h         1h       ZDI_IS4       Instruction Store 4       XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14h         | ZDI_WR_DATA_H     | Write Data High Byte        | XXh   |

| ZDI_BUS_CTL     Bus Control Register     00h       Ih     ZDI_IS4     Instruction Store 4     XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15h         | ZDI_WR_DATA_U     | Write Data Upper Byte       | XXh   |

| Ih     ZDI_IS4     Instruction Store 4     XXI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16h         | ZDI_RW_CTL        | Read/Write Control Register | 00h   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17h         | ZDI_BUS_CTL       | Bus Control Register        | 00h   |

| 2h ZDI IS3 Instruction Store 3 XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21h         | ZDI_IS4           | Instruction Store 4         | XXh   |

| =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22h         | ZDI_IS3           | Instruction Store 3         | XXh   |

| 3h ZDI_IS2 Instruction Store 2 XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23h         | ZDI_IS2           | Instruction Store 2         | XXh   |

| Ih ZDI_IS1 Instruction Store 1 XXI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24h         | ZDI_IS1           | Instruction Store 1         | XXh   |

| 5h ZDI_IS0 Instruction Store 0 XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25h         | ZDI_IS0           | Instruction Store 0         | XXh   |

| Dh ZDI_WR_MEM Write Memory Register XXh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30h         | ZDI_WR_MEM        | Write Memory Register       | XXh   |

## Table 133. ZDI Write Only Registers (Continued)

# **ZDI Read Only Registers**

Table 134 lists the ZDI Read Only registers. Many of the ZDI Read Only addresses are shared with ZDI Write Only registers.

| ZDI Address | ZDI Register Name | ZDI Register Function                          | Reset<br>Value |

|-------------|-------------------|------------------------------------------------|----------------|

| 00h         | ZDI_ID_L          | eZ80 <sup>®</sup> Product ID Low Byte Register | 08h            |

| 01h         | ZDI_ID_H          | eZ80 Product ID High Byte Register             | 00h            |

| 02h         | ZDI_ID_REV        | eZ80 Product ID Revision Register              | XXh            |

#### Table 134. ZDI Read Only Registers

ilog 295

# Table 178. Transmit Descriptor Status

| Bit   | Name                 | Description                                                                                                                                                                                                                               |

|-------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | TxOwner              | 0 = Host (eZ80 <sup>®</sup> ) owns, 1 = EMAC owns.                                                                                                                                                                                        |

| 14    | TxAbort              | 1 = Packet aborted (not transmitted).                                                                                                                                                                                                     |

| 13    | TxBPA                | 1 = Back pressure applied.                                                                                                                                                                                                                |

| 12    | TxHuge               | 1 = Packet size is very large (Pkt_Size > EmacMaxf).                                                                                                                                                                                      |

| 11    | TxLOOR               | 1 = Type/Length field is out of range (larger than 1518 bytes).                                                                                                                                                                           |

| 10    | TxLCError            | 1 = Type/Length field is not a Type field and it does not match the actual data byte length of the Ethernet packet. The data byte length is the number of bytes of data in the Ethernet packet between the Type/Length field and the FCS. |

| 9     | TxCrcError           | 1 = The packet contains an invalid FCS (CRC). This flag is set when CRCEN = 0 and the last 4 bytes of the packet are not the valid FCS.                                                                                                   |

| 8     | TxPktDeferred        | 1 = Packet is deferred.                                                                                                                                                                                                                   |

| 7     | TxXsDfr              | 1 = Packet is excessively deferred. (> 6071 nibble times in 100BaseT or 24,287 bit times in 10BaseT).                                                                                                                                     |

| 6     | TxFifoUnderRun       | 1 = TxFIFO experiences underrun. Check the TxAbort bit to see if the packet is aborted or retried.                                                                                                                                        |

| 5     | TxLateCol            | 1 = A late collision occurs. Collision is detected at a byte count > EmacCfg2[5:0]. Collisions detected before the byte count reaches EmacCfg2[5:0] are early collisions and retried.                                                     |

| 4     | TxMaxCol             | 1 = The maximum number of collisions occurs. #Collisions > EmacCfg3[3:0]. These packets are aborted.                                                                                                                                      |

| [3:0] | TxNumberOfCollisions | This field contains the number of collisions that occur while transmitting the packet.                                                                                                                                                    |

# Table 179. Receive Descriptor Status

| Bit | Name         | Description                               |

|-----|--------------|-------------------------------------------|

| 15  | RxOK         | 1 = Packet received intact.               |

| 14  | RxAlignError | 1 = An odd number of nibbles is received. |

| 13  | RxCrcError   | 1 = The CRC (FCS) is in error.            |

ilog|<sub>2</sub>

transfer capabilities at certain system operating frequencies, you must first understand the internal data bus bandwidth that is required under ideal conditions.

For 10BaseT Ethernet connectivity, the data rate is 10 Mbps, which equates to 1.25 Mbps. If the eZ80F91 MCU is operating in FULL-DUPLEX mode over 10BaseT, the data rate for RX data and TX data is 1.25 Mbps. Because raw data transfers at this rate consume a certain amount of CPU bandwidth, the CPU must support traffic from both directions as well as operate at a minimum clock frequency of (1.25 + 1.25) \* 2 = 5 MHz while transferring Ethernet packets to and from the physical layer.

Similarly, for 100BaseT Ethernet, the data rate is 100 Mbps, which equates to 12.5 Mbps. If the eZ80F91 MCU is operating in FULL-DUPLEX mode over 100BaseT, the data rate for RX data and TX data is 12.5 Mbps. Because raw data transfers at this rate consume a certain amount of CPU bandwidth, the CPU must support traffic from both directions as well as operate at a minimum clock frequency of  $(12.5 + 12.5) \times 2 = 50$  MHz while transferring Ethernet packets to and from the physical layer. Consequently, 50 MHz is the minimum system clock speed that the eZ80<sup>®</sup> CPU requires to sustain EMAC data transfers while not including any software overhead or additional eZ80 tasks.

The FIFO functionality of the EMAC operates at any frequency as long as the user application avoids overrun and underrun errors via higher-level flow control. Actual application requirements will dictate Ethernet modes of operation (FULL-DUPLEX, HALF-DUPLEX, etc.). Because each user and application is different, it becomes your responsibility to control the data flow with these parameters. Under ideal conditions, the system clock will operate somewhere between 5 MHz and 50 MHz to handle the EMAC data rates.

## EMAC Operation in HALT Modes

When the CPU is in HALT mode, the eZ80F91 device's EMAC block cannot be disabled as other peripherals. Upon receipt of an Ethernet packet, a maskable Receive interrupt is generated by the EMAC block, just as it would be in a non-halt mode. Accordingly, the processor wakes up and continues with the user-defined application.

### **EMAC Registers**

After a system reset, all EMAC registers are set to their default values. Any Writes to unused registers or register bits are ignored and reads return a value of 0. For compatibility with future revisions, unused bits within a register must always be written with a value of 0. Read/Write attributes, reset conditions, and bit descriptions of all of the EMAC registers are provided in this section.

ilog <sub>309</sub>

| Bit                                    | 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------|---|-----|-----|-----|-----|-----|-----|-----|

| Reset                                  | 0 | 0   | 0   | 1   | 0   | 0   | 1   | 0   |

| CPU Access                             | R | R/W |

| Note: R = Read Only; R/W = Read/Write. |   |     |     |     |     |     |     |     |

### Table 193. EMAC Non-Back-To-Back IPG Register—Part 2 (EMAC\_IPGR2 = 002Fh)

| Bit<br>Position | Value   | Description                                                                                   |

|-----------------|---------|-----------------------------------------------------------------------------------------------|

| 7               | 0       | Reserved.                                                                                     |

| [6:0]<br>IPGR2  | 00h–7Fh | This bit range is a programmable field representing the non-<br>back-to-back interpacket gap. |

### EMAC Maximum Frame Length Register—Low and High Bytes

The 16-bit field resets to 0600h, which represents a maximum Receive frame of 1536 bytes. An untagged maximum size Ethernet frame (packet) is 1518 bytes. A tagged frame adds four bytes for a total of 1522 bytes. If a shorter maximum length restriction is more appropriate, program this field. See Table 194 and Table 195 on page 310.

**Note:** The default value of 1536 bytes is large enough to cover the largest Ethernet packet, which contains 14 bytes of Ethernet header, 1500 bytes of MAC client data, plus 4 bytes of CRC for a total of 1518 maximum bytes. This value is also large enough to cover VLAN frames with prepended headers up to 18 bytes.

VLAN frames have a proprietary header prepended to the Ethernet packet. Setting the DCRCC bit in EMAC\_CFG1 will exclude the first 4 bytes—the proprietary header—from the CRC calculation. For VLAN packets, the maximum frame length is 1522, 4 more than for normal Ethernet packets due to the 4 byte prepended header. Normal packets feature a 12 byte header before the MAC client data. For more information about this topic, refer to Figure 3-1 of the IEEE 802.3 specification.

If a proprietary header is allowed, this field must be adjusted accordingly. For example, if 12 byte headers are prepended to frames, MAXF must be set to 1524 bytes to allow the maximum VLAN tagged frame plus the 12 byte header. The default value of 1536 is large enough to cover the largest Ethernet packet: 14 bytes of Ethernet header, 1500 bytes of MAC client data, plus 4 bytes of CRC for a total of 1518 bytes maximum. It is also large enough to cover VLAN packets with prepended headers up to 18 bytes. The following formulas illustrate:

**Ethernet Packet**— Maximum frame size = normal Ethernet packet – 14 (Ethernet header) + 1500 (MAC client data) + 4 (CRC) = 1518 bytes

# ilog <sub>322</sub>

| Bit                                    |         | 7   | 6                                                                                                                                                                                                                                     | 5 | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|-----|-----|

| Reset                                  |         | 0   | 0                                                                                                                                                                                                                                     | 0 | 0   | 0   | 0   | 0   | 0   |

| CPU Access                             |         | R   | R                                                                                                                                                                                                                                     | R | R/W | R/W | R/W | R/W | R/W |

| Note: R = Read Only, R/W = Read/Write. |         |     |                                                                                                                                                                                                                                       |   |     |     |     |     |     |

| Bit<br>Position                        | Value   | Des | cription                                                                                                                                                                                                                              |   |     |     |     |     |     |

| [7:0]<br>EMAC_RRP_H                    | 00h-FFI | Rec | These bits represent the High byte of the 2-byte EMAC<br>Receive Read Pointer value, {EMAC_RRP_H,<br>EMAC_RRP_L}. Bit 7 is bit 15 (msb) of the 16-bit value. Bits<br>7:5 default to 000 on reset; bit 0 is bit 8 of the 16-bit value. |   |     |     |     |     |     |

#### Table 213. EMAC Receive Read Pointer Register—High Byte (EMAC\_RRP\_H = 004Ah)

#### **EMAC Buffer Size Register**

The lower six bits of this register set the level at which the EMAC either transmits a pause control frame or jams the Ethernet bus, depending on the mode selected. When each of these bits contain a zero, this feature is disabled.

In FULL-DUPLEX mode, a Pause Control Frame is transmitted as a One-shot operation. The software must free up a number of Rx buffers so that the number of buffers remaining, EmacBlksLeft, is greater than TCPF\_LEV.

In HALF-DUPLEX mode, the EMAC jams the Ethernet by sending a continuous stream of hexadecimal 5s (5fh). When the software frees up the Rx buffers and the number of buffers remaining, EmacBlksLeft, is greater than TCPF\_LEV, the EMAC stops jamming.

ilog 340

#### **Table 233. DC Characteristics**

|                  | Parameter                     | T <sub>A</sub> =<br>0 °C to 70 °C |     |                       | T <sub>A</sub> =<br>−40 ºC to 105 ºC |                  |                       |       |                                                             |

|------------------|-------------------------------|-----------------------------------|-----|-----------------------|--------------------------------------|------------------|-----------------------|-------|-------------------------------------------------------------|

| Symbol           |                               | Minimum Typ                       |     | Maximum               | Minimum                              | Typ <sup>2</sup> | Maximum               | Units | Conditions                                                  |

| V <sub>DD</sub>  | Supply Voltage                | 3.0                               | 3.3 | 3.6                   | 3.0                                  | 3.3              | 3.6                   | V     |                                                             |