Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ80                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 50MHz                                                     |

| Connectivity               | Ethernet, I <sup>2</sup> C, IrDA, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 256KB (256K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 16K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | <u>.</u>                                                  |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 144-LBGA                                                  |

| Supplier Device Package    | 144-BGA (13x13)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f91na050ec |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog

26

**PLL Clock**—The eZ80F91 internal PLL driven by external crystals or external crystal oscillators in the range of 1 MHz to 10 MHz generates an SCLK up to 50 MHz. For more-details, see Phase-Locked Loop on page 265.

### SCLK Source Selection Example

For additional SCLK source selection examples, refer to *Crystal Oscillator/Resonator Guidelines for eZ80<sup>®</sup> and eZ80Acclaim!<sup>®</sup> Devices Technical Note (TN0013)* available on www.zilog.com.

ilog

## Reset

The Reset controller within the eZ80F91 device features a consistent reset function for all types of resets that affects the system. A system reset, referred in this document as RESET, returns the eZ80F91 to a defined state. All internal registers affected by a RESET return to their default conditions. RESET configures the GPIO port pins as inputs and clears the CPU's Program Counter to 000000h. Program code execution ceases during RESET.

The events that cause a RESET are:

- Power-on reset (POR).

- Low-Voltage Brownout (VBO).

- External **RESET** pin assertion.

- Watchdog Timer (WDT) time-out when configured to generate a RESET.

- Real-Time Clock alarm with the CPU in low-power SLEEP mode.

- Execution of a Debug RESET command.

During RESET, an internal RESET mode timer holds the system in RESET for 1025 system clock (SCLK) cycles to allow sufficient time for the primary crystal oscillator to stabilize. For internal RESET sources, the RESET mode timer begins incrementing on the next rising edge of SCLK following deactivation of the signal that is initiating the RESET event. For external RESET pin assertion, the RESET mode timer begins on the next rising edge of SCLK following assertion of the RESET mode timer begins on the next rising edge of SCLK following assertion of the RESET mode timer begins on the next rising edge of SCLK following assertion of the RESET mode timer begins on the next rising edge of SCLK following assertion of the RESET pin for three consecutive SCLK cycles.

**Note:** The default clock source for SCLK on RESET is the crystal input  $(X_{IN})$ . See the CLK\_MUX values in the PLL Control Register 0, (see Table 154 on page 269).

### External Reset Input and Indicator

The eZ80F91 RESET pin functions as both open-drain (active Low) RESET mode indicator and active Low RESET input. When a RESET event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the internal RESET mode timer times out. If the external reset signal is released prior to the end of the 1025 count time-out, program execution begins following the RESET mode time-out. If the external reset signal is released after the end of the 1025 count timeout, then program execution begins following release of the RESET input (the RESET pin is High for four consecutive SCLK cycles).

## ilog <sub>47</sub>

### Table 4. Clock Peripheral Power-Down Register 1 (CLK\_PPD1 = 00DBh)

| Bit                            | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access                     | R/W |

| <b>Note:</b> R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit Position    | Value | Description                                                                                          |

|-----------------|-------|------------------------------------------------------------------------------------------------------|

| 7<br>GPIO_D_OFF | 1     | System clock to GPIO Port D is powered down.<br>Port D alternate functions do not operate correctly. |

|                 | 0     | System clock to GPIO Port D is powered up.                                                           |

| 6<br>GPIO_C_OFF | 1     | System clock to GPIO Port C is powered down.<br>Port C alternate functions do not operate correctly. |

|                 | 0     | System clock to GPIO Port C is powered up.                                                           |

| 5<br>GPIO_B_OFF | 1     | System clock to GPIO Port B is powered down.<br>Port B alternate functions do not operate correctly. |

|                 | 0     | System clock to GPIO Port B is powered up.                                                           |

| 4<br>GPIO_A_OFF | 1     | System clock to GPIO Port A is powered down.<br>Port A alternate functions do not operate correctly. |

|                 | 0     | System clock to GPIO Port A is powered up.                                                           |

| 3               | 1     | System clock to SPI is powered down.                                                                 |

| SPI_OFF         | 0     | System clock to SPI is powered up.                                                                   |

| 2               | 1     | System clock to I <sup>2</sup> C is powered down.                                                    |

| I2C_OFF         | 0     | System clock to I <sup>2</sup> C is powered up.                                                      |

| 1               | 1     | System clock to UART1 is powered down.                                                               |

| UART1_OFF       | 0     | System clock to UART1 is powered up.                                                                 |

| 0               | 1     | System clock to UART0 and IrDA endec is powered down.                                                |

| UART0_OFF       | 0     | System clock to UART0 and IrDA endec is powered up.                                                  |

### Table 21. Intel Bus Mode Read States—Separate Address and Data Buses (Continued)

STATE T3 During State T3, no bus signals are altered. If the external READY (WAIT) pin is driven Low at least one CPU system clock cycle prior to the beginning of State T3, additional wait states (T<sub>WAIT</sub>) are asserted until the READY pin is driven High.

STATE T4 The CPU latches the Read data at the beginning of State T4. The CPU deasserts the RD signal and completes the Intel bus mode cycle.

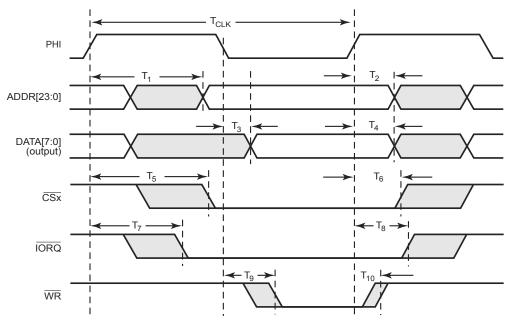

During Write operations with separate address and data buses, the Intel bus mode employs four states—T1, T2, T3, and T4 as listed in Table 22.

### Table 22. Intel Bus Mode Write States—Separate Address and Data Buses

| STATE T1 | The Write cycle begins in State T1. The CPU drives the address onto the address bus, the associated chip select signal is asserted, and the data is driven onto the data bus. The CPU drives the ALE signal High at the beginning of T1. During the middle of T1, the CPU drives ALE Low to facilitate the latching of the address. |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATE T2 | During State T2, the CPU asserts the $\overline{\text{WR}}$ signal. Depending on the instruction, either the MREQ or IORQ signal is asserted.                                                                                                                                                                                       |

| STATE T3 | During State T3, no bus signals are altered. If the external READY (WAIT) pin is driven Low at least one CPU system clock cycle prior to the beginning of State T3, additional wait states ( $T_{WAIT}$ ) are asserted until the READY pin is driven High.                                                                          |

| STATE T4 | The CPU deasserts the $\overline{\rm WR}$ signal at the beginning of State T4. The CPU holds the data and address buses till the end of T4. The bus cycle is completed at the end of T4.                                                                                                                                            |

Intel bus mode timing is displayed for a Read operation in Figure 13 on page 76 and for a Write operation in Figure 14 on page 77. If the READY signal (external WAIT pin) is driven Low prior to the beginning of State T3, additional wait states ( $T_{WAIT}$ ) are asserted until the READY signal is driven High. The Intel bus mode states are configured for 2 to 15 CPU system clock cycles. In the Figure 13 on page 76 and Figure 14 on page 77, each Intel bus mode state is 2 CPU system clock cycles in duration. Figure 13 on page 76 and Figure 14 on page 77 also display the assertion of one Wait state ( $T_{WAIT}$ ) by the selected peripheral.

ilog <sub>113</sub>

### Table 46. Flash Program Control Register (FLASH\_PGCTL = 00FFh)

| Bit                                    | 7 | 6 | 5 | 4 | 3 | 2   | 1   | 0   |

|----------------------------------------|---|---|---|---|---|-----|-----|-----|

| Reset                                  | 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0   |

| CPU Access                             | R | R | R | R | R | R/W | R/W | R/W |

| Note: R/W = Read/Write, R = Read Only. |   |   |   |   |   |     |     |     |

| Bit<br>Position | Value | Description                                                                                                                                |

|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| [7:3]           | 00h   | Reserved.                                                                                                                                  |

| [2]             | 0     | Row Program Disable or Row Program completed.                                                                                              |

| ROW_PGM         | 1     | Row Program Enable. This bit automatically resets to 0 when<br>the row address reaches 256 or when the Row Program<br>operation times out. |

| [1]<br>PG_ERASE | 0     | Page Erase Disable (Page Erase completed).                                                                                                 |

|                 | 1     | Page Erase Enable. This bit automatically resets to 0 when the PAGE ERASE operation is complete.                                           |

| [0]             | 0     | Mass Erase Disable (Mass Erase completed).                                                                                                 |

| MASS_ERASE      | 1     | Mass Erase Enable. This bit automatically resets to 0 when the MASS ERASE operation is complete.                                           |

ilog

129

Asserting TMR3\_OC\_CTL1[MAST\_MODE] selects MASTER MODE for all OUTPUT COMPARE events and sets output 0 as the master. As a result, outputs 1, 2, and 3 are caused to disregard output-specific configuration and comparison values and instead mimic the current settings for output 0.

The OCx bits in the TMR3\_IIR register are set whenever the corresponding timer compares occur. TMR3\_IER[IRQ\_OCx\_EN] allows the compare event to generate a timer interrupt.

### **Timer Port Pin Allocation**

The eZ80F91 device timers interface to the outside world via Ports A and B. These ports are also used for GPIO as well as other assorted functions. Table 53 on page 129 lists the timer pins and their respective functions.

|      |                   | Timer F           | er Function             |                         |  |

|------|-------------------|-------------------|-------------------------|-------------------------|--|

| Port | GPIO Port<br>Bits | GPIO Port<br>Mode | PWM_CTL1<br>MPWM_EN = 0 | PWM_CTL1<br>MPWM_EN = 1 |  |

| А    | PA0               | 7                 | OC0                     | PWM0                    |  |

|      | PA1               | 7                 | OC1                     | PWM1                    |  |

|      | PA2               | 7                 | OC2                     | PWM2                    |  |

|      | PA3               | 7                 | OC3                     | PWM3                    |  |

|      |                   |                   | PWM_CTL1<br>PAIR_EN = 0 | PWM_CTL1<br>PAIR_EN = 1 |  |

|      | PA4               | 7                 | TOUT0                   | PWM0                    |  |

|      | PA5               | 7                 | TOUT2                   | PWM1                    |  |

|      | PA6               | 7                 | EC1                     | PWM2                    |  |

|      | PA7               | 7                 |                         | PWM3                    |  |

| В    | PB0               | 7                 | IC0/                    | EC0                     |  |

|      | PB1               | 7                 | IC                      | 21                      |  |

|      | PB4               | 7                 | IC                      | 2                       |  |

|      | PB5               | 7                 | IC                      | 23                      |  |

### Table 53. GPIO Mode Selection Using Timer Pins

ilog <sub>184</sub>

| Bit                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|---|---|---|---|---|---|---|---|

| Reset                 | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access            | W | W | W | W | W | W | W | W |

| Note: W = Write Only. |   |   |   | 1 |   |   |   |   |

### Table 96. UART Transmit Holding Registers (UART0\_THR = 00C0h, UART1\_THR = 00D0h)

| Bit<br>Position | Value   | Description         |

|-----------------|---------|---------------------|

| [7:0]<br>TxD    | 00h–FFh | Transmit data byte. |

### **UART Receive Buffer Register**

The bits in this register reflect the data received. If less than eight bits are programmed for reception, the lower bits of the byte reflect the bits received, whereas upper unused bits are 0. The Receive FIFO is mapped at this address. If the FIFO is disabled, this buffer is only one byte deep.

These registers share the same address space as the UARTx\_THR and UARTx\_BRG\_L registers. See Table 97.

| Bit                               |  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------------------|--|---|---|---|---|---|---|---|---|

| Reset                             |  | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access                        |  | R | R | R | R | R | R | R | R |

| Note: R = Read only.              |  |   |   |   |   |   |   |   |   |

| Bit<br>Position Value Description |  |   |   |   |   |   |   |   |   |

|              |         | •                  |

|--------------|---------|--------------------|

| [7:0]<br>RxD | 00h–FFh | Receive data byte. |

### **UART Interrupt Enable Register**

The UARTx\_IER register is used to enable and disable the UART interrupts. The UARTx\_IER registers share the same I/O addresses as the UARTx\_BRG\_H registers. See Table 98 on page 185.

ilog <sub>185</sub>

### Table 98. UART Interrupt Enable Registers (UART0\_IER = 00C1h, UART1\_IER = 00D1h)

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position | Value | Description                                                                                                                                                           |  |  |  |  |  |

|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [7:5]           | 000   | Reserved.                                                                                                                                                             |  |  |  |  |  |

| 4               | 0     | Transmission complete interrupt is disabled.                                                                                                                          |  |  |  |  |  |

| 4<br>TCIE       | 1     | Transmission complete interrupt is generated when both the transmit hold register and the transmit shift register are empty.                                          |  |  |  |  |  |

| 3               | 0     | Modem interrupt on edge detect of status inputs is disabled.                                                                                                          |  |  |  |  |  |

| MIIE            | 1     | Modem interrupt on edge detect of status inputs is enabled.                                                                                                           |  |  |  |  |  |

| 2<br>LSIE       | 0     | Line status interrupt is disabled.                                                                                                                                    |  |  |  |  |  |

|                 | 1     | Line status interrupt is enabled for receive data errors: incorrect parity bit received, framing error, overrun error, or break detection.                            |  |  |  |  |  |

| 4               | 0     | Transmit interrupt is disabled.                                                                                                                                       |  |  |  |  |  |

| TIE             | 1     | Transmit interrupt is enabled. Interrupt is generated when the transmit FIFO/buffer is empty indicating no more bytes available for transmission.                     |  |  |  |  |  |

|                 | 0     | Receive interrupt is disabled.                                                                                                                                        |  |  |  |  |  |

| 0<br>RIE        | 1     | Receive interrupt and receiver time-out interrupt are enabled. Interrupt is generated if the FIFO/buffer contains data ready to be read or if the receiver times out. |  |  |  |  |  |

ilog <sub>193</sub>

| Bit      |       |                                                                                                                                                                                                                                                                                                                |

|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Position | Value | Description                                                                                                                                                                                                                                                                                                    |

|          | 0     | This bit is reset to 0 when the UARTx_RBR register is read or all bytes are read from the receiver FIFO.                                                                                                                                                                                                       |

| 0<br>DR  | 1     | Data ready. If the FIFO is not enabled, this bit is set to 1 when<br>a complete incoming character is transferred into the receiver<br>buffer register from the receiver shift register. If the FIFO is<br>enabled, this bit is set to 1 when a character is received and<br>transferred to the receiver FIFO. |

### **UART Modem Status Register**

This register is used to show the status of the UART signals. See Table 107.

Table 107. UART Modem Status Registers (UART0\_MSR = 00C6h, UART1\_MSR = 00D6h)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read only. |   | l |   |   |   |   | I |   |

| Bit<br>Position | Value | Description                                                                                                                                                                           |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DCD        | 0–1   | Data Carrier Detect<br>In NORMAL mode, this bit reflects the inverted state of the<br>DCDx input pin. In LOOP BACK mode, this bit reflects the<br>value of the UARTx_MCTL[3] = out2.  |

| 6<br>RI         | 0–1   | Ring Indicator<br>In NORMAL mode, this bit reflects the inverted state of the $\overline{RIx}$ input pin. In LOOP BACK mode, this bit reflects the value of the UARTx_MCTL[2] = out1. |

| 5<br>DSR        | 0–1   | Data Set Ready<br>In NORMAL mode, this bit reflects the inverted state of the<br>DSRx input pin. In LOOP BACK mode, this bit reflects the<br>value of the UARTx_MCTL[0] = DTR.        |

| 4<br>CTS        | 0–1   | Clear to Send<br>In NORMAL mode, this bit reflects the inverted state of the<br>CTSx input pin. In LOOP BACK mode, this bit reflects the value<br>of the UARTx_MCTL[1] = RTS.         |

ilog <sub>199</sub>

### Infrared Encoder/Decoder Register

After a RESET, the Infrared Encoder/Decoder Register is set to its default value. Any Writes to unused register bits are ignored and reads return a value of 0. The IR\_CTL register is listed in Table 110.

### Table 110. Infrared Encoder/Decoder Control Registers (IR\_CTL = 00BFh)

| Bit                                    | 7   | 6   | 5   | 4   | 3 | 2   | 1   | 0   |

|----------------------------------------|-----|-----|-----|-----|---|-----|-----|-----|

| Reset                                  | 0   | 0   | 0   | 0   | 0 | 0   | 0   | 0   |

| CPU Access                             | R/W | R/W | R/W | R/W | R | R/W | R/W | R/W |

| Note: R = Read only; R/W = Read/Write. |     |     |     |     |   |     |     |     |

| Bit                |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Position           | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| [7:4]<br>MIN_PULSE | 0000  | Minimum receive pulse width control. When this field is equal to 0x0, the IrDA decoder uses edge detection to accept arbitrarily narrow (that is, short) input pulses.                                                                                                                                                                                                                                                                                              |

|                    | 1h-Fh | When not equal to 0x0, this field forms the most-significant four<br>bits of the 6-bit down-counter used to determine if an input<br>pulse will be ignored because it is too narrow. The lower two<br>counter bits are hard-coded to load with 0x3, resulting in a total<br>down-count equal to ((IR_CTL[4:0]MIN_PULSE * 4) + 3). To be<br>accepted, input pulses must have a width greater than or equal<br>to the down-count value times the system clock period. |

| 3                  | 0     | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2                  | 0     | Internal LOOP BACK mode is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LOOP_BACK          | 1     | Internal LOOP BACK mode is enabled.<br>IR_TxD output is inverted and connected to IR_RxD input for<br>internal loop back testing.                                                                                                                                                                                                                                                                                                                                   |

| 1                  | 0     | IR_RxD data is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IR_RxEN            | 1     | IR_RxD data is passed to UART0 RxD.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0                  | 0     | Endec is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IR_EN              | 1     | Endec is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

218

#### Next I<sup>2</sup>C Action I<sup>2</sup>C State Code **Microcontroller Response** Clear IFLG 38h Arbitration lost Return to idle Or set STA, clear IFLG Transmit START when bus free Clear IFLG, clear AAK = $0^2$ 68h Arbitration lost, Receive data byte, transmit NACK SLA+W received, Or clear IFLG, set AAK = 1 Receive data byte, transmit ACK ACK transmitted<sup>1</sup> B0h Arbitration lost, Write byte to DATA, Transmit last byte, SLA+R received. clear IFLG, clear AAK = 0 receive ACK ACK transmitted<sup>3</sup> Or write byte to DATA, Transmit data byte, clear IFLG, set AAK = 1 receive ACK D0h Second address byte Write byte to data, Transmit data byte, + W transmitted. clear IFLG receive ACK ACK received Or set STA, clear IFLG Transmit repeated START Or set STP, clear IFLG Transmit STOP Or set STA & STP, Transmit STOP then clear IFLG START D8h Same as code D0h Same as code D0h Second address byte + W transmitted, ACK not received Notes

### Table 119. I<sup>2</sup>C 10-Bit Master Transmit Status Codes

1. W is defined as the Write bit; that is, the lsb is cleared to 0.

2. AAK is an  $I^2C$  control bit that identifies which ACK signal to transmit.

3. R is defined as the Read bit; that is, the lsb is set to 1.

If a repeated START condition is transmitted, the status code is 10h instead of 08h. After each data byte is transmitted, the IFLG is set to 1 and one of the status codes listed in Table 120 is loaded into the I2C\_SR register.

222

$I^2C$  goes from MASTER mode to SLAVE TRANSMIT mode when arbitration is lost during the transmission of an address, and the slave address and Read bit are received. This action is represented by the status code BOh in the  $I^2C\_SR$  register.

The data byte to be transmitted is loaded into the  $I^2C_DR$  register and the IFLG bit is cleared to 0. After the  $I^2C$  transmits the byte and receives an ACK, the IFLG bit is set to 1 and the  $I^2C_SR$  register contains B8h. When the final byte to be transmitted is loaded into the  $I^2C_DR$  register, the AAK bit is cleared when the IFLG is cleared to 0. After the final byte is transmitted, the IFLG is set and the  $I^2C_SR$  register contains C8h and the  $I^2C$  returns to an idle state. The AAK bit must be set to 1 before reentering SLAVE mode.

If no ACK is received after transmitting a byte, the IFLG is set and the  $I^2C\_SR$  register contains C0h. The  $I^2C$  then returns to an idle state. If a STOP condition is detected after an ACK bit, the  $I^2C$  returns to an idle state.

### **Slave Receive**

In SLAVE RECEIVE mode, a number of data bytes are received from a master transmitter. The I<sup>2</sup>C enters SLAVE RECEIVE mode when it receives its own slave address and a Write bit (lsb = 0) after a START condition. The I<sup>2</sup>C transmits an ACK bit and sets the IFLG bit in the I<sup>2</sup>C\_CTL register and the I<sup>2</sup>C\_SR register contains the status code 60h. The I<sup>2</sup>C also enters SLAVE RECEIVE mode when it receives the general call address 00h (if the GCE bit in the I<sup>2</sup>C\_SAR register is set). The status code is then 70h.

When the  $I^2C$  contains a 10-bit slave address (signified by F0h-F7h in the  $I^2C_SAR$  register), it transmits an acknowledge after the first address byte is received but no interrupt is generated. IFLG is not set and the status does not change. The  $I^2C$  generates an interrupt only after the second address byte is received. The  $I^2C$  sets the IFLG bit and loads the status code as described above.

$I^2C$  goes from MASTER mode to SLAVE RECEIVE mode when arbitration is lost during the transmission of an address, and the slave address and Write bit (or the general call address if the CGE bit in the  $I^2C_SAR$  register is set to 1) are received. The status code in the  $I^2C_SR$  register is 68h if the slave address is received or 78h if the general call address is received. The IFLG bit must be cleared to 0 to allow data transfer to continue.

If the AAK bit in the I<sup>2</sup>C\_CTL register is set to 1 then an ACK bit (Low level on SDA) is transmitted and the IFLG bit is set after each byte is received. The I<sup>2</sup>C\_SR register contains the two status codes 80h or 90h if SLAVE RECEIVE mode is entered with the general call address. The received data byte are read from the I<sup>2</sup>C\_DR register and the IFLG bit must be cleared to allow the transfer to continue. If a STOP condition or a repeated START condition is detected after the acknowledge bit, the IFLG bit is set and the I<sup>2</sup>C\_SR register contains status code A0h.

If the AAK bit is cleared to 0 during a transfer, the  $I^2C$  transmits a NACK bit (High level on SDA) after the next byte is received, and sets the IFLG bit to 1. The  $I^2C\_SR$  register

Note:

ilog <sub>244</sub>

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>ign_low_1  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If brk_addr1 is set to 1, ZDI initiates<br>a break when the entire 24-bit address, ADDR[23:0],<br>matches the 3-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H, ZDI_ADDR1_L}.                                                                         |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is enabled. If brk_addr1 is set to 1, ZDI initiates<br>a break when only the upper 2 bytes of the 24-bit address,<br>ADDR[23:8], match the 2-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H}. As a result, a break occurs anywhere<br>within a 256-byte page.      |

| 1<br>ign_low_0  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If brk_addr0 is set to 1, ZDI initiates<br>a break when the entire 24-bit address, ADDR[23:0],<br>matches the 3-byte value {ZDI_ADDR0_U,<br>ZDI_ADDR0_H, ZDI_ADDR0_L}.                                                                         |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is enabled. If the brk_addr1 is set to 0, ZDI<br>initiates a break when only the upper 2 bytes of the 24-bit<br>address, ADDR[23:8], match the 2 bytes value<br>{ZDI_ADDR0_U, ZDI_ADDR0_H}. As a result, a break<br>occurs anywhere within a 256-byte page. |

| 0               | 0     | ZDI single step mode is disabled.                                                                                                                                                                                                                                                                                                           |

| single_step     | 1     | ZDI single step mode is enabled. ZDI asserts a break following execution of each instruction.                                                                                                                                                                                                                                               |

ilog <sub>279</sub>

### Table 166. Rotate and Shift Instructions (Continued)

| Mnemonic | Instruction                       |

|----------|-----------------------------------|

| RRA      | Rotate Right–Accumulator          |

| RRC      | Rotate Right Circular             |

| RRCA     | Rotate Right Circular–Accumulator |

| RRD      | Rotate Right Decimal              |

| SLA      | Shift Left Arithmetic             |

| SRA      | Shift Right Arithmetic            |

| SRL      | Shift Right Logical               |

280

### **Opcode Map**

Table 167 through Table 173 on page 286 list the hex values for each of the eZ80<sup>®</sup> instructions.

### Table 167. Opcode Map—First Opcode

#### Legend Lower Opcode Nibble Upper Opcode 4 Nibble A AND Mnemonic A,H Second Operand First Operand Lower Nibble (Hex) С D F 3 5 В Е 2 4 7 9 0 1 6 8 A 0 NOF LD LD INC INC LD RLCA ADD LD DEC INC DEC LD RRCA DEC ΕX BC, (BC),A BC В В B,n AF,AF' HL,BC A,(BC) BC С С C,n Mmn DJNZ INC INC DEC LD RLA ADD DEC INC DEC RRA 1 LD LD JR LD LD (DE),A DE HL,DE A,(DE) DE Е d DE, D D D,n d Е E,n Mmn INC INC CPL 2 JR LD LD INC DEC LD DAA JR ADD LD DEC DEC LD Z,d NZ,d HL, (Mmn) HL н н H,n HL,HL HL, HL 1 L L,n Mmn HL (Mmn) 3 JR LD LD INC INC DEC LD SCF JR ADD LD DEC INC DEC LD CCF Α, NC.d SP. (Mmn), SP (HL) (HL) (HL),n CF.d HL,SP SP А А A,n Mmn (Mmn) А LD LD LD LD LD LD LD LD .SIS LD .LIS ID LD LD 4 LD LD suffix B,C B,D B,E B,H B,L B,(HL) B,A C,B suffix C,D C,E C,H C,L C,(HL) C,A 5 LD LD LD LD LD LD LD LD LD .SIL LD LD LD LD .LIL LD D,B D,C suffix D,E D,H D,L D,(HL) D,A E,B E,C E,D suffix E,H E,L E,(HL) E,A 6 LD H,D H,H H,A L,D H,B H,C H,E H,L H,(HL) L,B L.C L,E L,H L,L L,(HL) L,A HALT LD LD Upper Nibble (Hex) LD (HL),C A,C A,(HL) (HL),B (HL),D (HL),E (HL),H (HL),A A,D A,E A,H A,L (HL),L A,B A,A 8 ADD ADD ADD ADD ADD ADD ADD ADD ADC ADC ADC ADC ADC ADC ADC ADC A,B A,C A,D A,E A,H A,L A,(HL) A,A A,B A,C A,D A,E A,H A,L A,(HL) A,A SBC 9 SUB SUB SUB SUB SUB SUB SBC SBC SBC SUB SUB SBC SBC SBC SBC A,E A,(HL) A,B A,C A,D A,E A,H A,L A,(HL) A,A A,B A,C A,D A,H A,L A,A AND AND AND AND AND AND AND AND XOR XOR XOR XOR XOR XOR XOR XOR A.B A.C A.D A.E A.H A.L A,(HL) A.A A.B A.C A.D A.E A.H A.L A,(HL) A.A В OR OR OR OR OR OR OR OR CP CP CP CP CP CP CP CP A,B A,D A,C A,D A,H A,C A,E A,H A,(HL) A,B A,E A,L A,(HL) A,A A,L A,A С RET POP CALL PUSH ADD RST RET JP CALL CALL ADC RST JP JP RET See BC NZ, NZ, Ζ Ζ, 08h NZ Mmn BC A,n 00h Ζ, Mmn A,n Table Mmn Mmn Mmn Mmn 168 PUSH POP JP OUT CALL SUB EXX JP CALL D RST RET IN SBC RST RET See NC DE NC. (n),A NC. DE A,n 10h CF CF, A,(n) CF, 18h A,n Table Mmn Mmn Mmn Mmn 169 Е RET POP JP ΕX CALL PUSH AND RST RET JP JP ΕX CALL See XOR RST PO HL PO, (SP),HL PO, HL A,n 20h ΡE (HL) PE. DE,HL PE, A,n 28h Table Mmn Mmn Mmn Mmn 170 F RET POP JP DI CALL PUSH OR RST RET LD JP ΕI CALL See CP RST AF SP,HL Ρ Ρ. AF 30h Μ Μ, 38h P, A,n Μ, Table A,n Mmn Mmn Mmn Mmn 171

312

### **EMAC Hash Table Register**

The EMAC Hash Table Register represents the 8x8 hash table matrix. This table is used as an option to select between different multicast addresses. If a multicast address is received, the first 6 bits of the CRC are decoded and added to a table that points to a single bit within the hash table matrix. If the selected bit = 1, the multicast packet is accepted. If the bit = 0, the multicast packet is rejected. See Table 197.

# Table 197. EMAC Hash Table Register (EMAC\_HTBL\_0 = 0033h, EMAC\_HTBL\_1 = 0034h, EMAC\_HTBL\_2 = 0035h, EMAC\_HTBL\_3 = 0036h, EMAC\_HTBL\_4 = 0037h, EMAC\_HTBL\_5 = 0038h, EMAC\_HTBL\_6 = 0039h, EMAC\_HTBL\_7 = 003Ah)

| Bit                    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| EMAC_HTBL_0 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| EMAC_HTBL_1 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| EMAC_HTBL_2 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| EMAC_HTBL_3 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| EMAC_HTBL_4 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| EMAC_HTBL_5 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| EMAC_HTBL_6 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| EMAC_HTBL_7 Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access             | R/W |

| Note: R/W = Read/Write |     |     |     |     |     |     |     | •   |

Note: R/W = Read/Write

| Bit<br>Position      | Value       | Description                                                                                                                                                               |

|----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>EMAC_HTBL_x | 00h–<br>FFh | This field is the hash table. The 64 bit hash table is<br>{EMAC_HTBL_7, EMAC_HTBL_6, EMAC_HTBL_5,<br>EMAC_HTBL_4, EMAC_HTBL_3, EMAC_HTBL_2,<br>EMAC_HTBL_1, EMAC_HTBL_0}. |

ilog <sub>333</sub>

### **EMAC FIFO Flags Register**

The FIFO Flags value is set in the EMAC hardware to *half full*, or 16 bytes. See Table 228.

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read Only. |   |   |   |   |   |   |   |   |

| Bit       |       |                                |  |  |  |  |

|-----------|-------|--------------------------------|--|--|--|--|

| Position  | Value | Description                    |  |  |  |  |

| 7<br>TFF  | 1     | Transmit FIFO full             |  |  |  |  |

|           | 0     | Transmit FIFO not full         |  |  |  |  |

| 6         | 0     | Reserved                       |  |  |  |  |

| 5<br>TFAE | 1     | Transmit FIFO almost empty     |  |  |  |  |

|           | 0     | Transmit FIFO not almost empty |  |  |  |  |

| 4<br>TFE  | 1     | Transmit FIFO empty            |  |  |  |  |

|           | 0     | Transmit FIFO not empty        |  |  |  |  |

| 3<br>RFF  | 1     | Receive FIFO full              |  |  |  |  |

|           | 0     | Receive FIFO not full          |  |  |  |  |

| 2<br>RFAF | 1     | Receive FIFO almost full       |  |  |  |  |

|           | 0     | Receive FIFO not almost full   |  |  |  |  |

| 1<br>RFAE | 1     | Receive FIFO almost empty      |  |  |  |  |

|           | 0     | Receive FIFO not almost empty  |  |  |  |  |

| 0<br>RFE  | 1     | Receive FIFO empty             |  |  |  |  |

|           | 0     | Receive FIFO not empty         |  |  |  |  |

### 350

### Table 240. External I/O Read Timing (Continued)

|                 |                                          | Delay (ns) |         |

|-----------------|------------------------------------------|------------|---------|

| Parameter       | Abbreviation                             | Minimum    | Maximum |

| T <sub>8</sub>  | PHI Clock Rise to IORQ Deassertion Delay | 1.0        | 6.3     |

| T <sub>9</sub>  | PHI Clock Rise to RD Assertion Delay     | 2.7        | 7.0     |

| T <sub>10</sub> | PHI Clock Rise to RD Deassertion Delay   | 0.5        | 6.3     |

### **External I/O Write Timing**

Figure 71 and Table 241 on page 351 display the timing for external I/O Writes. PHI clock rise/fall to signal transition timing is independent of the particular bus mode employed  $(eZ80^{\$}, Z80^{\$}, Intel, or Motorola)$ .

Figure 71. External I/O Write Timing

UART Modem Control Register 190 UART Modem Status Interrupt 179 UART Modem Status Register 193 UART Receive Buffer Register 184 UART Receiver 177 UART Receiver Interrupts 178 UART Recommended Usage 179 UART Registers 183 UART Scratch Pad Register 194 UART Transmit Holding Register 183 UART Transmitter 176 UART Transmitter Interrupt 178 Universal Asynchronous Receiver/Transmitter 175 Usage, JTAG Boundary Scan 264

### V

VBO 41, 42, 340 VBO pulse reject period 341 VBO Voltage Threshold 341 VCC 2, 42, 341 VCC ramp rate 341 VCO 266. 273 vco 273 VLAN tagged frame 309 Voltage Brown-Out 340 Voltage Brown-Out Reset 42 Voltage Controlled Oscillator 265 Voltage Controlled Oscillator, PLL 266 voltage signal, high 100 voltage, input 266 voltage, peak-to-peak 273 voltage, supply 2, 50, 211, 267, 339, 340

### W

WAIT 1, 9, 75, 78, 81, 82

WAIT condition 112

WAIT Input Signal 69

WAIT pin, external 71

WAIT state 72, 78, 352, 353

Wait State Timing for Read Operations 352

Wait State Timing for Write Operations 353

WAIT states 58, 75, 78, 87, 239

Wait States 68 Watchdog Timer 1, 45, 115, 116, 238 Watchdog Timer Control Register 117 Watchdog Timer Operation 116 Watchdog Timer Registers 117 Watchdog Timer Reset Register 119 Watchdog Timer time-out 41, 45, 46 wcOl 209 WCOL-see Write Collision 204, 205 WDT 41, 45, 115, 116, 117 WDT clock source 115, 116, 118 WDT oscillator 117 WDT time-out 115, 116, 117, 119 WDT time-out period 116, 118 WP 25 WP pin 97, 107, 108, 109 WR 8, 65, 68, 71, 75, 78, 348, 351 Write Collision 205 write collision 204 write collision, SPI 209

### Χ

XIN input pin 335 XOUT output pin 335

### Ζ

Z80-70 Z80 Bus Mode 71 ZCL 233, 236, 243 ZDA 233, 243, 258 ZDI 231, 232, 257 ZDI Address Match Registers 241 ZDI Block Read 238 ZDI Block Write 236 ZDI Break Control Register 242 ZDI Bus Control Register 249 ZDI Bus Status Register 255 ZDI Clock and Data Conventions 233 ZDI clock pin 233 ZDI data pin 233 ZDI debug control 257 ZDI Master Control Register 245