# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | eZ80                                                          |

| Core Size                  | 8-Bit                                                         |

| Speed                      | 50MHz                                                         |

| Connectivity               | Ethernet, I <sup>2</sup> C, IrDA, SPI, UART/USART             |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                         |

| Number of I/O              | 32                                                            |

| Program Memory Size        | 256KB (256K x 8)                                              |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 16K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                     |

| Data Converters            | -                                                             |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                            |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 144-LBGA                                                      |

| Supplier Device Package    | 144-BGA (13x13)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f91na050ec00tr |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog <sub>18</sub>

| LQFP<br>Pin No | BGA<br>Pin No                            | Symbol | Function                                       | Signal Direction                                                                                                                                                                                                                                      | Description                                                                                                                                                                                                                                           |

|----------------|------------------------------------------|--------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 103            | D11 PB3 GPIO Port B SCK SPI Serial Clock |        | Bidirectional with<br>Schmitt-trigger<br>input | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port B pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |                                                                                                                                                                                                                                                       |

|                |                                          | SCK    |                                                | Bidirectional with<br>Schmitt-trigger<br>input                                                                                                                                                                                                        | SPI serial clock. This signal is multiplexed with PB3.                                                                                                                                                                                                |

| 104            | E9                                       | PB4    | GPIO Port B                                    | Bidirectional with<br>Schmitt-trigger<br>input                                                                                                                                                                                                        | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port B pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |                                          | IC2    | Input Capture                                  | Schmitt-trigger<br>input                                                                                                                                                                                                                              | Input Capture A Signal to Timer 3.<br>This signal is multiplexed with PB4.                                                                                                                                                                            |

| 105            | D10                                      | PB5    | GPIO Port B                                    | Bidirectional with<br>Schmitt-trigger<br>input                                                                                                                                                                                                        | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port B pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |                                          | IC3    | Input Capture                                  | Schmitt-trigger<br>input                                                                                                                                                                                                                              | Input Capture B Signal to Timer 3.<br>This signal is multiplexed with PB5.                                                                                                                                                                            |

## Table 2. Pin Identification on the eZ80F91 Device (Continued)

ilog <sub>21</sub>

| LQFP<br>Pin No | BGA<br>Pin No | Symbol | Function                 | Signal Direction | Description                                                                                                                                                                                                                                           |

|----------------|---------------|--------|--------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 117            | B9            | PA3    | GPIO Port A              | Bidirectional    | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port A pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |               | PWM3   | PWM Output 3             | Output           | This pin is used by Timer 3 for PWM<br>3. This signal is multiplexed with PA3.                                                                                                                                                                        |

|                |               | OC3    | Output<br>Compare 3      | Output           | This pin is used by Timer 3 for Output<br>Compare 3 This signal is multiplexed<br>with PA3.                                                                                                                                                           |

| 118            | 8 A9 PA4 (    |        | GPIO Port A              | Bidirectional    | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port A pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |               | PWM0   | PWM Output 0<br>Inverted | Output           | This pin is used by Timer 3 for<br>negative PWM 0. This signal is<br>multiplexed with PA4.                                                                                                                                                            |

|                |               | TOUT0  | Timer Out                | Output           | This pin is used by Timer 0 timer-out signal. This signal is multiplexed with PA4.                                                                                                                                                                    |

| 119            | C9            | PA5    | GPIO Port A              | Bidirectional    | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port A pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |               | PWM1   | PWM Output 1<br>Inverted | Output           | This pin is used by Timer 3 for negative PWM 1. This signal is multiplexed with PA5.                                                                                                                                                                  |

|                |               | TOUT2  | Timer Out                | Output           | This pin is used by the Timer 2 timer-<br>out signal. This signal is multiplexed<br>with PA5.                                                                                                                                                         |

## Table 2. Pin Identification on the eZ80F91 Device (Continued)

ilog <sub>32</sub>

| Address<br>(hex) | Mnemonic     | Name                                                 | Reset<br>(hex) | CPU<br>Access | Page<br>No |

|------------------|--------------|------------------------------------------------------|----------------|---------------|------------|

| 007D             | PWM0R_H      | PWM 0 Rising-Edge<br>Register—High Byte              | XX             | R/W           | 157        |

|                  | TMR3_CAPA_H  | Timer 3 Capture Value A<br>Register—High Byte        | XX             | R/W           | 141        |

| 007E             | PWM1R_L      | PWM 1 Rising-Edge<br>Register—Low Byte               | XX             | R/W           | 157        |

|                  | TMR3_CAPB_L  | Timer 3 Capture Value B<br>Register—Low Byte         | XX             | R/W           | 141        |

| 007F             | PWM1R_H      | PWM 1 Rising-Edge<br>Register—High Byte              | XX             | R/W           | 157        |

|                  | TMR3_CAPB_H  | Timer 3 Capture Value B<br>Register—High Byte        | XX             | R/W           | 142        |

| 0080             | PWM2R_L      | PWM 2 Rising-Edge<br>Register—Low Byte               | XX             | R/W           | 157        |

|                  | TMR3_OC_CTL1 | Timer 3 Output Compare Control<br>Register 1         | 00             | R/W           | 132        |

| 0081             | PWM2R_H      | PWM 2 Rising-Edge<br>Register—High Byte              | XX             | R/W           | 157        |

|                  | TMR3_OC_CTL2 | Timer 3 Output Compare Control<br>Register 2         | 00             | R/W           | 132        |

| 0082             | PWM3R_L      | PWM 3 Rising-Edge<br>Register—Low Byte               | XX             | R/W           | 157        |

|                  | TMR3_OC0_L   | Timer 3 Output Compare 0 Value<br>Register—Low Byte  | XX             | R/W           | 144        |

| 0083             | PWM3R_H      | PWM 3 Rising-Edge<br>Register—High Byte              | XX             | R/W           | 157        |

|                  | TMR3_OC0_H   | Timer 3 Output Compare 0 Value<br>Register—High Byte | XX             | R/W           | 145        |

| 0084             | PWM0F_L      | PWM 0 Falling-Edge<br>Register—Low Byte              | XX             | R/W           | 158        |

|                  | TMR3_OC1_L   | Timer 3 Output Compare 1 Value<br>Register—Low Byte  | XX             | R/W           | 144        |

## Table 3. Register Map (Continued)

ilog

59

boundary. Setting the LSB of the I register produces no effect on the interrupt vector address.

| Memory<br>Mode        | ADL<br>Bit | MADL<br>Bit | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z80 <sup>®</sup> Mode | 0          | 0           | Read the LSB of the interrupt vector placed on the internal vectored interrupt<br>bus, IVECT [8:0], by the interrupting peripheral.<br>IEF1 $\leftarrow$ 0<br>IEF2 $\leftarrow$ 0<br>The Starting Program Counter is effective {MBASE, PC[15:0]}.<br>Push the 2-byte return address PC[15:0] onto the ({MBASE,SPS}) stack.<br>The ADL mode bit remains cleared to 0.<br>The interrupt vector address is located at { MBASE, I[7:1], IVECT[8:0] }.<br>PC[23:0] $\leftarrow$ ( { MBASE, I[7:1], IVECT[8:0] } ).<br>The interrupt service routine must end with RETI.                                                                                                           |

| ADL Mode              | 1          | 0           | Read the LSB of the interrupt vector placed on the internal vectored interrupt<br>bus, IVECT [8:0], by the interrupting peripheral.<br>IEF1 $\leftarrow 0$<br>IEF2 $\leftarrow 0$<br>The Starting Program Counter is PC[23:0].<br>Push the 3-byte return address, PC[23:0], onto the SPL stack.<br>The ADL mode bit remains set to 1.<br>The interrupt vector address is located at { I[15:1], IVECT[8:0] }.<br>PC[23:0] $\leftarrow$ ( { I[15:1], IVECT[8:0] } ).<br>The interrupt service routine must end with RETI.                                                                                                                                                      |

| Z80 Mode              | 0          | 1           | <ul> <li>Read the LSB of the interrupt vector placed on the internal vectored interrupt bus, IVECT[8:0], bus by the interrupting peripheral.</li> <li>IEF1 ← 0</li> <li>IEF2 ← 0</li> <li>The Starting Program Counter is effective {MBASE, PC[15:0]}.</li> <li>Push the 2-byte return address, PC[15:0], onto the SPL stack.</li> <li>Push a 00h byte onto the SPL stack to indicate an interrupt from Z80 mode (because ADL = 0).</li> <li>Set the ADL mode bit to 1.</li> <li>The interrupt vector address is located at { I[15:1], IVECT[8:0] }.</li> <li>PC[23:0] ← ( { I[15:1], IVECT[8:0] } ).</li> <li>The interrupt service routine must end with RETI.L</li> </ul> |

## Table 13. Vectored Interrupt Operation

ilog | 110

FLASH\_DATA register causes an autoincrement of the Flash address stored in the Flash Address registers (FLASH\_PAGE, FLASH\_ROW, FLASH\_COL). See Table 43.

Table 43. Flash Page Select Register (FLASH\_PAGE = 00FCh)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access | R/W |

**Note:** R/W = Read/Write, R = Read Only.

| Bit<br>Position             | Value | Description                                                                                                                                                                                  |

|-----------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>INFO_EN              | 0     | Flash I/O access to PAGE ERASE operations are directed to main Flash memory. Info page is NOT affected by a MASS ERASE operation.                                                            |

|                             | 1     | Flash I/O access to PAGE ERASE operations are directed to the information page. PAGE ERASE operations only affect the information page. Info page is included during a MASS ERASE operation. |

| [6:0] 00h–7Fh<br>FLASH_PAGE |       | Page address of Flash memory to be used during the PAGE<br>ERASE or I/O access of main Flash memory. When<br>INFO_EN is set to 1, this field is ignored.                                     |

ilog

## 116

## Watchdog Timer Operation

#### **Enabling and Disabling the Watchdog Timer**

The WDT is disabled on a RESET. To enable the WDT, the application program must set WDT\_EN, which is bit 7 of the WDT\_CTL register. After WDT\_EN is set, no Writes are allowed to the WDT\_CTL register. When enabled, the WDT cannot be disabled except by a RESET.

#### **Time-Out Period Selection**

There are four choices of time-out periods for the WDT. The WDT time-out period is defined by the WDT\_PERIOD WDT\_CTL[1:0] field and WDT\_CLK WDT\_CTL[3:2] field of the Watchdog Timer control register (WDT\_CTL = 0093h). The approximate time-out period and corresponding clock cycles for three different WDT clock sources are listed in Table 47.

The WDT time-out period divider is set to one of the four available settings for the selected frequency of the WDT clock source. Basing the divider settings on the clock source values provides a time-out range from few seconds to few msecs, regardless of the frequency setting.

| WDT_CLK[<br>3:2]    | 00                     |                   |                         | 01      |                        | 10                         | 11       |         |

|---------------------|------------------------|-------------------|-------------------------|---------|------------------------|----------------------------|----------|---------|

|                     |                        | lz system<br>lock | 32.768 kHz RTC<br>clock |         | oscilla                | nal RC<br>itor (~10<br>Hz) | Reserved |         |

| WDT_PERI<br>OD[1:0] | Divider                | Timeout           | Divider                 | Timeout | Divider                | Timeout                    | Divider  | Timeout |

| 00                  | <b>2</b> <sup>27</sup> | 2.68 s            | <b>2</b> <sup>17</sup>  | 4.00 s  | 2 <sup>15</sup>        | 3.28 s                     | -        | -       |

| 01                  | 2 <sup>25</sup>        | 0.67 s            | <b>2</b> <sup>14</sup>  | 0.5 s   | <b>2</b> <sup>13</sup> | 0.82 s                     | -        | -       |

| 10                  | <b>2</b> <sup>22</sup> | 83.9 ms           | <b>2</b> <sup>11</sup>  | 62.5 ms | 2 <sup>9</sup>         | 51.2 ms                    | -        | -       |

| 11                  | 2 <sup>18</sup>        | 5.2 ms            | 2 <sup>7</sup>          | 3.9 ms  | 2 <sup>5</sup>         | 3.2 ms                     | -        | -       |

#### Table 47. WDT Approximate Time-Out Delays for Possible Clock Sources

#### **RESET or NMI Generation**

A WDT time-out causes a RESET or sends a NMI signal to the CPU. The default operation is for the WDT to cause a RESET.

If the NMI\_OUT bit in the WDT\_CTL register is set to 0, then on a WDT time-out, the RST\_FLAG bit in the WDT\_CTL register is set to 1. The RST\_FLAG bit is polled by the CPU to determine the source of the RESET event.

ilog <sub>134</sub>

| 2               | 0 | Interrupt requests for ICx are disabled (valid only in INPUT CAPTURE mode).<br>Timer 1: the capture pin is IC1.<br>Timer 3: the capture pin is IC3.                                       |

|-----------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ_ICB_EN      | 1 | Interrupt requests for ICx are enabled (valid only in INPUT CAPTURE mode).<br>For Timer 1: the capture pin is IC1.<br>For Timer 3: the capture pin is IC3.                                |

| 1<br>IRQ_ICA_EN | 0 | Interrupt requests for ICA or PWM power trip are disabled<br>(valid only in INPUT CAPTURE and PWM modes).<br>For Timer 1: the capture pin is IC0.<br>For Timer 3: the capture pin is IC2. |

|                 | 1 | Interrupt requests for ICA or PWM power trip are enabled<br>(valid only in INPUT CAPTURE and PWM modes).<br>For Timer 1: the capture pin is IC0.<br>For Timer 3: the capture pin is IC2.  |

| 0               | 0 | Interrupt on end-of-count is disabled.                                                                                                                                                    |

| IRQ_EOC_EN      | 1 | Interrupt on end-of-count is enabled.                                                                                                                                                     |

ilog

## 154

## Pulse-Width Modulation Control Register 2

The PWM Control Register 2 (see Table 74) controls pulse-width modulation AND/OR and edge delay functions.

## Table 74. PWM Control Register 2 (PWM\_CTL2 = 007Ah)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access | R/W |

Note: R/W = Read/Write.

| Bit      |       |                                |

|----------|-------|--------------------------------|

| Position | Value | Description                    |

|          | 00    | Disable AND/OR features on PWM |

| [7:6]    | 01    | Enable AND logic on PWM        |

| AON_EN   | 10    | Enable OR logic on PWM         |

|          | 11    | Disable AND/OR features on PWM |

|          | 00    | Disable AND/OR features on PWM |

| [5:4]    | 01    | Enable AND logic on PWM        |

| AO_EN    | 10    | Enable OR logic on PWM         |

|          | 11    | Disable AND/OR features on PWM |

ilog <sub>166</sub>

#### **Real-Time Clock Month Register**

This register contains the current month count. The RTC\_MON register begins counting at 01h. The value in the RTC\_MON register is unchanged by a RESET. The current setting of BCD\_EN determines whether the values in this register are binary (BCD\_EN = 0) or binary-coded decimal (BCD\_EN = 1). Access to this register is Read Only if the RTC is locked, and Read/Write if the RTC is unlocked. See Table 85.

#### Table 85. Real-Time Clock Month Register (RTC\_MON = 00E5h)

| Bit        | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------|------|------|------|------|------|------|------|------|

| Reset      | Х    | Х    | Х    | Х    | Х    | Х    | Х    | Х    |

| CPU Access | R/W* |

**Note:** X = Unchanged by RESET; R/W\* = Read Only if RTC locked, Read/Write if RTC unlocked.

#### Binary-Coded Decimal Operation (BCD\_EN = 1)

| Bit Position                                                                                    | Value | Description                                |  |  |  |  |

|-------------------------------------------------------------------------------------------------|-------|--------------------------------------------|--|--|--|--|

| [7:4]<br>TENS_MON                                                                               | 0–1   | The tens digit of the current month count. |  |  |  |  |

| [3:0]<br>MON                                                                                    | 0–9   | The ones digit of the current month count. |  |  |  |  |

| $\operatorname{Rinary}(\operatorname{Operation}(\operatorname{RCD}_{-}\operatorname{EN}_{-}0))$ |       |                                            |  |  |  |  |

#### Binary Operation (BCD\_EN = 0)

| <b>Bit Position</b> | Value   | Description              |

|---------------------|---------|--------------------------|

| [7:0]<br>MON        | 01h–0Ch | The current month count. |

ilog <sub>169</sub>

#### **Real-Time Clock Alarm Seconds Register**

This register contains the alarm seconds value. The value in the RTC\_ASEC register is unchanged by a RESET. The current setting of BCD\_EN determines whether the values in this register are binary (BCD\_EN = 0) or binary-coded decimal (BCD\_EN = 1). See Table 88.

#### Table 88. Real-Time Clock Alarm Seconds Register (RTC\_ASEC = 00E8h)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset      | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| CPU Access | R/W |

**Note:** X = Unchanged by RESET; R/W = Read/Write.

#### Binary-Coded Decimal Operation (BCD\_EN = 1)

| Bit Position      | Value    | Description                                |  |

|-------------------|----------|--------------------------------------------|--|

| [7:4]<br>ATEN_SEC | 0–5      | The tens digit of the alarm seconds value. |  |

| [3:0]<br>ASEC     | 0–9      | The ones digit of the alarm seconds value. |  |

| Binary Operat     | ion (BCD | _EN = 0)                                   |  |

| Bit Position      | Value    | Description                                |  |

| [7:0]             | 00h–3B   | 3h The alarm seconds value.                |  |

ilog

175

## Universal Asynchronous Receiver/Transmitter

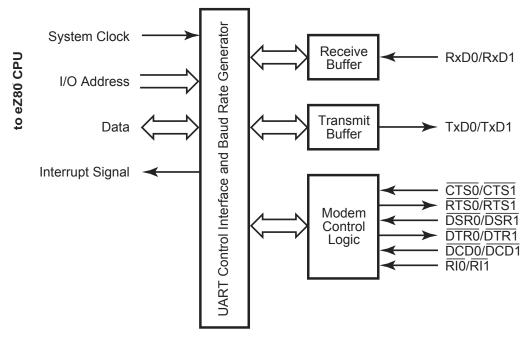

The UART module implements all of the logic required to support the asynchronous communications protocol. The module also implements two separate 16-byte-deep FIFOs for both transmission and reception. A block diagram of the UART is displayed in Figure 36.

Figure 36. UART Block Diagram

The UART module provides the following asynchronous communications protocolrelated features and functions:

- 5-, 6-, 7-, 8- or 9-bit data transmission.

- Even/odd, space/mark, address/data, or no parity bit generation and detection.

- Start and stop bit generation and detection (supports up to two stop bits).

- Line break detection and generation.

- Receiver overrun and framing errors detection.

- Logic and associated I/O to provide modem handshake capability.

ilog <sub>184</sub>

| Bit                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|---|---|---|---|---|---|---|---|

| Reset                 | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access            | W | W | W | W | W | W | W | W |

| Note: W = Write Only. |   |   |   |   |   |   |   |   |

#### Table 96. UART Transmit Holding Registers (UART0\_THR = 00C0h, UART1\_THR = 00D0h)

| Bit<br>Position | Value   | Description         |

|-----------------|---------|---------------------|

| [7:0]<br>TxD    | 00h–FFh | Transmit data byte. |

#### **UART Receive Buffer Register**

The bits in this register reflect the data received. If less than eight bits are programmed for reception, the lower bits of the byte reflect the bits received, whereas upper unused bits are 0. The Receive FIFO is mapped at this address. If the FIFO is disabled, this buffer is only one byte deep.

These registers share the same address space as the UARTx\_THR and UARTx\_BRG\_L registers. See Table 97.

| Bit                               |  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------------------|--|---|---|---|---|---|---|---|---|

| Reset                             |  | Х | Х | Х | Х | Х | Х | Х | Х |

| CPU Access                        |  | R | R | R | R | R | R | R | R |

| Note: R = Read only.              |  |   |   |   |   |   |   |   |   |

| Bit<br>Position Value Description |  |   |   |   |   |   |   |   |   |

|              |         | •                  |

|--------------|---------|--------------------|

| [7:0]<br>RxD | 00h–FFh | Receive data byte. |

#### UART Interrupt Enable Register

The UARTx\_IER register is used to enable and disable the UART interrupts. The UARTx\_IER registers share the same I/O addresses as the UARTx\_BRG\_H registers. See Table 98 on page 185.

ilog <sub>207</sub>

## Table 112. SPI Baud Rate Generator Register—Low Byte (SPI\_BRG\_L = 00B8h)

| Bit                |                         | 7                                                                                                                                        | 6   | 5   | 4   | 3   | 2   | 1   | 0 |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|---|

| Reset              | 0                       | 0                                                                                                                                        | 0   | 0   | 0   | 0   | 1   | 0   |   |

| CPU Access         | R/W                     | R/W                                                                                                                                      | R/W | R/W | R/W | R/W | R/W | R/W |   |

| Note: R/W = Re     | Note: R/W = Read/Write. |                                                                                                                                          |     |     |     |     |     |     |   |

| Bit                |                         |                                                                                                                                          |     |     |     |     |     |     |   |

| Position           | Value                   | Description                                                                                                                              |     |     |     |     |     |     |   |

| [7:0]<br>SPI_BRG_L | 00h–<br>FFh             | These bits represent the Low byte of the 16-bit BRG divider value. The complete BRG divisor value is returned by {SPI_BRG_H, SPI_BRG_L}. |     |     |     |     |     |     |   |

## Table 113. SPI Baud Rate Generator Register—High Byte (SPI\_BRG\_H = 00B9h)

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position    | Value   | Description                                                                                                                               |

|--------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>SPI_BRG_H | 00h–FFh | These bits represent the High byte of the 16-bit BRG divider value. The complete BRG divisor value is returned by {SPI_BRG_H, SPI_BRG_L}. |

ilog <sub>242</sub>

#### Address Information for ZDI Address Match Registers

ZDI\_ADDR0\_L = 00h, ZDI\_ADDR0\_H = 01h, ZDI\_ADDR0\_U = 02h, ZDI\_ADDR1\_L = 04h, ZDI\_ADDR1\_H = 05h, ZDI\_ADDR1\_U = 06h, ZDI\_ADDR2\_L = 08h, ZDI\_ADDR2\_H = 09h, ZDI\_ADDR2\_U = 0Ah, ZDI\_ADDR3\_L = 0Ch, ZDI\_ADDR3\_H = 0Dh, and ZDI\_ADDR3\_U = 0Eh in the ZDI Register Write Only Address Space.

#### **ZDI Break Control Register**

The ZDI Break Control register is used to enable break points. ZDI asserts a break when the CPU instruction address, ADDR[23:0], matches the value in the ZDI Address Match 3 registers, {ZDI\_ADDR3\_U, ZDI\_ADDR3\_H, ZDI\_ADDR3\_L}. BREAKs occurs only on an instruction boundary. If the instruction address is not the beginning of an instruction (that is, for multibyte instructions), then the break occurs at the end of the current instruction. The brk\_next bit is set to 1. The brk\_next bit must be reset to 0 to release the break. See Table 136 on page 243.

ilog <sub>268</sub>

## Power Requirement to the Phase-Locked Loop Function

Regardless of whether or not you chooses to use the PLL module block as a clock source for the eZ80F91 device, the PLL\_V<sub>DD</sub> (pin 87) must be connected to a V<sub>DD</sub> supply and the PLL\_V<sub>SS</sub> (pin 84) must be connected to a V<sub>SS</sub> supply for proper operation of the eZ80F91 using any system clock source.

## **PLL Registers**

#### PLL Divider Control Register—Low and High Bytes

This register is designed such that the 11 bit divider value is loaded into the divider module whenever the PLL\_DIV\_H register is written. Therefore, the procedure must be to load the PLL\_DIV\_L register, followed by the PLL\_DIV\_H register, for the divider to receive the appropriate value.

The divider is designed such that any divider value less than two is ignored; a value of two is used in its place.

The LSB of PLL divider N is set via the corresponding bits in the PLL\_DIV\_L register. See Table 152 and Table 153 on page 269.

**Note:** The PLL divider register are written only when the PLL is disabled. A read-back of the PLL Divider registers returns 0.

| Bit                   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------|---|---|---|---|---|---|---|---|

| Reset                 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| CPU Access            | W | W | W | W | W | W | W | W |

| Note: W = Write only. |   |   |   |   |   |   |   |   |

#### Table 152. PLL Divider Register—Low Bytes (PLL\_DIV\_L = 005Ch)

| Bit<br>Position    | Value   | Description                                                                                                                              |

|--------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>PLL_DIV_L | 00h–FFh | These bits represent the Low byte of the 11 bit PLL divider value. The complete PLL divider value is returned by {PLL_DIV_H, PLL_DIV_L}. |

ilog

290

#### Table 174. Arbiter Priority

| Priority<br>Level | Device<br>Serviced    | Flags                    |

|-------------------|-----------------------|--------------------------|

| 0                 | RxDMA High            | RxFIFO > half full (FAF) |

| 1                 | TxDMA High            | TxFIFO < half full (FAE) |

| 2                 | eZ80 <sup>®</sup> CPU |                          |

| 3                 | RxDMA Low             | RxFIFO < half full (FAE) |

| 4                 | TxDMA Low             | TxFIFO > half full (FAF) |

#### TxDMA

The TxDMA module moves the next packet to be transmitted from EMAC memory into the TxFIFO. Whenever the polling timer expires, the TxDMA reads the High status byte from the Tx descriptor table pointed to by the Transmit Read Pointer, TRP. Polling continues until the High status Read reaches bit 7, when the Emac\_Owns ownership semaphore, bit 15 of the descriptor table (see Table 178 on page 295) is set to 1. The TxDMA then initializes the packet length counter with the size of the packet from descriptor table bytes 3 and 4. The TxDMA moves the data into the TxFIFO until the packet length counter downcounts to zero. The TxDMA then waits for Transmission Complete signal to be asserted to indicate that the packet is sent and that the Transmit status from the EMAC is valid. The TxDMA updates the descriptor table status and resets the ownership semaphore, bit 15. Finally, the Tx\_DONE\_STAT bit of the EMAC Interrupt Status Register is set to 1, the address field, DMA\_Address, is updated from the descriptor table next pointer, NP (see Figure 62 on page 294). The High byte of the status is read to determine if the next packet is ready to be transmitted.

While the TxDMA is filling the TxFIFO, it monitors two signals from the Transmit FIFO State Machine (TxFifoSM) to detect error conditions and to determine if the packet is to be retransmitted (TxDMA\_Retry asserted) or the packet is aborted (TxDMA\_Abort asserted). If the packet is aborted, the TxDMA updates the descriptor status and moves to the next packet. If the packet is to be retried, the DMA\_Address is reset to the start of the packet, the packet length counter is reloaded from the descriptor table, bytes 3 and 4, and the packet is moved into the TxFIFO again. When an abort or retry event occurs, the TxDMA asserts the appropriate signal to reset the TxFIFO Read and Write pointers which clears out any data that is in the FIFO. The TxFifoSM negates the TxDMA\_Abort or TxDMA\_Retry signal(s) or both when the TxFCWP signal is High. This handshaking maintains synchronization between the TxDMA and the TxFifoSM.

#### **RxDMA**

The RxDMA reads the data from the RxFIFO and stores it in the EMAC memory Receive buffer. When the end of the packet is detected, the RxDMA reads the next two bytes from

ilog <sub>310</sub>

**VLAN Packet**— Maximum frame size = VLAN with 4 byte header -4 (VLAN header) + 14 (Ethernet header) + 1500 MAC client data) + 4 (CRC) = 1522 bytes.

Table 194. EMAC Maximum Frame Length Register—Low Byte (EMAC\_MAXF\_L = 0030h

| Bit                            | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                          | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| CPU Access                     | R/W |

| <b>Note:</b> R/W = Read/Write. |     |     |     |     |     |     |     |     |

| Bit<br>Position      | Value   | Description                                                                                                                                                           |

|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>EMAC_MAXF_L | 00h–FFh | These bits represent the Low byte of the 2 byte MAXF value, {EMAC_MAXF_H, EMAC_MAXF_L}. Bit 7 is bit 7 of the 16-bit value. Bit 0 is bit 0 (lsb) of the 16-bit value. |

#### Table 195. EMAC Maximum Frame Length Register—High Byte (EMAC\_MAXF\_H = 0031h)

| Bit        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset      | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 0   |

| CPU Access | R/W |

|            |     |     |     |     |     |     |     |     |

**Note:** R/W = Read/Write.

| Bit<br>Position      | Value       | Description                                                                                              |

|----------------------|-------------|----------------------------------------------------------------------------------------------------------|

| [7:0]<br>EMAC_MAXF_H | 00h–<br>FFh | These bits represent the High byte of the 2 byte MAXF value, {EMAC_MAXF_H, EMAC_MAXF_L}. Bit 7 is bit 15 |

|                      |             | (msb) of the 16-bit value. Bit 0 is bit 8 of the 16-bit value                                            |

| 11 | U | u |     |

|----|---|---|-----|

|    |   |   | 323 |

| Bit                     |         | 7                                                                                                     | 6                                       | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------------------|---------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|-----|-----|-----|--|

| Reset                   |         | 0                                                                                                     | 0 0 0 0 0 0 0 0                         |     |     |     |     |     |     |  |

| CPU Access              |         | R/W                                                                                                   | R/W                                     | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Note: R/W = Read/Write. |         |                                                                                                       |                                         |     |     |     |     |     |     |  |

| Bit                     |         |                                                                                                       |                                         |     |     |     |     |     |     |  |

| Position                | Value   | Descr                                                                                                 | Description                             |     |     |     |     |     |     |  |

| [7:6]                   | 00      | Set EMAC Rx/Tx buffer size to 256 bytes.                                                              |                                         |     |     |     |     |     |     |  |

| BUFSZ                   | 01      | Set EMAC Rx/Tx buffer size to 128 bytes.                                                              |                                         |     |     |     |     |     |     |  |

|                         | 10      | Set EMAC Rx/Tx buffer size to 64 bytes.                                                               |                                         |     |     |     |     |     |     |  |

|                         | 11      | Set El                                                                                                | Set EMAC Rx/Tx buffer size to 32 bytes. |     |     |     |     |     |     |  |

| [5:0]<br>TPCF_LEV       | 00h–3Fh | Transmit Pause Control Frame level. 00h disables the hardware generated transmit pause control frame. |                                         |     |     |     |     |     |     |  |

#### Table 214. EMAC Buffer Size Register (EMAC\_BUFSZ = 004Bh)

#### **EMAC Interrupt Enable Register**

Enabling the Receive Overrun interrupt allows software to detect an overrun condition as soon as it occurs. If this interrupt is not set, then an overrun cannot be detected until the software processes the Receive packet with the overrun and checks the Receive status in the Rx descriptor table. Because the receiver is disabled by an overrun error until the Rx\_OVR bit is cleared in the EMAC\_ISTAT register, this packet is the final packet in the Receive buffer. To re-enable the receiver before all of the Receive packets are processed and the Receive buffer is empty, software enables this interrupt to detect the overrun condition early. As it processes the Receive packets, it re-enables the receiver when the number of free buffers is greater than the number of minimum buffers. See Table 215 on page 324.

ilog

326

| Bit               |       |                                                                       |

|-------------------|-------|-----------------------------------------------------------------------|

| Position          | Value | Description                                                           |

| 1<br>Tx_CF_STAT   | 1     | Transmit Control Frame Interrupt (Transmit Interrupt) occurs.         |

|                   | 0     | Transmit Control Frame Interrupt (Transmit Interrupt) does not occur. |

| 0<br>Tx_DONE_STAT | 1     | Transmit Done interrupt (Transmit Interrupt) occurs.                  |

|                   | 0     | Transmit Done interrupt (Transmit Interrupt) does not occur.          |

## EMAC PHY Read Status Data Register—Low and High Bytes

The PHY MII Management Data Register is where the data Read from the PHY is stored. See Table 217 and Table 218 on page 327.

Table 217. EMAC PHY Read Status Data Register—Low Byte (EMAC\_PRSD\_L = 004Eh)

| Bit                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------|---|---|---|---|---|---|---|---|

| Reset                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access           | R | R | R | R | R | R | R | R |

| Note: R = Read Only. |   |   |   |   |   |   |   |   |

| Bit<br>Position      | Value   | Description                                                                                                                                                                                         |

|----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]<br>EMAC_PRSD_L | 00h–FFh | These bits represent the Low byte of the 2 byte EMAC PHY<br>Read Status Data value, {EMAC_PRSD_H,<br>EMAC_PRSD_L}. Bit 7 is bit 7 of the 16 bit value. Bit 0 is bit<br>0 (lsb) of the 16 bit value. |

ilog <sub>344</sub>

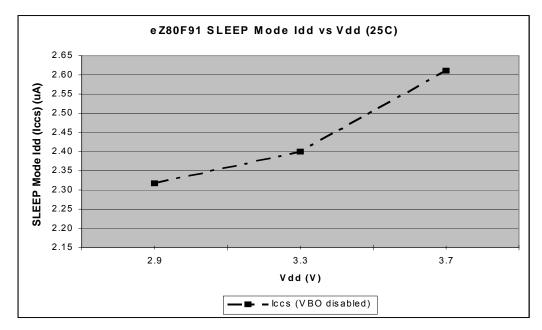

Figure 67 displays the typical current consumption of the eZ80F91 device versus Vdd while operating in SLEEP mode (units in microamps,  $10^{-6}$ A); all peripherals off, and VBO disabled.

Figure 67.  $I_{CC}$  vs. Vdd During SLEEP Mode

## **AC Characteristics**

This section provides information about the AC characteristics and timing of the eZ80F91 device. All AC timing information assumes a standard load of 50 pF on all outputs. See Table 236.

| Table 2 | 236. AC | Characteristics |

|---------|---------|-----------------|

|---------|---------|-----------------|

| Symbol            | Parameter                  | T <sub>A</sub> =<br>0 ⁰C to 70 °C |         | T <sub>A</sub> =<br>−40 °C to 105 °C |         |       |                                                          |

|-------------------|----------------------------|-----------------------------------|---------|--------------------------------------|---------|-------|----------------------------------------------------------|

|                   |                            | Minimum                           | Maximum | Minimum                              | Maximum | Units | Conditions                                               |

| T <sub>XIN</sub>  | System Clock<br>Cycle Time | 20                                | 1000    | 20                                   | 1000    | ns    | V <sub>DD</sub> = 3.0–3.6 V                              |

| T <sub>XINH</sub> | System Clock<br>High Time  | 8                                 |         | 8                                    |         | ns    | V <sub>DD</sub> = 3.0–3.6 V;<br>T <sub>CLK</sub> = 20 ns |

| T <sub>XINL</sub> | System Clock<br>Low Time   | 8                                 |         | 8                                    |         | ns    | V <sub>DD</sub> = 3.0–3.6 V;<br>T <sub>CLK</sub> = 20 ns |