Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ80                                                      |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 50MHz                                                     |

| Connectivity               | Ethernet, I <sup>2</sup> C, IrDA, SPI, UART/USART         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 32                                                        |

| Program Memory Size        | 256KB (256K x 8)                                          |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 16K × 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                 |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 144-LBGA                                                  |

| Supplier Device Package    | 144-BGA (13x13)                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/ez80f91na050sg |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ilog |,

| LQFP<br>Pin No | BGA<br>Pin No | Symbol          | Function                  | Signal Direction      | Description                                                                                                                           |  |  |  |  |

|----------------|---------------|-----------------|---------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 17             | F1            | ADDR12          | Address Bus               | Bidirectional         | Configured as an output in normal                                                                                                     |  |  |  |  |

| 18             | F2            | ADDR13          | Address Bus Bidirectional |                       | operation. The address bus selects a<br>location in memory or I/O space to be                                                         |  |  |  |  |

| 19             | F3            | ADDR14          | Address Bus               | Bidirectional         | read or written. Configured as an input                                                                                               |  |  |  |  |

| 20             | F4            | ADDR15          | Address Bus               | Bidirectional         | during bus acknowledge cyclesDrives the Chip Select/Wait State                                                                        |  |  |  |  |

| 21             | G1            | ADDR16          | Address Bus               | Bidirectional         | Generator block to generate Chip<br>Selects.                                                                                          |  |  |  |  |

| 22             | G2            | V <sub>DD</sub> | Power Supply              |                       | Power Supply.                                                                                                                         |  |  |  |  |

| 23             | G3            | V <sub>SS</sub> | Ground                    |                       | Ground.                                                                                                                               |  |  |  |  |

| 24             | F5            | ADDR17          | Address Bus               | Bidirectional         | Configured as an output in normal                                                                                                     |  |  |  |  |

| 25             | H1            | ADDR18          | Address Bus               | Bidirectional         | operation. The address bus selects a location in memory or I/O space to be                                                            |  |  |  |  |

| 26             | H2            | ADDR19          | Address Bus               | Bidirectional         | read or written. Configured as an input                                                                                               |  |  |  |  |

| 27             | G4            | ADDR20          | Address Bus               | Bidirectional         | during bus acknowledge cyclesDrives the Chip Select/Wait State                                                                        |  |  |  |  |

| 28             | H3            | ADDR21          | Address Bus               | Bidirectional         | Generator block to generate Chip                                                                                                      |  |  |  |  |

| 29             | J1            | ADDR22          | Address Bus               | Bidirectional         | <sup>-</sup> Selects.                                                                                                                 |  |  |  |  |

| 30             | G5            | ADDR23          | Address Bus               | Bidirectional         | -                                                                                                                                     |  |  |  |  |

| 31             | J2            | V <sub>DD</sub> | Power Supply              |                       | Power Supply.                                                                                                                         |  |  |  |  |

| 32             | H4            | V <sub>SS</sub> | Ground                    |                       | Ground.                                                                                                                               |  |  |  |  |

| 33             | J3            | CS0             | Chip Select 0             | Output, Active<br>Low | $\overline{\text{CS0}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS0}}$ memory or I/O address space. |  |  |  |  |

| 34             | K1            | CS1             | Chip Select 1             | Output, Active<br>Low | CS1 Low indicates that an access is occurring in the defined CS1 memory or I/O address space.                                         |  |  |  |  |

| 35             | K2            | CS2             | Chip Select 2             | Output, Active<br>Low | $\overline{\text{CS2}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS2}}$ memory or I/O address space. |  |  |  |  |

| 36             | L1            | CS3             | Chip Select 3             | Output, Active<br>Low | $\overline{\text{CS3}}$ Low indicates that an access is occurring in the defined $\overline{\text{CS3}}$ memory or I/O address space. |  |  |  |  |

| 37             | M1            | V <sub>DD</sub> | Power Supply              |                       | Power Supply.                                                                                                                         |  |  |  |  |

| 38             | M2            | V <sub>SS</sub> | Ground                    |                       | Ground.                                                                                                                               |  |  |  |  |

## Table 2. Pin Identification on the eZ80F91 Device (Continued)

ilog

20

| LQFP<br>Pin No | BGA<br>Pin No | Symbol | Function            | Signal Direction | Description                                                                                                                                                                                                                                           |

|----------------|---------------|--------|---------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 114            | A10           | PA0    | GPIO Port A         | Bidirectional    | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port A pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |               | PWM0   | PWM<br>Output 0     | Output           | This pin is used by Timer 3 for PWM<br>0. This signal is multiplexed with PA0                                                                                                                                                                         |

|                |               | OC0    | Output<br>Compare 0 | Output           | This pin is used by Timer 3 for Output<br>Compare 0. This signal is multiplexed<br>with PA0.                                                                                                                                                          |

| 115            | B10           | PA1    | GPIO Port A         | Bidirectional    | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port A pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |               | PWM1   | PWM<br>Output 1     | Output           | This pin is used by Timer 3 for PWM<br>1. This signal is multiplexed with PA1.                                                                                                                                                                        |

|                |               | OC1    | Output<br>Compare 1 | Output           | This pin is used by Timer 3 for Output<br>Compare 1. This signal is multiplexed<br>with PA1.                                                                                                                                                          |

| 116            | E8            | PA2    | GPIO Port A         | Bidirectional    | This pin is used for GPIO. It is<br>individually programmed as input or<br>output and is also used individually as<br>an interrupt input. Each Port A pin,<br>when programmed as output is<br>selected to be an open-drain or open-<br>source output. |

|                |               | PWM2   | PWM<br>Output 2     | Output           | This pin is used by Timer 3 for PWM 2. This signal is multiplexed with PA2.                                                                                                                                                                           |

|                |               | OC2    | Output<br>Compare 2 | Output           | This pin is used by Timer 3 for Output<br>Compare 2. This signal is multiplexed<br>with PA2.                                                                                                                                                          |

## Table 2. Pin Identification on the eZ80F91 Device (Continued)

ilog

## Reset

The Reset controller within the eZ80F91 device features a consistent reset function for all types of resets that affects the system. A system reset, referred in this document as RESET, returns the eZ80F91 to a defined state. All internal registers affected by a RESET return to their default conditions. RESET configures the GPIO port pins as inputs and clears the CPU's Program Counter to 000000h. Program code execution ceases during RESET.

The events that cause a RESET are:

- Power-on reset (POR).

- Low-Voltage Brownout (VBO).

- External **RESET** pin assertion.

- Watchdog Timer (WDT) time-out when configured to generate a RESET.

- Real-Time Clock alarm with the CPU in low-power SLEEP mode.

- Execution of a Debug RESET command.

During RESET, an internal RESET mode timer holds the system in RESET for 1025 system clock (SCLK) cycles to allow sufficient time for the primary crystal oscillator to stabilize. For internal RESET sources, the RESET mode timer begins incrementing on the next rising edge of SCLK following deactivation of the signal that is initiating the RESET event. For external RESET pin assertion, the RESET mode timer begins on the next rising edge of SCLK following assertion of the RESET pin for three consecutive SCLK cycles.

**Note:** The default clock source for SCLK on RESET is the crystal input  $(X_{IN})$ . See the CLK\_MUX values in the PLL Control Register 0, (see Table 154 on page 269).

### External Reset Input and Indicator

The eZ80F91 RESET pin functions as both open-drain (active Low) RESET mode indicator and active Low RESET input. When a RESET event occurs, the internal circuitry begins driving the RESET pin Low. The RESET pin is held Low by the internal circuitry until the internal RESET mode timer times out. If the external reset signal is released prior to the end of the 1025 count time-out, program execution begins following the RESET mode time-out. If the external reset signal is released after the end of the 1025 count timeout, then program execution begins following release of the RESET input (the RESET pin is High for four consecutive SCLK cycles).

## 116

## Watchdog Timer Operation

### **Enabling and Disabling the Watchdog Timer**

The WDT is disabled on a RESET. To enable the WDT, the application program must set WDT\_EN, which is bit 7 of the WDT\_CTL register. After WDT\_EN is set, no Writes are allowed to the WDT\_CTL register. When enabled, the WDT cannot be disabled except by a RESET.

### **Time-Out Period Selection**

There are four choices of time-out periods for the WDT. The WDT time-out period is defined by the WDT\_PERIOD WDT\_CTL[1:0] field and WDT\_CLK WDT\_CTL[3:2] field of the Watchdog Timer control register (WDT\_CTL = 0093h). The approximate time-out period and corresponding clock cycles for three different WDT clock sources are listed in Table 47.

The WDT time-out period divider is set to one of the four available settings for the selected frequency of the WDT clock source. Basing the divider settings on the clock source values provides a time-out range from few seconds to few msecs, regardless of the frequency setting.

| WDT_CLK[<br>3:2]    | 00                     |                   |                        | 01             |                        | 10                         | 11      |         |  |

|---------------------|------------------------|-------------------|------------------------|----------------|------------------------|----------------------------|---------|---------|--|

|                     |                        | lz system<br>lock |                        | kHz RTC<br>ock | oscilla                | nal RC<br>itor (~10<br>Hz) | Res     | erved   |  |

| WDT_PERI<br>OD[1:0] | Divider                | Timeout           | Divider                | Timeout        | Divider                | Timeout                    | Divider | Timeout |  |

| 00                  | <b>2</b> <sup>27</sup> | 2.68 s            | <b>2</b> <sup>17</sup> | 4.00 s         | 2 <sup>15</sup>        | 3.28 s                     | -       | -       |  |

| 01                  | 2 <sup>25</sup>        | 0.67 s            | <b>2</b> <sup>14</sup> | 0.5 s          | <b>2</b> <sup>13</sup> | 0.82 s                     | -       | -       |  |

| 10                  | <b>2</b> <sup>22</sup> | 83.9 ms           | <b>2</b> <sup>11</sup> | 62.5 ms        | 2 <sup>9</sup>         | 51.2 ms                    | -       | -       |  |

| 11                  | 2 <sup>18</sup>        | 5.2 ms            | 2 <sup>7</sup>         | 3.9 ms         | 2 <sup>5</sup>         | 3.2 ms                     | -       | -       |  |

### Table 47. WDT Approximate Time-Out Delays for Possible Clock Sources

### **RESET or NMI Generation**

A WDT time-out causes a RESET or sends a NMI signal to the CPU. The default operation is for the WDT to cause a RESET.

If the NMI\_OUT bit in the WDT\_CTL register is set to 0, then on a WDT time-out, the RST\_FLAG bit in the WDT\_CTL register is set to 1. The RST\_FLAG bit is polled by the CPU to determine the source of the RESET event.

### **RTC Oscillator Input**

When the timer clock source is the Real-Time Clock (RTC) signal, the timer functions just as it does in EVENT COUNT mode, except that it samples the internal RTC clock rather than the ECx pin.

### **Input Capture**

INPUT CAPTURE mode allows the CPU to determine the timing of specified events on a set of external pins.

A timer intended for use in INPUT CAPTURE mode is setup the same way as in BASIC mode, with one exception. The CPU must also write the TMRx\_CAP\_CTL register to select the edge on which to capture: rising, falling, or both. When one of these events occurs on an input capture pin, the current 16 bit timer value is latched into the capture value register pair (TMRx\_CAP\_A or TMRx\_CAP\_B depending on the IC pin exhibiting the event).

Reading the Low byte of the register pair causes the timer to ignore other capture events on the associated external pin until the High byte is read. This instance prevents a subsequent capture event from overwriting the High byte between the two Reads and generating an invalid capture value. The capture value registers are Read Only.

A capture flag (ICA or ICB) in the TMR $x_{IIR}$  register is set whenever a capture event occurs. Setting the interrupt identification register bit TMR $x_{IER}[IRQ_{ICx}EN]$  enables the capture event to generate a timer interrupt. The port pins must be configured as alternate functions, see GPIO Mode 7—Alternate Functions on page 51.

### **Output Compare**

The output compare function reverses the input capture function. Rather than store a timer value when an external event occurs, OUTPUT COMPARE mode waits until the timer reaches a specified value, then generates an external event. Although the same base timer is used, up to four separate external pins are driven each with its own compare value.

To use OUTPUT COMPARE mode, the CPU must first configure the basic timer parameters. Then it must load up to four 16-bit compare values into the four TMR3\_OCx register pairs. Next, it must load the TMR3\_OC\_CTL2 register to specify the event that occurs on comparison. You can select the following events: SET, CLEAR, and TOGGLE. Finally, the CPU must enable OUTPUT COMPARE mode by asserting TMR3\_OC\_CTL1[OC\_EN].

The initial value for the OCx pins in OUTPUT COMPARE mode is 0 by default. It is possible to initialize this value to 1 or force a value at a later time. Setting the TMR3\_OC\_CTL2[OCx\_MODE] value to 0 forces the OCx pin to the selected state provided by the TMR3\_OC\_CTL1[OCx\_INIT] bits. Regardless of any compare events, the pin stays at the forced value until OCx\_MODE is changed. After release, it retains the forced value until modified by an OUTPUT COMPARE event.

| Parameter                    | Control Register(s)             | Value |

|------------------------------|---------------------------------|-------|

| Timer Reload Value           | {TMR3_RR_H, TMR3_RR_L}          | 000Ch |

| PWM0 rising edge             | {TMR3_PWM0R_H,<br>TMR3_PWM0R_L} | 0008h |

| PWM0 falling edge            | {TMR3_PWM0F_H, TMR3_PWM0F_L}    | 0004h |

| PWM1 rising edge             | {TMR3_PWM1R_H,<br>TMR3_PWM1R_L} | 0006h |

| PWM1 falling edge            | {TMR3_PWM1F_H, TMR3_PWM1F_L}    | 0007h |

| PWM enable                   | TMR3_PWM_CTL1[PAIR_EN]          | 1     |

| PWM0 enable                  | TMR3_PWM_CTL1[PWM0_EN]          | 1     |

| PWM1 enable                  | TMR3_PWM_CTL1[PWM1_EN]          | 1     |

| Multi-PWM enable             | TMR3_PWM_CTL1[MPWM_EN]          | 1     |

| Prescaler Divider = 4        | TMR3_CTL[CLK_DIV]               | 00b   |

| PWM nonoverlapping delay = 0 | TMR3_PWM_CTL2[PWM_DLY]          | 0000b |

### Table 71. Example: Multi-PWM Addressing

### **PWM Master Mode**

In PWM Master mode, the pair of output signals generated from the PWM0 generator (PWM0 and PWM0) are directed to all four sets of PWM output pairs. Setting TMR3\_PWM\_CTL1[MM\_EN] to 1 enables PWM Master mode. Assuming the outputs are all enabled and no AND/OR gating is used, all four PWM output pairs transition simultaneously under the direction of PWM0 and PWM0. In PWM Master mode, the outputs still be gated individually using the AND/OR gating functions described in the next section. Multi-PWM mode and the individual PWM outputs must be enabled along with PWM Master mode. It is possible to enable or disable any combination of the four PWM outputs while running in PWM Master mode.

## **Modification of Edge Transition Values**

Special circuitry is included for the update of the PWM edge transition values. Normal use requires that these values be updated while the PWM generator is running.

**Note:** Under certain circumstances, electric motors driven by the PWM logic encounters rough operation. In other words, cycles are skipped if the PWM waveform edge is not carefully modified.

Without special consideration, if a PWM generator looks for a particular count to make a state transition and if the edge transition value changes to a value that already occurred in

181

UARTx\_LSR register before reading the UARTx\_RBR register to determine that there is no error in the received data.

To control and check modem status, the application sets up the modem by writing to the UARTx\_MCTL register and reading the UARTx\_MSR register before starting the process described above.

**Poll Mode Transfers**—When interrupts are disabled, all data transfers are referred to as poll mode transfers. In poll mode transfers, the application must continually poll the UARTx\_LSR register to transmit or receive data without enabling the interrupts. The same holds true for the UARTx\_MSR register. If the interrupts are not enabled, the data in the UARTx\_IIR register cannot be used to determine the cause of interrupt.

## **Baud Rate Generator**

The Baud Rate Generator consists of a 16-bit downcounter, two registers, and associated decoding logic. The initial value of the Baud Rate Generator is defined by the two BRG Divisor Latch registers, {UARTx\_BRG\_H, UARTx\_BRG\_L}. At the rising edge of each system clock, the BRG decrements until it reaches the value 0001h. On the next system clock rising edge, the BRG reloads the initial value from {UARTx\_BRG\_H, UARTx\_BRG\_L} and outputs a pulse to indicate the end-of-count.

Calculate the UART data rate with the following equation:

UART Data Rate (bits/s) = <u>System Clock Frequency</u> 16 X UART Baud Rate Generator Divisor

Upon RESET, the 16-bit BRG divisor value resets to the smallest allowable value of 0002h. Therefore, the minimum BRG clock divisor ratio is 2. A software Write to either the Low- or High-byte registers for the BRG Divisor Latch causes both the Low and High bytes to load into the BRG counter, and causes the count to restart.

The divisor registers are accessed only if bit 7 of the UART Line Control register (UARTx\_LCTL) is set to 1. After reset, this bit is reset to 0.

### **Recommended Use of the Baud Rate Generator**

The following is the normal sequence of operations that must occur after the eZ80F91 is powered on to configure the BRG:

- 1. Assert and deassert RESET.

- 2. Set UARTx\_LCTL[7] to 1 to enable access of the BRG divisor registers.

- 3. Program the UARTx\_BRG\_L and UARTx\_BRG\_H registers.

- 4. Clear UARTx\_LCTL[7] to 0 to disable access of the BRG divisor registers.

ilog <sub>203</sub>

divide-by-two clock divider. In MASTER mode, the SPI serial clock is one-half the frequency of the clock signal created by the SPI's Baud Rate Generator.

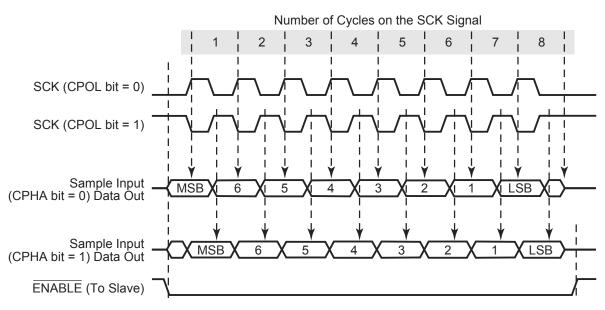

As displayed in Figure 42 and Table 111, four possible timing relations are chosen by using the clock polarity (CPOL) and clock phase CPHA control bits in the SPI Control register. See SPI Control Register on page 208. Both the master and slave must operate with the identical timing, CPOL, and CPHA. The master device always places data on the MOSI line a half-cycle before the clock edge (SCK signal), for the slave device to latch the data.

Figure 42. SPI Timing

### Table 111. SPI Clock Phase and Clock Polarity Operation

| СРНА | CPOL | SCK<br>Transmit<br>Edge | SCK<br>Receive<br>Edge | SCK<br>Idle<br>State | SS High<br>Between<br>Characters? |

|------|------|-------------------------|------------------------|----------------------|-----------------------------------|

| 0    | 0    | Falling                 | Rising                 | Low                  | Yes                               |

| 0    | 1    | Rising                  | Falling                | High                 | Yes                               |

| 1    | 0    | Rising                  | Falling                | Low                  | No                                |

| 1    | 1    | Falling                 | Rising                 | High                 | No                                |

ilog | 2014

## **SPI** Functional Description

When a master transmits to a slave device via the MOSI signal, the slave device responds by sending data to the master via the master's MISO signal. The result is a full-duplex transmission, with both *data out* and *data in* synchronized with the same clock signal. The byte transmitted is replaced by the byte received, eliminating the need for separate transmit-empty and receive-full status bits. A single status bit, SPIF, is used to signify that the I/O operation is complete. See SPI Status Register on page 209.

The SPI is double-buffered during reads, but not during Writes. If a Write is performed during data transfer, the transfer occurs uninterrupted, and the Write is unsuccessful. This condition causes the write collision (WCOL) status bit in the SPI\_SR register to be set. After a data byte is shifted, the SPI flag of the SPI\_SR register is set to 1.

In SPI MASTER mode, the SCK pin functions as an output. It idles High or Low depending on the CPOL bit in the SPI\_CTL register until data is written to the shift register. Data transfer is initiated by writing to the transmit shift register, SPI\_TSR. Eight clocks are then generated to shift the eight bits of transmit data out via the MOSI pin while shifting in eight bits of data via the MISO pin. After transfer, the SCK signal becomes idle.

In SPI SLAVE mode, the start logic receives a logic Low from the  $\overline{SS}$  pin and a clock input at the SCK pin; as a result, the slave is synchronized to the master. Data from the master is received serially from the slave MOSI signal and is loaded into the 8-bit shift register. After the 8-bit shift register is loaded, its data is parallel-transferred to the Read buffer. During a Write cycle, data is written into the shift register. Next, the slave waits for the SPI master to initiate a data transfer, supply a clock signal, and shift the data out on the slave's MISO signal.

If the CPHA bit in the SPI\_CTL register is 0, a transfer begins when the  $\overline{SS}$  pin signal goes Low. The transfer ends when  $\overline{SS}$  goes High after eight clock cycles on SCK. When the CPHA bit is set to 1, a transfer begins the first time SCK becomes active while  $\overline{SS}$  is Low. The transfer ends when the SPI flag is set to 1.

## **SPI Flags**

### **Mode Fault**

The Mode Fault flag (MODF) indicates that there is a multimaster conflict in the system control. The MODF bit is normally cleared to 0 and is only set to 1 when the master device's  $\overline{SS}$  pin is pulled Low. When a mode fault is detected, the following sequence occurs:

- 1. The MODF flag (SPI\_SR[4]) is set to 1.

- 2. The SPI device is disabled by clearing the SPI\_EN bit (SPI\_CTL[5]) to 0.

- 3. The MASTER\_EN bit (SPI\_CTL[4]) is cleared to 0, forcing the device into SLAVE mode.

ilog

209

### **SPI Status Register**

The SPI Status Read Only register returns the status of data transmitted using the serial peripheral interface. Reading the SPI\_SR register clears Bits 7, 6, and 4 to a logical 0. See Table 115.

### Table 115. SPI Status Register (SPI\_SR = 00BBh)

| Bit                 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------------|---|---|---|---|---|---|---|---|

| Reset               | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| CPU Access          | R | R | R | R | R | R | R | R |

| Natas D - Daad Only |   |   |   | • | • | • |   | • |

Note: R = Read Only.

| Bit       |       |                                                                                                                                       |  |  |  |  |  |

|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Position  | Value | Description                                                                                                                           |  |  |  |  |  |

|           | 0     | SPI data transfer is not finished.                                                                                                    |  |  |  |  |  |

| 7<br>SPIF | 1     | SPI data transfer is finished. If enabled, an interrupt is generated. This bit flag is cleared to 0 by a Read of the SPI_SR register. |  |  |  |  |  |

| 6         | 0     | An SPI write collision is not detected.                                                                                               |  |  |  |  |  |

| WCOL      | 1     | An SPI write collision is detected. This bit Flag is cleared to 0 by a Read of the SPI_SR registers.                                  |  |  |  |  |  |

| 5         | 0     | Reserved.                                                                                                                             |  |  |  |  |  |

| 4         | 0     | A mode fault (multimaster conflict) is not detected.                                                                                  |  |  |  |  |  |

| 4<br>MODF | 1     | A mode fault (multimaster conflict) is detected. This bit Flag is cleared to 0 by a Read of the SPI_SR register.                      |  |  |  |  |  |

| [3:0]     | 0000  | Reserved.                                                                                                                             |  |  |  |  |  |

### **SPI Transmit Shift Register**

The SPI Transmit Shift register (SPI\_TSR) is used by the SPI master to transmit data over SPI serial bus to the slave device. A Write to the SPI\_TSR register places data directly into the shift register for transmission. A Write to this register within an SPI device configured as a master initiates transmission of the byte of the data loaded into the register. At the completion of transmitting a byte of data, the SPI Flag (SPI\_SR[7]) is set to 1 in both the master and slave devices.

The SPI Transmit Shift Write Only register shares the same address space as the SPI Receive Buffer Read Only register. See Table 116 on page 210.

ilog

# I<sup>2</sup>C Serial I/O Interface

## I<sup>2</sup>C General Characteristics

The Inter-Integrated Circuit  $(I^2C)$  serial I/O bus is a two-wire communication interface that operates in four modes:

- MASTER TRANSMIT

- MASTER RECEIVE

- SLAVE TRANSMIT

- SLAVE RECEIVE

The I<sup>2</sup>C interface consists of a Serial Clock (SCL) and Serial Data (SDA). Both SCL and SDA are bidirectional lines connected to a positive supply voltage via an external pull-up resistor. When the bus is free, both lines are High. The output stages of devices connected to the bus must be configured as open-drain outputs. Data on the I<sup>2</sup>C bus are transferred at a rate of up to 100 kbps in STANDARD mode, or up to 400 kbps in FAST mode. One clock pulse is generated for each data bit transferred.

### **Clocking Overview**

If another device on the  $I^2C$  bus drives the clock line when the  $I^2C$  is in MASTER mode, the  $I^2C$  synchronizes its clock to the  $I^2C$  bus clock. The High period of the clock is determined by the device that generates the shortest High clock period. The Low period of the clock is determined by the device that generates the longest Low clock period.

The Low period of the clock is stretched by a slave to slow down the bus master. The Low period is also stretched for handshaking purposes. This result is accomplished after each bit transfer or each byte transfer. The I<sup>2</sup>C stretches the clock after each byte transfer until the IFLG bit in the I2C\_CTL register is cleared to 0.

### **Bus Arbitration Overview**

In MASTER mode, the I<sup>2</sup>C checks that each transmitted logic 1 appears on the I<sup>2</sup>C bus as a logic 1. If another device on the bus overrules and pulls the SDA signal Low, arbitration is lost. If arbitration is lost during the transmission of a data byte or a Not Acknowledge (NACK) bit, the I<sup>2</sup>C returns to an idle state. If arbitration is lost during the transmission of an address, the I<sup>2</sup>C switches to SLAVE mode so that it recognizes its own slave address or the general call address.

218

#### Next I<sup>2</sup>C Action I<sup>2</sup>C State Code **Microcontroller Response** Clear IFLG 38h Arbitration lost Return to idle Or set STA, clear IFLG Transmit START when bus free Clear IFLG, clear AAK = $0^2$ 68h Arbitration lost, Receive data byte, transmit NACK SLA+W received, Or clear IFLG, set AAK = 1 Receive data byte, transmit ACK ACK transmitted<sup>1</sup> B0h Arbitration lost, Write byte to DATA, Transmit last byte, SLA+R received. clear IFLG, clear AAK = 0 receive ACK ACK transmitted<sup>3</sup> Or write byte to DATA, Transmit data byte, clear IFLG, set AAK = 1 receive ACK D0h Second address byte Write byte to data, Transmit data byte, + W transmitted. clear IFLG receive ACK ACK received Or set STA, clear IFLG Transmit repeated START Or set STP, clear IFLG Transmit STOP Or set STA & STP, Transmit STOP then clear IFLG START D8h Same as code D0h Same as code D0h Second address byte + W transmitted, ACK not received Notes

## Table 119. I<sup>2</sup>C 10-Bit Master Transmit Status Codes

1. W is defined as the Write bit; that is, the lsb is cleared to 0.

2. AAK is an  $I^2C$  control bit that identifies which ACK signal to transmit.

3. R is defined as the Read bit; that is, the lsb is set to 1.

If a repeated START condition is transmitted, the status code is 10h instead of 08h. After each data byte is transmitted, the IFLG is set to 1 and one of the status codes listed in Table 120 is loaded into the I2C\_SR register.

219

## Table 120. I<sup>2</sup>C Master Transmit Status Codes For Data Bytes

| Code | I <sup>2</sup> C State                     | Microcontroller Response          | Next I <sup>2</sup> C Action       |

|------|--------------------------------------------|-----------------------------------|------------------------------------|

| 28h  | Data byte transmitted, ACK received        | Write byte to data,<br>clear IFLG | Transmit data byte,<br>receive ACK |

|      |                                            | Or set STA, clear IFLG            | Transmit repeated START            |

|      |                                            | Or set STP, clear IFLG            | Transmit STOP                      |

|      |                                            | Or set STA & STP,<br>clear IFLG   | Transmit START then STOP           |

| 30h  | Data byte transmitted,<br>ACK not received | Same as code 28h                  | Same as code 28h                   |

| 38h  | Arbitration lost                           | Clear IFLG                        | Return to idle                     |

|      |                                            | Or set STA, clear IFLG            | Transmit START when bus free       |

When all bytes are transmitted, the microcontroller must write a 1 to the STP bit in the I2C\_CTL register. The I<sup>2</sup>C then transmits a STOP condition, clears the STP bit and returns to an idle state.

### **Master Receive**

In MASTER RECEIVE mode, the I<sup>2</sup>C receives a number of bytes from a slave transmitter.

After the START condition is transmitted, the IFLG bit is 1 and the status code 08h is loaded into the I2C\_SR register. The I2C\_DR register must be loaded with the slave address (or the first part of a 10-bit slave address), with the lsb set to 1 to signify a Read. The IFLG bit must be cleared to 0 as a prompt for the transfer to continue.

When the 7-bit slave address (or the first part of a 10-bit address) and the Read bit are transmitted, the IFLG bit is set and one of the status codes listed in Table 121 on page 220 is loaded into the I2C\_SR register.

ilog

238

a read operation at 0x00 increments the PC to 0x02. To read the next byte, the PC must be decremented by one.

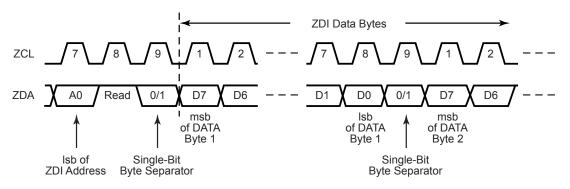

### **ZDI Block Read**

A block Read operation is initiated in the same manner as a single-byte Read; however, the ZDI master continues to clock in the next byte from the ZDI slave as the ZDI slave continues to output data. The ZDI register address counter increments with each Read. If the ZDI register address reaches the end of the Read Only ZDI register address space (20h), the address stops incrementing. Figure 56 displays the ZDI's block Read timing.

Figure 56. ZDI Block Data Read Timing

## **Operation of the eZ80F91 Device during ZDI Break Points**

If the ZDI forces the CPU to break, only the CPU suspends operation. The system clock continues to operate and drive other peripherals. Those peripherals that operate autonomously from the CPU continues to operate, if so enabled. For example, the Watchdog Timer and Programmable Reload Timers continue to count during a ZDI break point.

When using the ZDI interface, any Write or Read operations of peripheral registers in the I/O address space produces the same effect as Read or Write operations using the CPU. As many register Read/Write operations exhibit secondary effects, such as clearing flags or causing operations to commence, the effects of the Read/Write operations during a ZDI break must be taken into consideration.

## **Bus Requests During ZDI Debug Mode**

The ZDI block on the eZ80F91 device allows an external device to take control of the address and data bus while the eZ80F91 device is in DEBUG mode. ZDI\_BUSACK\_EN causes ZDI to allow or prevent acknowledgement of bus requests by external peripherals. The bus acknowledge occurs only at the end of the current ZDI operation (indicated by a High during the single-bit byte separator). The default reset condition is for bus acknowl-

ilog <sub>244</sub>

| Bit<br>Position | Value | Description                                                                                                                                                                                                                                                                                                                                 |

|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>ign_low_1  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If brk_addr1 is set to 1, ZDI initiates<br>a break when the entire 24-bit address, ADDR[23:0],<br>matches the 3-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H, ZDI_ADDR1_L}.                                                                         |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is enabled. If brk_addr1 is set to 1, ZDI initiates<br>a break when only the upper 2 bytes of the 24-bit address,<br>ADDR[23:8], match the 2-byte value {ZDI_ADDR1_U,<br>ZDI_ADDR1_H}. As a result, a break occurs anywhere<br>within a 256-byte page.      |

| 1<br>ign_low_0  | 0     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is disabled. If brk_addr0 is set to 1, ZDI initiates<br>a break when the entire 24-bit address, ADDR[23:0],<br>matches the 3-byte value {ZDI_ADDR0_U,<br>ZDI_ADDR0_H, ZDI_ADDR0_L}.                                                                         |

|                 | 1     | The <i>Ignore the Low Byte</i> function of the ZDI Address Match<br>1 registers is enabled. If the brk_addr1 is set to 0, ZDI<br>initiates a break when only the upper 2 bytes of the 24-bit<br>address, ADDR[23:8], match the 2 bytes value<br>{ZDI_ADDR0_U, ZDI_ADDR0_H}. As a result, a break<br>occurs anywhere within a 256-byte page. |

| 0               | 0     | ZDI single step mode is disabled.                                                                                                                                                                                                                                                                                                           |

| single_step     | 1     | ZDI single step mode is enabled. ZDI asserts a break following execution of each instruction.                                                                                                                                                                                                                                               |

ilog <sub>283</sub>

## Table 170. Opcode Map—Second Opcode After 0EDh

| f Se  | Ipper<br>libble<br>cond<br>code |        | 2<br>BC<br>"BC | Mner         | nonic   |         |        |          |         |       |        |               |       |       |            |          |

|-------|---------------------------------|--------|----------------|--------------|---------|---------|--------|----------|---------|-------|--------|---------------|-------|-------|------------|----------|

| =irst | Operar                          | nd     | S              | econd C      | Operand |         |        |          |         |       |        |               |       |       |            |          |

|       |                                 |        |                |              |         |         | L      | ower Nit | ble (He | x)    |        |               |       |       |            |          |

|       | 0                               | 1      | 2              | 3            | 4       | 5       | 6      | 7        | 8       | 9     | Α      | В             | С     | D     | E          | F        |

| 0     | IN0                             |        | LEA            | LEA          | TST     |         |        | LD BC,   | IN0     | OUT0  |        |               | TST   |       |            |          |

|       | B,(n)                           | (n),B  | BC,<br>IX+d    | BC,<br>IY+d  | A,B     |         |        | (HL)     | C,(n)   | (n),C |        |               | A,C   |       |            | (HI<br>B |

| 1     | IN0                             | OUT0   | LEA            | LEA          | TST     |         |        | LD DE,   | INO     | OUT0  |        |               | TST   |       |            | LD(F     |

|       | D,(n)                           | (n),D  | DE,            | DE,          | A,D     |         |        | (HL)     | E,(n)   | (n),E |        |               | A,E   |       |            | Ď        |

|       |                                 |        | IX+d           | IY+d         |         |         |        |          |         |       |        |               |       |       |            |          |

| 2     | IN0                             |        | LEA HL         |              | TST     |         |        | LD HL,   | IN0     | OUT0  |        |               | TST   |       |            | LI       |

|       | H,(n)                           | (n),H  | ,IX+d          | ,IY+d        | A,H     |         |        | (HL)     | L,(n)   | (n),L |        |               | A,L   |       |            | (HI<br>H |

| 3     |                                 | LD IY, | LEA IX         | LEA IY       | TST     |         |        | LD IX,   | INO     | OUT0  |        |               | TST   |       | LD         |          |

| Ũ     |                                 | (HL)   | ,IX+d          | ,IY+d        | A,(HL)  |         |        | (HL)     | A,(n)   | (n),A |        |               | A,A   |       | (HL),IY    | (HI      |

|       |                                 | ( )    | , .            | , -          | ~ /     |         |        |          |         | ( )/  |        |               | ,     |       | < <i>n</i> | ÌD       |

| 4     | IN                              | OUT    | SBC            | LD           | NEG     | RETN    | IM 0   | LD       | IN      | OUT   | ADC    | LD            | MLT   | RETI  |            | LI       |

|       | B,(BC)                          | (BC),B | HL,BC          |              |         |         |        | I,A      | C,(C)   | (C),C | HL,BC  | BC,           | BC    |       |            | R,       |

| 5     | IN                              | OUT    | SBC            | BC<br>LD     |         | LEA IY, | IM 1   | LD       | IN      | OUT   | ADC    | (Mmn)<br>LD   | MLT   |       | IM 2       | LI       |

| 5     | D,(BC)                          | (BC),D | HL,DE          |              | IY+d    | IX+d    | IIVI I | A,I      | E,(C)   | (C),E | HL,DE  | DE,           | DE    |       | IIVI Z     | A,       |

|       | В,(ВС)                          | (00),0 | TIC, DC        | DE           | 11.0    | IX U    |        | Λ,Ι      | L,(U)   | (0),∟ | 112,02 | (Mmn)         | DL    |       |            | Л,       |

| 6     | IBN                             | OUT    | SBC            | LD           | TST     | PEA     | PEA    | RRD      | IN      | OUT   | ADC    | LD            | MLT   | LD    | LD         | RL       |

|       | H,(C)                           | (BC),H | HL,HL          | (Mmn),<br>HL | A,n     | IX+d    | IY+d   |          | L,(C)   | (C),L | HL,HL  | HL,<br>(Mmn)  | HL    | MB,A  | A,MB       |          |

| 7     |                                 |        | SBC            | LD           | TSTIO   |         | SLP    |          | IN      | OUT   | ADC    | LD            | MLT   | STMIX | RSMIX      |          |

|       |                                 |        | HL,SP          | (Mmn),       | n       |         |        |          | A,(C)   | (C),A | HL,SP  | SP,           | SP    |       |            |          |

| 8     |                                 |        | INIM           | SP<br>OTIM   | INI2    |         |        |          |         |       | INDM   | (Mmn)<br>OTDM | IND2  |       |            |          |

| 0     |                                 |        |                | 011101       | 11 112  |         |        |          |         |       | INDIV  | OTDIVI        | INDZ  |       |            |          |

| 9     |                                 |        | INIMR          | OTIMR        | INI2R   |         |        |          |         |       | INDMR  | OTDMR         | IND2R |       |            |          |

| А     | LDI                             | CPI    | INI            | OUTI         | OUTI2   |         |        |          | LDD     | CPD   | IND    | OUTD          | OUTD2 |       |            |          |

| В     | LDIR                            | CPIR   | INIR           | OTIR         | OTI2R   |         |        |          | LDDR    | CPDR  | INDR   | OTDR          | OTD2R |       |            |          |

| С     |                                 |        | INIRX          | OTIRX        |         |         |        | LD       |         |       | INDRX  | OTDRX         |       |       |            |          |

| 0     |                                 |        |                |              |         |         |        | I,HL     |         |       |        | 5.51          |       |       |            |          |

| D     |                                 |        |                |              |         |         |        | LD       |         |       |        |               |       |       |            |          |

| Е     |                                 |        |                |              |         |         |        | HL,I     |         |       |        |               |       |       |            |          |

| F     |                                 |        |                |              |         |         |        |          |         |       |        |               |       |       |            |          |

ilog

290

### Table 174. Arbiter Priority

| Priority<br>Level | Device<br>Serviced    | Flags                    |

|-------------------|-----------------------|--------------------------|

| 0                 | RxDMA High            | RxFIFO > half full (FAF) |

| 1                 | TxDMA High            | TxFIFO < half full (FAE) |

| 2                 | eZ80 <sup>®</sup> CPU |                          |

| 3                 | RxDMA Low             | RxFIFO < half full (FAE) |

| 4                 | TxDMA Low             | TxFIFO > half full (FAF) |

### TxDMA

The TxDMA module moves the next packet to be transmitted from EMAC memory into the TxFIFO. Whenever the polling timer expires, the TxDMA reads the High status byte from the Tx descriptor table pointed to by the Transmit Read Pointer, TRP. Polling continues until the High status Read reaches bit 7, when the Emac\_Owns ownership semaphore, bit 15 of the descriptor table (see Table 178 on page 295) is set to 1. The TxDMA then initializes the packet length counter with the size of the packet from descriptor table bytes 3 and 4. The TxDMA moves the data into the TxFIFO until the packet length counter downcounts to zero. The TxDMA then waits for Transmission Complete signal to be asserted to indicate that the packet is sent and that the Transmit status from the EMAC is valid. The TxDMA updates the descriptor table status and resets the ownership semaphore, bit 15. Finally, the Tx\_DONE\_STAT bit of the EMAC Interrupt Status Register is set to 1, the address field, DMA\_Address, is updated from the descriptor table next pointer, NP (see Figure 62 on page 294). The High byte of the status is read to determine if the next packet is ready to be transmitted.

While the TxDMA is filling the TxFIFO, it monitors two signals from the Transmit FIFO State Machine (TxFifoSM) to detect error conditions and to determine if the packet is to be retransmitted (TxDMA\_Retry asserted) or the packet is aborted (TxDMA\_Abort asserted). If the packet is aborted, the TxDMA updates the descriptor status and moves to the next packet. If the packet is to be retried, the DMA\_Address is reset to the start of the packet, the packet length counter is reloaded from the descriptor table, bytes 3 and 4, and the packet is moved into the TxFIFO again. When an abort or retry event occurs, the TxDMA asserts the appropriate signal to reset the TxFIFO Read and Write pointers which clears out any data that is in the FIFO. The TxFifoSM negates the TxDMA\_Abort or TxDMA\_Retry signal(s) or both when the TxFCWP signal is High. This handshaking maintains synchronization between the TxDMA and the TxFifoSM.

### **RxDMA**

The RxDMA reads the data from the RxFIFO and stores it in the EMAC memory Receive buffer. When the end of the packet is detected, the RxDMA reads the next two bytes from

ilog <sub>299</sub>

### **EMAC Configuration Register 1**

The EMAC Configuration Register 1 allows control of the padding, autodetection, cyclic redundancy checking (CRC) control, full-duplex, field length checking, maximum packet ignores, and proprietary header options. See Table 181.

Table 181. EMAC Configuration Register 1 (EMAC\_CFG1 = 0021h)

| Bit<br>Reset  |             | 7                                                                                                                                                                                      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|---------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

|               |             | 0                                                                                                                                                                                      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| CPU Access    |             | R/W                                                                                                                                                                                    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| Note: R/W = I | Read/Write. |                                                                                                                                                                                        |     |     |     |     |     |     |     |  |

| Bit           |             |                                                                                                                                                                                        |     |     |     |     |     |     |     |  |

| Position      | Value       | Description                                                                                                                                                                            |     |     |     |     |     |     |     |  |

| 7<br>PADEN    | 0           | No padding. Assume all frames presented to EMAC have proper length.                                                                                                                    |     |     |     |     |     |     |     |  |

|               | 1           | EMAC pads all short frames by adding zeroes to the end of the data field. This bit is used in conjunction with ADPADN and VLPAD.                                                       |     |     |     |     |     |     |     |  |

| 6<br>ADPADN   | 0           | Disable autodetection.                                                                                                                                                                 |     |     |     |     |     |     |     |  |

|               | 1           | Enable frame detection by comparing the two bytes following<br>the source address with 0x8100 (VLAN Protocol ID) and pad<br>accordingly. This bit is ignored if PADEN is cleared to 0. |     |     |     |     |     |     |     |  |

| 5<br>VLPAD    | 0           | Do not pad all short frames.                                                                                                                                                           |     |     |     |     |     |     |     |  |

|               | 1           | EMAC pads all short frames to 64 bytes and append a valid CRC. This bit is ignored if PADEN is cleared to 0.                                                                           |     |     |     |     |     |     |     |  |

| 4<br>CRCEN    | 0           | Do not append CRC.                                                                                                                                                                     |     |     |     |     |     |     |     |  |

|               | 1           | Append CRC to every frame regardless of padding options.                                                                                                                               |     |     |     |     |     |     |     |  |

| 3<br>FULLD    | 0           | HALF-DUPLEX mode. CSMA/CD is enabled.                                                                                                                                                  |     |     |     |     |     |     |     |  |

|               | 1           | Enable FULL-DUPLEX mode. CSMA/CD is disabled.                                                                                                                                          |     |     |     |     |     |     |     |  |

| 2<br>FLCHK    | 0           | Ignore the length field within Transmit/Receive frames.                                                                                                                                |     |     |     |     |     |     |     |  |

|               | 1           | Both Transmit and Receive frame lengths are compared to the length/type field. If the length/type field represents a length then the frame length check is performed.                  |     |     |     |     |     |     |     |  |

| 1<br>HUGEN    | 0           | Limit the Receive frame-size to the number of bytes specified in the MAXF[15:0] field.                                                                                                 |     |     |     |     |     |     |     |  |

|               | 1           | Allow unlimited sized frames to be received. Ignore the MAXF[15:0] field.                                                                                                              |     |     |     |     |     |     |     |  |

ilog

301

### **EMAC Configuration Register 2**

The EMAC Configuration Register 2 controls the behavior of the back pressure and late collision data from the Descriptor table. See Table 183.

### Table 183. EMAC Configuration Register 2 (EMAC\_CFG2 = 0022h)

| Bit                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Reset                   | 0   | 0   | 1   | 1   | 0   | 1   | 1   | 1   |

| CPU Access              | R/W |

| Note: R/W = Read/Write. |     |     |     |     |     |     |     |     |

Bit Position Value Description 7 0 Use normal back-off algorithm prior to transmitting packet. No **BPNB** back pressure applied. 1 After incidentally causing a collision during back pressure, the EMAC immediately (that is, no back-off) retransmits the packet without back-off, which reduces the chance of further collisions and ensures that the Transmit packets are sent. 6 0 Enable exponential back-off. NOBO 1 The EMAC immediately retransmits following a collision rather than use the binary exponential backfill algorithm, as specified in the IEEE 802.3 specification. 00h–3Fh Sets the number of bytes after Start Frame Delimiter (SFD) for [5:0] LCOL which a late collision occurs. By default, all late collisions are aborted.

## ilog <sub>322</sub>

| Bit                 |             | 7      | 6                                                                                                                                                                                                                                     | 5 | 4   | 3   | 2   | 1   | 0   |  |

|---------------------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|-----|-----|--|

| Reset               |             | 0      | 0                                                                                                                                                                                                                                     | 0 | 0   | 0   | 0   | 0   | 0   |  |

| CPU Access          |             | R      | R                                                                                                                                                                                                                                     | R | R/W | R/W | R/W | R/W | R/W |  |

| Note: R = Read C    | Only, R/W = | = Read | Write.                                                                                                                                                                                                                                |   |     |     |     |     |     |  |

| Bit<br>Position     | Value       | Des    | cription                                                                                                                                                                                                                              |   |     |     |     |     |     |  |

| [7:0]<br>EMAC_RRP_H | 00h-FFI     | Rec    | These bits represent the High byte of the 2-byte EMAC<br>Receive Read Pointer value, {EMAC_RRP_H,<br>EMAC_RRP_L}. Bit 7 is bit 15 (msb) of the 16-bit value. Bits<br>7:5 default to 000 on reset; bit 0 is bit 8 of the 16-bit value. |   |     |     |     |     |     |  |

### Table 213. EMAC Receive Read Pointer Register—High Byte (EMAC\_RRP\_H = 004Ah)

### **EMAC Buffer Size Register**

The lower six bits of this register set the level at which the EMAC either transmits a pause control frame or jams the Ethernet bus, depending on the mode selected. When each of these bits contain a zero, this feature is disabled.

In FULL-DUPLEX mode, a Pause Control Frame is transmitted as a One-shot operation. The software must free up a number of Rx buffers so that the number of buffers remaining, EmacBlksLeft, is greater than TCPF\_LEV.

In HALF-DUPLEX mode, the EMAC jams the Ethernet by sending a continuous stream of hexadecimal 5s (5fh). When the software frees up the Rx buffers and the number of buffers remaining, EmacBlksLeft, is greater than TCPF\_LEV, the EMAC stops jamming.