Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                       |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 16MHz                                                                        |

| Connectivity               | CANbus, SCI, UART/USART                                                      |

| Peripherals                | POR, WDT                                                                     |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | Mask ROM                                                                     |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 8x8/10b                                                                  |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-LQFP                                                                      |

| Supplier Device Package    | 48-LQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387pmt-gs-112 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number<br>Parameter                                                                                              | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MB90387<br>MB90387S | MB90V495G |  |  |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|--|--|

| 8/10-bit A/D converter                                                                                                | <ul> <li>Number of channels: 8</li> <li>Resolution: Selectable 10-bit or 8-bit.</li> <li>Conversion time: 6.125 μs (at 16 MHz machine clock, including sampling time)</li> <li>Sequential conversion of two or more successive channels is allowed. (Setting a maximum of 8 channels is allowed.)</li> <li>Single conversion mode: Selected channel is converted only once.</li> <li>Sequential conversion mode: Selected channel is converted repetitively.</li> <li>Halt conversion mode: Conversion of selected channel is stopped and activated alternately.</li> </ul> |                     |           |  |  |

| UART(SCI)                                                                                                             | Number of channels: 1<br>Clock-synchronous transfer: 62.5 kbps to 2 Mbps<br>Clock-asynchronous transfer: 9,615 bps to 500 kbps<br>Communication is allowed by bi-directional serial communication function and master<br>slave type connection.                                                                                                                                                                                                                                                                                                                             |                     |           |  |  |

| CAN<br>B built-in message buffers.<br>Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)<br>CAN wake-up |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                     |           |  |  |

\*1: Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

\*2: MB90387S, MB90F387S

# 2. Packages And Product Models

| Package | MB90F387, MB90F387S | MB90387, MB90387S |

|---------|---------------------|-------------------|

| LQA048  | $\bigcirc$          | $\bigcirc$        |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to Package Dimension for details of the package.

# 3. Product Comparison

## Memory Space

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

- On MB90V495G, an image from FF4000<sup>H</sup> to FFFFFF<sup>H</sup> is viewed on 00 bank and an image of FE0000<sup>H</sup> to FF3FFF<sup>H</sup> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387/387S, an image from FF4000H to FFFFFFH is viewed on 00 bank and an image of FE0000H to FF3FFFH is viewed only on FF bank.

# 7. Handling Devices

## Do Not Exceed Maximum Rating (preventing "latch up")

- On a CMOS IC, latch-up may occur when applying a voltage higher than Vcc or a voltage lower than Vss to input or output pin, which has no middle or high withstand voltage. Latch-up may also occur when a voltage exceeding maximum rating is applied across Vcc pin and Vss pin.

- Latch-up causes drastic increase of power current, which may lead to destruction of elements by heat. Extreme caution must be taken not to exceed maximum rating.

- When turning on and off analog power source, take extra care not to apply an analog power voltages (AVcc and AVR) and analog input voltage that are higher than digital power voltage (Vcc).

## Handling Unused Pins

Leaving unused input pins open may cause permanent destruction by malfunction or latch-up. Apply pull-up or pull-down process to the unused pins using resistors of 2 kΩ or higher. Leave unused input/output pins open under output status, or process as input pins if they are under input status.

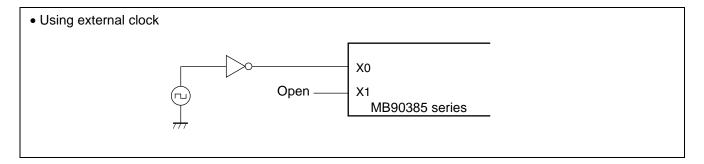

## **Using External Clock**

■ When using an external clock, drive only X0 pin and leave X1 pin open. An example of using an external clock is shown below.

### Notes When Using No Sub Clock

■ If an oscillator is not connected to X0A and X1A pin, apply pull-down resistor to X0A pin and leave X1A pin open.

### About Power Supply Pins

- If two or more Vcc and Vss pins exist, the pins that should be at the same potential are connected to each other inside the device. For reducing unwanted emissions and preventing malfunction of strobe signals caused by increase of ground level, however, be sure to connect the Vcc and Vss pins to the power source and the ground externally.

- Pay attention to connect a power supply to Vcc and Vss of MB90385 series device in a lowest-possible impedance.

- Near pins of MB90385 series device, connecting a bypass capacitor is recommended at 0.1 µF across Vcc pin and Vss pin.

### **Crystal Oscillator Circuit**

- Noises around X0 and X1 pins cause malfunctions on a MB90385 series device. Design a print circuit so that X0 and X1 pins, an crystal oscillator (or a ceramic oscillator), and bypass capacitor to the ground become as close as possible to each other. Furthermore, avoid wires to X0 and X1 pins crossing each other as much as possible.

- Print circuit designing that surrounds X0 and X1 pins with grounding wires, which ensures stable operation, is strongly recommended.

### Caution on Operations during PLL Clock Mode

If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

### Sequence of Turning on Power of A/D Converter and Applying Analog Input

- Be sure to turn on digital power (Vcc) before applying signals to the A/D converter and applying analog input signals (AN0 to AN7 pins).

- Be sure to turn off the power of A/D converter and analog input before turning off the digital power source.

- Be sure not to apply AVR exceeding AVcc when turning on and off. (No problems occur if analog and digital power is turned on and off simultaneously.)

#### Handling Pins When A/D Converter is Not Used

■ If the A/D converter is not used, connect the pins under the following conditions: "AVcc=AVR=Vcc," and "AVss=Vss"

#### Note on Turning on Power

For preventing malfunctions on built-in step-down circuit, maintain a minimum of 50 μs of voltage rising time (between 0.2 V and 2.7V) when turning on the power.

### Stabilization of Supply Voltage

■ A sudden change in the supply voltage may cause the device to malfunction even within the specified Vcc supply voltage operating range. Therefore, the Vcc supply voltage should be stabilized.

For reference, the supply voltage should be controlled so that Vcc ripple variations (peak-to-peak values) at commercial frequencies (50 Hz / 60 Hz) fall below 10% of the standard Vcc supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instantaneous power switching.

| Address                  | Register<br>Abbreviation | Register                                  | Read/<br>Write | Resource                                      | Initial Value         |

|--------------------------|--------------------------|-------------------------------------------|----------------|-----------------------------------------------|-----------------------|

| 000038н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| to<br>00003Fн            |                          |                                           |                |                                               |                       |

| 000040н                  | PPGC0                    | PPG0 operation mode control register      | R/W, W         | 8/16-bit PPG timer 0/                         | 0Х000ХХ1в             |

| 000041н                  | PPGC1                    | PPG1 operation mode control register      | R/W, W         |                                               | 0Х00001в              |

| 000042н                  | PPG01                    | PPG0/1 count clock selection register     | R/W            |                                               | 000000XXB             |

| 000043н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000044н                  | PPGC2                    | PPG2 operation mode control register      | R/W, W         | 8/16-bit PPG timer 2/                         | 0X000XX1в             |

| 000045н                  | PPGC3                    | PPG3 operation mode control register      | R/W, W         | 3                                             | 0Х00001в              |

| 000046н                  | PPG23                    | PPG2/3 count clock selection register     | R/W            | 1 [                                           | 000000XXв             |

| 000047н to<br>00004Fн    |                          | (Reserve                                  | ed area) *     | · ·                                           |                       |

| 000050н                  | IPCP0                    | Input capture data register 0             | R              | 16-bit input/output                           | XXXXXXXXB             |

| 000051н                  |                          |                                           |                | timer                                         | XXXXXXXXB             |

| 000052н                  | IPCP1                    | Input capture data register 1             | R              | 1 [                                           | XXXXXXXXB             |

| 000053н                  |                          |                                           |                |                                               | XXXXXXXXB             |

| 000054н                  | ICS01                    | Input capture control status register     | R/W            | 1 [                                           | 0000000в              |

| 000055н                  | ICS23                    |                                           |                |                                               | 0000000в              |

| 000056н                  | TCDT                     | Timer counter data register               | R/W            | 1 [                                           | 0000000в              |

| 000057н                  |                          |                                           |                |                                               | 0000000в              |

| 000058н                  | TCCS                     | Timer counter control status register     | R/W            | 1 [                                           | 0000000в              |

| 000059н                  |                          | (Reserve                                  | ed area) *     | · ·                                           |                       |

| 00005Ан                  | IPCP2                    | Input capture data register 2             | R              | 16-bit input/output                           | XXXXXXXXB             |

| 00005Вн                  |                          |                                           |                | timer                                         | XXXXXXXXB             |

| 00005Сн                  | IPCP3                    | Input capture data register 3             | R              |                                               | XXXXXXXXB             |

| 00005Dн                  |                          |                                           |                |                                               | XXXXXXXXB             |

| 00005Eнto<br>000065н     |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000066н                  | TMCSR0                   | Timer control status register             | R/W            | 16-bit reload timer 0                         | 0000000в              |

| 000067н                  |                          |                                           | R/W            |                                               | XXXX0000 <sub>B</sub> |

| 000068н                  | TMCSR1                   |                                           | R/W            | 16-bit reload timer 1                         | 0000000в              |

| 000069н                  |                          |                                           | R/W            |                                               | XXXX0000b             |

| 00006Анto<br>00006Ен     |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 00006Fн                  | ROMM                     | ROM mirroring function selection register | W              | ROM mirroring<br>function selection<br>module | XXXXXXX1B             |

| 000070н<br>to<br>00007Fн |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000080н                  | BVALR                    | Message buffer enabling register          | R/W            | CAN controller                                | 0000000в              |

| 000081н                  |                          |                                           | ed area) *     |                                               |                       |

| 000082н                  | TREQR                    | Send request register                     | R/W            | CAN controller                                | 0000000в              |

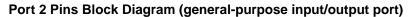

### **Port 2 Registers**

- Port 2 registers include port 2 data register (PDR2) and port 2 direction register (DDR2).

- The bits configuring the register correspond to port 2 pins on a one-to-one basis.

### **Relation between Port 2 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 2    | PDR2,DDR2                               | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P27  | P26  | P25  | P24  | P23  | P22  | P21  | P20  |

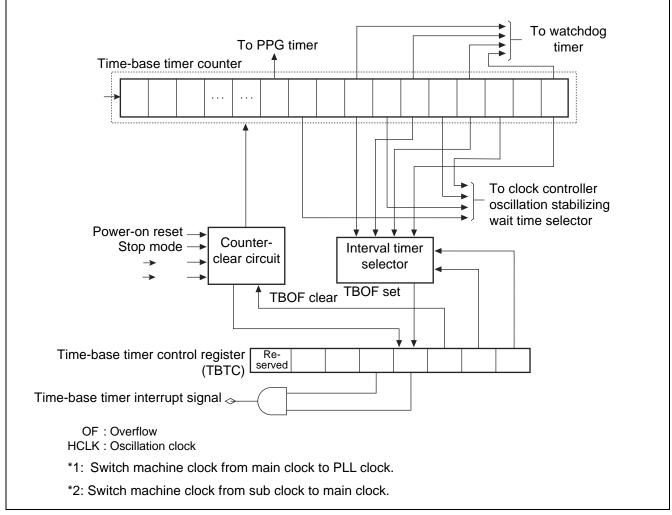

### 12.2 Time-Base Timer

The time-base time is an 18-bit free-run counter (time-base timer counter) that counts up in synchronization with the main clock (dividing main oscillation clock by 2).

- Four choices of interval time are selectable, and generation of interrupt request is allowed for each interval time.

- Provides operation clock signal to oscillation stabilizing wait timer and peripheral functions.

### **Interval Timer Function**

- When the counter of time-base timer reaches an interval time specified by interval time selection bit (TBTC:TBC1, TBC0), an overflow (carrying-over) occurs (TBTC: TBOF=1) and interrupt request is generated.

- If an interrupt by overflow is permitted (TBTC: TBIE=1), an interrupt is generated when overflow occurs (TBTC: TBOF=1).

- The following four interval time settings are selectable:

### Interval Time of Time-base Timer

| Count Clock     | Interval Time                            |

|-----------------|------------------------------------------|

| 2/HCLK (0.5 μs) | 2 <sup>12</sup> /HCLK (Approx. 1.0 ms)   |

|                 | 2 <sup>14</sup> /HCLK (Approx. 4.1 ms)   |

|                 | 216/HCLK (Approx. 16.4 ms)               |

|                 | 2 <sup>19</sup> /HCLK (Approx. 131.1 ms) |

### HCLK: Oscillation clock

Values in parentheses "()" are those under operation of 4-MHz oscillation clock.

### Time-base Timer Block Diagram

Actual interrupt request number of time-base timer is as follows: Interrupt request number: #16 (10<sub>H</sub>)

## 12.7 8/16-bit PPG Timer Outline

The 8/16-bit PPG timer is a 2-channel reload timer module (PPG0 and PPG1) that allows outputting pulses of arbitrary cycle and duty cycle. Combination of the two channels allows selection among the following operations:

- 8-bit PPG output 2-channel independent operation mode

- 16-bit PPG output operation mode

- 8-bit and 8-bit PPG output operation mode

MB90385 series device has two 8/16-bit built-in PPG timers. This section describes functions of PPG0/1. PPG2/3 have the same functions as those of PPG0/1.

### Functions of 8/16-bit PPG Timer

The 8/16-bit PPG timer is composed of four 8-bit reload register (PRLH0/PRLL0, PRLH1/PRLL1) and two PPG down counters (PCNT0, PCNT1).

- Widths of "H" and "L" in output pulse are specifiable independently. Cycle and duty factor of output pulse is specifiable arbitrarily.

- Count clock is selectable among 6 internal clocks.

- The timer is usable as an interval timer, by generating interrupt requests for each interval.

- The time is usable as a D/A converter, with an external circuit.

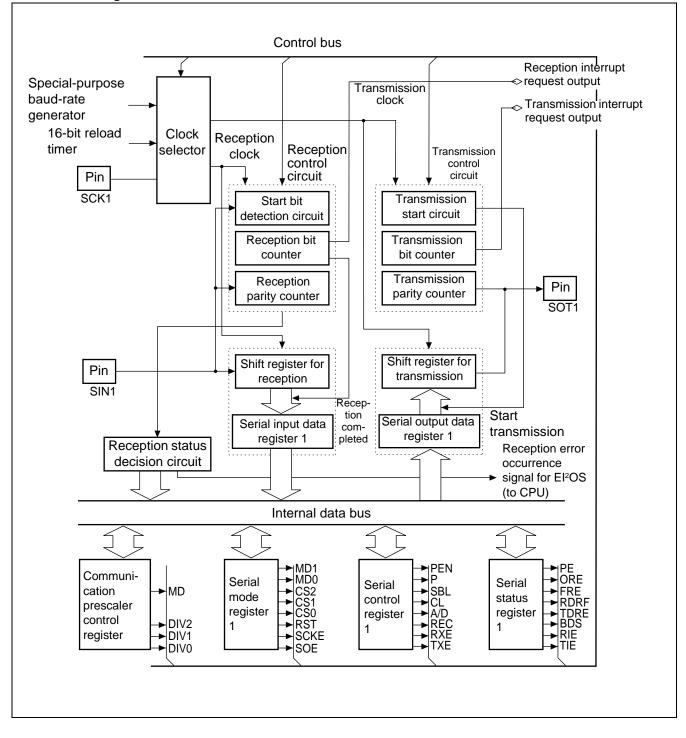

### **UART Block Diagram**

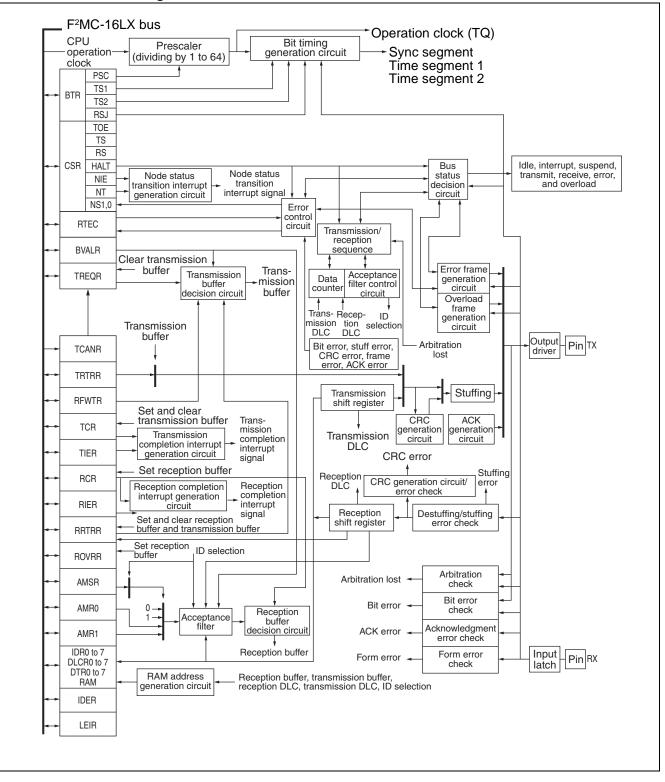

### **CAN Controller Block Diagram**

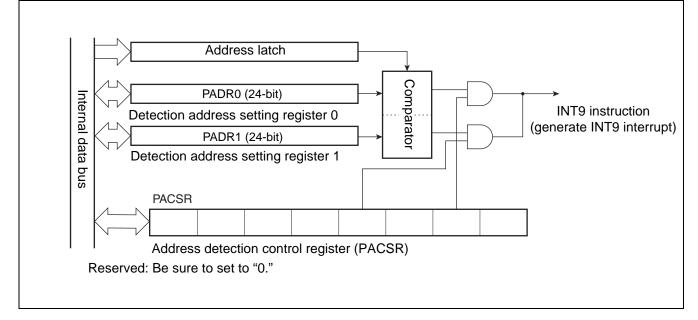

### 12.13 Address Matching Detection Function Outline

The address matching detection function checks if an address of an instruction to be processed next to a currently-processed instruction is identical with an address specified in the detection address register. If the addresses match with each other, an instruction to be processed next in program is forcibly replaced with INT9 instruction, and process branches to the interrupt process program. Using INT9 interrupt, this function is available for correcting program by batch processing.

### Address Matching Detection Function Outline

- An address of an instruction to be processed next to a currently-processed instruction of the program is always retained in an address latch via internal data bus. By the address matching detection function, the address value retained in the address latch is always compared with an address specified in detection address setting register. If the compared address values match with each other, an instruction to be processed next by CPU is forcibly replaced with INT9 instruction, and an interrupt process program is executed.

- Two detection address setting registers are provided (PADR0 and PADR1), and each register is provided with interrupt permission bit. Generation of interrupt, which is caused by address matching between the address retained in address latch and the address specified in address setting register, is permitted and prohibited on a register-by-register basis.

### Address Matching Detection Function Block Diagram

Address latch

Retains address value output to internal data bus.

- Address detection control register (PACSR) Specifies if interrupt is permitted or prohibited when addresses match with each other.

- Detection address setting (PADR0, PADR1) Specifies addresses to be compared with values in address latch.

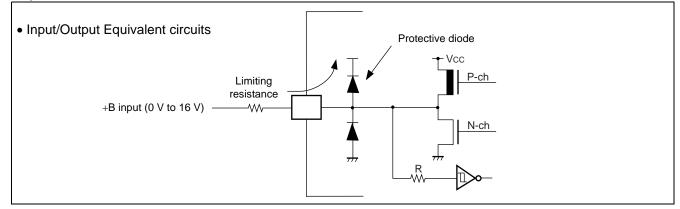

- Use within recommended operating conditions.

- Use at DC voltage (current).

- The +B signal should always be applied a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits:

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

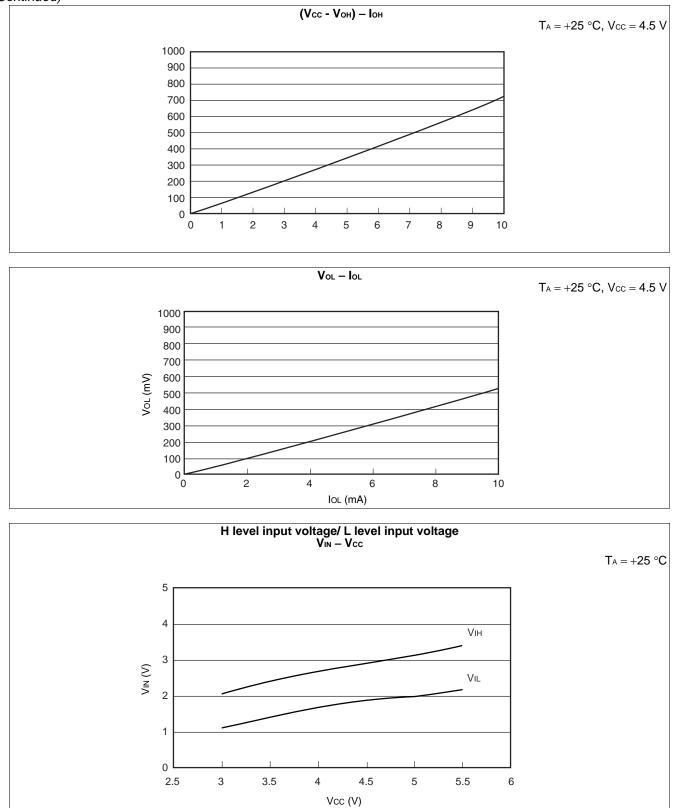

# **13.3 DC Characteristics**

|                             |        |                               | (****                                                                           | - 5.0 V±107 | Value    | 1V35 – 0.0 V | , 14 – | –40 °C to +105 |

|-----------------------------|--------|-------------------------------|---------------------------------------------------------------------------------|-------------|----------|--------------|--------|----------------|

| Parameter                   | Symbol | Pin Name                      | Conditions                                                                      | Min         |          | Мах          | Unit   | Remarks        |

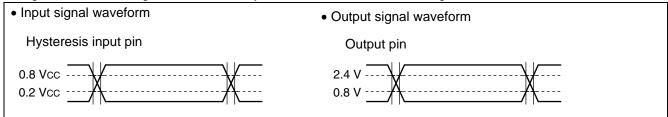

| "H" level<br>input          | Vins   | CMOS hysteresis<br>input pin  | _                                                                               | 0.8 Vcc     | Тур<br>— | Vcc + 0.3    | V      |                |

| voltage                     | Vінм   | MD input pin                  | _                                                                               | Vcc - 0.3   | _        | Vcc + 0.3    | V      |                |

| "L" level<br>input          | Vils   | CMOS hysteresis<br>input pin  | _                                                                               | Vss - 0.3   | _        | 0.2 Vcc      | V      |                |

| voltage                     | Vilm   | MD input pin                  | —                                                                               | Vss - 0.3   | —        | Vss + 0.3    | V      |                |

| "H" level<br>output         | Voh1   | Pins other than<br>P14 to P17 | Vcc = 4.5 V,<br>Іон = -4.0 mA                                                   | Vcc - 0.5   | _        | —            | V      |                |

| voltage                     | Vон2   | P14 to P17                    | Vcc = 4.5 V,<br>Іон = -14.0 mA                                                  | Vcc - 0.5   | _        | —            | V      |                |

| "L" level<br>output         | Vol1   | Pins other than<br>P14 to P17 | $V_{CC} = 4.5 V,$<br>$I_{OL} = 4.0 mA$                                          | —           | _        | 0.4          | V      |                |

| voltage                     | Vol2   | P14 to P17                    | Vcc = 4.5 V,<br>Io∟ = 20.0 mA                                                   | —           | —        | 0.4          | V      |                |

| Input leak<br>current       | lι∟    | All input pins                | Vcc = 5.5 V,<br>Vss < Vi < Vcc                                                  | -5          | _        | +5           | μA     |                |

| Power<br>supply<br>current* | Icc    | Vcc                           | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, normal operation.            | —           | 25       | 30           | mA     |                |

|                             |        |                               | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, writing on<br>Flash memory.  | _           | 45       | 50           | mA     | MB90F387/S     |

|                             |        |                               | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, deleting on<br>Flash memory. | _           | 45       | 50           | mA     | MB90F387/S     |

|                             | lccs   |                               | Vcc = 5.0 V,<br>Internally operating at<br>16 MHz, sleeping.                    | _           | 8        | 12           | mA     |                |

|                             | Icts   |                               | Vcc = 5.0 V,<br>Internally operating at<br>2 MHz, transition from main          | —           | 0.75     | 1.0          | mA     | MB90F387/S     |

|                             |        |                               | clock mode, in time-base timer<br>mode.                                         |             | 0.2      | 0.35         |        | MB90387/S      |

### (Vcc = 5.0 V±10%, Vss = AVss = 0.0 V, T<sub>A</sub> = -40 °C to +105 °C)

| Deremeter                   | Symbol | Pin Name                                      | Conditions                                                                                                  |     | Value |     | Unit | Remarks                                                         |

|-----------------------------|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|-----------------------------------------------------------------|

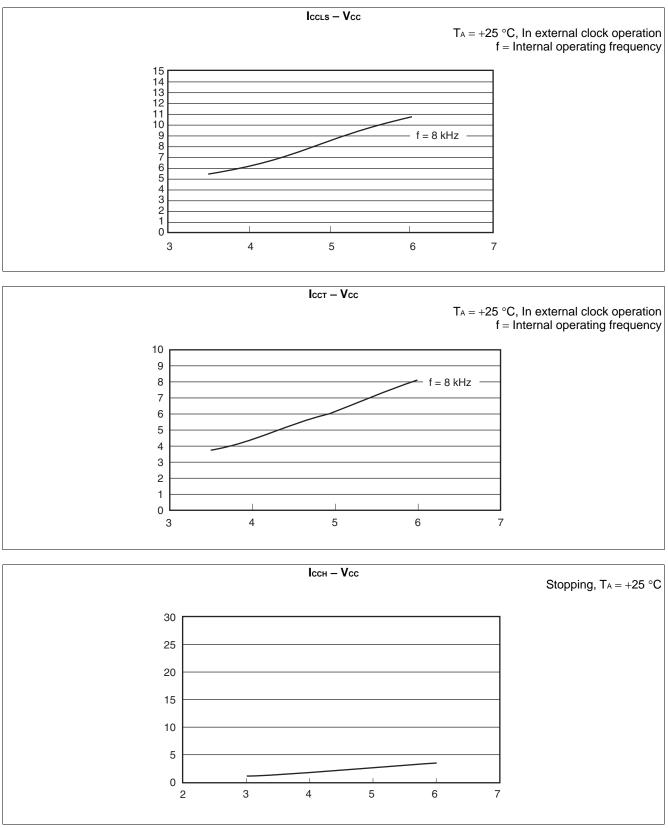

| Parameter                   | Symbol | Pin Name                                      | Conditions                                                                                                  | Min | Тур   | Max | Unit | Remarks                                                         |

| Power<br>supply<br>current* | lcc∟   | Vcc                                           | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>subclock operation,                                       |     | 0.3   | 1.2 | mA   | MB90F387/S                                                      |

|                             |        |                                               | $T_A = +25^{\circ}C$                                                                                        |     | 40    | 100 | μΑ   | MB90387/S                                                       |

|                             | ICCLS  |                                               | $V_{CC} = 5.0 V$ ,<br>Internally operating at 8 kHz,<br>subclock,<br>sleep mode,<br>$T_{A} = + 25^{\circ}C$ | _   | 10    | 30  | μA   |                                                                 |

|                             | Ісст   |                                               | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>watch mode,<br>$T_A = + 25^{\circ}C$                      |     | 8     | 25  | μΑ   |                                                                 |

|                             | Іссн   |                                               | Stopping,<br>T <sub>A</sub> = + 25°C                                                                        | _   | 5     | 20  | μΑ   |                                                                 |

| Input<br>capacity           | CIN    | Other than AVcc,<br>AVss, AVR, C, Vcc,<br>Vss | -                                                                                                           | _   | 5     | 15  | pF   |                                                                 |

| Pull-up<br>resistor         | Rup    | RST                                           | -                                                                                                           | 25  | 50    | 100 | kΩ   |                                                                 |

| Pull-down<br>resistor       | Rdown  | MD2                                           | -                                                                                                           | 25  | 50    | 100 | kΩ   | Flash product is<br>not provided<br>with pull-down<br>resistor. |

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 \circ C to +105 \circ C)$

\*: Test conditions of power supply current are based on a device using external clock.

Rating values of alternating current is defined by the measurement reference voltage values shown below:

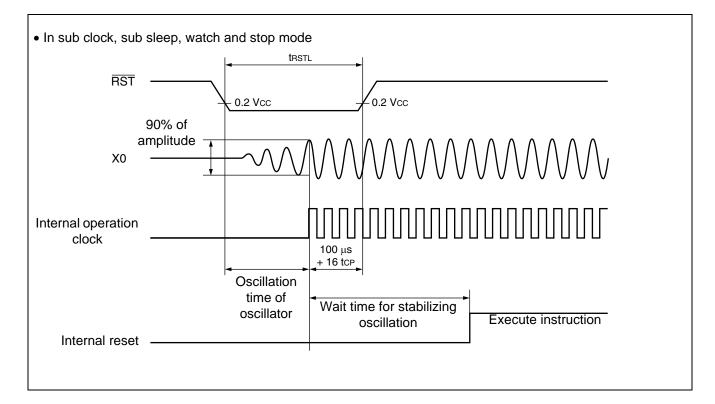

### 13.4.2 Reset Input Timing

| Parameter        | Symbol        | Pin Name Value |                                                                                |     | Unit | Remarks                                                                                        |

|------------------|---------------|----------------|--------------------------------------------------------------------------------|-----|------|------------------------------------------------------------------------------------------------|

| Falameter        | Symbol        |                | Min                                                                            | Мах | Onit | Reillarks                                                                                      |

| Reset input time | <b>t</b> RSTL | RST            | 16 tce*3                                                                       | -   | ns   | Normal operation                                                                               |

|                  |               |                | Oscillation time of oscillator <sup>*1</sup> + $100 \ \mu s$ + $16 \ tcP^{*3}$ | -   |      | In sub clock <sup>*2</sup> , sub<br>sleep <sup>*2</sup> , watch <sup>*2</sup> and<br>stop mode |

|                  |               |                | 100                                                                            | _   | μS   | In timebase timer                                                                              |

\*1: Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

\*2: Except for MB90F387S and MB90387S.

\*3: Refer to "(1) Clock timing" ratings for tcp (internal operation clock cycle time).

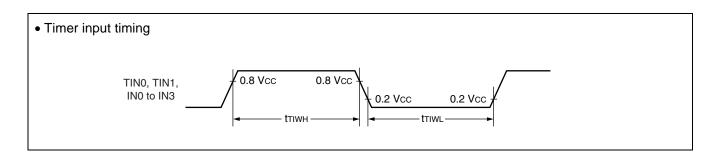

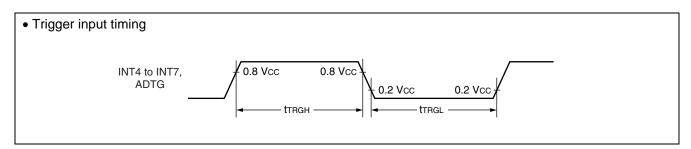

### 13.4.6 Trigger Input Timing

(Vcc = 4.5 V to 5.5 V, Vss = 0.0 V,  $T_A = -40 \text{ °C to } +105 \text{ °C}$ )

| Parameter         | Symbol Pin Name |                       | Pin Name Conditions |         | ue  | Unit | Remarks |

|-------------------|-----------------|-----------------------|---------------------|---------|-----|------|---------|

| Farameter         | Symbol          | FIII Name             | Conditions          | Min     | Max | Onit | Remains |

| Input pulse width | ttrgh<br>ttrgl  | INT4 to INT7,<br>ADTG | _                   | 5 tcp * | _   | ns   |         |

\*: Refer to Clock Timing ratings for tcp (internal operation clock cycle time).

### (Continued)

(Continued)

### (Continued)

# 17. Major Changes

Spansion Publication Number: DS07-13717-5E

| Page | Section                                                                                              | Change Results                                                                                                                        |

|------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 4    | ■ PRODUCT LINEUP                                                                                     | Changed the number of channel of 8/16 bit PPG timer. or one 16-bit channel $\rightarrow$ or two 16-bit channels                       |

| 13   | ■ BLOCK DIAGRAM                                                                                      | Changed the direction of arrow of TIN0, TIN1 signals of 16-bit reload timer.<br>right arrow (output) $\rightarrow$ left arrow (input) |

| 67   | <ul> <li>ELECTRIC CHARACTERISTICS</li> <li>4. AC Characteristics</li> <li>(4) UART timing</li> </ul> | Changed the value of Serial clock.<br>Serial clock "H" pulse width: 4tcp→2tcp<br>Serial clock "L" pulse width: 4tcp→2tcp              |

NOTE: Please see "Document History" about later revised information.