Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 014110                   |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | F <sup>2</sup> MC-16LX                                                         |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16MHz                                                                          |

| Connectivity               | CANbus, SCI, UART/USART                                                        |

| Peripherals                | POR, WDT                                                                       |

| Number of I/O              | 34                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | Mask ROM                                                                       |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x8/10b                                                                    |

| Oscillator Type            | External                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 48-LQFP                                                                        |

| Supplier Device Package    | 48-LQFP (7x7)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387pmt-gs-185e1 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

Module for activation of expanded intelligent I/O service (EI<sup>2</sup>OS), and generation of external interrupt.

#### **Delay Interrupt Generator Module**

Generates interrupt request for task switching.

#### 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 μs (at 16 MHz machine clock, including sampling time)

#### **Program Patch Function**

■ Address matching detection for 2 address pointers.

## MB90387/387S/F387/F387S MB90V495G

## Contents

| Product Lineup                                              | . 4 |

|-------------------------------------------------------------|-----|

| Packages And Product Models                                 | 5   |

| Product Comparison                                          | . 5 |

| Pin Assignment                                              | 6   |

| Pin Description                                             | . 7 |

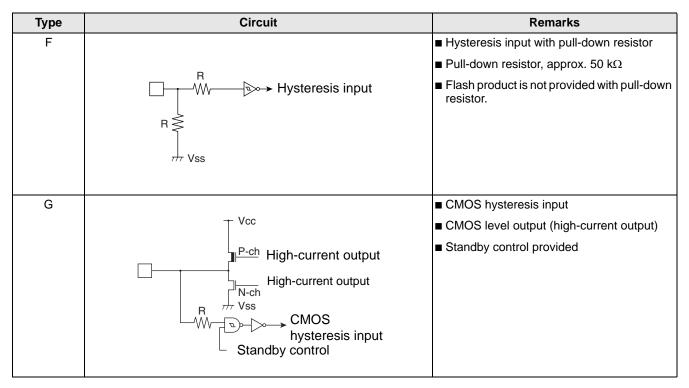

| I/O Circuit Type                                            | . 9 |

| Handling Devices                                            | 10  |

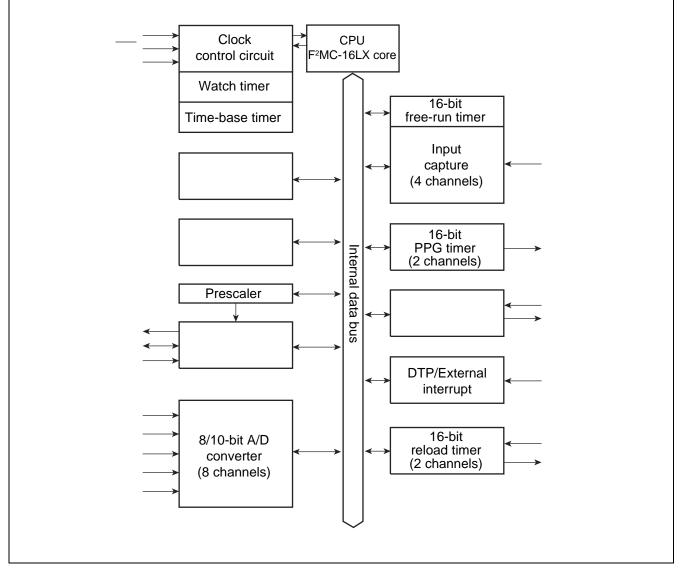

| Block Diagram                                               | 12  |

| Memory Map<br>Memory Allocation of MB90385<br>Memory Map    | 12  |

| I/О Мар                                                     | 14  |

| Interrupt Sources, Interrupt Vectors, And Interrupt Control |     |

| Registers                                                   | 21  |

| Peripheral Resources                                        | 22  |

| I/O Ports                                                   | 22  |

| Time-Base Timer                                             | 28  |

| Watchdog Timer                                              | 30  |

| 16-bit Input/Output Timer                                   |     |

| 16-bit Reload Timer                                         |     |

| Watch Timer Outline                                         |     |

| 8/16-bit PPG Timer Outline                                  | 39  |

| Address Matching Detection Function Outline | 43<br>45<br>47<br>49<br>51<br>52       |

|---------------------------------------------|----------------------------------------|

| 512 Kbit Flash Memory Outline               |                                        |

| Electrical Characteristics                  | 55<br>57<br>58<br>60<br>67<br>68<br>70 |

| Example Characteristics 7                   | 71                                     |

| Ordering Information 7                      | 77                                     |

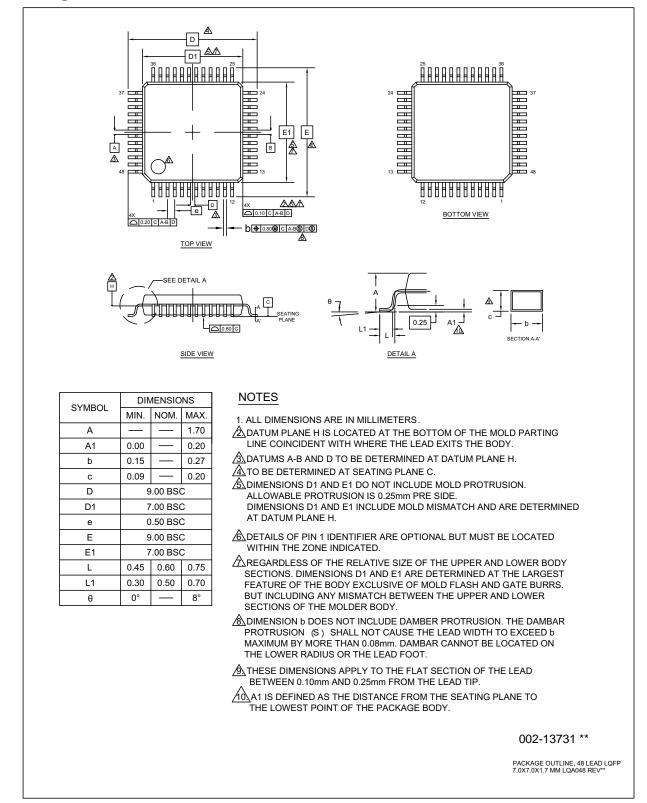

| Package Dimension                           | 78                                     |

| Major Changes 7                             | 79                                     |

| Document History                            |                                        |

| Sales, Solutions, and Legal Information 8   | 81                                     |

| Part Number<br>Parameter | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MB90387<br>MB90387S | MB90V495G |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|

| 8/10-bit A/D converter   | Number of channels: 8<br>Resolution: Selectable 10-bit or 8-bit.<br>Conversion time: 6.125 µs (at 16 MHz machine clock, including sampling time)<br>Sequential conversion of two or more successive channels is allowed. (Setting a<br>maximum of 8 channels is allowed.)<br>Single conversion mode: Selected channel is converted only once.<br>Sequential conversion mode: Selected channel is converted repetitively.<br>Halt conversion mode: Conversion of selected channel is stopped and activated alter-<br>nately. |                     |           |

| UART(SCI)                | Number of channels: 1<br>Clock-synchronous transfer: 62.5 kbps to 2 Mbps<br>Clock-asynchronous transfer: 9,615 bps to 500 kbps<br>Communication is allowed by bi-directional serial communication function and master/<br>slave type connection.                                                                                                                                                                                                                                                                            |                     |           |

| CAN                      | Compliant with Ver 2.0A and Ver 2.0B CAN specifications.<br>8 built-in message buffers.<br>Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)<br>CAN wake-up                                                                                                                                                                                                                                                                                                                                                  |                     | clock)    |

\*1: Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

\*2: MB90387S, MB90F387S

## 2. Packages And Product Models

| Package | MB90F387, MB90F387S | MB90387, MB90387S |

|---------|---------------------|-------------------|

| LQA048  | $\bigcirc$          | $\bigcirc$        |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to Package Dimension for details of the package.

### 3. Product Comparison

#### Memory Space

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

- On MB90V495G, an image from FF4000<sup>H</sup> to FFFFFF<sup>H</sup> is viewed on 00 bank and an image of FE0000<sup>H</sup> to FF3FFF<sup>H</sup> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387/387S, an image from FF4000H to FFFFFFH is viewed on 00 bank and an image of FE0000H to FF3FFFH is viewed only on FF bank.

## 7. Handling Devices

#### Do Not Exceed Maximum Rating (preventing "latch up")

- On a CMOS IC, latch-up may occur when applying a voltage higher than Vcc or a voltage lower than Vss to input or output pin, which has no middle or high withstand voltage. Latch-up may also occur when a voltage exceeding maximum rating is applied across Vcc pin and Vss pin.

- Latch-up causes drastic increase of power current, which may lead to destruction of elements by heat. Extreme caution must be taken not to exceed maximum rating.

- When turning on and off analog power source, take extra care not to apply an analog power voltages (AVcc and AVR) and analog input voltage that are higher than digital power voltage (Vcc).

#### Handling Unused Pins

Leaving unused input pins open may cause permanent destruction by malfunction or latch-up. Apply pull-up or pull-down process to the unused pins using resistors of 2 kΩ or higher. Leave unused input/output pins open under output status, or process as input pins if they are under input status.

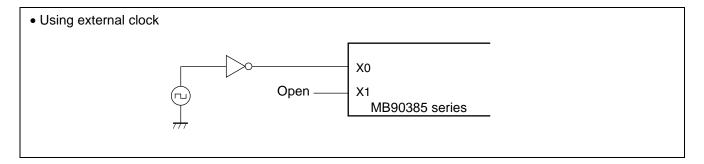

#### **Using External Clock**

■ When using an external clock, drive only X0 pin and leave X1 pin open. An example of using an external clock is shown below.

## 8. Block Diagram

### 9. Memory Map

MB90385 series allows specifying a memory access mode "single chip mode."

#### 9.1 Memory Allocation of MB90385

MB90385 series model has 24-bit wide internal address bus and up to 24-bit bus of external address bus. A maximum of 16-Mbyte memory space of external access memory is accessible.

| Address                  | Register<br>Abbreviation | Register               | Read/<br>Write    | Resource           | Initial Value                 |

|--------------------------|--------------------------|------------------------|-------------------|--------------------|-------------------------------|

| 003910н                  | PRLL0                    | PPG0 reload register L | R/W               | 8/16-bit PPG timer | XXXXXXXXB                     |

| <b>003911</b> н          | PRLH0                    | PPG0 reload register H | R/W               |                    | XXXXXXXXB                     |

| 003912н                  | PRLL1                    | PPG1 reload register L | R/W               |                    | XXXXXXXXB                     |

| 003913н                  | PRLH1                    | PPG1 reload register H | R/W               |                    | XXXXXXXXB                     |

| 003914н                  | PRLL2                    | PPG2 reload register L | R/W               |                    | XXXXXXXXB                     |

| <b>003915</b> н          | PRLH2                    | PPG2 reload register H | R/W               |                    | XXXXXXXXB                     |

| <b>003916</b> н          | PRLL3                    | PPG3 reload register L | R/W               |                    | XXXXXXXX <sub>B</sub>         |

| <b>003917</b> н          | PRLH3                    | PPG3 reload register H | R/W               |                    | XXXXXXXXB                     |

| 003918н<br>to<br>00392Fн |                          |                        | (Reserved area) * |                    |                               |

| 003930н<br>to<br>003BFFн |                          |                        | (Reserved area) * |                    |                               |

| 003C00н<br>to<br>003C0Fн |                          | RAM (                  | General-purpose R | AM)                |                               |

| 003C10н<br>to<br>003C13н | IDR0                     | ID register 0          | R/W               | CAN controller     | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C14н<br>to<br>003C17н | IDR1                     | ID register 1          | R/W               | -                  | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C18н<br>to<br>003C1Bн | IDR2                     | ID register 2          | R/W               | _                  | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C1Cн<br>to<br>003C1Fн | IDR3                     | ID register 3          | R/W               | -                  | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C20н<br>to<br>003C23н | IDR4                     | ID register 4          | R/W               | _                  | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C24н<br>to<br>003C27н | IDR5                     | ID register 5          | R/W               | _                  | XXXXXXXXAB<br>to<br>XXXXXXXXB |

| 003C28н<br>to<br>003C2Bн | IDR6                     | ID register 6          | R/W               | -                  | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C2Cн<br>to<br>003C2Fн | IDR7                     | ID register 7          | R/W               |                    | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C30н,<br>003C31н      | DLCR0                    | DLC register 0         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXB        |

| 003C32н,<br>003C33н      | DLCR1                    | DLC register 1         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXB        |

| 003C34н,<br>003C35н      | DLCR2                    | DLC register 2         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXXB       |

| 003C36н,<br>003C37н      | DLCR3                    | DLC register 3         | R/W               |                    | XXXXXXXXB,<br>XXXXXXXXB       |

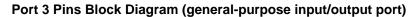

#### **Port 3 Registers**

- Port 3 registers include port 3 data register (PDR3) and port 3 direction register (DDR3).

- The bits configuring the register correspond to port 3 pins on a one-to-one basis.

#### **Relation between Port 3 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 3    | PDR3, DDR3                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P37  | P36* | P35* | _    | P33  | P32  | P31  | P30  |

\*: P35 and P36 do not exist on MB90387and MB90F387.

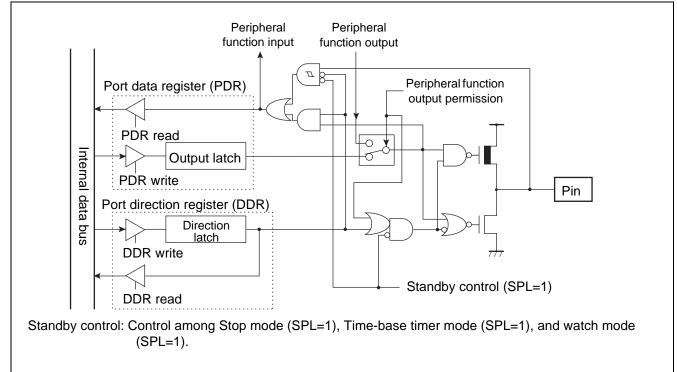

#### 12.4 16-bit Input/Output Timer

The 16-bit input/output timer is a compound module composed of 16-bit free-run timer, (1 unit) and input capture (2 units, 4 input pins). The timer, using the 16-bit free-run timer as a basis, enables measurement of clock cycle of an input signal and its pulse width.

#### Configuration of 16-bit Input/Output Timer

The 16-bit input/output timer is composed of the following modules:

- 16-bit free-run timer (1 unit)

- Input capture (2 units, 2 input pins per unit)

#### Functions of 16-bit Input/Output Timer

#### Functions of 16-bit Free-run Timer

The 16-bit free-run timer is composed of 16-bit up counter, timer counter control status register, and prescaler. The 16-bit up counter increments in synchronization with dividing ratio of machine clock.

- Count clock is set among four types of machine clock dividing rates.

- Generation of interrupt is allowed by counter value overflow.

- Activation of expanded intelligent I/O service (EI<sup>2</sup>OS) is allowed by interrupt generation.

- Counter value of 16-bit free-run timer is cleared to "0000<sup>H</sup>" by either resetting or software-clearing with timer count clear bit (TCCS: CLR).

- Counter value of 16-bit free-run timer is output to input capture, which is available as base time for capture operation.

#### Functions of Input Capture

The input capture, upon detecting an edge of a signal input to the input pin from external device, stores a counter value of 16-bit freerun timer at the time of detection into the input capture data register. The function includes the input capture data registers corresponding to four input pins, input capture control status register, and edge detection circuit.

- Rising edge, falling edge, and both edges are selectable for detection.

- Generating interrupt on CPU is allowed by detecting an edge of input signal.

- Expanded intelligent I/O service (EI<sup>2</sup>OS) is activated by interrupt generation.

- The four input capture input pins and input capture data registers allows monitoring of a maximum of four events.

#### 16-bit Input/Output Timer Block Diagram

#### 12.5 16-bit Reload Timer

The 16-bit reload timer has the following functions:

- Count clock is selectable among 3 internal clocks and external event clock.

- Activation trigger is selectable between software trigger and external trigger.

- Generation of CPU interrupt is allowed upon occurrence of underflow on 16-bit timer register. Available as an interval timer using the interrupt function.

- When underflow of 16-bit timer register (TMR) occurs, one of two reload modes is selectable between one-shot mode that halts counting operation of TMR, and reload mode that reloads 16-bit reload register value to TMR, continuing TMR counting operation.

- The 16-bit reload timer is ready for expanded intelligent I/O service (El<sup>2</sup>OS).

- MB90385 series device has 2 channels of built-in 16-bit reload timer.

#### **Operation Mode of 16-bit Reload Timer**

| Count Clock         | Activation Trigger                 | Operation upon Underflow   |

|---------------------|------------------------------------|----------------------------|

| Internal clock mode | Software trigger, external trigger | One-shot mode, reload mode |

| Event count mode    | Software trigger                   | One-shot mode, reload mode |

#### Internal Clock Mode

- The 16-bit reload timer is set to internal clock mode, by setting count clock selection bit (TMCSR: CSL1, CSL0) to "00<sub>B</sub>", "01<sub>B</sub>", "10<sub>B</sub>".

- In the internal clock mode, the counter decrements in synchronization with the internal clock.

- Three types of count clock cycles are selectable by count clock selection bit (TMCSR: CSL1, CSL0) in timer control status register.

- Edge detection of software trigger or external trigger is specified as an activation trigger.

#### 12.6 Watch Timer Outline

The watch timer is a 15-bit free-run counter that increments in synchronization with sub clock.

- Interval time is selectable among 7 choices, and generation of interrupt request is allowed for each interval.

- Provides operation clock to the subclock oscillation stabilizing wait timer and watchdog timer.

- Always uses subclock as a count clock regardless of settings of clock selection register (CKSCR).

#### **Interval Timer Function**

- In the watch timer, a bit corresponding to the interval time overflows (carry-over) when an interval time, which is specified by interval time selection bit, is reached. Then overflow flag bit is set (WTC: WTOF=1).

- If an interrupt by overflow is permitted (WTC: WTIE=1), an interrupt request is generated upon setting an overflow flag bit.

- Interval time of watch timer is selectable among the following seven choices:

#### Interval Time of Watch Timer

| Sub Clock Cycle | Interval Time                   |

|-----------------|---------------------------------|

| 1/SCLK (122 μs) | 2 <sup>8</sup> /SCLK (31.25 ms) |

|                 | 2º/SCLK (62.5 ms)               |

|                 | 2 <sup>10</sup> /SCLK (125 ms)  |

|                 | 2 <sup>11</sup> /SCLK (250 ms)  |

|                 | 2 <sup>12</sup> /SCLK (500 ms)  |

|                 | 2 <sup>13</sup> /SCLK (1.0 s)   |

|                 | 2 <sup>14</sup> /SCLK (2.0 s)   |

#### SCLK: Sub clock frequency

Values in parentheses "()" are calculation when operating with 8.192 kHz clock.

## MB90387/387S/F387/F387S MB90V495G

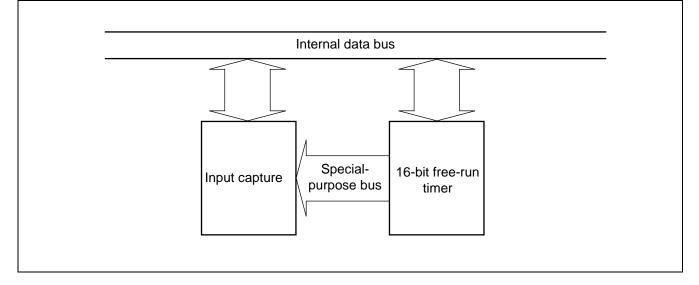

8/16-bit PPG Timer 1 Block Diagram

#### 12.9 DTP/External Interrupt and CAN Wakeup Outline

DTP/external interrupt transfers an interrupt request generated by an external peripheral device or a data transmission request to CPU, generating external interrupt request and activating expanded intelligent I/O service. Input RX of CAN controller is used as external interrupt input.

#### **DTP/External Interrupt and CAN Wakeup Function**

An interrupt request input from external peripheral device to external input pins (INT7 to INT4) and RX pin, just as interrupt request of peripheral device, generates an interrupt request. The interrupt request generates an external interrupt and activates expanded intelligent I/O service (EI<sup>2</sup>OS).

If the expanded intelligent I/O service (EI<sup>2</sup>OS) has been disabled by interrupt control register (ICR: ISE=0), external interrupt function is enabled and branches to interrupt processing.

If the EI<sup>2</sup>OS has been enabled, (ICR: ISE=1), DTP function is enabled and automatic data transmission is performed by EI<sup>2</sup>OS. After performing specified number of data transmission processes, the process branches to interrupt processing.

|                   | External Interrupt                                                                                          | DTP Function                                                                                                        |  |

|-------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Input pin         | 5 pins (RX, and INT4 to INT7)                                                                               |                                                                                                                     |  |

| Interrupt cause   | Specify for each pin with detection level setting register (ELVR).                                          |                                                                                                                     |  |

|                   | Input of "H" level/"L" level/rising edge/falling edge.                                                      | Input of "H" level/ "L" level                                                                                       |  |

| Interrupt number  | #15 (0Fн), #24 (18н), #27 (1Вн)                                                                             |                                                                                                                     |  |

| Interrupt control | Enabling or disabling output of interrupt request, using DTP/external interrupt permission register (ENIR). |                                                                                                                     |  |

| Interrupt flag    | Retaining interrupt cause with DTP/external interrupt cause register (EIRR).                                |                                                                                                                     |  |

| Process selection | Disable El <sup>2</sup> OS (ICR: ISE=0)                                                                     | Enable El <sup>2</sup> OS (ICR: ISE=1)                                                                              |  |

| Process           | Branch to external interrupt process                                                                        | After automatic data transmission by El <sup>2</sup> OS for specified number of times, branch to interrupt process. |  |

| Table 12-2. | DTP/External In | terrupt and CAN | Wakeup Outline |

|-------------|-----------------|-----------------|----------------|

|-------------|-----------------|-----------------|----------------|

#### 12.11 UART Outline

UART is a general-purpose serial data communication interface for synchronous and asynchronous communication using external devices.

- Provided with bi-directional communication function for both clock-synchronous and clock-asynchronous modes.

- Provided with master/slave communication function (multi-processor mode). (Only master side is available.)

- Interrupt request is generated upon completion of reception, completion of transmission and detection of reception error.

- Ready for expanded intelligent service, El<sup>2</sup>OS.

#### Table 12-3. UART Functions

|                                                                             | Description                                                                                                                                                                                                                   |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Data buffer                                                                 | Full-duplex double buffer                                                                                                                                                                                                     |  |

| Transmission mode                                                           | Clock synchronous (No start/stop bit, no parity bit)<br>Clock asynchronous (start-stop synchronous)                                                                                                                           |  |

| Baud rate                                                                   | Built-in special-purpose baud-rate generator. Setting is selectable amon values.<br>Input of external values is allowed.<br>Use of clock from external timer (16-bit reload timer 0) is allowed.                              |  |

| Data length                                                                 | 7 bits (only asynchronous normal mode)<br>8 bits                                                                                                                                                                              |  |

| Signaling system                                                            | Non Return to Zero (NRZ) system                                                                                                                                                                                               |  |

| Reception error detection                                                   | Framing error<br>Overrun error<br>Parity error (not detectable in operation mode 1 (multi-processor mode))                                                                                                                    |  |

| Interrupt request                                                           | Receive interrupt (reception completed, reception error detected)<br>Transmission interrupt (transmission completed)<br>Ready for expanded intelligent I/O service (El <sup>2</sup> OS) in both transmission and<br>reception |  |

| Master/slave communication function<br>(asynchronous, multi-processor mode) | Communication between 1 (master) and n (slaves) are available (usable as master only).                                                                                                                                        |  |

Note: Start/stop bit is not added upon clock-synchronous transmission. Data only is transmitted.

#### Table 12-4. UART Operation Modes

| Operation Mode |                                    | Data L         | ength          | Synchronization | Stop Bit Length    |

|----------------|------------------------------------|----------------|----------------|-----------------|--------------------|

|                |                                    | With Parity    | Without Parity | Synchronization | Stop Bit Length    |

| 0              | Asynchronous mode<br>(normal mode) | 7-bit or 8-bit |                | Asynchronous    | 1- bit or 2-bit *2 |

| 1              | Multi processor mode               | 8+1*1          | -              | Asynchronous    |                    |

| 2              | Synchronous mode                   | 8              | -              | Synchronous     | No                 |

#### -: Disallowed

1: "+1" is an address/data selection bit used for communication control (bit 11 of SCR1 register: A/D).

2: Only 1 bit is detected as a stop bit on data reception.

#### 12.12 CAN Controller

The Controller Area Network (CAN) is a serial communication protocol compliant with CANVer2.0A and Ver2.0B. The protocol allows data transmission and reception in both standard frame format and expanded frame format.

#### Features of CAN Controller

- CAN controller format is compliant with CANVer2.0A and Ver2.0B.

- The protocol allows data transmission and reception in standard frame format and expanded frame format.

- Automatic transmission of data frame by remote frame reception is allowed.

- Baud rate ranges from 10 kbps to 1 Mbps (with 16-MHz machine clock).

#### Table 12-5. Data Transmission Baud Rate

| Machine Clock | Baud Rate (Max) |

|---------------|-----------------|

| 16 MHz        | 1 Mbps          |

| 12 MHz        | 1 Mbps          |

| 8 MHz         | 1 Mbps          |

| 4 MHz         | 500 kbps        |

| 2 MHz         | 250 kbps        |

- Provided with 8 transmission/reception message buffers.

- Transmission/reception is allowed at ID 11 bit in standard format, and at ID 29 bit in expanded frame format.

- Specifying 0 byte to 8 bytes is allowed in message data.

- Multi-level message buffer configuration is allowed.

- CAN controller has two built-in acceptance masks. Mask settings are independently allowed for the two acceptance masks on reception IDs.

- The two acceptance masks allow reception in standard frame format and expanded frame format.

- For types of masking, all-bit comparison, all-bit masking, and partial masking with acceptance mask register 0/1, are specifiable.

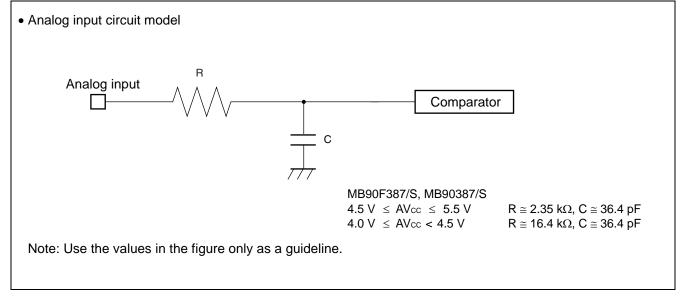

#### 13.7 Notes on A/D Converter Section

Use the device with external circuits of the following output impedance for analog inputs:

Recommended output impedance of external circuits are: Approx. 3.9 k $\Omega$  or lower (4.5 V  $\leq$  AVcc  $\leq$  5.5 V) (sampling period=2.00  $\mu$ s at 16 MHz machine clock), Approx. 11 k $\Omega$  or lower (4.0 V  $\leq$  AVcc < 4.5 V) (sampling period=8.0  $\mu$ s at 16 MHz machine clock).

If an external capacitor is used, in consideration of the effect by tap capacitance caused by external capacitors and on-chip capacitors, capacitance of the external one is recommended to be several thousand times as high as internal capacitor.

If output impedance of an external circuit is too high, a sampling period for an analog voltage may be insufficient.

#### About errors

As [AVR-AVss] become smaller, values of relative errors grow larger.

#### 13.8 Flash Memory Program/Erase Characteristics

| Parameter                               | Conditions                                                                       | Value  |     |       | Unit  | Remarks                                      |

|-----------------------------------------|----------------------------------------------------------------------------------|--------|-----|-------|-------|----------------------------------------------|

| Falameter                               |                                                                                  | Min    | Тур | Max   | Unit  | Remarks                                      |

| Sector erase time                       | $\begin{array}{l} T_{\text{A}}=+~25~^{\circ}C\\ V_{\text{CC}}=5.0~V \end{array}$ | -      | 1   | 15    | S     | Excludes 00H programming<br>prior to erasure |

| Chip erase time                         |                                                                                  | -      | 4   | -     | S     | Excludes 00H programming<br>prior to erasure |

| Word (16-bit width)<br>programming time |                                                                                  | -      | 16  | 3,600 | μS    | Except for the over head time of the system  |

| Program/Erase cycle                     | _                                                                                | 10,000 | -   | -     | cycle |                                              |

| Flash Data Retention Time               | Average<br>T <sub>A</sub> = + 85 °C                                              | 20     | -   | -     | Year  | *                                            |

\*: This value comes from the technology qualification (using Arrhenius equation to translate high temperature measurements into normalized value at + 85 °C).

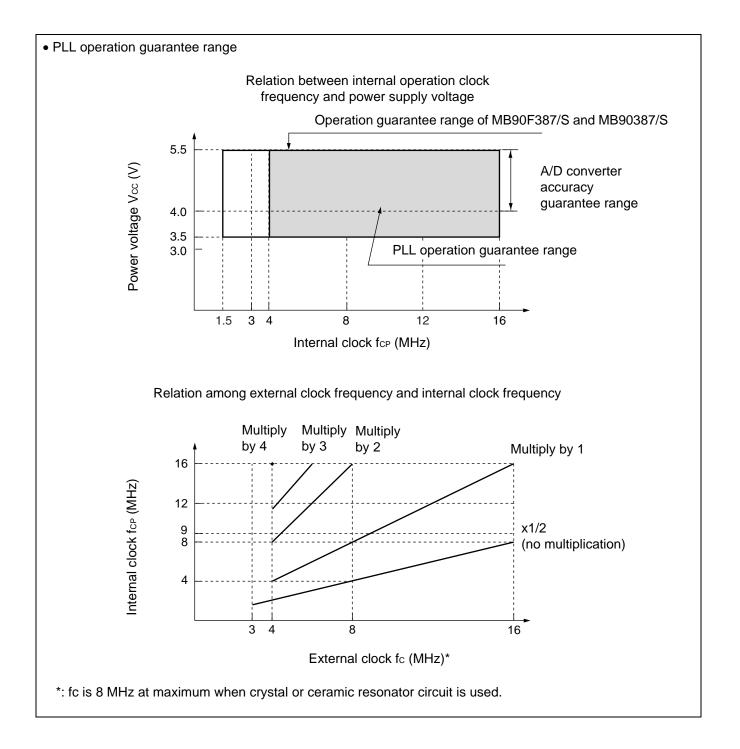

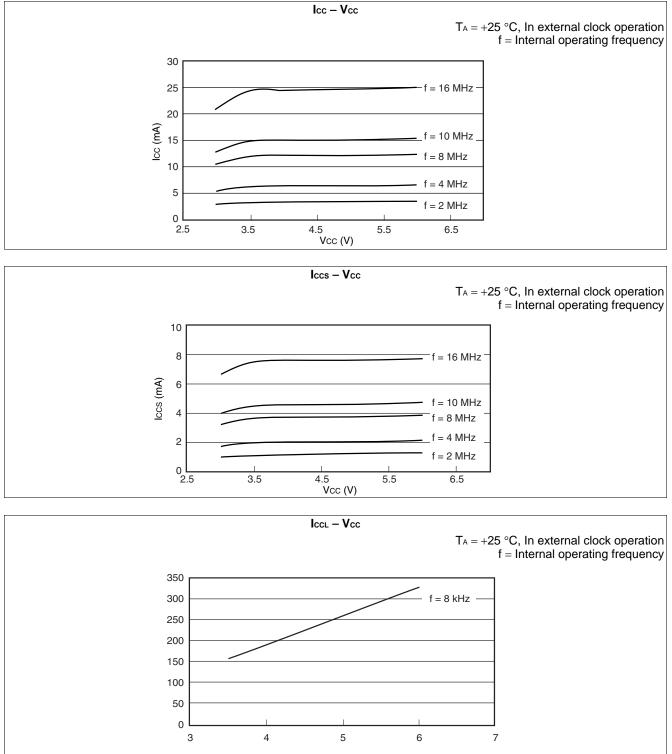

## 14. Example Characteristics

#### MB90F387

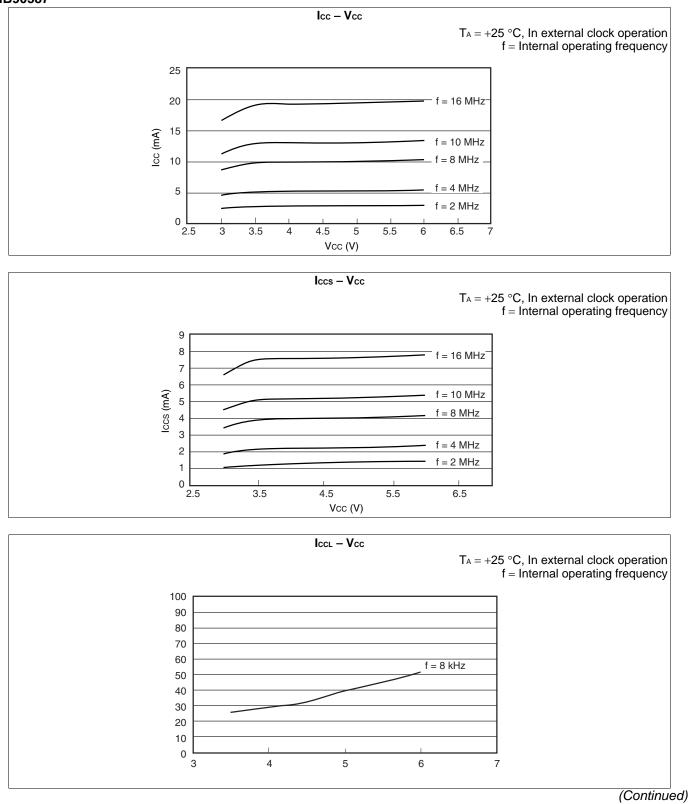

(Continued)

## MB90387/387S/F387/F387S MB90V495G

## 15. Ordering Information

| Part Number                                              | Package                         | Remarks |

|----------------------------------------------------------|---------------------------------|---------|

| MB90F387PMT<br>MB90387PMT<br>MB90F387SPMT<br>MB90387SPMT | 48-pin plastic LQFP<br>(LQA048) |         |

### 16. Package Dimension