Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | F <sup>2</sup> MC-16LX                                                             |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 16MHz                                                                              |

| Connectivity               | CANbus, SCI, UART/USART                                                            |

| Peripherals                | POR, WDT                                                                           |

| Number of I/O              | 36                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | Mask ROM                                                                           |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                        |

| Data Converters            | A/D 8x8/10b                                                                        |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 48-LQFP                                                                            |

| Supplier Device Package    | 48-LQFP (7x7)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-g-383sn-ye1 |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MB90387/387S/F387/F387S MB90V495G

## Contents

| Product Lineup                                              | . 4 |

|-------------------------------------------------------------|-----|

| Packages And Product Models                                 | 5   |

| Product Comparison                                          | . 5 |

| Pin Assignment                                              | 6   |

| Pin Description                                             | . 7 |

| I/O Circuit Type                                            | . 9 |

| Handling Devices                                            | 10  |

| Block Diagram                                               | 12  |

| Memory Map<br>Memory Allocation of MB90385<br>Memory Map    | 12  |

| I/О Мар                                                     | 14  |

| Interrupt Sources, Interrupt Vectors, And Interrupt Control |     |

| Registers                                                   | 21  |

| Peripheral Resources                                        | 22  |

| I/O Ports                                                   | 22  |

| Time-Base Timer                                             | 28  |

| Watchdog Timer                                              | 30  |

| 16-bit Input/Output Timer                                   |     |

| 16-bit Reload Timer                                         |     |

| Watch Timer Outline                                         |     |

| 8/16-bit PPG Timer Outline                                  | 39  |

| Address Matching Detection Function Outline | 43<br>45<br>47<br>49<br>51<br>52       |

|---------------------------------------------|----------------------------------------|

| 512 Kbit Flash Memory Outline               |                                        |

| Electrical Characteristics                  | 55<br>57<br>58<br>60<br>67<br>68<br>70 |

| Example Characteristics 7                   | 71                                     |

| Ordering Information 7                      | 77                                     |

| Package Dimension                           | 78                                     |

| Major Changes 7                             | 79                                     |

| Document History                            |                                        |

| Sales, Solutions, and Legal Information 8   | 81                                     |

## 1. Product Lineup

| Parameter                         | Part Number              | MB90F387<br>MB90F387S                                                                                                                                                                     |                                                                                               |                        |  |  |  |

|-----------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------|--|--|--|

| Classification                    |                          | Flash ROM                                                                                                                                                                                 | Mask ROM                                                                                      | Evaluation product     |  |  |  |

| ROM capacity                      |                          | 64 Kby                                                                                                                                                                                    | 64 Kbytes                                                                                     |                        |  |  |  |

| RAM capacity                      |                          | 2 Kbyt                                                                                                                                                                                    | es                                                                                            | 6 Kbytes               |  |  |  |

| Process                           |                          |                                                                                                                                                                                           | CMOS                                                                                          | 1                      |  |  |  |

| Package                           |                          | LQFP-48 (pin pit                                                                                                                                                                          | ch 0.50 mm)                                                                                   | PGA-256                |  |  |  |

| Operating power                   | supply voltage           | 3.5 V to 5                                                                                                                                                                                | 5.5 V                                                                                         | 4.5 V to 5.5 V         |  |  |  |

| Special power su<br>emulator*1    | ipply for                | -                                                                                                                                                                                         |                                                                                               | None                   |  |  |  |

| CPU functions                     |                          | Number of basic instructions<br>Instruction bit length<br>Instruction length<br>Data bit length                                                                                           | : 351 instructions<br>: 8 bits and 16 bits<br>: 1 byte to 7 bytes<br>: 1 bit, 8 bits, 16 bits |                        |  |  |  |

|                                   |                          | Minimum instruction execution ti                                                                                                                                                          |                                                                                               |                        |  |  |  |

|                                   |                          | Interrupt processing time: 1.5 µs                                                                                                                                                         |                                                                                               |                        |  |  |  |

| Low power const<br>(standby) mode | umption                  | Sleep mode / Watch mode / Time                                                                                                                                                            | e-base timer mode / Stop mo                                                                   | ode / CPU intermittent |  |  |  |

| I/O port                          |                          | General-purpose input/output ports (CMOS output): 34 ports (36 ports*2) including 4 high-current output ports (P14 to P17)                                                                |                                                                                               |                        |  |  |  |

| Time-base timer                   |                          | 18-bit free-run counter<br>Interrupt cycle: 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms<br>(with oscillation clock frequency at 4 MHz)                                                      |                                                                                               |                        |  |  |  |

| Watchdog timer                    |                          | Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms<br>(with oscillation clock frequency at 4 MHz)                                                                             |                                                                                               |                        |  |  |  |

| 16-bit input/<br>output timer     | 16-bit free-run<br>timer | Number of channels: 1<br>Interrupt upon occurrence of overflow                                                                                                                            |                                                                                               |                        |  |  |  |

|                                   | Input capture            | Number of channels: 4<br>Retaining free-run timer value set by pin input (rising edge, falling edge, and both edges)                                                                      |                                                                                               |                        |  |  |  |

| 16-bit reload time                | P.                       | Number of channels: 2<br>16-bit reload timer operation<br>Count clock cycle: 0.25 μs, 0.5 μs, 2.0 μs<br>(at 16-MHz machine clock frequency)<br>External event count is allowed.           |                                                                                               |                        |  |  |  |

| Watch timer                       |                          | 15-bit free-run counter<br>Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s<br>(with 8.192 kHz sub clock)                                                          |                                                                                               |                        |  |  |  |

| 8/16-bit PPG timer                |                          | Number of channels: 2 (four 8-bi<br>PPG operation is allowed with fo<br>Outputting pulse wave of arbitrar<br>Count clock: 62.5 ns to 1 $\mu$ s<br>(with 16 MHz machine clock)             | ur 8-bit channels or two 16-b                                                                 | ut channels.           |  |  |  |

| Delay interrupt g                 | enerator module          | Interrupt generator module for task switching. Used for realtime OS.                                                                                                                      |                                                                                               |                        |  |  |  |

| DTP/External inte                 | errupt                   | Number of inputs: 4<br>Activated by rising edge, falling edge, "H" level or "L" level input.<br>External interrupt or expanded intelligent I/O service (EI <sup>2</sup> OS) is available. |                                                                                               |                        |  |  |  |

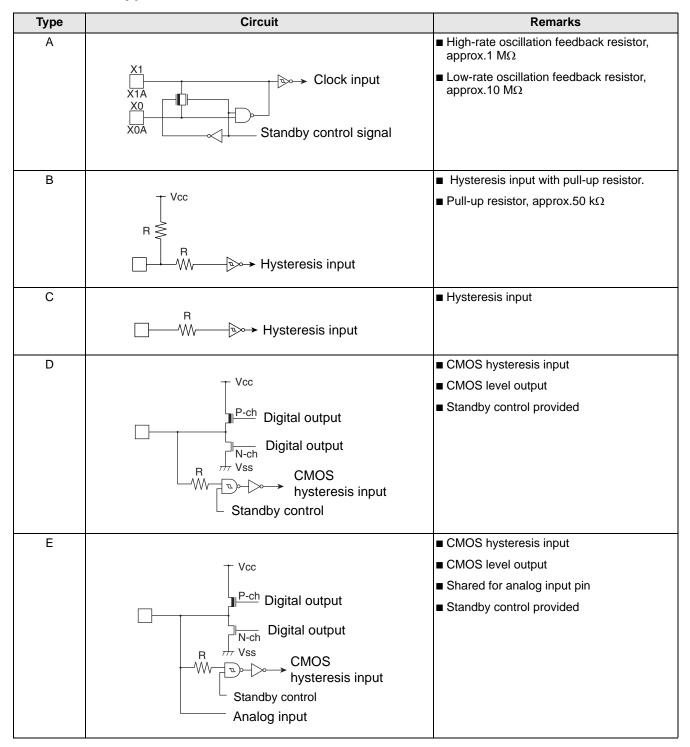

## 6. I/O Circuit Type

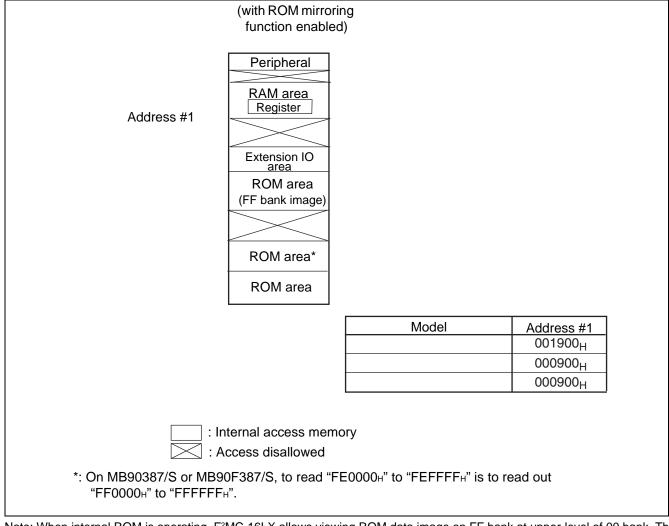

#### 9.2 Memory Map

Note: When internal ROM is operating, F<sup>2</sup>MC-16LX allows viewing ROM data image on FF bank at upper-level of 00 bank. This function is called "mirroring ROM," which allows effective use of C compiler small model.

F<sup>2</sup>MC-16LX assigns the same low order 16-bit address to FF bank and 00 bank, which allows referencing table in ROM without specifying "far" using pointer.

For example, when accessing to "00C000H", ROM data at "FFC000H" is accessed actually. However, because ROM area of FF bank exceeds 48 Kbytes, viewing all areas is not possible on 00 bank image. Because ROM data of "FF4000H" to "FFFFFH" is viewed on "004000H" to "00FFFFH" image, store a ROM data table in area "FF4000H" to "FFFFFH."

# 10. I/O Map

| Address                  | Register<br>Abbreviation | Register                                                    | Read/<br>Write | Resource                  | Initial Value |

|--------------------------|--------------------------|-------------------------------------------------------------|----------------|---------------------------|---------------|

| 00000н                   |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000001н                  | PDR1                     | Port 1 data register                                        | R/W            | Port 1                    | XXXXXXXXB     |

| 000002н                  | PDR2                     | Port 2 data register                                        | R/W            | Port 2                    | XXXXXXXXB     |

| 00003н                   | PDR3                     | Port 3 data register                                        | R/W            | Port 3                    | XXXXXXXXB     |

| 000004н                  | PDR4                     | Port 4 data register                                        | R/W            | Port 4                    | XXXXXXXXB     |

| 000005н                  | PDR5                     | Port 5 data register                                        | R/W            | Port 5                    | XXXXXXXXB     |

| 000006н<br>to<br>000010н |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000011н                  | DDR1                     | Port 1 direction data register                              | R/W            | Port 1                    | 0000000в      |

| 000012н                  | DDR2                     | Port 2 direction data register                              | R/W            | Port 2                    | 0000000в      |

| 000013н                  | DDR3                     | Port 3 direction data register                              | R/W            | Port 3                    | 000Х0000в     |

| 000014н                  | DDR4                     | Port 4 direction data register                              | R/W            | Port 4                    | ХХХ00000в     |

| 000015н                  | DDR5                     | Port 5 direction data register                              | R/W            | Port 5                    | 0000000в      |

| 000016н<br>to<br>00001Ан |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00001Bн                  | ADER                     | Analog input permission register                            | R/W            | 8/10-bit A/D<br>converter | 11111111в     |

| 00001Cнto<br>000025н     |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000026н                  | SMR1                     | Serial mode register 1                                      | R/W            | UART1                     | 0000000в      |

| 000027н                  | SCR1                     | Serial control register 1                                   | R/W, W         |                           | 00000100в     |

| 000028н                  | SIDR1/<br>SODR1          | Serial input data register 1/ Serial output data register 1 | R, W           |                           | XXXXXXXXB     |

| 000029н                  | SSR1                     | Serial status data register 1                               | R, R/W         |                           | 00001000в     |

| 00002Ан                  |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00002Вн                  | CDCR1                    | Communication prescaler control register 1                  | R/W            | UART1                     | 0ХХХ0000в     |

| 00002Cнto<br>00002Fн     |                          | (Reserve                                                    | ed area) *     |                           | ·             |

| 000030н                  | ENIR                     | DTP/External interrupt permission register                  | R/W            | DTP/External<br>interrupt | 0000000в      |

| 000031н                  | EIRR                     | DTP/External interrupt permission register                  | R/W            |                           | XXXXXXXXB     |

| 000032н                  | ELVR                     | Detection level setting register                            | R/W            | 1                         | 0000000в      |

| 000033н                  |                          |                                                             | R/W            | 1                         | 0000000в      |

| 000034н                  | ADCS                     | A/D control status register                                 | R/W            | 8/10-bit A/D              | 0000000в      |

| 000035н                  |                          |                                                             | R/W, W         | converter                 | 0000000в      |

| 000036н                  | ADCR                     | A/D data register                                           | W, R           | 1                         | XXXXXXXXB     |

| 000037н                  |                          |                                                             | R              | 1                         | 00101XXXв     |

| Address                  | Register<br>Abbreviation | Register                                               | Read/<br>Write | Resource                            | Initial Value |

|--------------------------|--------------------------|--------------------------------------------------------|----------------|-------------------------------------|---------------|

| 0000В0н                  | ICR00                    | Interrupt control register 00                          | R/W            | Interrupt controller                | 00000111в     |

| 0000B1н                  | ICR01                    | Interrupt control register 01                          |                |                                     | 00000111в     |

| 0000В2н                  | ICR02                    | Interrupt control register 02                          |                |                                     | 00000111в     |

| 0000ВЗн                  | ICR03                    | Interrupt control register 03                          |                |                                     | 00000111в     |

| 0000В4н                  | ICR04                    | Interrupt control register 04                          |                |                                     | 00000111в     |

| 0000B5н                  | ICR05                    | Interrupt control register 05                          |                |                                     | 00000111в     |

| 0000В6н                  | ICR06                    | Interrupt control register 06                          |                |                                     | 00000111в     |

| <b>0000B7</b> н          | ICR07                    | Interrupt control register 07                          |                |                                     | 00000111в     |

| 0000B8н                  | ICR08                    | Interrupt control register 08                          |                |                                     | 00000111в     |

| 0000B9н                  | ICR09                    | Interrupt control register 09                          |                |                                     | 00000111в     |

| 0000ВАн                  | ICR10                    | Interrupt control register 10                          |                |                                     | 00000111в     |

| 0000ВВн                  | ICR11                    | Interrupt control register 11                          |                |                                     | 00000111в     |

| 0000ВСн                  | ICR12                    | Interrupt control register 12                          |                |                                     | 00000111в     |

| 0000BDн                  | ICR13                    | Interrupt control register 13                          |                |                                     | 00000111в     |

| 0000ВЕн                  | ICR14                    | Interrupt control register 14                          |                |                                     | 00000111в     |

| 0000BFн                  | ICR15                    | Interrupt control register 15                          |                |                                     | 00000111в     |

| 0000C0н<br>to<br>0000FFн |                          | (Reser                                                 | ved area) *    |                                     |               |

| 001FF0⊦                  | PADR0                    | Detection address setting register 0 (low-order)       | R/W            | Address matching detection function | XXXXXXXXB     |

| 001FF1⊦                  |                          | Detection address setting register 0 (middle-order)    |                |                                     | XXXXXXXXB     |

| 001FF2⊦                  |                          | Detection address setting register 0 (high-order)      |                |                                     | XXXXXXXXB     |

| 001FF3⊦                  | PADR1                    | Detection address setting register 1 (low-order)       | R/W            | ] [                                 | XXXXXXXXB     |

| 001FF4⊦                  |                          | Detection address setting register 1<br>(middle-order) |                |                                     | XXXXXXXXB     |

| 001FF5н                  | 1                        | Detection address setting register 1 (high-order)      | 1              |                                     | XXXXXXXXB     |

| 003900н                  | TMR0/                    | 16-bit timer register 0/16-bit reload                  | R,W            | 16-bit reload timer 0               | XXXXXXXXB     |

| 003901н                  | TMRLR0                   | register                                               |                | F F                                 | XXXXXXXXB     |

| 003902н                  | TMR1/                    | 16-bit timer register 1/16-bit reload                  | R,W            | 16-bit reload timer 1               | XXXXXXXXB     |

| 003903н                  | TMRLR1                   | register                                               |                |                                     | XXXXXXXXB     |

| 003904н<br>to<br>00390Fн |                          | (Reser                                                 | ved area) *    |                                     |               |

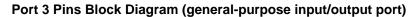

## **Port 3 Registers**

- Port 3 registers include port 3 data register (PDR3) and port 3 direction register (DDR3).

- The bits configuring the register correspond to port 3 pins on a one-to-one basis.

## **Relation between Port 3 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 3    | PDR3, DDR3                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P37  | P36* | P35* | _    | P33  | P32  | P31  | P30  |

\*: P35 and P36 do not exist on MB90387and MB90F387.

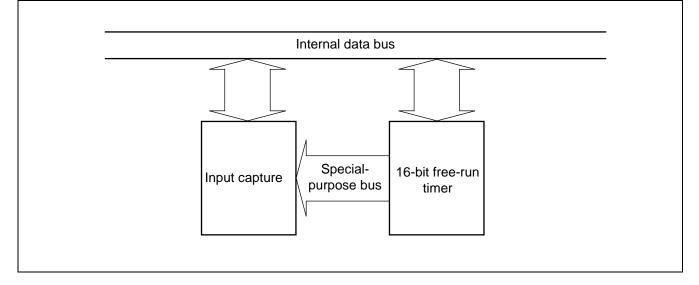

### 12.4 16-bit Input/Output Timer

The 16-bit input/output timer is a compound module composed of 16-bit free-run timer, (1 unit) and input capture (2 units, 4 input pins). The timer, using the 16-bit free-run timer as a basis, enables measurement of clock cycle of an input signal and its pulse width.

#### Configuration of 16-bit Input/Output Timer

The 16-bit input/output timer is composed of the following modules:

- 16-bit free-run timer (1 unit)

- Input capture (2 units, 2 input pins per unit)

#### Functions of 16-bit Input/Output Timer

#### Functions of 16-bit Free-run Timer

The 16-bit free-run timer is composed of 16-bit up counter, timer counter control status register, and prescaler. The 16-bit up counter increments in synchronization with dividing ratio of machine clock.

- Count clock is set among four types of machine clock dividing rates.

- Generation of interrupt is allowed by counter value overflow.

- Activation of expanded intelligent I/O service (EI<sup>2</sup>OS) is allowed by interrupt generation.

- Counter value of 16-bit free-run timer is cleared to "0000<sup>H</sup>" by either resetting or software-clearing with timer count clear bit (TCCS: CLR).

- Counter value of 16-bit free-run timer is output to input capture, which is available as base time for capture operation.

#### Functions of Input Capture

The input capture, upon detecting an edge of a signal input to the input pin from external device, stores a counter value of 16-bit freerun timer at the time of detection into the input capture data register. The function includes the input capture data registers corresponding to four input pins, input capture control status register, and edge detection circuit.

- Rising edge, falling edge, and both edges are selectable for detection.

- Generating interrupt on CPU is allowed by detecting an edge of input signal.

- Expanded intelligent I/O service (EI<sup>2</sup>OS) is activated by interrupt generation.

- The four input capture input pins and input capture data registers allows monitoring of a maximum of four events.

#### 16-bit Input/Output Timer Block Diagram

## 12.7 8/16-bit PPG Timer Outline

The 8/16-bit PPG timer is a 2-channel reload timer module (PPG0 and PPG1) that allows outputting pulses of arbitrary cycle and duty cycle. Combination of the two channels allows selection among the following operations:

- 8-bit PPG output 2-channel independent operation mode

- 16-bit PPG output operation mode

- 8-bit and 8-bit PPG output operation mode

MB90385 series device has two 8/16-bit built-in PPG timers. This section describes functions of PPG0/1. PPG2/3 have the same functions as those of PPG0/1.

#### Functions of 8/16-bit PPG Timer

The 8/16-bit PPG timer is composed of four 8-bit reload register (PRLH0/PRLL0, PRLH1/PRLL1) and two PPG down counters (PCNT0, PCNT1).

- Widths of "H" and "L" in output pulse are specifiable independently. Cycle and duty factor of output pulse is specifiable arbitrarily.

- Count clock is selectable among 6 internal clocks.

- The timer is usable as an interval timer, by generating interrupt requests for each interval.

- The time is usable as a D/A converter, with an external circuit.

# MB90387/387S/F387/F387S MB90V495G

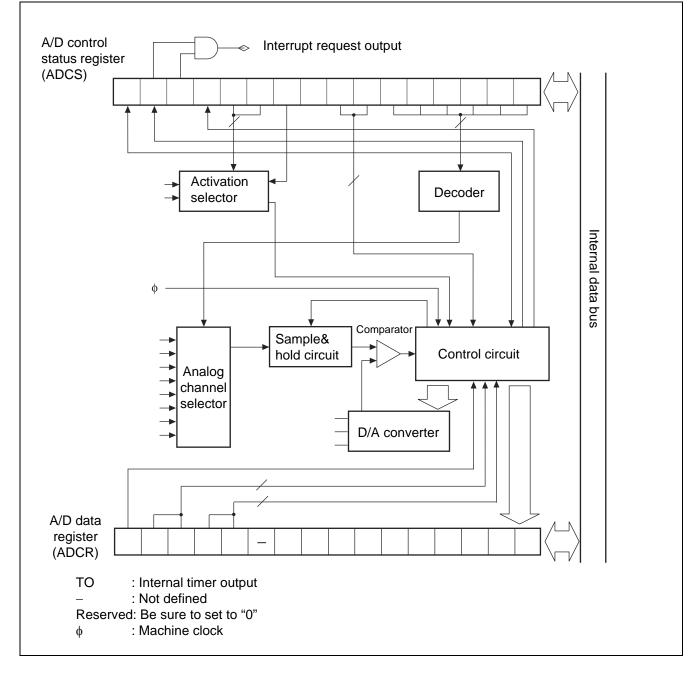

## 8/10-bit A/D Converter Block Diagram

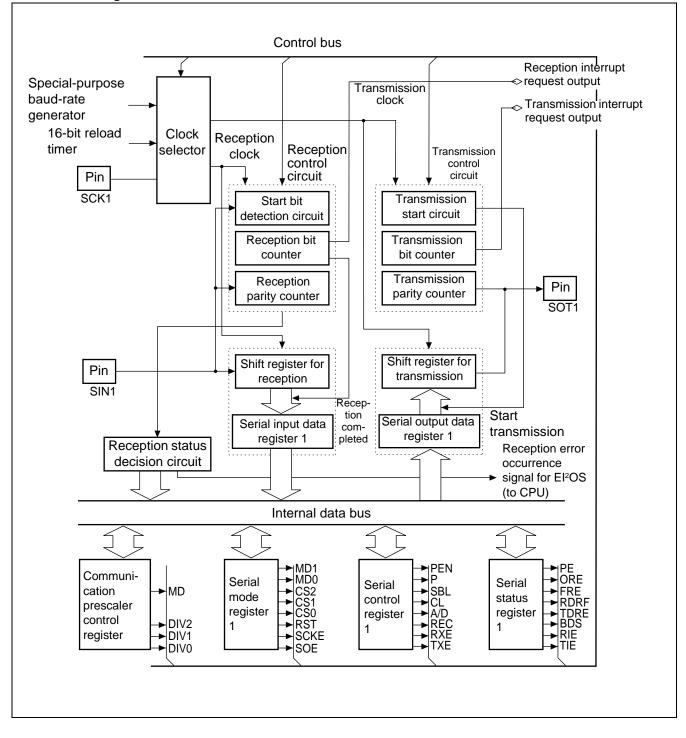

## 12.11 UART Outline

UART is a general-purpose serial data communication interface for synchronous and asynchronous communication using external devices.

- Provided with bi-directional communication function for both clock-synchronous and clock-asynchronous modes.

- Provided with master/slave communication function (multi-processor mode). (Only master side is available.)

- Interrupt request is generated upon completion of reception, completion of transmission and detection of reception error.

- Ready for expanded intelligent service, El<sup>2</sup>OS.

#### Table 12-3. UART Functions

|                                                                          | Description                                                                                                                                                                                                                   |  |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Data buffer                                                              | Full-duplex double buffer                                                                                                                                                                                                     |  |  |  |  |

| Transmission mode                                                        | Clock synchronous (No start/stop bit, no parity bit)<br>Clock asynchronous (start-stop synchronous)                                                                                                                           |  |  |  |  |

| Baud rate                                                                | Built-in special-purpose baud-rate generator. Setting is selectable among 8 values.<br>Input of external values is allowed.<br>Use of clock from external timer (16-bit reload timer 0) is allowed.                           |  |  |  |  |

| Data length                                                              | 7 bits (only asynchronous normal mode)<br>8 bits                                                                                                                                                                              |  |  |  |  |

| Signaling system                                                         | Non Return to Zero (NRZ) system                                                                                                                                                                                               |  |  |  |  |

| Reception error detection                                                | Framing error<br>Overrun error<br>Parity error (not detectable in operation mode 1 (multi-processor mode))                                                                                                                    |  |  |  |  |

| Interrupt request                                                        | Receive interrupt (reception completed, reception error detected)<br>Transmission interrupt (transmission completed)<br>Ready for expanded intelligent I/O service (EI <sup>2</sup> OS) in both transmission and<br>reception |  |  |  |  |

| Master/slave communication function (asynchronous, multi-processor mode) | Communication between 1 (master) and n (slaves) are available (usable as master only).                                                                                                                                        |  |  |  |  |

Note: Start/stop bit is not added upon clock-synchronous transmission. Data only is transmitted.

#### Table 12-4. UART Operation Modes

|   | Operation Mode                     | Data L         | ength          | Synchronization | Stop Bit Length |              |                    |

|---|------------------------------------|----------------|----------------|-----------------|-----------------|--------------|--------------------|

|   | Operation mode                     | With Parity    | Without Parity | Synchronization |                 |              |                    |

| 0 | Asynchronous mode<br>(normal mode) | 7-bit or 8-bit |                | 7-bit or 8-bit  |                 | Asynchronous | 1- bit or 2-bit *2 |

| 1 | Multi processor mode               | 8+1*1          | -              | Asynchronous    |                 |              |                    |

| 2 | Synchronous mode                   | 8              | 8 –            |                 | No              |              |                    |

#### -: Disallowed

1: "+1" is an address/data selection bit used for communication control (bit 11 of SCR1 register: A/D).

2: Only 1 bit is detected as a stop bit on data reception.

### **UART Block Diagram**

## 12.12 CAN Controller

The Controller Area Network (CAN) is a serial communication protocol compliant with CANVer2.0A and Ver2.0B. The protocol allows data transmission and reception in both standard frame format and expanded frame format.

#### Features of CAN Controller

- CAN controller format is compliant with CANVer2.0A and Ver2.0B.

- The protocol allows data transmission and reception in standard frame format and expanded frame format.

- Automatic transmission of data frame by remote frame reception is allowed.

- Baud rate ranges from 10 kbps to 1 Mbps (with 16-MHz machine clock).

#### Table 12-5. Data Transmission Baud Rate

| Machine Clock | Baud Rate (Max) |

|---------------|-----------------|

| 16 MHz        | 1 Mbps          |

| 12 MHz        | 1 Mbps          |

| 8 MHz         | 1 Mbps          |

| 4 MHz         | 500 kbps        |

| 2 MHz         | 250 kbps        |

- Provided with 8 transmission/reception message buffers.

- Transmission/reception is allowed at ID 11 bit in standard format, and at ID 29 bit in expanded frame format.

- Specifying 0 byte to 8 bytes is allowed in message data.

- Multi-level message buffer configuration is allowed.

- CAN controller has two built-in acceptance masks. Mask settings are independently allowed for the two acceptance masks on reception IDs.

- The two acceptance masks allow reception in standard frame format and expanded frame format.

- For types of masking, all-bit comparison, all-bit masking, and partial masking with acceptance mask register 0/1, are specifiable.

## Sector Configuration of 512 Kbit Flash Memory

| Flash memory    | CPU address | Writer address* |

|-----------------|-------------|-----------------|

|                 | FF0000H     | 70000н          |

| SA0 (32 Kbytes) |             |                 |

|                 | FF7FFFH     | 77FFFH          |

|                 | FF8000H     | 78000н          |

| SA1 (8 Kbytes)  |             |                 |

|                 | FF9FFFH     | 79FFFH          |

|                 | FFA000H     | 7А000н          |

| SA2 (8 Kbytes)  |             |                 |

|                 | FFBFFFH     | 7BFFFH          |

|                 | FFC000H     | 7С000н          |

| SA3 (16 Kbytes) |             |                 |

|                 | FFFFFH      | 7FFFFH          |

\*: "Writer address" is an address equivalent to CPU address, which is used when data is written on Flash memory, using parallel writer. When writing/ deleting data with general-purpose writer, the writer address is used for writing and deleting.

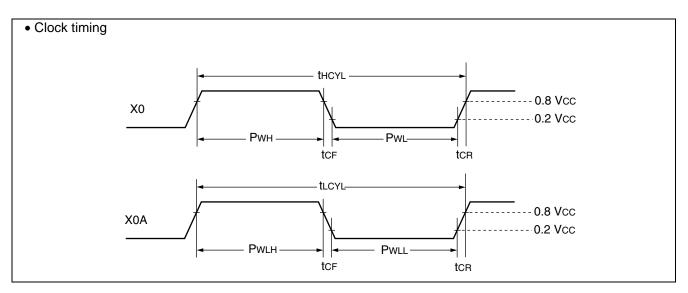

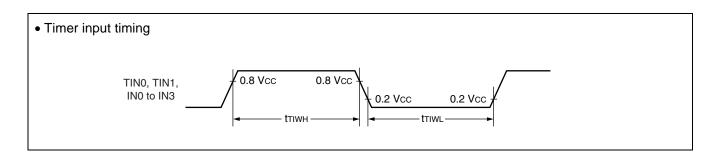

## **13.4 AC Characteristics**

13.4.1 Clock Timing

| Parameter                           | Symbol        | Pin Name |      | Value  |      | Unit | Remarks                                        |

|-------------------------------------|---------------|----------|------|--------|------|------|------------------------------------------------|

| Parameter                           | Symbol        | Pin Name | Min  | Тур    | Max  | Unit | Remarks                                        |

| Clock frequency                     | fc            | X0, X1   | 3    | —      | 8    | MHz  | When crystal or ceramic<br>resonator is used*2 |

|                                     |               |          | 3    | —      | 16   | MHz  | External clock input*1, *2                     |

|                                     |               |          | 4    | —      | 16   | MHz  | PLL Multiply by 1 *2                           |

|                                     |               |          | 4    | —      | 8    | MHz  | PLL Multiply by 2 *2                           |

|                                     |               |          | 4    | —      | 5.33 | MHz  | PLL Multiply by 3 *2                           |

|                                     |               |          | 4    | —      | 4    | MHz  | PLL Multiply by 4 *2                           |

|                                     | fc∟           | X0A, X1A | _    | 32.768 | _    | kHz  |                                                |

| Clock cycle time                    | <b>t</b> HCYL | X0, X1   | 125  | —      | 333  | ns   |                                                |

|                                     | <b>t</b> LCYL | X0A, X1A | _    | 30.5   | _    | μS   |                                                |

| Input clock pulse width             | Pwh, Pwl      | X0       | 10   | —      |      | ns   | Set duty factor at 30% to 70% as a guideline.  |

|                                     | Pwlh,Pwll     | X0A      |      | 15.2   |      | μS   |                                                |

| Input clock rise time and fall time | tcr, tcr      | X0       |      | —      | 5    | ns   | When external clock is used                    |

| Internal operation clock frequency  | fср           | _        | 1.5  | —      | 16   | MHz  | When main clock is used                        |

|                                     | <b>f</b> LCP  | _        |      | 8.192  |      | kHz  | When sub clock is used                         |

| Internal operation clock cycle time | tcp           | _        | 62.5 | —      | 666  | ns   | When main clock is used                        |

|                                     | <b>t</b> LCP  | _        | _    | 122.1  |      | μS   | When sub clock is used                         |

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 \circ C to +105 \circ C)$

\*1: Internal operation clock frequency should not exceed 16 MHz.

\*2: When selecting the PLL clock, the range of clock frequency is limited. Use this product within range as mentioned in "Relation among external clock frequency and internal clock frequency".

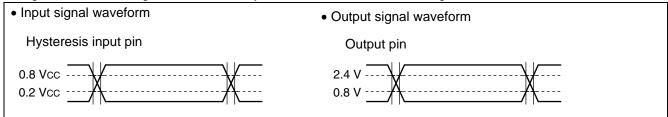

Rating values of alternating current is defined by the measurement reference voltage values shown below:

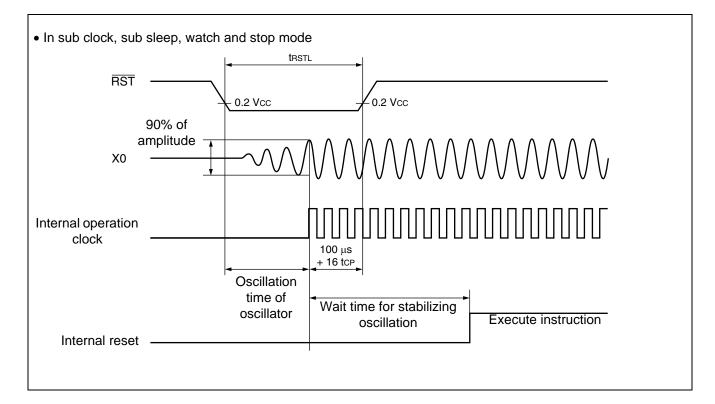

#### 13.4.2 Reset Input Timing

| Parameter        | Symbol        | Pin Name | Value                                                                          |     | Unit | Remarks                                                                                        |  |

|------------------|---------------|----------|--------------------------------------------------------------------------------|-----|------|------------------------------------------------------------------------------------------------|--|

|                  |               |          | Min                                                                            | Мах | Onit | indiks                                                                                         |  |

| Reset input time | <b>t</b> RSTL | RST      | 16 tce*3                                                                       | -   | ns   | Normal operation                                                                               |  |

|                  |               |          | Oscillation time of oscillator <sup>*1</sup> + $100 \ \mu s$ + $16 \ tcP^{*3}$ | -   |      | In sub clock <sup>*2</sup> , sub<br>sleep <sup>*2</sup> , watch <sup>*2</sup> and<br>stop mode |  |

|                  |               |          | 100                                                                            | _   | μS   | In timebase timer                                                                              |  |

\*1: Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

\*2: Except for MB90F387S and MB90387S.

\*3: Refer to "(1) Clock timing" ratings for tcp (internal operation clock cycle time).

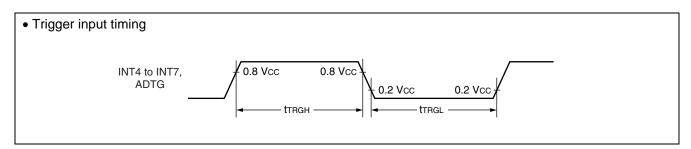

#### 13.4.6 Trigger Input Timing

(Vcc = 4.5 V to 5.5 V, Vss = 0.0 V,  $T_A = -40 \text{ °C to } +105 \text{ °C}$ )

| Parameter         | Symbol         | Pin Name              | Conditions | Value   |     | Unit | Remarks  |

|-------------------|----------------|-----------------------|------------|---------|-----|------|----------|

| Farameter         |                |                       |            | Min     | Max | Unit | itemaiks |

| Input pulse width | ttrgh<br>ttrgl | INT4 to INT7,<br>ADTG | _          | 5 tcթ * | _   | ns   |          |

\*: Refer to Clock Timing ratings for tcp (internal operation clock cycle time).

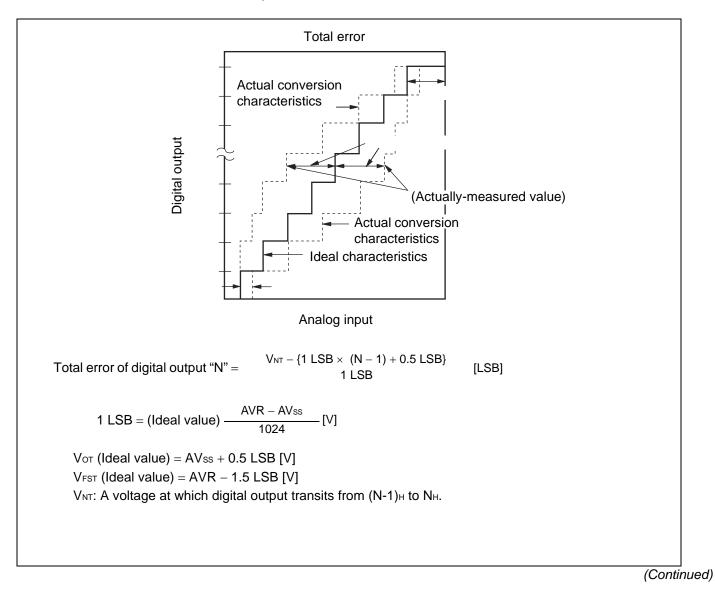

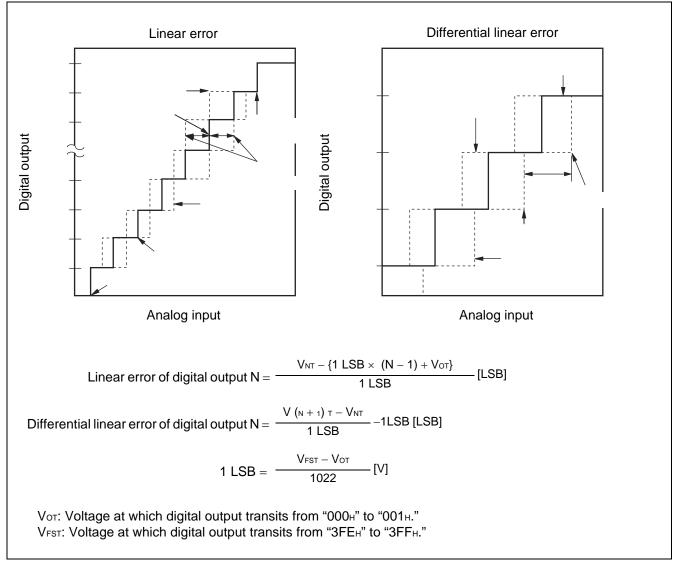

### **13.6 Definition of A/D Converter Terms**

| Resolution:                | Analog variation that is recognized by an A/D converter.                                                                                                                                                                                       |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Linear error:              | Deviation between a line across zero-transition line ("00 0000 00 0" $\leftarrow \rightarrow$ "00 0000 0001") and full-scale transition line ("11 1111 11 1 0" $\leftarrow \rightarrow$ "11 1111 1111") and actual conversion characteristics. |

| Differential linear error: | Deviation of input voltage, which is required for changing output code by 1 LSB, from an ideal value.                                                                                                                                          |

| Total error:               | Difference between an actual value and an ideal value. A total error includes zero transition error, full-<br>scale transition error, and linear error.                                                                                        |

# MB90387/387S/F387/F387S MB90V495G

### (Continued)

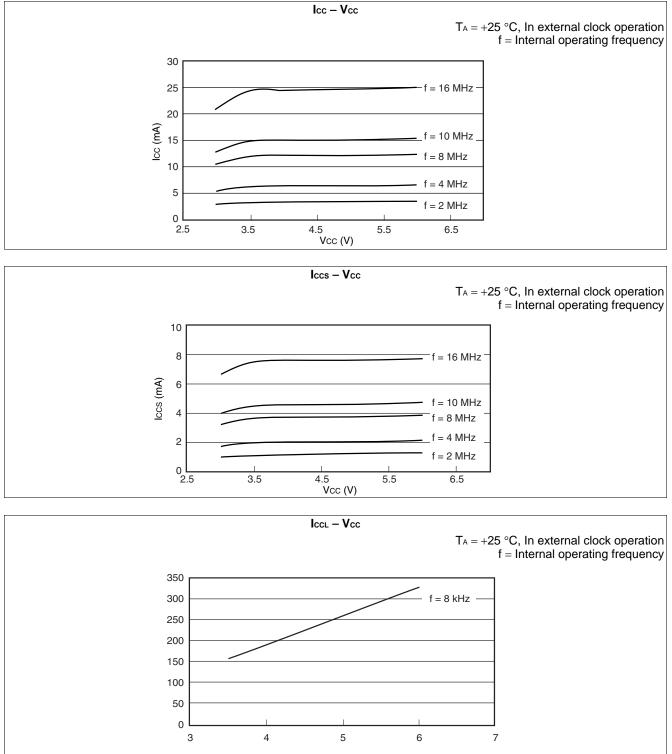

## 14. Example Characteristics

## MB90F387

(Continued)