Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                    |

|----------------------------|------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                           |

| Core Processor             | F <sup>2</sup> MC-16LX                                                             |

| Core Size                  | 16-Bit                                                                             |

| Speed                      | 16MHz                                                                              |

| Connectivity               | CANbus, SCI, UART/USART                                                            |

| Peripherals                | POR, WDT                                                                           |

| Number of I/O              | 36                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                     |

| Program Memory Type        | Mask ROM                                                                           |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 2K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                        |

| Data Converters            | A/D 8x8/10b                                                                        |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                      |

| Package / Case             | 48-LQFP                                                                            |

| Supplier Device Package    | 48-LQFP (7x7)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-g-388sn-ye1 |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

Module for activation of expanded intelligent I/O service (EI<sup>2</sup>OS), and generation of external interrupt.

#### **Delay Interrupt Generator Module**

Generates interrupt request for task switching.

#### 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 μs (at 16 MHz machine clock, including sampling time)

#### **Program Patch Function**

■ Address matching detection for 2 address pointers.

| Part Number<br>Parameter | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MB90387<br>MB90387S | MB90V495G |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|--|--|--|

| 8/10-bit A/D converter   | Number of channels: 8<br>Resolution: Selectable 10-bit or 8-bit.<br>Conversion time: 6.125 µs (at 16 MHz machine clock, including sampling time)<br>Sequential conversion of two or more successive channels is allowed. (Setting a<br>maximum of 8 channels is allowed.)<br>Single conversion mode: Selected channel is converted only once.<br>Sequential conversion mode: Selected channel is converted repetitively.<br>Halt conversion mode: Conversion of selected channel is stopped and activated alter-<br>nately. |                     |           |  |  |  |

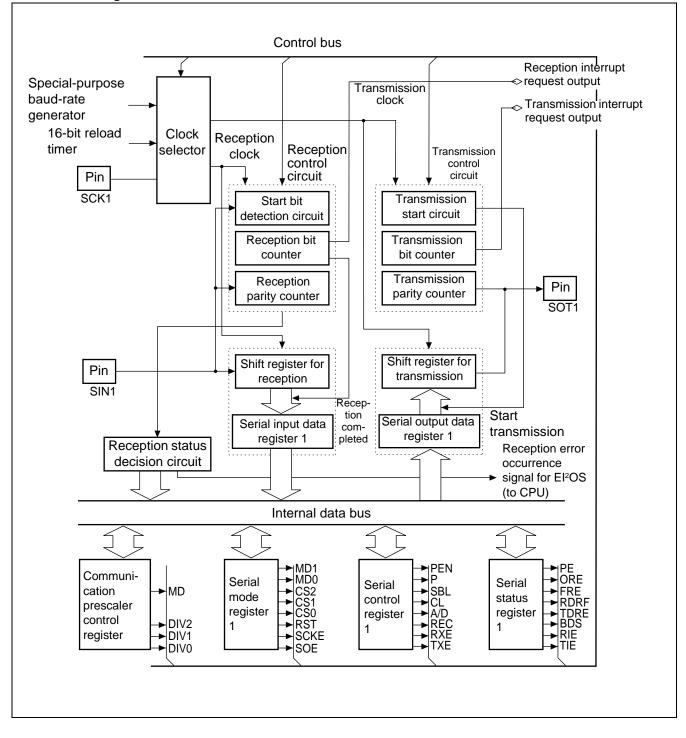

| UART(SCI)                | Number of channels: 1<br>Clock-synchronous transfer: 62.5 kbps to 2 Mbps<br>Clock-asynchronous transfer: 9,615 bps to 500 kbps<br>Communication is allowed by bi-directional serial communication function and master,<br>slave type connection.                                                                                                                                                                                                                                                                            |                     |           |  |  |  |

| CAN                      | 2.0B CAN specifications.<br>1 Mbps (by 16 MHz machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | clock)              |           |  |  |  |

\*1: Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

\*2: MB90387S, MB90F387S

### 2. Packages And Product Models

| Package | MB90F387, MB90F387S | MB90387, MB90387S |

|---------|---------------------|-------------------|

| LQA048  | $\bigcirc$          | $\bigcirc$        |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to Package Dimension for details of the package.

### 3. Product Comparison

#### Memory Space

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

- On MB90V495G, an image from FF4000<sup>H</sup> to FFFFFF<sup>H</sup> is viewed on 00 bank and an image of FE0000<sup>H</sup> to FF3FFF<sup>H</sup> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387/387S, an image from FF4000H to FFFFFFH is viewed on 00 bank and an image of FE0000H to FF3FFFH is viewed only on FF bank.

## 5. Pin Description

| Pin No.  | Pin Name     | Circuit<br>Type | Function                                                                                                    |  |  |  |

|----------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| 1        | AVcc         | -               | Vcc power input pin for A/D converter.                                                                      |  |  |  |

| 2        | AVR          | -               | Power (Vref+) input pin for A/D converter. Use as input for Vcc or lower.                                   |  |  |  |

| 3 to 10  | P50 to P57   | Е               | General-purpose input/output ports.                                                                         |  |  |  |

|          | AN0 to AN7   |                 | Functions as analog input pins for A/D converter. Valid when analog input setting is "enabled."             |  |  |  |

| 11       | P37          | D               | General-purpose input/output port.                                                                          |  |  |  |

|          | ADTG         |                 | Function as an external trigger input pin for A/D converter. Use the pin by setting as input port.          |  |  |  |

| 12       | P20          | D               | General-purpose input/output port.                                                                          |  |  |  |

|          | TIN0         |                 | Function as an event input pin for reload timer 0. Use the pin by setting as input po                       |  |  |  |

| 13       | P21          | D               | General-purpose input/output port.                                                                          |  |  |  |

|          | TOT0         |                 | Function as an event output pin for reload timer 0. Valid only when output setting is "enabled."            |  |  |  |

| 14       | P22          | D               | General-purpose input/output port.                                                                          |  |  |  |

|          | TIN1         |                 | Function as an event input pin for reload timer 1. Use the pin by setting as input po                       |  |  |  |

| 15       | P23          | D               | General-purpose input/output port.                                                                          |  |  |  |

|          | TOT1         |                 | Function as an event output pin for reload timer 1. Valid only when output setting "enabled."               |  |  |  |

| 16 to 19 | P24 to P27   | D               | General-purpose input/output ports.                                                                         |  |  |  |

|          | INT4 to INT7 |                 | Functions as external interrupt input pins. Use the pins by setting as input port.                          |  |  |  |

| 20       | MD2          | F               | Input pin for specifying operation mode. Connect directly to Vss.                                           |  |  |  |

| 21       | MD1          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |  |

| 22       | MD0          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |  |  |  |

| 23       | RST          | В               | External reset input pin.                                                                                   |  |  |  |

| 24       | Vcc          | -               | Power source (5 V) input pin.                                                                               |  |  |  |

| 25       | Vss          | -               | Power source (0 V) input pin.                                                                               |  |  |  |

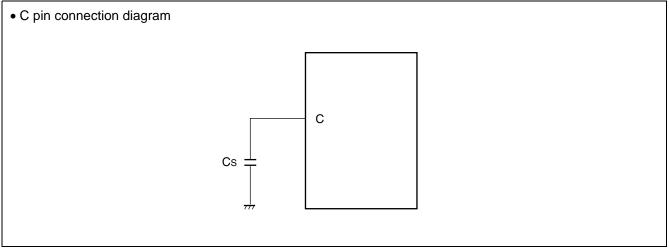

| 26       | С            | -               | Capacitor pin for stabilizing power source. Connect a ceramic capacitor of approximately 0.1 $\mu\text{F}.$ |  |  |  |

| 27       | X0           | А               | Pin for high-rate oscillation.                                                                              |  |  |  |

| 28       | X1           | А               | Pin for high-rate oscillation.                                                                              |  |  |  |

| 29 to 32 | P10 to P13   | D               | General-purpose input/output ports.                                                                         |  |  |  |

|          | IN0 to IN3   |                 | Functions as trigger input pins of input capture ch.0 to ch.3. Use the pins by setting as input ports.      |  |  |  |

| 33 to 36 | P14 to P17   | G               | General-purpose input/output ports. High-current output ports.                                              |  |  |  |

|          | PPG0 to PPG3 |                 | Functions as output pins of PPG timers 01 and 23. Valid when output setting is "enabled."                   |  |  |  |

| 37       | P40          | D               | General-purpose input/output port.                                                                          |  |  |  |

|          | SIN1         |                 | Serial data input pin for UART. Use the pin by setting as input port.                                       |  |  |  |

| 38       | P41          | D               | General-purpose input/output port.                                                                          |  |  |  |

|          | SCK1         |                 | Serial clock input pin for UART. Valid only when serial clock input/output setting on UART is "enabled."    |  |  |  |

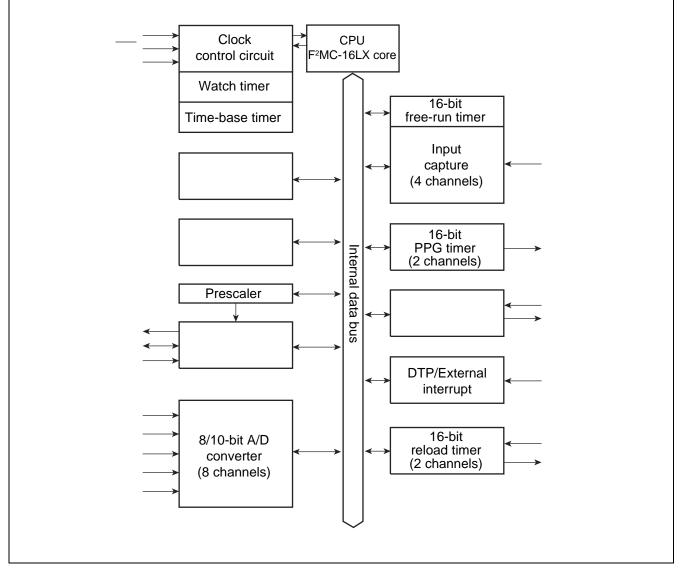

### 8. Block Diagram

#### 9. Memory Map

MB90385 series allows specifying a memory access mode "single chip mode."

#### 9.1 Memory Allocation of MB90385

MB90385 series model has 24-bit wide internal address bus and up to 24-bit bus of external address bus. A maximum of 16-Mbyte memory space of external access memory is accessible.

## 10. I/O Map

| Address                  | Register<br>Abbreviation | Register                                                    | Read/<br>Write | Resource                  | Initial Value |

|--------------------------|--------------------------|-------------------------------------------------------------|----------------|---------------------------|---------------|

| 00000н                   |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000001н                  | PDR1                     | Port 1 data register                                        | R/W            | Port 1                    | XXXXXXXXB     |

| 000002н                  | PDR2                     | Port 2 data register                                        | R/W            | Port 2                    | XXXXXXXXB     |

| 00003н                   | PDR3                     | Port 3 data register                                        | R/W            | Port 3                    | XXXXXXXXB     |

| 000004н                  | PDR4                     | Port 4 data register                                        | R/W            | Port 4                    | XXXXXXXXB     |

| 000005н                  | PDR5                     | Port 5 data register                                        | R/W            | Port 5                    | XXXXXXXXB     |

| 000006н<br>to<br>000010н |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000011н                  | DDR1                     | Port 1 direction data register                              | R/W            | Port 1                    | 0000000в      |

| 000012н                  | DDR2                     | Port 2 direction data register                              | R/W            | Port 2                    | 0000000в      |

| 000013н                  | DDR3                     | Port 3 direction data register                              | R/W            | Port 3                    | 000Х0000в     |

| 000014н                  | DDR4                     | Port 4 direction data register                              | R/W            | Port 4                    | ХХХ00000в     |

| 000015н                  | DDR5                     | Port 5 direction data register                              | R/W            | Port 5                    | 0000000в      |

| 000016н<br>to<br>00001Ан |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00001Bн                  | ADER                     | Analog input permission register                            | R/W            | 8/10-bit A/D<br>converter | 11111111в     |

| 00001Cнto<br>000025н     |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000026н                  | SMR1                     | Serial mode register 1                                      | R/W            | UART1                     | 0000000в      |

| 000027н                  | SCR1                     | Serial control register 1                                   | R/W, W         |                           | 00000100в     |

| 000028н                  | SIDR1/<br>SODR1          | Serial input data register 1/ Serial output data register 1 | R, W           |                           | XXXXXXXXB     |

| 000029н                  | SSR1                     | Serial status data register 1                               | R, R/W         |                           | 00001000в     |

| 00002Ан                  |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00002Вн                  | CDCR1                    | Communication prescaler control register 1                  | R/W            | UART1                     | 0ХХХ0000в     |

| 00002Cнto<br>00002Fн     |                          | (Reserve                                                    | ed area) *     |                           | ·             |

| 000030н                  | ENIR                     | DTP/External interrupt permission register                  | R/W            | DTP/External<br>interrupt | 0000000в      |

| 000031н                  | EIRR                     | DTP/External interrupt permission register                  | R/W            |                           | XXXXXXXXB     |

| 000032н                  | ELVR                     | Detection level setting register                            | R/W            | 1                         | 0000000в      |

| 000033н                  |                          |                                                             | R/W            | 1                         | 0000000в      |

| 000034н                  | ADCS                     | A/D control status register                                 | R/W            | 8/10-bit A/D              | 0000000в      |

| 000035н                  |                          |                                                             | R/W, W         | converter                 | 0000000в      |

| 000036н                  | ADCR                     | A/D data register                                           | W, R           | 1                         | XXXXXXXXB     |

| 000037н                  |                          |                                                             | R              | 1                         | 00101XXXв     |

| Address                  | Register<br>Abbreviation | Register                                               | Read/<br>Write | Resource                            | Initial Value |

|--------------------------|--------------------------|--------------------------------------------------------|----------------|-------------------------------------|---------------|

| 0000В0н                  | ICR00                    | Interrupt control register 00                          | R/W            | Interrupt controller                | 00000111в     |

| 0000B1н                  | ICR01                    | Interrupt control register 01                          |                |                                     | 00000111в     |

| 0000В2н                  | ICR02                    | Interrupt control register 02                          |                |                                     | 00000111в     |

| 0000ВЗн                  | ICR03                    | Interrupt control register 03                          |                |                                     | 00000111в     |

| 0000В4н                  | ICR04                    | Interrupt control register 04                          |                |                                     | 00000111в     |

| 0000B5н                  | ICR05                    | Interrupt control register 05                          |                |                                     | 00000111в     |

| 0000В6н                  | ICR06                    | Interrupt control register 06                          |                |                                     | 00000111в     |

| <b>0000B7</b> н          | ICR07                    | Interrupt control register 07                          |                |                                     | 00000111в     |

| 0000B8н                  | ICR08                    | Interrupt control register 08                          |                |                                     | 00000111в     |

| 0000B9н                  | ICR09                    | Interrupt control register 09                          |                |                                     | 00000111в     |

| 0000ВАн                  | ICR10                    | Interrupt control register 10                          |                |                                     | 00000111в     |

| 0000ВВн                  | ICR11                    | Interrupt control register 11                          |                |                                     | 00000111в     |

| 0000ВСн                  | ICR12                    | Interrupt control register 12                          |                |                                     | 00000111в     |

| 0000BDн                  | ICR13                    | Interrupt control register 13                          |                |                                     | 00000111в     |

| 0000ВЕн                  | ICR14                    | Interrupt control register 14                          |                |                                     | 00000111в     |

| 0000BFн                  | ICR15                    | Interrupt control register 15                          |                |                                     | 00000111в     |

| 0000C0н<br>to<br>0000FFн |                          | (Reser                                                 | ved area) *    |                                     |               |

| 001FF0⊦                  | PADR0                    | Detection address setting register 0 (low-order)       | R/W            | Address matching detection function | XXXXXXXXB     |

| 001FF1⊦                  |                          | Detection address setting register 0 (middle-order)    |                |                                     | XXXXXXXXB     |

| 001FF2⊦                  |                          | Detection address setting register 0 (high-order)      |                |                                     | XXXXXXXXB     |

| 001FF3⊦                  | PADR1                    | Detection address setting register 1 (low-order)       | R/W            | ] [                                 | XXXXXXXXB     |

| 001FF4⊦                  |                          | Detection address setting register 1<br>(middle-order) |                |                                     | XXXXXXXXB     |

| 001FF5н                  | 1                        | Detection address setting register 1 (high-order)      | 1              |                                     | XXXXXXXXB     |

| 003900н                  | TMR0/                    | 16-bit timer register 0/16-bit reload                  | R,W            | 16-bit reload timer 0               | XXXXXXXXB     |

| 003901н                  | TMRLR0                   | register                                               |                | F F                                 | XXXXXXXXB     |

| 003902н                  | TMR1/                    | 16-bit timer register 1/16-bit reload                  | R,W            | 16-bit reload timer 1               | XXXXXXXXB     |

| 003903н                  | TMRLR1                   | register                                               |                |                                     | XXXXXXXXB     |

| 003904н<br>to<br>00390Fн |                          | (Reser                                                 | ved area) *    |                                     |               |

| Address                  | Register<br>Abbreviation | Register                                                         | Read/<br>Write | Resource       | Initial Value                |                |          |  |  |  |

|--------------------------|--------------------------|------------------------------------------------------------------|----------------|----------------|------------------------------|----------------|----------|--|--|--|

| 003D0Dн                  |                          | (Reserv                                                          | ed area) *     |                |                              |                |          |  |  |  |

| 003D0Eн                  | TIER                     | Send completion interrupt permission R/W CAN controller register |                |                |                              | CAN controller | 0000000в |  |  |  |

| 003D0Fн                  |                          | (Reserved area) *                                                |                |                |                              |                |          |  |  |  |

| 003D10н,<br>003D11н      | AMSR                     | Acceptance mask selection register R/W CAN controller            |                | CAN controller | XXXXXXXXB,<br>XXXXXXXB       |                |          |  |  |  |

| 003D12н,<br>003D13н      | (Reserved area) *        |                                                                  |                |                |                              |                |          |  |  |  |

| 003D14н<br>to<br>003D17н | AMR0                     | Acceptance mask register 0                                       | R/W            | CAN controller | XXXXXXXXB<br>to<br>XXXXXXXXB |                |          |  |  |  |

| 003D18н<br>to<br>003D1Bн | AMR1                     | Acceptance mask register 1                                       | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |                |          |  |  |  |

| 003D1Cн<br>to<br>003DFFн |                          | (Reserv                                                          | ed area) *     |                |                              |                |          |  |  |  |

| 003E00н<br>to<br>003EFFн |                          | (Reserved area) *                                                |                |                |                              |                |          |  |  |  |

| 003FF0н<br>to<br>003FFFн |                          | (Reserv                                                          | ed area) *     |                |                              |                |          |  |  |  |

Initial values:

0: Initial value of this bit is "0."

1: Initial value of this bit is "1."

X: Initial value of this bit is undefined.

\*: "Reserved area" should not be written anything. Result of reading from "Reserved area" is undefined.

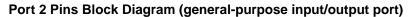

#### **Port 2 Registers**

- Port 2 registers include port 2 data register (PDR2) and port 2 direction register (DDR2).

- The bits configuring the register correspond to port 2 pins on a one-to-one basis.

#### **Relation between Port 2 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 2    | PDR2,DDR2                               | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P27  | P26  | P25  | P24  | P23  | P22  | P21  | P20  |

### MB90387/387S/F387/F387S MB90V495G

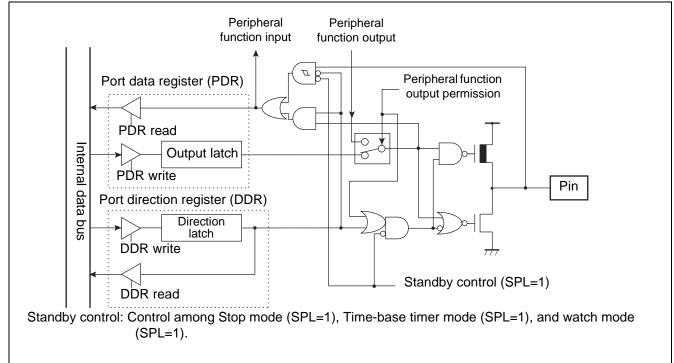

#### Time-base Timer Block Diagram

Actual interrupt request number of time-base timer is as follows: Interrupt request number: #16 (10<sub>H</sub>)

### MB90387/387S/F387/F387S MB90V495G

#### Watchdog timer control register(WDTC) Watch timer control register (WTC) WRST ERST SRST WTE WT1 WT0 PONR \_\_\_\_ WDCS Watchdog timer 2, Activate Reset occurs \_ Counter Watchdog Shift to sleep mode -----2-bit Internal reset Count clock reset clear control Shift to time-base counter - 6 generation generation selector circuit timer mode circuit circuit Shift to watch mode Clear Shift to stop mode 4 4 Time-base timer counter Main clock $\times 2^2$ × 28 × 29 × 210 × 211 × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> $\times 2^1$ × 215 × 216 × 2<sup>17</sup> $\times 2^{18}$ (dividing HCLK by 2) Watch counter Sub clock $\times 2^2$ × 2<sup>5</sup> $\times 2^{6}$ × 2<sup>8</sup> × 2<sup>9</sup> × 2<sup>10</sup> × 2<sup>11</sup> × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> × 2<sup>15</sup> $\times 2^{1}$ $\times 2^7$ . SCLK HCLK: Oscillation clock SCLK: Sub clock

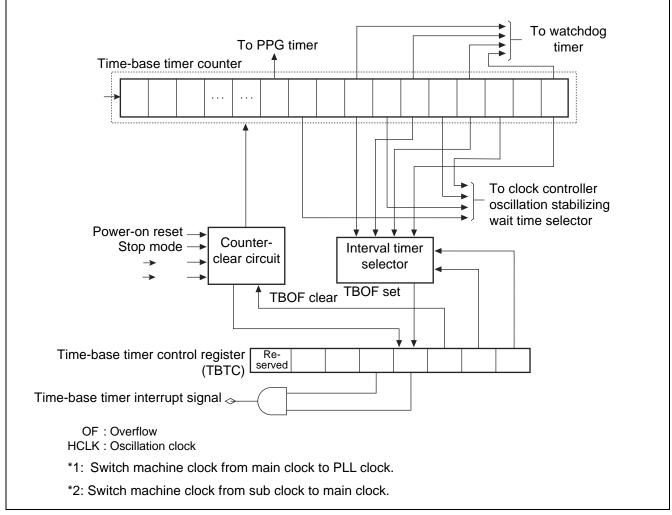

#### Watchdog Timer Block Diagram

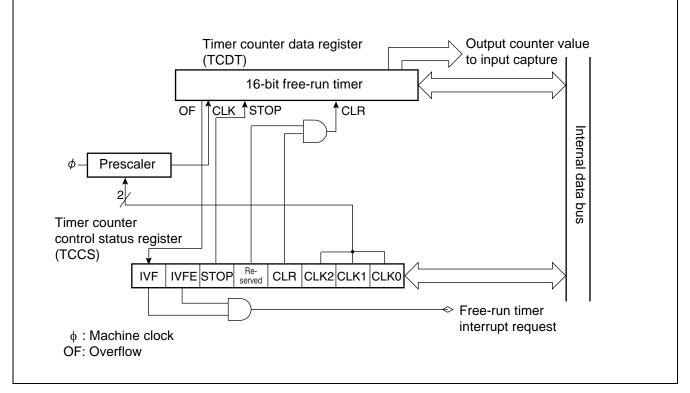

#### 16-bit Free-run Timer

Counter value of 16-bit free-run timer is used as reference time (base time) of input capture.

#### Input Capture

Input capture detects rising edge, falling edge or both edges and retains a counter value of 16-bit free-run timer. Detection of edge on input signal is allowed to generate interrupt.

#### 16-bit Free-run Timer Block Diagram

#### **Detailed Pin Assignment on Block Diagram**

The 16-bit input/output timer includes a 16-bit free-run timer. Interrupt request number of the 16-bit free-run timer is as follows: Interrupt request number: 19 (13<sub>H</sub>)

#### Prescaler

The prescaler divides a machine clock and provides a counter clock to the 16-bit up counter. Dividing ratio of the machine clock is specified by timer counter control status register (TCCS) among four values.

#### Timer Counter Data Register (TCDT)

The timer counter data register is a 16-bit up counter. A current counter value of the 16-bit free-run timer is read. Writing a value during halt of the counter allows setting an arbitrary counter value.

## MB90387/387S/F387/F387S MB90V495G

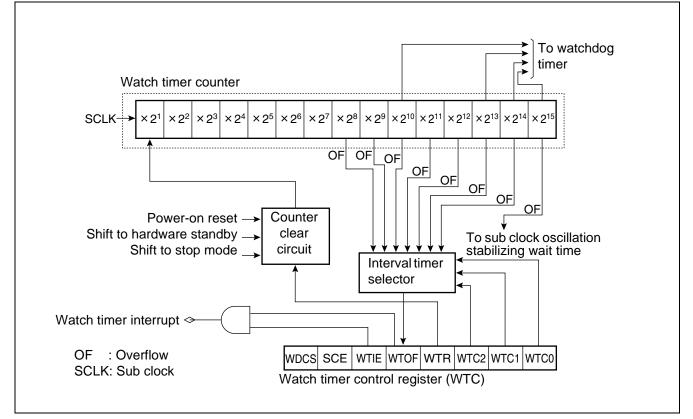

#### Watch Timer Block Diagram

Actual interrupt request number of watch timer is as follows: Interrupt request number: #28 (1C<sub>H</sub>)

#### Watch Timer Counter

A 15-bit up counter that uses sub clock (SCLK) as a count clock.

#### **Counter Clear Circuit**

A circuit that clears the watch timer counter.

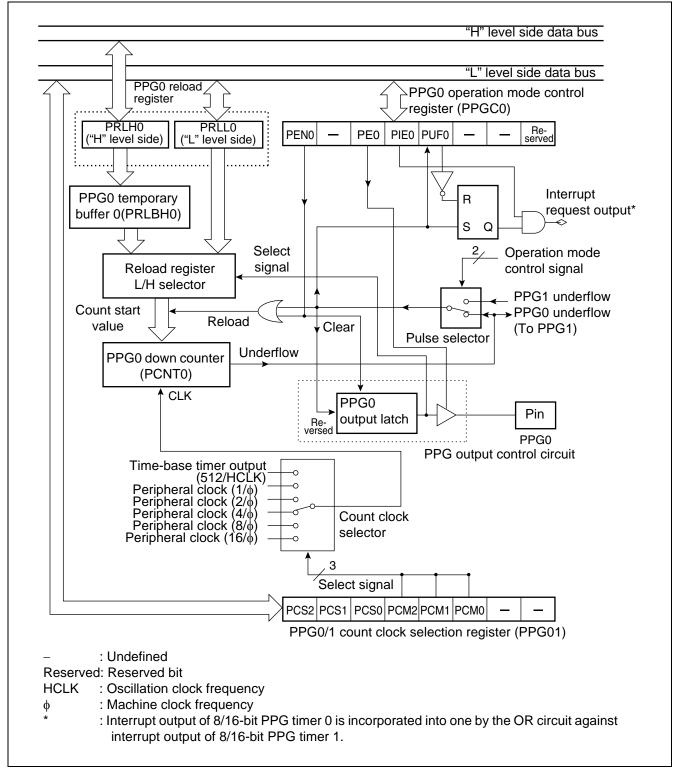

#### 8/16-bit PPG Timer 0 Block Diagram

#### 12.9 DTP/External Interrupt and CAN Wakeup Outline

DTP/external interrupt transfers an interrupt request generated by an external peripheral device or a data transmission request to CPU, generating external interrupt request and activating expanded intelligent I/O service. Input RX of CAN controller is used as external interrupt input.

#### **DTP/External Interrupt and CAN Wakeup Function**

An interrupt request input from external peripheral device to external input pins (INT7 to INT4) and RX pin, just as interrupt request of peripheral device, generates an interrupt request. The interrupt request generates an external interrupt and activates expanded intelligent I/O service (EI<sup>2</sup>OS).

If the expanded intelligent I/O service (EI<sup>2</sup>OS) has been disabled by interrupt control register (ICR: ISE=0), external interrupt function is enabled and branches to interrupt processing.

If the EI<sup>2</sup>OS has been enabled, (ICR: ISE=1), DTP function is enabled and automatic data transmission is performed by EI<sup>2</sup>OS. After performing specified number of data transmission processes, the process branches to interrupt processing.

|                   | External Interrupt                                         | DTP Function                                                                                                        |  |  |  |  |

|-------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Input pin         | 5 pins (RX, and INT4 to INT7)                              |                                                                                                                     |  |  |  |  |

| Interrupt cause   | Specify for each pin with detection level setting r        | egister (ELVR).                                                                                                     |  |  |  |  |

|                   | Input of "H" level/"L" level/rising edge/falling edge.     | Input of "H" level/ "L" level                                                                                       |  |  |  |  |

| Interrupt number  | #15 (0Fн), #24 (18н), #27 (1Вн)                            |                                                                                                                     |  |  |  |  |

| Interrupt control | Enabling or disabling output of interrupt request, (ENIR). | using DTP/external interrupt permission register                                                                    |  |  |  |  |

| Interrupt flag    | Retaining interrupt cause with DTP/external inter          | rrupt cause register (EIRR).                                                                                        |  |  |  |  |

| Process selection | Disable El <sup>2</sup> OS (ICR: ISE=0)                    | Enable El <sup>2</sup> OS (ICR: ISE=1)                                                                              |  |  |  |  |

| Process           | Branch to external interrupt process                       | After automatic data transmission by El <sup>2</sup> OS for specified number of times, branch to interrupt process. |  |  |  |  |

| Table 12-2. | DTP/External In | terrupt and CAN | Wakeup Outline |

|-------------|-----------------|-----------------|----------------|

|-------------|-----------------|-----------------|----------------|

#### **UART Block Diagram**

#### 12.15 512 Kbit Flash Memory Outline

The following three methods are provided for data writing and deleting on Flash memory:

- 1. Parallel writer

- 2. Serial special-purpose writer

- 3. Writing/deleting by program execution

This section describes "3. Writing/deleting by program execution."

#### 512 Kbit Flash Memory Outline

The 512 Kbit Flash memory is allocated on FF<sub>H</sub> bank of CPU memory map. Using the function of Flash memory interface circuit, the memory allows read access and program access from CPU.

Writing/deleting on Flash memory is performed by instruction from CPU via Flash memory interface. Because rewriting is allowed on mounted memory, modifying program and data is performed efficiently.

#### Features of 512 Kbit Flash Memory

- 128 K words x 8 bits/64 K words x 16 bits (16 K + 8 K + 8 K + 32 K) sector configuration

- Automatic program algorithm (Embedded Algorithm: Similar to MBM29LV200.)

- Built-in deletion pause/deletion resume function

- Detection of completed writing/deleting by data polling and toggle bits.

- Detection of completed writing/deleting by CPU interrupt.

- Deletion is allowed on a sector-by-sector basis (sectors are combined freely).

- Number of writing/deleting operations (minimum): 10,000 times

- Sector protection

- Expanded sector protection

- Temporaly sector unprotection

Note: A function of reading manufacture code and device code is not provided. These codes are not accessible by command either.

#### Flash Memory Writing/Deleting

- Writing and reading data is not allowed simultaneously on the Flash memory.

- Data writing and deleting on the Flash memory is performed by the processes as follows: Make a copy of program on Flash memory onto RAM. Then, execute the program copied on the RAM.

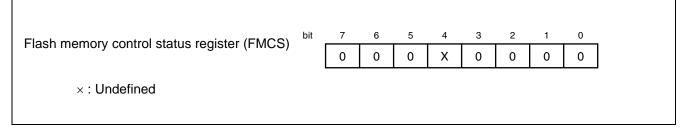

#### List of Registers and Reset Values in Flash Memory

#### Sector Configuration

For access from CPU, SA0 to SA3 are allocated in FF bank register.

#### 13.2 Recommended Operating Conditions

(Vss = AVss = 0.0V)

| Parameter             | Symbol | Value |     |      |      | Remarks                            |  |

|-----------------------|--------|-------|-----|------|------|------------------------------------|--|

| Falameter             | Symbol | Min   | Тур | Max  | Unit | Reindi K5                          |  |

| Power supply voltage  | Vcc    | 3.5   | 5.0 | 5.5  | V    | Under normal operation             |  |

|                       |        | 3.0   | _   | 5.5  |      | Retain status of stop<br>operation |  |

|                       | AVcc   | 4.0   | -   | 5.5  | V    | *2                                 |  |

| Smoothing capacitor   | Cs     | 0.1   | -   | 1.0  | μF   | *1                                 |  |

| Operating temperature | TA     | -40   | -   | +105 | °C   |                                    |  |

\*1: Use a ceramic capacitor, or a capacitor of similar frequency characteristics. On the Vcc pin, use a bypass capacitor that has a larger capacity than that of Cs.

Refer to the following figure for connection of smoothing capacitor Cs.

\*2: AVcc is a voltage at which accuracy is guaranteed. AVcc should not exceed Vcc.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

| Deremeter                   | Symbol | /mbol Pin Name                                | Conditions                                                                                                  |     | Value | Unit | Remarks |                                                                 |

|-----------------------------|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|------|---------|-----------------------------------------------------------------|

| Parameter                   | Symbol | Pin Name                                      | Conditions                                                                                                  | Min | Тур   | Max  | Unit    | Remarks                                                         |

| Power<br>supply<br>current* | lcc∟   | Vcc                                           | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>subclock operation,                                       |     | 0.3   | 1.2  | mA      | MB90F387/S                                                      |

| 000                         |        |                                               | $T_A = +25^{\circ}C$                                                                                        |     | 40    | 100  | μΑ      | MB90387/S                                                       |

|                             | ICCLS  |                                               | $V_{CC} = 5.0 V$ ,<br>Internally operating at 8 kHz,<br>subclock,<br>sleep mode,<br>$T_{A} = + 25^{\circ}C$ | _   | 10    | 30   | μA      |                                                                 |

|                             | Ісст   |                                               | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>watch mode,<br>$T_A = + 25^{\circ}C$                      |     | 8     | 25   | μΑ      |                                                                 |

|                             | Іссн   |                                               | Stopping,<br>T <sub>A</sub> = + 25°C                                                                        | _   | 5     | 20   | μΑ      |                                                                 |

| Input<br>capacity           | CIN    | Other than AVcc,<br>AVss, AVR, C, Vcc,<br>Vss | -                                                                                                           | _   | 5     | 15   | pF      |                                                                 |

| Pull-up<br>resistor         | Rup    | RST                                           | -                                                                                                           | 25  | 50    | 100  | kΩ      |                                                                 |

| Pull-down<br>resistor       | Rdown  | MD2                                           | -                                                                                                           | 25  | 50    | 100  | kΩ      | Flash product is<br>not provided<br>with pull-down<br>resistor. |

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 \circ C to +105 \circ C)$

\*: Test conditions of power supply current are based on a device using external clock.

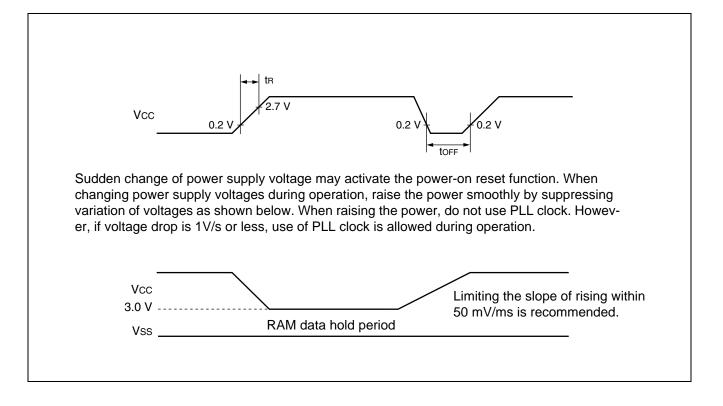

13.4.3 Power-on Reset

| Parameter                  | Symbol     | Pin Name | Conditions | Value |     | Unit | Remarks                        |

|----------------------------|------------|----------|------------|-------|-----|------|--------------------------------|

| Farameter                  |            |          |            | Min   | Max | Unit | Relliarks                      |

| Power supply rise time     | <b>t</b> ℝ | Vcc      | -          | 0.05  | 30  | ms   |                                |

| Power supply shutdown time | toff       | Vcc      |            | 1     | -   | ms   | Waiting time until<br>power-on |

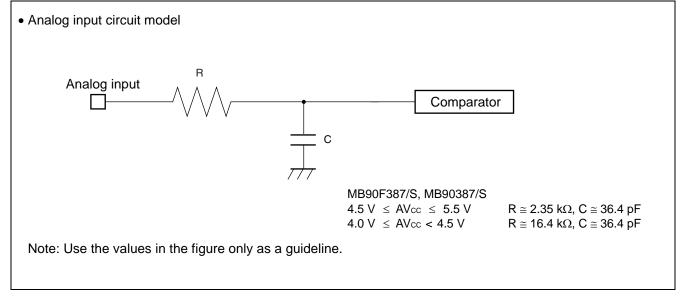

#### 13.7 Notes on A/D Converter Section

Use the device with external circuits of the following output impedance for analog inputs:

Recommended output impedance of external circuits are: Approx. 3.9 k $\Omega$  or lower (4.5 V  $\leq$  AVcc  $\leq$  5.5 V) (sampling period=2.00  $\mu$ s at 16 MHz machine clock), Approx. 11 k $\Omega$  or lower (4.0 V  $\leq$  AVcc < 4.5 V) (sampling period=8.0  $\mu$ s at 16 MHz machine clock).

If an external capacitor is used, in consideration of the effect by tap capacitance caused by external capacitors and on-chip capacitors, capacitance of the external one is recommended to be several thousand times as high as internal capacitor.

If output impedance of an external circuit is too high, a sampling period for an analog voltage may be insufficient.

#### About errors

As [AVR-AVss] become smaller, values of relative errors grow larger.

#### 13.8 Flash Memory Program/Erase Characteristics

| Parameter                               | Conditions                                                                       |         | Value |       | Unit  | Remarks                                      |  |

|-----------------------------------------|----------------------------------------------------------------------------------|---------|-------|-------|-------|----------------------------------------------|--|

| Falameter                               | Conditions                                                                       | Min Typ |       | Max   | Onit  | Remarks                                      |  |

| Sector erase time                       | $\begin{array}{l} T_{\text{A}}=+~25~^{\circ}C\\ V_{\text{CC}}=5.0~V \end{array}$ | -       | 1     | 15    | S     | Excludes 00H programming<br>prior to erasure |  |

| Chip erase time                         |                                                                                  | -       | 4     | -     | S     | Excludes 00H programming<br>prior to erasure |  |

| Word (16-bit width)<br>programming time |                                                                                  | -       | 16    | 3,600 | μS    | Except for the over head time of the system  |  |

| Program/Erase cycle                     | _                                                                                | 10,000  | -     | -     | cycle |                                              |  |

| Flash Data Retention Time               | Average<br>T <sub>A</sub> = + 85 °C                                              | 20      | -     | -     | Year  | *                                            |  |

\*: This value comes from the technology qualification (using Arrhenius equation to translate high temperature measurements into normalized value at + 85 °C).