Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                          |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | CANbus, SCI, UART/USART                                                         |

| Peripherals                | POR, WDT                                                                        |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | Mask ROM                                                                        |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x8/10b                                                                     |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 48-LQFP                                                                         |

| Supplier Device Package    | 48-LQFP (7x7)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-gs-110e1 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Part Number<br>Parameter | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MB90387<br>MB90387S | MB90V495G                 |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|--|--|--|

| 8/10-bit A/D converter   | Number of channels: 8<br>Resolution: Selectable 10-bit or 8-bit.<br>Conversion time: 6.125 $\mu$ s (at 16 MHz machine clock, including sampling time)<br>Sequential conversion of two or more successive channels is allowed. (Setting a<br>maximum of 8 channels is allowed.)<br>Single conversion mode: Selected channel is converted only once.<br>Sequential conversion mode: Selected channel is converted repetitively.<br>Halt conversion mode: Conversion of selected channel is stopped and activated alter-<br>nately. |                     |                           |  |  |  |

| UART(SCI)                | Number of channels: 1<br>Clock-synchronous transfer: 62.9<br>Clock-asynchronous transfer: 9,0<br>Communication is allowed by bi-<br>slave type connection.                                                                                                                                                                                                                                                                                                                                                                       | 615 bps to 500 kbps | tion function and master/ |  |  |  |

| CAN                      | Compliant with Ver 2.0A and Ver<br>8 built-in message buffers.<br>Transmission rate of 10 kbps to<br>CAN wake-up                                                                                                                                                                                                                                                                                                                                                                                                                 | ·                   | clock)                    |  |  |  |

\*1: Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

\*2: MB90387S, MB90F387S

## 2. Packages And Product Models

| Package | MB90F387, MB90F387S | MB90387, MB90387S |

|---------|---------------------|-------------------|

| LQA048  | $\bigcirc$          | $\bigcirc$        |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to Package Dimension for details of the package.

## 3. Product Comparison

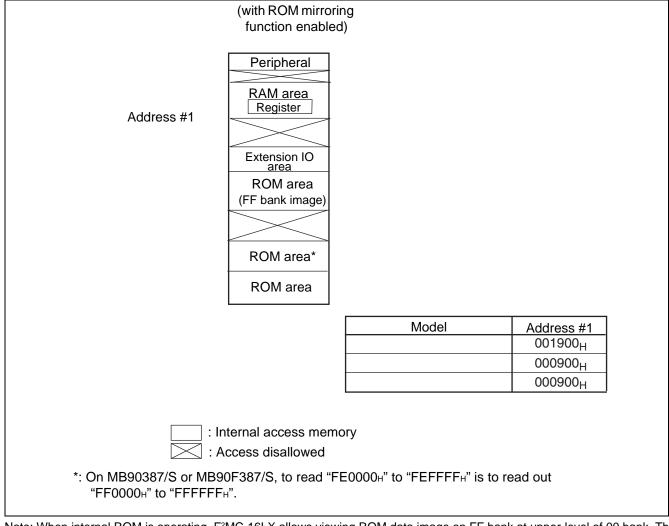

## Memory Space

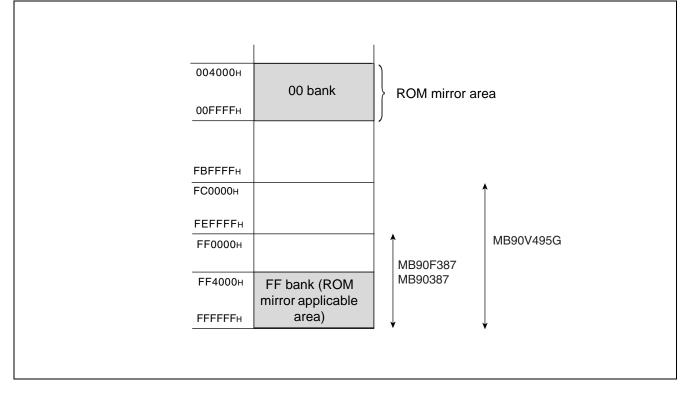

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

- On MB90V495G, an image from FF4000<sup>H</sup> to FFFFFF<sup>H</sup> is viewed on 00 bank and an image of FE0000<sup>H</sup> to FF3FFF<sup>H</sup> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387/387S, an image from FF4000H to FFFFFFH is viewed on 00 bank and an image of FE0000H to FF3FFFH is viewed only on FF bank.

# 5. Pin Description

| Pin No.  | Pin Name     | Circuit<br>Type | Function                                                                                                    |

|----------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------|

| 1        | AVcc         | -               | Vcc power input pin for A/D converter.                                                                      |

| 2        | AVR          | -               | Power (Vref+) input pin for A/D converter. Use as input for Vcc or lower.                                   |

| 3 to 10  | P50 to P57   | Е               | General-purpose input/output ports.                                                                         |

|          | AN0 to AN7   |                 | Functions as analog input pins for A/D converter. Valid when analog input setting is "enabled."             |

| 11       | P37          | D               | General-purpose input/output port.                                                                          |

|          | ADTG         |                 | Function as an external trigger input pin for A/D converter. Use the pin by setting as input port.          |

| 12       | P20          | D               | General-purpose input/output port.                                                                          |

|          | TIN0         |                 | Function as an event input pin for reload timer 0. Use the pin by setting as input port.                    |

| 13       | P21          | D               | General-purpose input/output port.                                                                          |

|          | TOT0         |                 | Function as an event output pin for reload timer 0. Valid only when output setting is "enabled."            |

| 14       | P22          | D               | General-purpose input/output port.                                                                          |

|          | TIN1         |                 | Function as an event input pin for reload timer 1. Use the pin by setting as input port.                    |

| 15       | P23          | D               | General-purpose input/output port.                                                                          |

|          | TOT1         |                 | Function as an event output pin for reload timer 1. Valid only when output setting is "enabled."            |

| 16 to 19 | P24 to P27   | D               | General-purpose input/output ports.                                                                         |

|          | INT4 to INT7 |                 | Functions as external interrupt input pins. Use the pins by setting as input port.                          |

| 20       | MD2          | F               | Input pin for specifying operation mode. Connect directly to Vss.                                           |

| 21       | MD1          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |

| 22       | MD0          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                           |

| 23       | RST          | В               | External reset input pin.                                                                                   |

| 24       | Vcc          | -               | Power source (5 V) input pin.                                                                               |

| 25       | Vss          | -               | Power source (0 V) input pin.                                                                               |

| 26       | С            | -               | Capacitor pin for stabilizing power source. Connect a ceramic capacitor of approximately 0.1 $\mu\text{F}.$ |

| 27       | X0           | А               | Pin for high-rate oscillation.                                                                              |

| 28       | X1           | А               | Pin for high-rate oscillation.                                                                              |

| 29 to 32 | P10 to P13   | D               | General-purpose input/output ports.                                                                         |

|          | IN0 to IN3   |                 | Functions as trigger input pins of input capture ch.0 to ch.3. Use the pins by setting as input ports.      |

| 33 to 36 | P14 to P17   | G               | General-purpose input/output ports. High-current output ports.                                              |

|          | PPG0 to PPG3 |                 | Functions as output pins of PPG timers 01 and 23. Valid when output setting is "enabled."                   |

| 37       | P40          | D               | General-purpose input/output port.                                                                          |

|          | SIN1         |                 | Serial data input pin for UART. Use the pin by setting as input port.                                       |

| 38       | P41          | D               | General-purpose input/output port.                                                                          |

|          | SCK1         |                 | Serial clock input pin for UART. Valid only when serial clock input/output setting on UART is "enabled."    |

#### 9.2 Memory Map

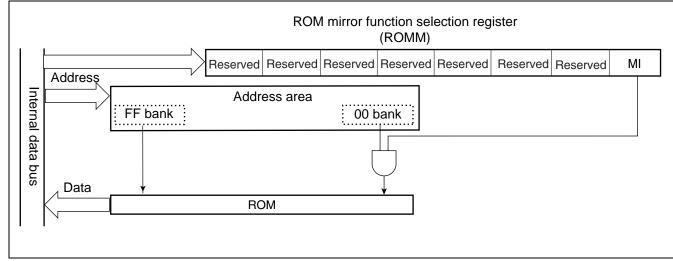

Note: When internal ROM is operating, F<sup>2</sup>MC-16LX allows viewing ROM data image on FF bank at upper-level of 00 bank. This function is called "mirroring ROM," which allows effective use of C compiler small model.

F<sup>2</sup>MC-16LX assigns the same low order 16-bit address to FF bank and 00 bank, which allows referencing table in ROM without specifying "far" using pointer.

For example, when accessing to "00C000H", ROM data at "FFC000H" is accessed actually. However, because ROM area of FF bank exceeds 48 Kbytes, viewing all areas is not possible on 00 bank image. Because ROM data of "FF4000H" to "FFFFFH" is viewed on "004000H" to "00FFFFH" image, store a ROM data table in area "FF4000H" to "FFFFFH."

| Address                  | Register<br>Abbreviation | Register                                                | Read/<br>Write | Resource                            | Initial Value         |  |  |  |  |  |

|--------------------------|--------------------------|---------------------------------------------------------|----------------|-------------------------------------|-----------------------|--|--|--|--|--|

| 000083н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |  |

| 000084н                  | TCANR                    | Send cancel register                                    | W              | CAN controller                      | 0000000в              |  |  |  |  |  |

| 000085н                  |                          | (Reserved area) *                                       |                |                                     |                       |  |  |  |  |  |

| 000086н                  | TCR                      | Send completion register                                | R/W            | CAN controller                      | 0000000в              |  |  |  |  |  |

| 000087н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |  |

| 000088н                  | RCR                      | Receive completion register                             | R/W            | CAN controller                      | 0000000в              |  |  |  |  |  |

| 000089н                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |  |

| 00008Ан                  | RRTRR                    | Receive RTR register                                    | R/W            | CAN controller                      | 0000000в              |  |  |  |  |  |

| 00008Вн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |  |

| 00008Сн                  | ROVRR                    | Receive overrun register                                | R/W            | CAN controller                      | 0000000в              |  |  |  |  |  |

| 00008Dн                  |                          | (Reserve                                                | ed area) *     |                                     |                       |  |  |  |  |  |

| 00008Eн                  | RIER                     | Receive completion interrupt<br>permission register     | R/W            | CAN controller                      | 0000000в              |  |  |  |  |  |

| 00008Fн<br>to<br>00009Dн |                          | (Reserv                                                 | ed area) *     |                                     |                       |  |  |  |  |  |

| 00009Eн                  | PACSR                    | Address detection control register                      | R/W            | Address matching detection function | 0000000в              |  |  |  |  |  |

| 00009Fн                  | DIRR                     | Delay interrupt request generation/<br>release register | R/W            | Delay interrupt generation module   | XXXXXXX0B             |  |  |  |  |  |

| 0000А0н                  | LPMCR                    | Lower power consumption mode control register           | W,R/W          | Lower power consumption mode        | 00011000в             |  |  |  |  |  |

| 0000A1н                  | CKSCR                    | Clock selection register                                | R,R/W          | Clock                               | 11111100в             |  |  |  |  |  |

| 0000А2н<br>to<br>0000А7н |                          | (Reserv                                                 | ed area) *     |                                     |                       |  |  |  |  |  |

| 0000A8н                  | WDTC                     | Watchdog timer control register                         | R,W            | Watchdog timer                      | XXXXX111 <sub>B</sub> |  |  |  |  |  |

| 0000A9н                  | TBTC                     | Time-base timer control register                        | R/W,W          | Time-base timer                     | 1XX00100в             |  |  |  |  |  |

| 0000ААн                  | WTC                      | Watch timer control register                            | R,R/W          | Watch timer                         | 1Х001000в             |  |  |  |  |  |

| 0000ABн<br>to<br>0000ADн |                          | (Reserv                                                 | ed area) *     | · · · · ·                           |                       |  |  |  |  |  |

| 0000AEн                  | FMCS                     | Flash memory control status register                    | R,W,R/W        | 512k-bit Flash<br>memory            | 000X0000 <sub>B</sub> |  |  |  |  |  |

| 0000AFн                  |                          | (Reserv                                                 | ed area) *     | . 1                                 |                       |  |  |  |  |  |

| Address                  | Register<br>Abbreviation | Register               | Read/<br>Write    | Resource               | Initial Value                 |  |  |

|--------------------------|--------------------------|------------------------|-------------------|------------------------|-------------------------------|--|--|

| 003910н                  | PRLL0                    | PPG0 reload register L | R/W               | 8/16-bit PPG timer     | XXXXXXXXB                     |  |  |

| <b>003911</b> н          | PRLH0                    | PPG0 reload register H | R/W               |                        | XXXXXXXXB                     |  |  |

| 003912н                  | PRLL1                    | PPG1 reload register L | R/W               |                        | XXXXXXXXB                     |  |  |

| 003913н                  | PRLH1                    | PPG1 reload register H | R/W               |                        | XXXXXXXXB                     |  |  |

| 003914н                  | PRLL2                    | PPG2 reload register L | R/W               |                        | XXXXXXXXB                     |  |  |

| <b>003915</b> н          | PRLH2                    | PPG2 reload register H | R/W               |                        | XXXXXXXXB                     |  |  |

| <b>003916</b> н          | PRLL3                    | PPG3 reload register L | R/W               |                        | XXXXXXXX <sub>B</sub>         |  |  |

| <b>003917</b> н          | PRLH3                    | PPG3 reload register H | R/W               |                        | XXXXXXXXB                     |  |  |

| 003918н<br>to<br>00392Fн |                          |                        | (Reserved area) * |                        |                               |  |  |

| 003930н<br>to<br>003BFFн |                          |                        | (Reserved area) * |                        |                               |  |  |

| 003C00н<br>to<br>003C0Fн |                          | RAM (                  | General-purpose R | AM)                    |                               |  |  |

| 003C10н<br>to<br>003C13н | IDR0                     | ID register 0          | R/W               | CAN controller         | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |

| 003C14н<br>to<br>003C17н | IDR1                     | ID register 1          | R/W               | -                      | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |

| 003C18н<br>to<br>003C1Bн | IDR2                     | ID register 2          | R/W               | _                      | XXXXXXXXB<br>to<br>XXXXXXXB   |  |  |

| 003C1Cн<br>to<br>003C1Fн | IDR3                     | ID register 3          | R/W               | -                      | XXXXXXXXB<br>to<br>XXXXXXXXB  |  |  |

| 003C20н<br>to<br>003C23н | IDR4                     | ID register 4          | R/W               | _                      | XXXXXXXXB<br>to<br>XXXXXXXB   |  |  |

| 003C24н<br>to<br>003C27н | IDR5                     | ID register 5          | R/W               | _                      | XXXXXXXXAB<br>to<br>XXXXXXXXB |  |  |

| 003C28н<br>to<br>003C2Bн | IDR6                     | ID register 6          | R/W               | -                      | XXXXXXXXB<br>to<br>XXXXXXXB   |  |  |

| 003C2Cн<br>to<br>003C2Fн | IDR7                     | ID register 7          | R/W               |                        | XXXXXXXXB<br>to<br>XXXXXXXB   |  |  |

| 003C30н,<br>003C31н      | DLCR0                    | DLC register 0         | R/W               |                        | XXXXXXXXB,<br>XXXXXXXB        |  |  |

| 003C32н,<br>003C33н      | DLCR1                    | DLC register 1         |                   | XXXXXXXXB,<br>XXXXXXXB |                               |  |  |

| 003C34н,<br>003C35н      | DLCR2                    | DLC register 2         | R/W               |                        | XXXXXXXXB,<br>XXXXXXXXB       |  |  |

| 003C36н,<br>003C37н      | DLCR3                    | DLC register 3         | R/W               |                        | XXXXXXXXB,<br>XXXXXXXXB       |  |  |

| Address                  | Register<br>Abbreviation | Register                                      | Read/<br>Write | Resource       | Initial Value                |  |  |  |  |  |

|--------------------------|--------------------------|-----------------------------------------------|----------------|----------------|------------------------------|--|--|--|--|--|

| 003D0Dн                  |                          | (Reserv                                       | ed area) *     |                |                              |  |  |  |  |  |

| 003D0Eн                  | TIER                     | Send completion interrupt permission register | R/W            | CAN controller | 0000000в                     |  |  |  |  |  |

| 003D0Fн                  |                          | (Reserved area) *                             |                |                |                              |  |  |  |  |  |

| 003D10н,<br>003D11н      | AMSR                     | Acceptance mask selection register            | R/W            | CAN controller | XXXXXXXXB,<br>XXXXXXXB       |  |  |  |  |  |

| 003D12н,<br>003D13н      | (Reserved area) *        |                                               |                |                |                              |  |  |  |  |  |

| 003D14н<br>to<br>003D17н | AMR0                     | Acceptance mask register 0                    | R/W            | CAN controller | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003D18н<br>to<br>003D1Bн | AMR1                     | Acceptance mask register 1                    | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003D1Cн<br>to<br>003DFFн |                          | (Reserv                                       | ed area) *     |                |                              |  |  |  |  |  |

| 003E00н<br>to<br>003EFFн |                          | (Reserved area) *                             |                |                |                              |  |  |  |  |  |

| 003FF0н<br>to<br>003FFFн |                          | (Reserv                                       | ed area) *     |                |                              |  |  |  |  |  |

Initial values:

0: Initial value of this bit is "0."

1: Initial value of this bit is "1."

X: Initial value of this bit is undefined.

\*: "Reserved area" should not be written anything. Result of reading from "Reserved area" is undefined.

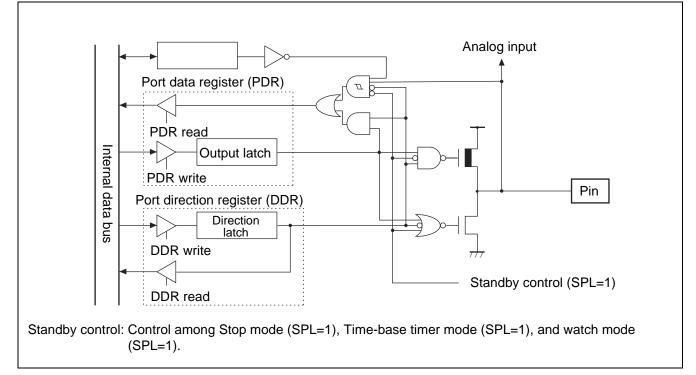

## Port 5 Pins Block Diagram

## **Port 5 Registers**

- Port 5 registers include port 5 data register (PDR5), port 5 direction register (DDR5), and analog input permission register (ADER).

- Analog input permission register (ADER) allows or disallows input of analog signal to the analog input pin.

- The bits configuring the register correspond to port 5 pins on a one-to-one basis.

#### **Relation between Port 5 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 5    | PDR5, DDR5                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | ADER                                    | ADE7 | ADE6 | ADE5 | ADE4 | ADE3 | ADE2 | ADE1 | ADE0 |

|           | Corresponding pins                      | P57  | P56  | P55  | P54  | P53  | P52  | P51  | P50  |

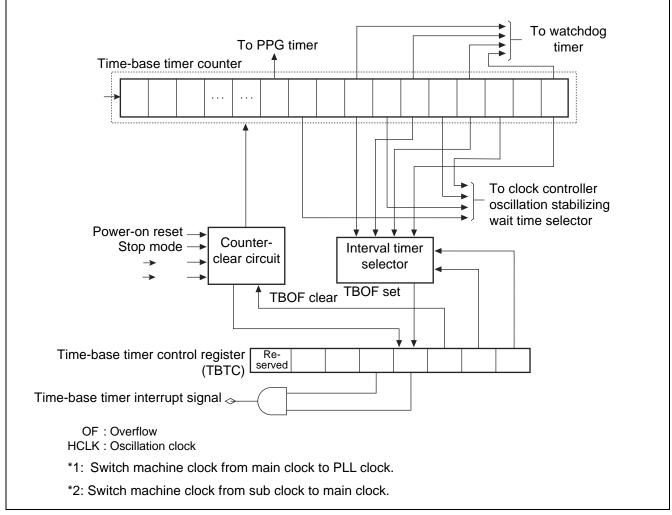

## Time-base Timer Block Diagram

Actual interrupt request number of time-base timer is as follows: Interrupt request number: #16 (10<sub>H</sub>)

## 12.3 Watchdog Timer

The watchdog timer is a 2-bit counter that uses time-base timer or watch timer as count clock. If the counter is not cleared within an interval time, CPU is reset.

### Watchdog Timer Functions

- The watchdog timer is a timer counter that prevents runaway of a program. Once a watchdog timer is activated, the counter of watchdog timer must always be cleared within a specified time of interval. If specified interval time elapses without clearing the counter of a watchdog timer, CPU resetting occurs. This is the function of a watchdog timer.

- The interval time of a watchdog timer is determined by a clock cycle, which is input as a count clock. Watchdog resetting occurs between a minimum time and a maximum time specified.

- The output target of a clock source is specified by the watchdog clock selection bit (WTC: WDCS) in the watch timer control register.

- Interval time of a watchdog timer is specified by the time-base timer output selection bit / watch timer output selection bit (WDTC: WT1, WT0) in the watchdog timer control register.

| Min                  | Мах                  | Clock Cycle                                  | Min                 | Max                 | Clock Cycle                                  |

|----------------------|----------------------|----------------------------------------------|---------------------|---------------------|----------------------------------------------|

| Approx. 3.58 ms      | Approx. 4.61 ms      | (2 <sup>14</sup> ±2 <sup>11</sup> )<br>/HCLK | Approx. 0.457 s     | Approx. 0.576 s     | (2 <sup>12</sup> ±2 <sup>9</sup> )<br>/SCLK  |

| Approx. 14.33 ms     | Approx. 18.3 ms      | (2 <sup>16</sup> ±2 <sup>13</sup> )<br>/HCLK | Approx. 3.584 s     | Approx. 4.608 s     | (2 <sup>15</sup> ±2 <sup>12</sup> )<br>/SCLK |

| Approx. 57.23 ms     | Approx. 73.73 ms     | (2 <sup>18</sup> ±2 <sup>15</sup> )<br>/HCLK | Approx. 7.168 s     | Approx. 9.216 s     | (2 <sup>16</sup> ±2 <sup>13</sup> )<br>/SCLK |

| Approx.<br>458.75 ms | Approx.<br>589.82 ms | (2 <sup>21</sup> ±2 <sup>18</sup> )<br>/HCLK | Approx.<br>14.336 s | Approx.<br>18.432 s | (2 <sup>17</sup> ±2 <sup>14</sup> )<br>/SCLK |

#### Interval Timer of Watchdog Timer

HCLK: Oscillation clock (4 MHz), CSCLK: Sub clock (8.192 kHz)

#### Notes:

- If the time-base timer is cleared when watchdog timer count clock is used as time base timer output (carry-over signal), watchdog reset time may become longer.

- When using the sub clock as machine clock, be sure to specify watchdog timer clock source selection bit (WDCS) in watch timer control register (WTC) at "0," selecting output of watch timer.

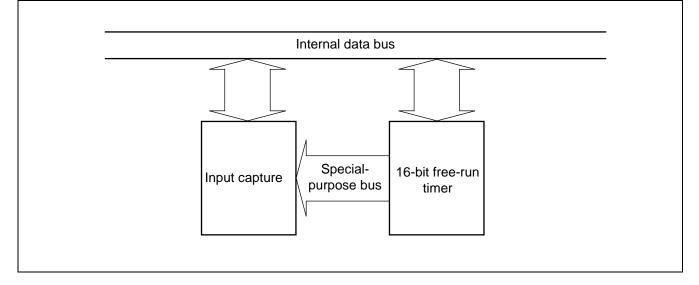

## 12.4 16-bit Input/Output Timer

The 16-bit input/output timer is a compound module composed of 16-bit free-run timer, (1 unit) and input capture (2 units, 4 input pins). The timer, using the 16-bit free-run timer as a basis, enables measurement of clock cycle of an input signal and its pulse width.

## Configuration of 16-bit Input/Output Timer

The 16-bit input/output timer is composed of the following modules:

- 16-bit free-run timer (1 unit)

- Input capture (2 units, 2 input pins per unit)

#### Functions of 16-bit Input/Output Timer

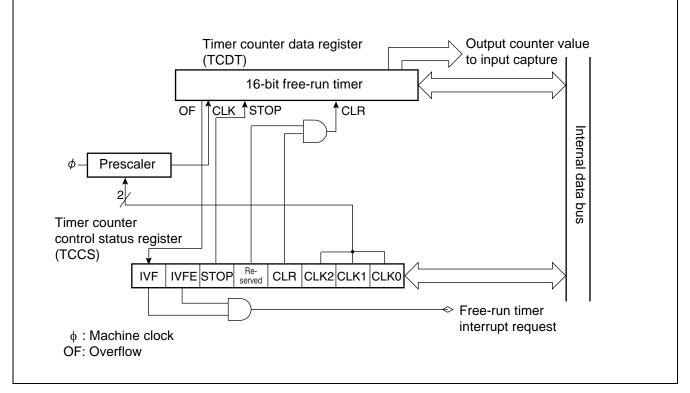

#### Functions of 16-bit Free-run Timer

The 16-bit free-run timer is composed of 16-bit up counter, timer counter control status register, and prescaler. The 16-bit up counter increments in synchronization with dividing ratio of machine clock.

- Count clock is set among four types of machine clock dividing rates.

- Generation of interrupt is allowed by counter value overflow.

- Activation of expanded intelligent I/O service (EI<sup>2</sup>OS) is allowed by interrupt generation.

- Counter value of 16-bit free-run timer is cleared to "0000<sup>H</sup>" by either resetting or software-clearing with timer count clear bit (TCCS: CLR).

- Counter value of 16-bit free-run timer is output to input capture, which is available as base time for capture operation.

#### Functions of Input Capture

The input capture, upon detecting an edge of a signal input to the input pin from external device, stores a counter value of 16-bit freerun timer at the time of detection into the input capture data register. The function includes the input capture data registers corresponding to four input pins, input capture control status register, and edge detection circuit.

- Rising edge, falling edge, and both edges are selectable for detection.

- Generating interrupt on CPU is allowed by detecting an edge of input signal.

- Expanded intelligent I/O service (EI<sup>2</sup>OS) is activated by interrupt generation.

- The four input capture input pins and input capture data registers allows monitoring of a maximum of four events.

#### 16-bit Input/Output Timer Block Diagram

## 16-bit Free-run Timer

Counter value of 16-bit free-run timer is used as reference time (base time) of input capture.

## Input Capture

Input capture detects rising edge, falling edge or both edges and retains a counter value of 16-bit free-run timer. Detection of edge on input signal is allowed to generate interrupt.

## 16-bit Free-run Timer Block Diagram

## **Detailed Pin Assignment on Block Diagram**

The 16-bit input/output timer includes a 16-bit free-run timer. Interrupt request number of the 16-bit free-run timer is as follows: Interrupt request number: 19 (13<sub>H</sub>)

## Prescaler

The prescaler divides a machine clock and provides a counter clock to the 16-bit up counter. Dividing ratio of the machine clock is specified by timer counter control status register (TCCS) among four values.

## Timer Counter Data Register (TCDT)

The timer counter data register is a 16-bit up counter. A current counter value of the 16-bit free-run timer is read. Writing a value during halt of the counter allows setting an arbitrary counter value.

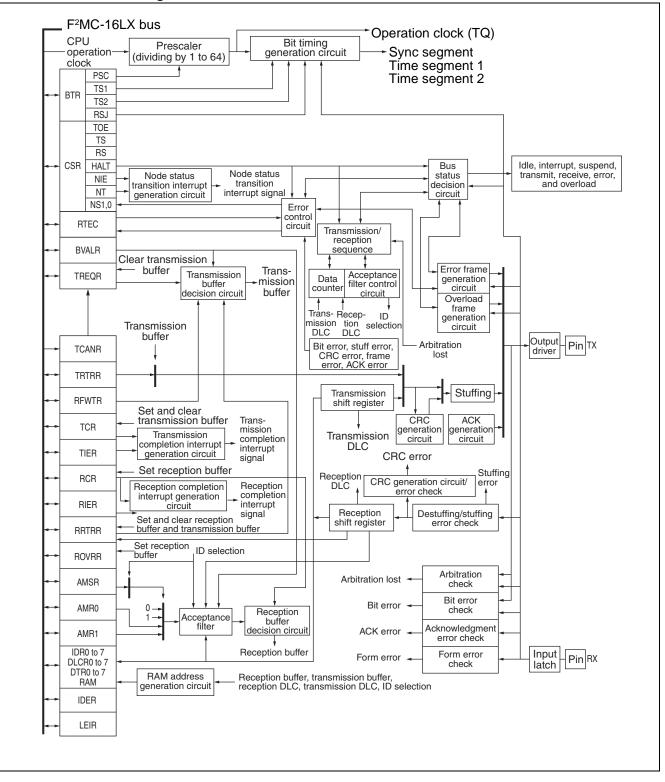

## 12.12 CAN Controller

The Controller Area Network (CAN) is a serial communication protocol compliant with CANVer2.0A and Ver2.0B. The protocol allows data transmission and reception in both standard frame format and expanded frame format.

## Features of CAN Controller

- CAN controller format is compliant with CANVer2.0A and Ver2.0B.

- The protocol allows data transmission and reception in standard frame format and expanded frame format.

- Automatic transmission of data frame by remote frame reception is allowed.

- Baud rate ranges from 10 kbps to 1 Mbps (with 16-MHz machine clock).

#### Table 12-5. Data Transmission Baud Rate

| Machine Clock | Baud Rate (Max) |

|---------------|-----------------|

| 16 MHz        | 1 Mbps          |

| 12 MHz        | 1 Mbps          |

| 8 MHz         | 1 Mbps          |

| 4 MHz         | 500 kbps        |

| 2 MHz         | 250 kbps        |

- Provided with 8 transmission/reception message buffers.

- Transmission/reception is allowed at ID 11 bit in standard format, and at ID 29 bit in expanded frame format.

- Specifying 0 byte to 8 bytes is allowed in message data.

- Multi-level message buffer configuration is allowed.

- CAN controller has two built-in acceptance masks. Mask settings are independently allowed for the two acceptance masks on reception IDs.

- The two acceptance masks allow reception in standard frame format and expanded frame format.

- For types of masking, all-bit comparison, all-bit masking, and partial masking with acceptance mask register 0/1, are specifiable.

#### **CAN Controller Block Diagram**

## 12.14 ROM Mirror Function Selection Module Outline

The ROM mirror function selection module sets the data in ROM assigned to FF bank so that the data is read by access to 00 bank.

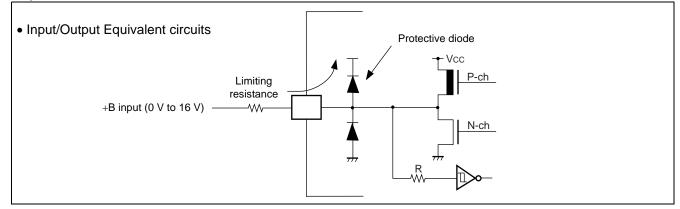

## FF Bank Access by ROM Mirror Function

- Use within recommended operating conditions.

- Use at DC voltage (current).

- The +B signal should always be applied a limiting resistance placed between the +B signal and the microcontroller.

- The value of the limiting resistance should be set so that when the +B signal is applied the input current to the microcontroller pin does not exceed rated values, either instantaneously or for prolonged periods.

- Note that when the microcontroller drive current is low, such as in the power saving modes, the +B input potential may pass through the protective diode and increase the potential at the Vcc pin, and this may affect other devices.

- Note that if a +B signal is input when the microcontroller power supply is off (not fixed at 0 V), the power supply is provided from the pins, so that incomplete operation may result.

- Note that if the +B input is applied during power-on, the power supply is provided from the pins and the resulting supply voltage may not be sufficient to operate the power-on reset.

- Care must be taken not to leave the +B input pin open.

- Note that analog system input/output pins other than the A/D input pins (LCD drive pins, comparator input pins, etc.) cannot accept +B signal input.

- Sample recommended circuits:

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

| Deremeter                   | Symbol | Pin Name                                      | Conditions                                                                                                  |     | Value | Unit | Remarks |                                                                 |

|-----------------------------|--------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----|-------|------|---------|-----------------------------------------------------------------|

| Parameter                   | Symbol | Pin Name                                      | Conditions                                                                                                  | Min | Тур   | Max  | Unit    | Remarks                                                         |

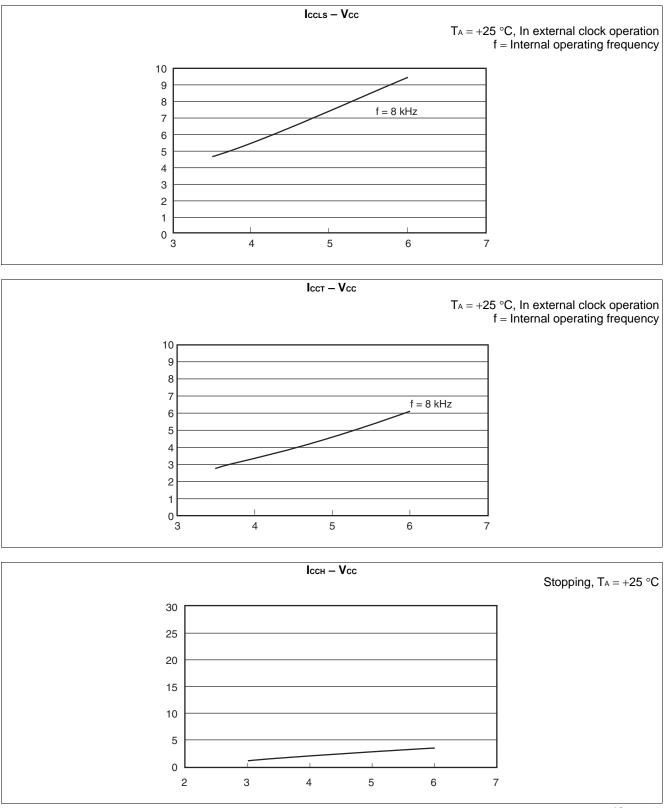

| Power<br>supply<br>current* | lcc∟   | Vcc                                           | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>subclock operation,                                       |     | 0.3   | 1.2  | mA      | MB90F387/S                                                      |

| 000                         |        |                                               | $T_A = +25^{\circ}C$                                                                                        |     | 40    | 100  | μΑ      | MB90387/S                                                       |

|                             | ICCLS  |                                               | $V_{CC} = 5.0 V$ ,<br>Internally operating at 8 kHz,<br>subclock,<br>sleep mode,<br>$T_{A} = + 25^{\circ}C$ | _   | 10    | 30   | μA      |                                                                 |

|                             | Ісст   |                                               | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>watch mode,<br>$T_A = + 25^{\circ}C$                      |     | 8     | 25   | μΑ      |                                                                 |

|                             | Іссн   |                                               | Stopping,<br>T <sub>A</sub> = + 25°C                                                                        | _   | 5     | 20   | μΑ      |                                                                 |

| Input<br>capacity           | CIN    | Other than AVcc,<br>AVss, AVR, C, Vcc,<br>Vss | -                                                                                                           | _   | 5     | 15   | pF      |                                                                 |

| Pull-up<br>resistor         | Rup    | RST                                           | -                                                                                                           | 25  | 50    | 100  | kΩ      |                                                                 |

| Pull-down<br>resistor       | Rdown  | MD2                                           | -                                                                                                           | 25  | 50    | 100  | kΩ      | Flash product is<br>not provided<br>with pull-down<br>resistor. |

$(Vcc = 5.0 V \pm 10\%, Vss = AVss = 0.0 V, T_A = -40 \circ C to +105 \circ C)$

\*: Test conditions of power supply current are based on a device using external clock.

## 13.4.4 UART Timing

| Parameter                                      | Symbol Pin Name |               | Conditions                              | Value   |     | Unit | Remarks |

|------------------------------------------------|-----------------|---------------|-----------------------------------------|---------|-----|------|---------|

| Falameter                                      |                 |               | Conditions                              | Min     | Max | Unit | Remarks |

| Serial clock cycle time                        | tscyc           | SCK1          | Internal shift clock                    | 4 tcp * | -   | ns   |         |

| $SCK \downarrow \to SOT$ delay time            | <b>t</b> slov   | SCK1,<br>SOT1 | mode output pin is: CL<br>= 80 pF+1TTL. | -80     | +80 | ns   |         |

| Valid SIN $\rightarrow$ SCK $\uparrow$         | <b>t</b> ivsh   | SCK1, SIN1    |                                         | 100     | -   | ns   |         |

| SCK $\uparrow \rightarrow$ valid SIN hold time | <b>t</b> shix   | SCK1, SIN1    |                                         | 60      | -   | ns   |         |

| Serial clock "H" pulse width                   | <b>t</b> shsl   | SCK1          | External shift clock                    | 2 tcp * | -   | ns   |         |

| Serial clock "L" pulse width                   | tslsh           | SCK1          | mode output pin is: CL<br>= 80 pF+1TTL. | 2 tcp * | -   | ns   |         |

| $SCK \downarrow \to SOT$ delay time            | tslov           | SCK1,<br>SOT1 | – 00 pr +111L.                          | -       | 150 | ns   |         |

| Valid SIN $\rightarrow$ SCK $\uparrow$         | <b>t</b> ivsh   | SCK1, SIN1    |                                         | 60      | -   | ns   |         |

| SCK $\uparrow \rightarrow$ valid SIN hold time | tsнix           | SCK1, SIN1    |                                         | 60      | _   | ns   |         |

## (Vcc = 4.5 V to 5.5 V, Vss = 0.0 V, T\_A = -40 °C to +105 °C)

\*: Refer to Clock Timing ratings for  $t_{\mbox{\tiny CP}}$  (internal operation clock cycle time).

Notes:

■ AC Characteristics in CLK synchronous mode.

$\blacksquare$  C<sub>L</sub> is a load capacitance value on pins for testing.

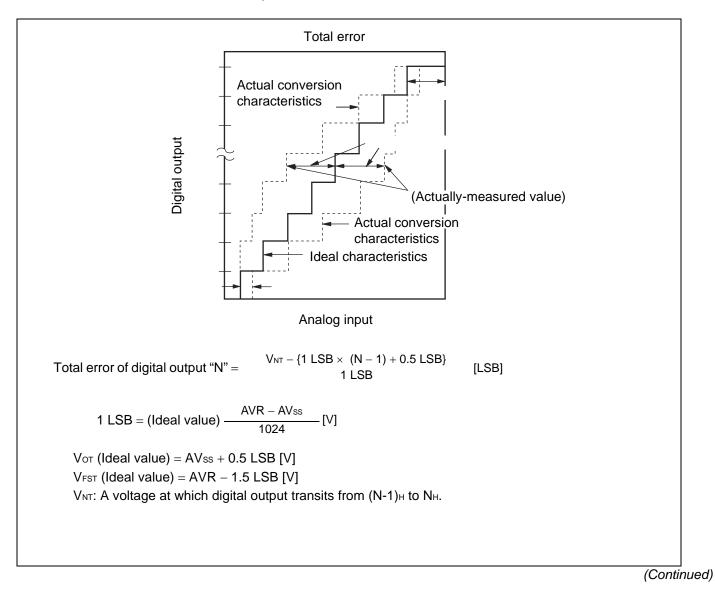

## **13.6 Definition of A/D Converter Terms**

| Resolution:                | Analog variation that is recognized by an A/D converter.                                                                                                                                                                                       |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Linear error:              | Deviation between a line across zero-transition line ("00 0000 00 0" $\leftarrow \rightarrow$ "00 0000 0001") and full-scale transition line ("11 1111 11 1 0" $\leftarrow \rightarrow$ "11 1111 1111") and actual conversion characteristics. |

| Differential linear error: | Deviation of input voltage, which is required for changing output code by 1 LSB, from an ideal value.                                                                                                                                          |

| Total error:               | Difference between an actual value and an ideal value. A total error includes zero transition error, full-<br>scale transition error, and linear error.                                                                                        |

## (Continued)