Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                        |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | CANbus, SCI, UART/USART                                                       |

| Peripherals                | POR, WDT                                                                      |

| Number of I/O              | 36                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | Mask ROM                                                                      |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x8/10b                                                                   |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-LQFP                                                                       |

| Supplier Device Package    | 48-LQFP (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-gs-138 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16-bit Microcontrollers F<sup>2</sup>MC-16LX MB90385 Series

MB90385 series devices are general-purpose high-performance 16-bit micro controllers designed for process control of consumer products, which require high-speed real-time processing. The devices of this series have the built-in full-CAN interface.

The system, inheriting the architecture of F<sup>2</sup>MC family, employs additional instruction ready for high-level languages, expanded addressing mode, enhanced multiply-divide instructions, and enriched bit-processing instructions. Furthermore, employment of 32-bit accumulator achieves processing of long-word data (32 bits).

The peripheral resources of MB90385 series include the following:

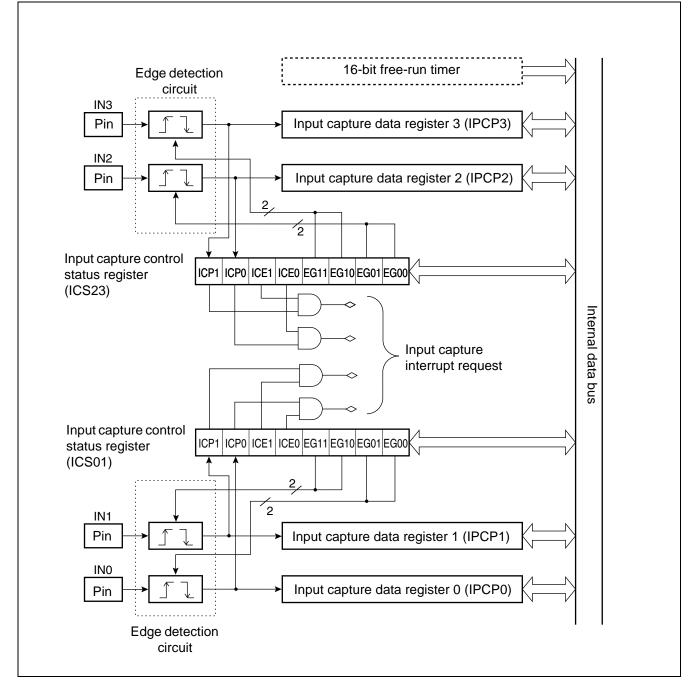

8/10-bit A/D converter, UART (SCI), 8/16-bit PPG timer, 16-bit input-output timer (16-bit free-run timer, input capture 0, 1, 2, 3 (ICU)), and CAN controller.

### Features

### Clock

- Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 4 times of oscillation clock (for 4-MHz oscillation clock, 4 MHz to 16 MHz).

- Operation by sub-clock (8.192 kHz) is allowed. (MB90387, MB90F387)

- Minimum execution time of instruction: 62.5 ns (when operating with 4-MHz oscillation clock, and 4-time multiplied PLL clock).

### 16 Mbyte CPU memory Space

24-bit internal addressing

### Instruction System Best Suited to Controller

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions and RETI instructions

- Enhanced high-precision computing with 32-bit accumulator

# Instruction System Compatible with High-level Language (C language) and Multitask

- Employing system stack pointer

- Enhanced various pointer indirect instructions

- Barrel shift instructions

### **Increased Processing Speed**

4-byte instruction queue

# Powerful Interrupt Function with 8 Levels and 34 Factors

### Automatic Data Transfer Function Independent of CPU

Expanded intelligent I/O service function (EI<sup>2</sup> OS): Maximum of 16 channels

### Low Power Consumption (standby) Mode

■ Sleep mode (a mode that halts CPU operating clock)

- Time-base timer mode (a mode that operates oscillation clock, sub clock, time-base timer and watch timer only)

- Watch mode (a mode that operates sub clock and watch timer only)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU blocking operation mode

### Process

CMOS technology

### I/O Port

General-purpose input/output port (CMOS output):

MB90387, MB90F387: 34 ports (including 4 high-current output ports) MB90387S, MB90F387S: 36 ports (including 4 high-current output ports)

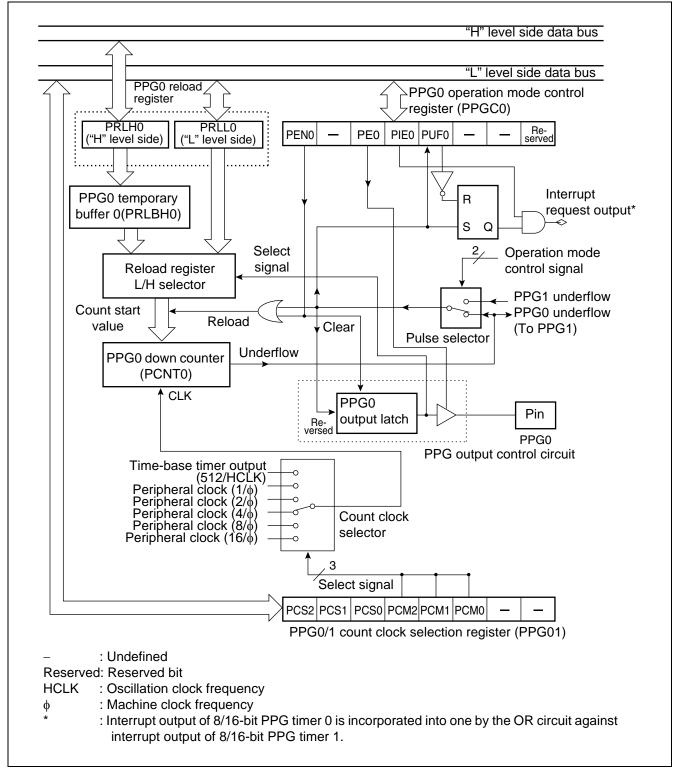

### Timer

- Time-base timer, watch timer, watchdog timer: 1 channel

- 8/16-bit PPG timer: 8-bit x 4 channels, or 16-bit x 2 channels

- 16-bit reload timer: 2 channels

- 16-bit input/output timer

- 16-bit free run timer: 1 channel

- □ 16-bit input capture: (ICU): 4 channels

Interrupt request is issued upon latching a count value of 16bit free run timer by detection of an edge on pin input.

### CAN Controller: 1 channel

- Compliant with Ver2.0A and Ver2.0B CAN specifications

- 8 built-in message buffers

- Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)

- CAN wake-up

**198 Champion Court**

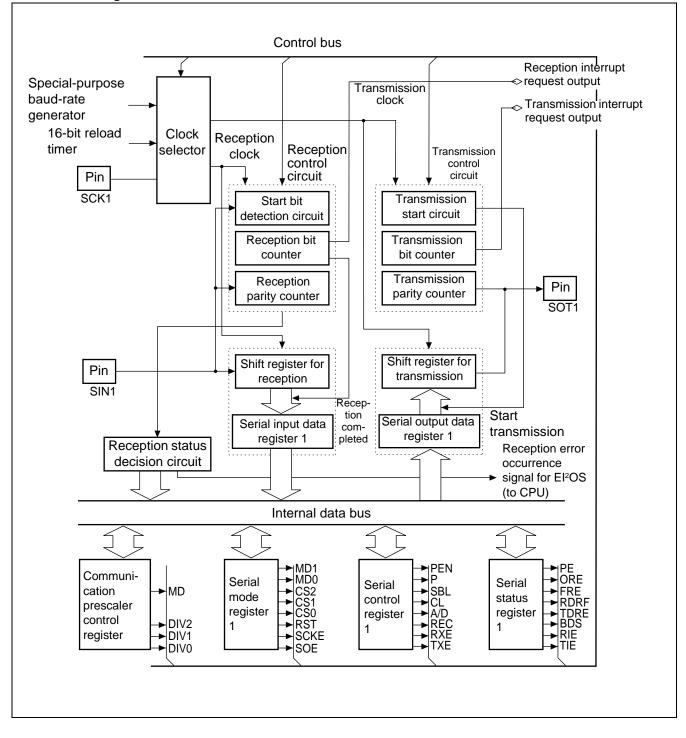

### UART (SCI): 1 channel

- Equipped with full-duplex double buffer

- Clock-asynchronous or clock-synchronous serial transmission is available.

### Cypress Semiconductor Corporation

Document Number: 002-07765 Rev. \*A

San Jose, CA 95134-1709

408-943-2600

Revised February 5, 2018

# DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

Module for activation of expanded intelligent I/O service (EI<sup>2</sup>OS), and generation of external interrupt.

### **Delay Interrupt Generator Module**

Generates interrupt request for task switching.

### 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 μs (at 16 MHz machine clock, including sampling time)

### **Program Patch Function**

■ Address matching detection for 2 address pointers.

### 7. Handling Devices

### Do Not Exceed Maximum Rating (preventing "latch up")

- On a CMOS IC, latch-up may occur when applying a voltage higher than Vcc or a voltage lower than Vss to input or output pin, which has no middle or high withstand voltage. Latch-up may also occur when a voltage exceeding maximum rating is applied across Vcc pin and Vss pin.

- Latch-up causes drastic increase of power current, which may lead to destruction of elements by heat. Extreme caution must be taken not to exceed maximum rating.

- When turning on and off analog power source, take extra care not to apply an analog power voltages (AVcc and AVR) and analog input voltage that are higher than digital power voltage (Vcc).

### Handling Unused Pins

Leaving unused input pins open may cause permanent destruction by malfunction or latch-up. Apply pull-up or pull-down process to the unused pins using resistors of 2 kΩ or higher. Leave unused input/output pins open under output status, or process as input pins if they are under input status.

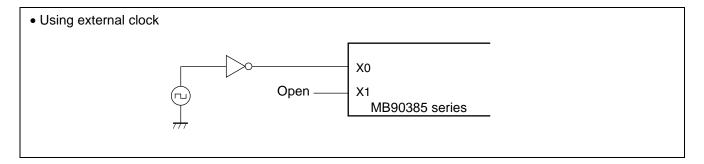

### **Using External Clock**

■ When using an external clock, drive only X0 pin and leave X1 pin open. An example of using an external clock is shown below.

| Address                  | Register<br>Abbreviation | Register                                  | Read/<br>Write | Resource                                      | Initial Value         |

|--------------------------|--------------------------|-------------------------------------------|----------------|-----------------------------------------------|-----------------------|

| 000038н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| to<br>00003Fн            |                          |                                           |                |                                               |                       |

| 000040н                  | PPGC0                    | PPG0 operation mode control register      | R/W, W         | 8/16-bit PPG timer 0/                         | 0Х000ХХ1в             |

| 000041н                  | PPGC1                    | PPG1 operation mode control register      | 0Х00001в       |                                               |                       |

| 000042н                  | PPG01                    | PPG0/1 count clock selection register     | R/W            |                                               | 000000XXB             |

| 000043н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000044н                  | PPGC2                    | PPG2 operation mode control register      | R/W, W         | 8/16-bit PPG timer 2/                         | 0X000XX1в             |

| 000045н                  | PPGC3                    | PPG3 operation mode control register      | R/W, W         | 3                                             | 0Х00001в              |

| 000046н                  | PPG23                    | PPG2/3 count clock selection register     | R/W            | 1 [                                           | 00000XXв              |

| 000047н to<br>00004Fн    |                          | (Reserve                                  | ed area) *     | · ·                                           |                       |

| 000050н                  | IPCP0                    | Input capture data register 0             | R              | 16-bit input/output                           | XXXXXXXXB             |

| 000051н                  |                          |                                           |                | timer                                         | XXXXXXXXB             |

| 000052н                  | IPCP1                    | Input capture data register 1             | R              | 1 [                                           | XXXXXXXXB             |

| 000053н                  |                          |                                           |                |                                               | XXXXXXXXB             |

| 000054н                  | ICS01                    | Input capture control status register     | R/W            | 1 [                                           | 0000000в              |

| 000055н                  | ICS23                    |                                           |                |                                               | 0000000в              |

| 000056н                  | TCDT                     | Timer counter data register               | R/W            | 1 [                                           | 0000000в              |

| 000057н                  |                          |                                           |                |                                               | 0000000в              |

| 000058н                  | TCCS                     | Timer counter control status register     | R/W            | 1 [                                           | 0000000в              |

| 000059н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 00005Ан                  | IPCP2                    | Input capture data register 2             | R              | 16-bit input/output                           | XXXXXXXXB             |

| 00005Вн                  |                          |                                           |                | timer                                         | XXXXXXXXB             |

| 00005Сн                  | IPCP3                    | Input capture data register 3             | R              | 1 [                                           | XXXXXXXXB             |

| 00005Dн                  |                          |                                           |                |                                               | XXXXXXXXB             |

| 00005Eнto<br>000065н     |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000066н                  | TMCSR0                   | Timer control status register             | R/W            | 16-bit reload timer 0                         | 0000000в              |

| 000067н                  |                          |                                           | R/W            |                                               | XXXX0000 <sub>B</sub> |

| 000068н                  | TMCSR1                   |                                           | R/W            | 16-bit reload timer 1                         | 0000000в              |

| 000069н                  |                          |                                           | R/W            | ] Γ                                           | XXXX0000b             |

| 00006Анto<br>00006Ен     |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 00006Fн                  | ROMM                     | ROM mirroring function selection register | W              | ROM mirroring<br>function selection<br>module | XXXXXXX1B             |

| 000070н<br>to<br>00007Fн |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000080н                  | BVALR                    | Message buffer enabling register          | R/W            | CAN controller                                | 0000000в              |

| 000081н                  |                          |                                           | ed area) *     |                                               |                       |

| 000082н                  | TREQR                    | Send request register                     | R/W            | CAN controller                                | 0000000в              |

| Address                  | Register<br>Abbreviation | Register               | Read/<br>Write    | Resource                     | Initial Value                 |

|--------------------------|--------------------------|------------------------|-------------------|------------------------------|-------------------------------|

| 003910н                  | PRLL0                    | PPG0 reload register L | R/W               | 8/16-bit PPG timer           | XXXXXXXXB                     |

| <b>003911</b> н          | PRLH0                    | PPG0 reload register H | R/W               |                              | XXXXXXXXB                     |

| 003912н                  | PRLL1                    | PPG1 reload register L | R/W               |                              | XXXXXXXXB                     |

| 003913н                  | PRLH1                    | PPG1 reload register H |                   | XXXXXXXXB                    |                               |

| 003914н                  | PRLL2                    | PPG2 reload register L | R/W               |                              | XXXXXXXXB                     |

| <b>003915</b> н          | PRLH2                    | PPG2 reload register H | R/W               |                              | XXXXXXXXB                     |

| <b>003916</b> н          | PRLL3                    | PPG3 reload register L | R/W               |                              | XXXXXXXX <sub>B</sub>         |

| <b>003917</b> н          | PRLH3                    | PPG3 reload register H | R/W               |                              | XXXXXXXXB                     |

| 003918н<br>to<br>00392Fн |                          |                        | (Reserved area) * |                              |                               |

| 003930н<br>to<br>003BFFн |                          |                        | (Reserved area) * |                              |                               |

| 003C00н<br>to<br>003C0Fн |                          | RAM (                  | General-purpose R | AM)                          |                               |

| 003C10н<br>to<br>003C13н | IDR0                     | ID register 0          | R/W               | CAN controller               | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C14н<br>to<br>003C17н | IDR1                     | ID register 1          | -                 | XXXXXXXXB<br>to<br>XXXXXXXXB |                               |

| 003C18н<br>to<br>003C1Bн | IDR2                     | ID register 2          | D register 2 R/W  |                              | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C1Cн<br>to<br>003C1Fн | IDR3                     | ID register 3          | R/W               | _                            | XXXXXXXXB<br>to<br>XXXXXXXXB  |

| 003C20н<br>to<br>003C23н | IDR4                     | ID register 4          | R/W               | _                            | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C24н<br>to<br>003C27н | IDR5                     | ID register 5          | R/W               | _                            | XXXXXXXXAB<br>to<br>XXXXXXXXB |

| 003C28н<br>to<br>003C2Bн | IDR6                     | ID register 6          | R/W               | -                            | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C2Cн<br>to<br>003C2Fн | IDR7                     | ID register 7          | D register 7 R/W  |                              | XXXXXXXXB<br>to<br>XXXXXXXB   |

| 003C30н,<br>003C31н      | DLCR0                    | DLC register 0         | R/W               |                              | XXXXXXXXB,<br>XXXXXXXB        |

| 003C32н,<br>003C33н      | DLCR1                    | DLC register 1         | R/W               |                              | XXXXXXXXB,<br>XXXXXXXB        |

| 003C34н,<br>003C35н      | DLCR2                    | DLC register 2         | R/W               |                              | XXXXXXXXB,<br>XXXXXXXXB       |

| 003C36н,<br>003C37н      | DLCR3                    | DLC register 3         | R/W               |                              | XXXXXXXXB,<br>XXXXXXXXB       |

| Interrupt Source                  | El <sup>2</sup> OS | l      | nterrup | ot Vector | Interrupt C | Priority*3             |              |

|-----------------------------------|--------------------|--------|---------|-----------|-------------|------------------------|--------------|

| interrupt Source                  | Readiness          | Number |         | Address   | ICR         | Address                | FIOTILY      |

| UART1 reception completed         | O                  | #37    | 25н     | FFFF68H   | ICR13       | 0000BDH*1              | High         |

| UART1 transmission completed      | Δ                  | #38    | 26н     | FFFF64⊦   |             |                        | $\uparrow$   |

| Reserved                          | ×                  | #39    | 27н     | FFFF60H   | ICR14       | 0000BEH*1              |              |

| Reserved                          | ×                  | #40    | 28н     | FFFF5CH   |             |                        |              |

| Flash memory                      | ×                  | #41    | 29н     | FFFF58H   | ICR15       | 0000BF <sub>H</sub> *1 | $\downarrow$ |

| Delay interrupt generation module | ×                  | #42    | 2Ан     | FFFF54⊦   | <u> </u>    |                        | Low          |

○ : Available

× : Unavailable

© : Available El<sup>2</sup>OS function is provided.

$\Delta$ : Available when a cause of interrupt sharing a same ICR is not used.

\*1:

□ Peripheral functions sharing an ICR register have the same interrupt level.

□ If peripheral functions share an ICR register, only one function is available when using expanded intelligent I/O service.

If peripheral functions share an ICR register, a function using expanded intelligent I/O service does not allow interrupt by another function.

\*2: Input capture 1 corresponds to EI2OS, however, PPG does not. When using EI2OS by input capture 1, interrupt should be disabled for PPG.

\*3:Priority when two or more interrupts of a same level occur simultaneously.

### 12. Peripheral Resources

### 12.1 I/O Ports

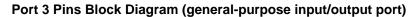

The I/O ports are used as general-purpose input/output ports (parallel I/O ports). The MB60385 series model is provided with 5 ports (34 inputs). The ports function as input/output pins for peripheral functions also.

### I/O Port Functions

An I/O port, using port data resister (PDR), outputs the output data to I/O pin and input a signal input to I/O port. The port direction register (DDR) specifies direction of input/output of I/O pins on a bit-by-bit basis.

The following summarizes functions of the ports and sharing peripheral functions:

- Port 1: General-purpose input/output port, used also for PPG timer output and input capture inputs.

- Port 2: General-purpose input/output port, used also for reload timer input/output and external interrupt input.

- Port 3: General-purpose input/output port, used also for A/D converter activation trigger pin.

- Port 4: General-purpose input/output port, used also for UART input/output and CAN controller send/receive pin.

- Port 5: General-purpose input/output port, used also analog input pin.

### **Port 3 Registers**

- Port 3 registers include port 3 data register (PDR3) and port 3 direction register (DDR3).

- The bits configuring the register correspond to port 3 pins on a one-to-one basis.

### **Relation between Port 3 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 3    | PDR3, DDR3                              | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P37  | P36* | P35* | _    | P33  | P32  | P31  | P30  |

\*: P35 and P36 do not exist on MB90387and MB90F387.

### Input Capture Block Diagram

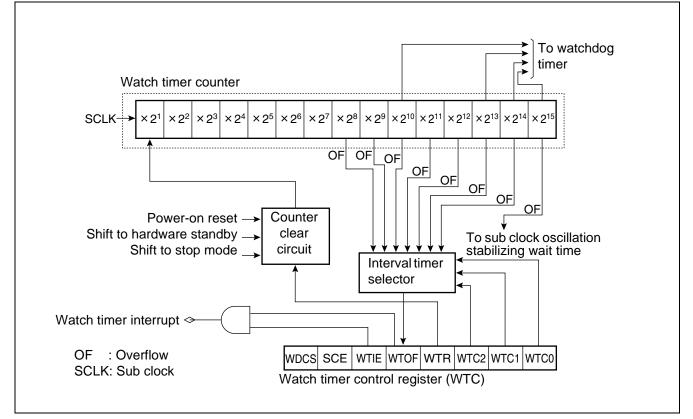

### 12.6 Watch Timer Outline

The watch timer is a 15-bit free-run counter that increments in synchronization with sub clock.

- Interval time is selectable among 7 choices, and generation of interrupt request is allowed for each interval.

- Provides operation clock to the subclock oscillation stabilizing wait timer and watchdog timer.

- Always uses subclock as a count clock regardless of settings of clock selection register (CKSCR).

### **Interval Timer Function**

- In the watch timer, a bit corresponding to the interval time overflows (carry-over) when an interval time, which is specified by interval time selection bit, is reached. Then overflow flag bit is set (WTC: WTOF=1).

- If an interrupt by overflow is permitted (WTC: WTIE=1), an interrupt request is generated upon setting an overflow flag bit.

- Interval time of watch timer is selectable among the following seven choices:

### Interval Time of Watch Timer

| Sub Clock Cycle | Interval Time                   |

|-----------------|---------------------------------|

| 1/SCLK (122 μs) | 2 <sup>8</sup> /SCLK (31.25 ms) |

|                 | 2º/SCLK (62.5 ms)               |

|                 | 2 <sup>10</sup> /SCLK (125 ms)  |

|                 | 2 <sup>11</sup> /SCLK (250 ms)  |

|                 | 2 <sup>12</sup> /SCLK (500 ms)  |

|                 | 2 <sup>13</sup> /SCLK (1.0 s)   |

|                 | 2 <sup>14</sup> /SCLK (2.0 s)   |

### SCLK: Sub clock frequency

Values in parentheses "()" are calculation when operating with 8.192 kHz clock.

### Watch Timer Block Diagram

Actual interrupt request number of watch timer is as follows: Interrupt request number: #28 (1C<sub>H</sub>)

### Watch Timer Counter

A 15-bit up counter that uses sub clock (SCLK) as a count clock.

### **Counter Clear Circuit**

A circuit that clears the watch timer counter.

### 8/16-bit PPG Timer 0 Block Diagram

### 12.9 DTP/External Interrupt and CAN Wakeup Outline

DTP/external interrupt transfers an interrupt request generated by an external peripheral device or a data transmission request to CPU, generating external interrupt request and activating expanded intelligent I/O service. Input RX of CAN controller is used as external interrupt input.

### **DTP/External Interrupt and CAN Wakeup Function**

An interrupt request input from external peripheral device to external input pins (INT7 to INT4) and RX pin, just as interrupt request of peripheral device, generates an interrupt request. The interrupt request generates an external interrupt and activates expanded intelligent I/O service (EI<sup>2</sup>OS).

If the expanded intelligent I/O service (EI<sup>2</sup>OS) has been disabled by interrupt control register (ICR: ISE=0), external interrupt function is enabled and branches to interrupt processing.

If the EI<sup>2</sup>OS has been enabled, (ICR: ISE=1), DTP function is enabled and automatic data transmission is performed by EI<sup>2</sup>OS. After performing specified number of data transmission processes, the process branches to interrupt processing.

|                   | External Interrupt                                                     | DTP Function                                                                                                        |  |  |  |  |  |  |

|-------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Input pin         | 5 pins (RX, and INT4 to INT7)                                          |                                                                                                                     |  |  |  |  |  |  |

| Interrupt cause   | use Specify for each pin with detection level setting register (ELVR). |                                                                                                                     |  |  |  |  |  |  |

|                   | Input of "H" level/"L" level/rising edge/falling edge.                 | Input of "H" level/ "L" level                                                                                       |  |  |  |  |  |  |

| Interrupt number  | #15 (0Fн), #24 (18н), #27 (1Вн)                                        |                                                                                                                     |  |  |  |  |  |  |

| Interrupt control | Enabling or disabling output of interrupt request, (ENIR).             | using DTP/external interrupt permission register                                                                    |  |  |  |  |  |  |

| Interrupt flag    | Retaining interrupt cause with DTP/external inter                      | rrupt cause register (EIRR).                                                                                        |  |  |  |  |  |  |

| Process selection | Disable El <sup>2</sup> OS (ICR: ISE=0)                                | Enable El <sup>2</sup> OS (ICR: ISE=1)                                                                              |  |  |  |  |  |  |

| Process           | Branch to external interrupt process                                   | After automatic data transmission by El <sup>2</sup> OS for specified number of times, branch to interrupt process. |  |  |  |  |  |  |

| Table 12-2. | DTP/External In | terrupt and CAN | Wakeup Outline |

|-------------|-----------------|-----------------|----------------|

|-------------|-----------------|-----------------|----------------|

### **UART Block Diagram**

### 12.12 CAN Controller

The Controller Area Network (CAN) is a serial communication protocol compliant with CANVer2.0A and Ver2.0B. The protocol allows data transmission and reception in both standard frame format and expanded frame format.

### Features of CAN Controller

- CAN controller format is compliant with CANVer2.0A and Ver2.0B.

- The protocol allows data transmission and reception in standard frame format and expanded frame format.

- Automatic transmission of data frame by remote frame reception is allowed.

- Baud rate ranges from 10 kbps to 1 Mbps (with 16-MHz machine clock).

### Table 12-5. Data Transmission Baud Rate

| Machine Clock | Baud Rate (Max) |

|---------------|-----------------|

| 16 MHz        | 1 Mbps          |

| 12 MHz        | 1 Mbps          |

| 8 MHz         | 1 Mbps          |

| 4 MHz         | 500 kbps        |

| 2 MHz         | 250 kbps        |

- Provided with 8 transmission/reception message buffers.

- Transmission/reception is allowed at ID 11 bit in standard format, and at ID 29 bit in expanded frame format.

- Specifying 0 byte to 8 bytes is allowed in message data.

- Multi-level message buffer configuration is allowed.

- CAN controller has two built-in acceptance masks. Mask settings are independently allowed for the two acceptance masks on reception IDs.

- The two acceptance masks allow reception in standard frame format and expanded frame format.

- For types of masking, all-bit comparison, all-bit masking, and partial masking with acceptance mask register 0/1, are specifiable.

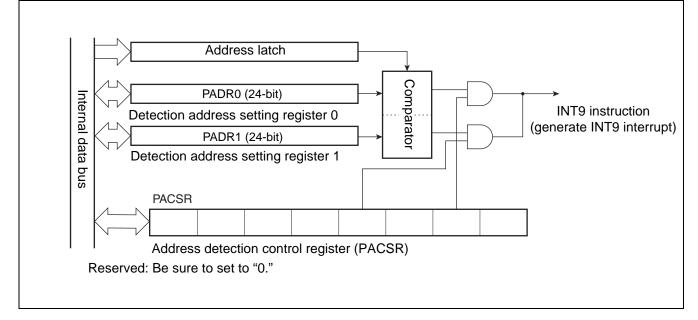

### 12.13 Address Matching Detection Function Outline

The address matching detection function checks if an address of an instruction to be processed next to a currently-processed instruction is identical with an address specified in the detection address register. If the addresses match with each other, an instruction to be processed next in program is forcibly replaced with INT9 instruction, and process branches to the interrupt process program. Using INT9 interrupt, this function is available for correcting program by batch processing.

### Address Matching Detection Function Outline

- An address of an instruction to be processed next to a currently-processed instruction of the program is always retained in an address latch via internal data bus. By the address matching detection function, the address value retained in the address latch is always compared with an address specified in detection address setting register. If the compared address values match with each other, an instruction to be processed next by CPU is forcibly replaced with INT9 instruction, and an interrupt process program is executed.

- Two detection address setting registers are provided (PADR0 and PADR1), and each register is provided with interrupt permission bit. Generation of interrupt, which is caused by address matching between the address retained in address latch and the address specified in address setting register, is permitted and prohibited on a register-by-register basis.

### Address Matching Detection Function Block Diagram

Address latch

Retains address value output to internal data bus.

- Address detection control register (PACSR) Specifies if interrupt is permitted or prohibited when addresses match with each other.

- Detection address setting (PADR0, PADR1) Specifies addresses to be compared with values in address latch.

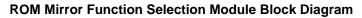

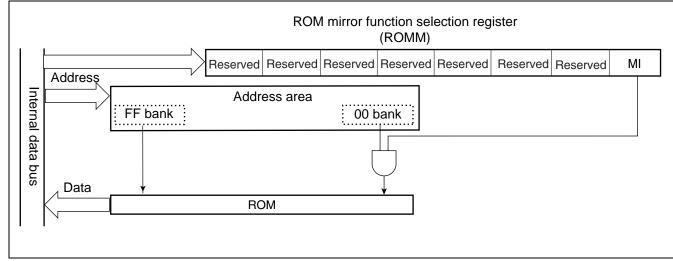

### 12.14 ROM Mirror Function Selection Module Outline

The ROM mirror function selection module sets the data in ROM assigned to FF bank so that the data is read by access to 00 bank.

### FF Bank Access by ROM Mirror Function

## **13. Electrical Characteristics**

### 13.1 Absolute Maximum Rating

| Parameter                              | Symbol          | Rat       | ting      | Unit | Remarks               |

|----------------------------------------|-----------------|-----------|-----------|------|-----------------------|

| Parameter                              | Symbol          | Min       | Max       | Unit | Remarks               |

| Power supply voltage*1                 | Vcc             | Vss - 0.3 | Vss + 6.0 | V    |                       |

|                                        | AVcc            | Vss - 0.3 | Vss + 6.0 | V    | Vcc = AVcc*2          |

|                                        | AVR             | Vss - 0.3 | Vss + 6.0 | V    | $AVcc \ge AVR^{*2}$   |

| Input voltage*1                        | Vi              | Vss - 0.3 | Vss + 6.0 | V    | *3                    |

| Output voltage*1                       | Vo              | Vss - 0.3 | Vss + 6.0 | V    | *3                    |

| Maximum clamp current                  |                 | - 2.0     | + 2.0     | mA   | *7                    |

| Total maximum clamp current            | Σ   Iclamp      | -         | 20        | mA   | *7                    |

| "L" level maximum output current       | IOL1            | -         | 15        | mA   | Normal output*4       |

|                                        | IOL2            | -         | 40        | mA   | High-current output*4 |

| "L" level average output current       | IOLAV1          | -         | 4         | mA   | Normal output*5       |

|                                        | IOLAV2          | -         | 30        | mA   | High-current output*5 |

| "L" level maximum total output current | Σlol1           | -         | 125       | mA   | Normal output         |

|                                        | ΣΙοι2           | -         | 160       | mA   | High-current output   |

| "L" level average total output current | $\Sigma$ lolav1 | -         | 40        | mA   | Normal output*6       |

|                                        | $\Sigma$ Iolav2 | -         | 40        | mA   | High-current output*6 |

| "H" level maximum output current       | Іон1            | -         | -15       | mA   | Normal output*4       |

|                                        | Іон2            | -         | -40       | mA   | High-current output*4 |

| "H" level average output current       | IOHAV1          | -         | -4        | mA   | Normal output*5       |

|                                        | IOHAV2          | -         | -30       | mA   | High-current output*5 |

| "H" level maximum total output current | ΣІон1           | -         | -125      | mA   | Normal output         |

|                                        | ΣІон2           | -         | -160      | mA   | High-current output   |

| "H" level average total output current | ΣΙομαν1         | -         | -40       | mA   | Normal output*6       |

|                                        | ΣΙομαν2         | -         | -40       | mA   | High-current output*6 |

| Power consumption                      | PD              | -         | 245       | mW   |                       |

| Operating temperature                  | TA              | -40       | +105      | °C   |                       |

| Storage temperature                    | Tstg            | -55       | +150      | °C   |                       |

\*1: The parameter is based on  $V_{SS} = AV_{SS} = 0.0 V$ .

\*2: AVcc and AVR should not exceed Vcc.

\*3: VI and Vo should not exceed Vcc + 0.3 V. However if the maximum current to/from an input is limited by some means with external components, the IcLAMP rating supersedes the VI rating.

\*4: A peak value of an applicable one pin is specified as a maximum output current.

- \*5: An average current value of an applicable one pin within 100 ms is specified as an average output current. (Average value is found by multiplying operating current by operating rate.)

- \*6: An average current value of all pins within 100 ms is specified as an average total output current. (Average value is found by multiplying operating current by operating rate.)

\*7:

Applicable to pins: P10 to P17, P20 to P27, P30 to P33, P35\*, P36\*, P37, P40 to P44, P50 to P57

\*: P35 and P36 are MB90387S and MB90F387S only.

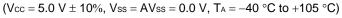

13.4.3 Power-on Reset

| Parameter                  | Symbol | Pin Name | Conditions | Va      | lue | Unit | Remarks                        |

|----------------------------|--------|----------|------------|---------|-----|------|--------------------------------|

| Farameter                  | Symbol |          | Conditions | Min Max |     | Onit | reliaiks                       |

| Power supply rise time     | tR     | Vcc      | -          | 0.05    | 30  | ms   |                                |

| Power supply shutdown time | toff   | Vcc      |            | 1       | -   | ms   | Waiting time until<br>power-on |

### 13.5 A/D Converter

| Deremeter                     | Cumple of | Din Norra     |                | Value             | l les it          | D    |                                                                             |

|-------------------------------|-----------|---------------|----------------|-------------------|-------------------|------|-----------------------------------------------------------------------------|

| Parameter                     | Symbol    | Pin Name      | Min            | Тур               | Max               | Unit | Remarks                                                                     |

| Resolution                    | -         | -             | _              | _                 | 10                | bit  |                                                                             |

| Total error                   | _         | _             | _              | _                 | ± 3.0             | LSB  |                                                                             |

| Nonlinear error               | -         | _             | _              | _                 | ± 2.5             | LSB  |                                                                             |

| Differential linear error     | -         | -             | _              | _                 | ± 1.9             | LSB  |                                                                             |

| Zero transition voltage       | Vот       | AN0 to<br>AN7 | AVss – 1.5 LSB | AVss + 0.5<br>LSB | AVss + 2.5<br>LSB | V    | 1 LSB = (AVR – AVss) /<br>1024                                              |

| Full-scale transition voltage | Vfst      | AN0 to<br>AN7 | AVR – 3.5 LSB  | AVR – 1.5<br>LSB  | AVR + 0.5<br>LSB  | V    |                                                                             |

| Compare time                  | -         | -             | 66 tcp *1      | _                 | _                 | ns   | With 16 MHz machine clock $5.5 \text{ V} \ge AV_{CC} \ge 4.5 \text{ V}$     |

|                               |           |               | 88 tcp *1      | _                 | _                 | ns   | With 16 MHz<br>machine clock<br>$4.5 \text{ V} > AV_{CC} \ge 4.0 \text{ V}$ |

| Sampling time                 | -         | -             | 32 tcp *1      | _                 | _                 | ns   | With 16 MHz machine clock $5.5 \text{ V} \ge AV_{CC} \ge 4.5 \text{ V}$     |

|                               |           |               | 128 tcp *1     | _                 | _                 | ns   | With 16 MHz<br>machine clock<br>4.5 V > AVcc ≥ 4.0 V                        |

| Analog port input<br>current  | Iain      | AN0 to<br>AN7 | -              | -                 | 10                | μA   |                                                                             |

| Analog input voltage          | Vain      | AN0 to<br>AN7 | AVss           | -                 | AVR               | V    |                                                                             |

| Reference voltage             | -         | AVR           | AVss + 2.7     | _                 | AVcc              | V    |                                                                             |

| Power supply current          | la        | AVcc          | _              | 3.5               | 7.5               | mA   |                                                                             |

|                               | Іан       | AVcc          | _              | -                 | 5                 | μA   | *2                                                                          |

| Reference voltage             | IR        | AVR           | _              | 165               | 250               | μA   |                                                                             |

| supplying current             | IRH       | AVR           | _              | _                 | 5                 | μA   | *2                                                                          |

| Variation among channels      | -         | AN0 to<br>AN7 | _              | -                 | 4                 | LSB  |                                                                             |

$(Vcc = AVcc = 4.0 \text{ V to } 5.5 \text{ V}, \text{ Vss} = AVss = 0.0 \text{ V}, 3.0 \text{ V} \le AVR - AVss, \text{ T}_{\text{A}} = -40 \text{ }^{\circ}\text{C} \text{ to } +105 \text{ }^{\circ}\text{C})$

\*1: Refer to Clock Timing on AC Characteristics.

\*2: If A/D converter is not operating, a current when CPU is stopped is applicable (Vcc=AVcc=AVR=5.0 V).

### (Continued)