Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | F <sup>2</sup> MC-16LX                                                        |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 16MHz                                                                         |

| Connectivity               | CANbus, SCI, UART/USART                                                       |

| Peripherals                | POR, WDT                                                                      |

| Number of I/O              | 36                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | Mask ROM                                                                      |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x8/10b                                                                   |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 48-LQFP                                                                       |

| Supplier Device Package    | 48-LQFP (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb90387spmt-gs-141 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# DTP/External Interrupt: 4 channels, CAN wakeup: 1channel

Module for activation of expanded intelligent I/O service (EI<sup>2</sup>OS), and generation of external interrupt.

## **Delay Interrupt Generator Module**

Generates interrupt request for task switching.

## 8/10-bit A/D Converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 μs (at 16 MHz machine clock, including sampling time)

## **Program Patch Function**

■ Address matching detection for 2 address pointers.

## MB90387/387S/F387/F387S MB90V495G

| Pin No.  | Pin Name   | Circuit<br>Type | Function                                                                                               |  |

|----------|------------|-----------------|--------------------------------------------------------------------------------------------------------|--|

| 39       | P42        | D               | General-purpose input/output port.                                                                     |  |

|          | SOT1       |                 | Serial data input pin for UART. Valid only when serial data input/output setting on UART is "enabled." |  |

| 40       | P43        | D               | General-purpose input/output port.                                                                     |  |

|          | ТХ         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |  |

| 41       | P44        | D               | General-purpose input/output port.                                                                     |  |

|          | RX         |                 | Transmission output pin for CAN. Valid only when output setting is "enabled."                          |  |

| 42 to 45 | P30 to P33 | D               | General-purpose input/output ports.                                                                    |  |

| 46       | X0A*       | А               | Pin for low-rate oscillation.                                                                          |  |

|          | P35*       |                 | General-purpose input/output port.                                                                     |  |

| 47       | X1A*       | A               | Pin for low-rate oscillation.                                                                          |  |

|          | P36*       | 1               | General-purpose input/output port.                                                                     |  |

| 48       | AVss       | -               | Vss power source input pin for A/D converter.                                                          |  |

\*: MB90387, MB90F387: X1A, X0A MB90387S, MB90F387S: P36, P35

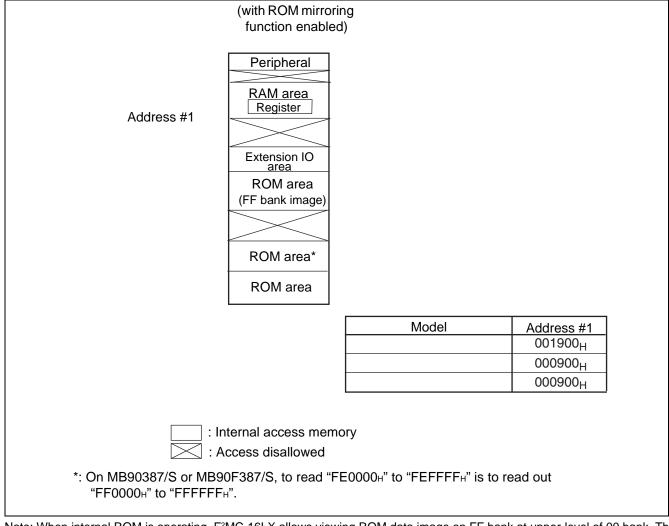

## 9.2 Memory Map

Note: When internal ROM is operating, F<sup>2</sup>MC-16LX allows viewing ROM data image on FF bank at upper-level of 00 bank. This function is called "mirroring ROM," which allows effective use of C compiler small model.

F<sup>2</sup>MC-16LX assigns the same low order 16-bit address to FF bank and 00 bank, which allows referencing table in ROM without specifying "far" using pointer.

For example, when accessing to "00C000H", ROM data at "FFC000H" is accessed actually. However, because ROM area of FF bank exceeds 48 Kbytes, viewing all areas is not possible on 00 bank image. Because ROM data of "FF4000H" to "FFFFFH" is viewed on "004000H" to "00FFFFH" image, store a ROM data table in area "FF4000H" to "FFFFFH."

## 10. I/O Map

| Address                  | Register<br>Abbreviation | Register                                                    | Read/<br>Write | Resource                  | Initial Value |

|--------------------------|--------------------------|-------------------------------------------------------------|----------------|---------------------------|---------------|

| 00000н                   |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000001н                  | PDR1                     | Port 1 data register                                        | R/W            | Port 1                    | XXXXXXXXB     |

| 000002н                  | PDR2                     | Port 2 data register                                        | R/W            | Port 2                    | XXXXXXXXB     |

| 00003н                   | PDR3                     | Port 3 data register                                        | R/W            | Port 3                    | XXXXXXXXB     |

| 000004н                  | PDR4                     | Port 4 data register                                        | R/W            | Port 4                    | XXXXXXXXB     |

| 000005н                  | PDR5                     | Port 5 data register                                        | R/W            | Port 5                    | XXXXXXXXB     |

| 000006н<br>to<br>000010н |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000011н                  | DDR1                     | Port 1 direction data register                              | R/W            | Port 1                    | 0000000в      |

| 000012н                  | DDR2                     | Port 2 direction data register                              | R/W            | Port 2                    | 0000000в      |

| 000013н                  | DDR3                     | Port 3 direction data register                              | R/W            | Port 3                    | 000Х0000в     |

| 000014н                  | DDR4                     | Port 4 direction data register                              | R/W            | Port 4                    | ХХХ00000в     |

| 000015н                  | DDR5                     | Port 5 direction data register                              | R/W            | Port 5                    | 0000000в      |

| 000016н<br>to<br>00001Ан |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00001Bн                  | ADER                     | Analog input permission register                            | R/W            | 8/10-bit A/D<br>converter | 11111111в     |

| 00001Cнto<br>000025н     |                          | (Reserve                                                    | ed area) *     |                           |               |

| 000026н                  | SMR1                     | Serial mode register 1                                      | R/W            | UART1                     | 0000000в      |

| 000027н                  | SCR1                     | Serial control register 1                                   | R/W, W         |                           | 00000100в     |

| 000028н                  | SIDR1/<br>SODR1          | Serial input data register 1/ Serial output data register 1 | R, W           |                           | XXXXXXXXB     |

| 000029н                  | SSR1                     | Serial status data register 1                               | R, R/W         |                           | 00001000в     |

| 00002Ан                  |                          | (Reserve                                                    | ed area) *     |                           |               |

| 00002Вн                  | CDCR1                    | Communication prescaler control register 1                  | R/W            | UART1                     | 0ХХХ0000в     |

| 00002Cнto<br>00002Fн     |                          | (Reserve                                                    | ed area) *     |                           | ·             |

| 000030н                  | ENIR                     | DTP/External interrupt permission register                  | R/W            | DTP/External<br>interrupt | 0000000в      |

| 000031н                  | EIRR                     | DTP/External interrupt permission register                  | R/W            |                           | XXXXXXXXB     |

| 000032н                  | ELVR                     | Detection level setting register                            | R/W            | 1                         | 0000000в      |

| 000033н                  |                          |                                                             | R/W            | 1                         | 0000000в      |

| 000034н                  | ADCS                     | A/D control status register                                 | R/W            | 8/10-bit A/D              | 0000000в      |

| 000035н                  |                          |                                                             | R/W, W         | converter                 | 0000000в      |

| 000036н                  | ADCR                     | A/D data register                                           | W, R           | 1                         | XXXXXXXXB     |

| 000037н                  |                          |                                                             | R              | 1                         | 00101XXXв     |

| Address                  | Register<br>Abbreviation | Register                                  | Read/<br>Write | Resource                                      | Initial Value         |

|--------------------------|--------------------------|-------------------------------------------|----------------|-----------------------------------------------|-----------------------|

| 000038н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| to<br>00003Fн            |                          |                                           |                |                                               |                       |

| 000040н                  | PPGC0                    | PPG0 operation mode control register      | R/W, W         | 8/16-bit PPG timer 0/                         | 0Х000ХХ1в             |

| 000041н                  | PPGC1                    | PPG1 operation mode control register      | R/W, W         |                                               | 0Х00001в              |

| 000042н                  | PPG01                    | PPG0/1 count clock selection register     | R/W            |                                               | 000000XXB             |

| 000043н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000044н                  | PPGC2                    | PPG2 operation mode control register      | R/W, W         | 8/16-bit PPG timer 2/                         | 0X000XX1в             |

| 000045н                  | PPGC3                    | PPG3 operation mode control register      | R/W, W         | 3                                             | 0Х00001в              |

| 000046н                  | PPG23                    | PPG2/3 count clock selection register     | R/W            | 1 [                                           | 00000XXв              |

| 000047н to<br>00004Fн    |                          | (Reserve                                  | ed area) *     | · ·                                           |                       |

| 000050н                  | IPCP0                    | Input capture data register 0             | R              | 16-bit input/output                           | XXXXXXXXB             |

| 000051н                  |                          |                                           |                | timer                                         | XXXXXXXXB             |

| 000052н                  | IPCP1                    | Input capture data register 1             | R              | 1 [                                           | XXXXXXXXB             |

| 000053н                  |                          |                                           |                |                                               | XXXXXXXXB             |

| 000054н                  | ICS01                    | Input capture control status register     | R/W            | 1 [                                           | 0000000в              |

| 000055н                  | ICS23                    | 3                                         |                |                                               | 0000000в              |

| 000056н                  | TCDT                     | Timer counter data register               | R/W            | 1 [                                           | 0000000в              |

| 000057н                  |                          |                                           |                |                                               | 0000000в              |

| 000058н                  | TCCS                     | Timer counter control status register     | R/W            | 1 [                                           | 0000000в              |

| 000059н                  |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 00005Ан                  | IPCP2                    | Input capture data register 2             | R              | 16-bit input/output                           | XXXXXXXXB             |

| 00005Вн                  |                          |                                           |                | timer                                         | XXXXXXXXB             |

| 00005Сн                  | IPCP3                    | Input capture data register 3             | R              | 1 [                                           | XXXXXXXXB             |

| 00005Dн                  |                          |                                           |                |                                               | XXXXXXXXB             |

| 00005Eнto<br>000065н     |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000066н                  | TMCSR0                   | Timer control status register             | R/W            | 16-bit reload timer 0                         | 0000000в              |

| 000067н                  |                          |                                           | R/W            |                                               | XXXX0000 <sub>B</sub> |

| 000068н                  | TMCSR1                   |                                           | R/W            | 16-bit reload timer 1                         | 0000000в              |

| 000069н                  |                          |                                           | R/W            | ] Γ                                           | XXXX0000b             |

| 00006Анto<br>00006Ен     |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 00006Fн                  | ROMM                     | ROM mirroring function selection register | W              | ROM mirroring<br>function selection<br>module | XXXXXXX1B             |

| 000070н<br>to<br>00007Fн |                          | (Reserve                                  | ed area) *     |                                               |                       |

| 000080н                  | BVALR                    | Message buffer enabling register          | R/W            | CAN controller                                | 0000000в              |

| 000081н                  |                          |                                           | ed area) *     |                                               |                       |

| 000082н                  | TREQR                    | Send request register                     | R/W            | CAN controller                                | 0000000в              |

| Address                  | Register<br>Abbreviation                                 | Register                                                | Read/<br>Write | Resource                            | Initial Value         |

|--------------------------|----------------------------------------------------------|---------------------------------------------------------|----------------|-------------------------------------|-----------------------|

| 000083н                  |                                                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000084н                  | TCANR                                                    | Send cancel register                                    | W              | CAN controller                      | 0000000в              |

| 000085н                  |                                                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000086н                  | TCR                                                      | Send completion register                                | R/W            | CAN controller                      | 0000000в              |

| 000087н                  |                                                          | (Reserve                                                | ed area) *     |                                     |                       |

| 000088н                  | RCR                                                      | Receive completion register                             | R/W            | CAN controller                      | 0000000в              |

| 000089н                  |                                                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Ан                  | RRTRR                                                    | Receive RTR register                                    | R/W            | CAN controller                      | 0000000в              |

| 00008Вн                  |                                                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Сн                  | ROVRR                                                    | Receive overrun register                                | R/W            | CAN controller                      | 0000000в              |

| 00008Dн                  |                                                          | (Reserve                                                | ed area) *     |                                     |                       |

| 00008Eн                  | RIER Receive completion interrupt<br>permission register |                                                         | R/W            | CAN controller                      | 0000000в              |

| 00008Fн<br>to<br>00009Dн |                                                          | (Reserv                                                 | ed area) *     |                                     |                       |

| 00009Eн                  | PACSR                                                    | Address detection control register                      | R/W            | Address matching detection function | 0000000в              |

| 00009Fн                  | DIRR                                                     | Delay interrupt request generation/<br>release register | R/W            | Delay interrupt generation module   | XXXXXXX0B             |

| 0000А0н                  | LPMCR                                                    | Lower power consumption mode control register           | W,R/W          | Lower power consumption mode        | 00011000в             |

| 0000A1н                  | CKSCR                                                    | Clock selection register                                | R,R/W          | Clock                               | 11111100в             |

| 0000A2н<br>to<br>0000A7н |                                                          | (Reserv                                                 | ed area) *     |                                     |                       |

| 0000A8н                  | WDTC                                                     | Watchdog timer control register                         | R,W            | Watchdog timer                      | XXXXX111 <sub>B</sub> |

| 0000A9н                  | TBTC                                                     | Time-base timer control register                        | R/W,W          | Time-base timer                     | 1XX00100в             |

| 0000ААн                  | WTC                                                      | Watch timer control register                            | R,R/W          | Watch timer                         | 1Х001000в             |

| 0000ABн<br>to<br>0000ADн |                                                          | (Reserv                                                 | ed area) *     | ·                                   |                       |

| 0000AEн                  | FMCS                                                     | Flash memory control status register                    | R,W,R/W        | 512k-bit Flash<br>memory            | 000X0000 <sub>B</sub> |

| 0000AFн                  |                                                          | (Reserv                                                 | ed area) *     | . 1                                 |                       |

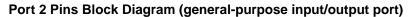

## **Port 2 Registers**

- Port 2 registers include port 2 data register (PDR2) and port 2 direction register (DDR2).

- The bits configuring the register correspond to port 2 pins on a one-to-one basis.

## **Relation between Port 2 Registers and Pins**

| Port Name | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|-----------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 2    | PDR2,DDR2                               | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|           | Corresponding pins                      | P27  | P26  | P25  | P24  | P23  | P22  | P21  | P20  |

## MB90387/387S/F387/F387S MB90V495G

#### Watchdog timer control register(WDTC) Watch timer control register (WTC) WRST ERST SRST WTE WT1 WT0 PONR \_\_\_\_ WDCS Watchdog timer 2, Activate Reset occurs \_ Counter Watchdog Shift to sleep mode -----2-bit Internal reset Count clock reset clear control Shift to time-base counter - 6 generation generation selector circuit timer mode circuit circuit Shift to watch mode Clear Shift to stop mode 4 4 Time-base timer counter Main clock $\times 2^2$ × 28 × 29 × 210 × 211 × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> $\times 2^1$ × 215 × 216 × 2<sup>17</sup> $\times 2^{18}$ (dividing HCLK by 2) Watch counter Sub clock $\times 2^2$ × 2<sup>5</sup> $\times 2^{6}$ × 2<sup>8</sup> × 2<sup>9</sup> × 2<sup>10</sup> × 2<sup>11</sup> × 2<sup>12</sup> × 2<sup>13</sup> × 2<sup>14</sup> × 2<sup>15</sup> $\times 2^{1}$ $\times 2^7$ . SCLK HCLK: Oscillation clock SCLK: Sub clock

## Watchdog Timer Block Diagram

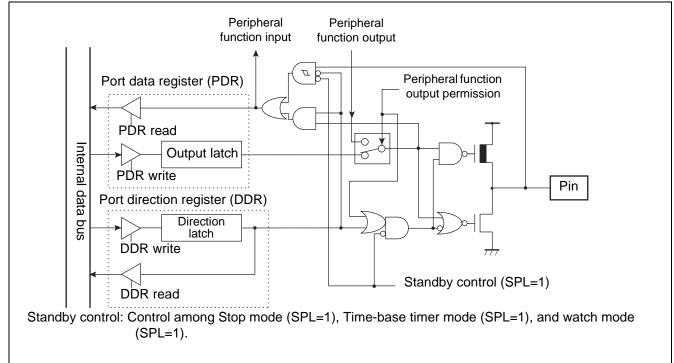

## 12.4 16-bit Input/Output Timer

The 16-bit input/output timer is a compound module composed of 16-bit free-run timer, (1 unit) and input capture (2 units, 4 input pins). The timer, using the 16-bit free-run timer as a basis, enables measurement of clock cycle of an input signal and its pulse width.

## Configuration of 16-bit Input/Output Timer

The 16-bit input/output timer is composed of the following modules:

- 16-bit free-run timer (1 unit)

- Input capture (2 units, 2 input pins per unit)

## Functions of 16-bit Input/Output Timer

#### Functions of 16-bit Free-run Timer

The 16-bit free-run timer is composed of 16-bit up counter, timer counter control status register, and prescaler. The 16-bit up counter increments in synchronization with dividing ratio of machine clock.

- Count clock is set among four types of machine clock dividing rates.

- Generation of interrupt is allowed by counter value overflow.

- Activation of expanded intelligent I/O service (EI<sup>2</sup>OS) is allowed by interrupt generation.

- Counter value of 16-bit free-run timer is cleared to "0000<sup>H</sup>" by either resetting or software-clearing with timer count clear bit (TCCS: CLR).

- Counter value of 16-bit free-run timer is output to input capture, which is available as base time for capture operation.

#### Functions of Input Capture

The input capture, upon detecting an edge of a signal input to the input pin from external device, stores a counter value of 16-bit freerun timer at the time of detection into the input capture data register. The function includes the input capture data registers corresponding to four input pins, input capture control status register, and edge detection circuit.

- Rising edge, falling edge, and both edges are selectable for detection.

- Generating interrupt on CPU is allowed by detecting an edge of input signal.

- Expanded intelligent I/O service (EI<sup>2</sup>OS) is activated by interrupt generation.

- The four input capture input pins and input capture data registers allows monitoring of a maximum of four events.

### 16-bit Input/Output Timer Block Diagram

## 12.5 16-bit Reload Timer

The 16-bit reload timer has the following functions:

- Count clock is selectable among 3 internal clocks and external event clock.

- Activation trigger is selectable between software trigger and external trigger.

- Generation of CPU interrupt is allowed upon occurrence of underflow on 16-bit timer register. Available as an interval timer using the interrupt function.

- When underflow of 16-bit timer register (TMR) occurs, one of two reload modes is selectable between one-shot mode that halts counting operation of TMR, and reload mode that reloads 16-bit reload register value to TMR, continuing TMR counting operation.

- The 16-bit reload timer is ready for expanded intelligent I/O service (El<sup>2</sup>OS).

- MB90385 series device has 2 channels of built-in 16-bit reload timer.

## **Operation Mode of 16-bit Reload Timer**

| Count Clock         | Activation Trigger                 | Operation upon Underflow   |

|---------------------|------------------------------------|----------------------------|

| Internal clock mode | Software trigger, external trigger | One-shot mode, reload mode |

| Event count mode    | Software trigger                   | One-shot mode, reload mode |

## Internal Clock Mode

- The 16-bit reload timer is set to internal clock mode, by setting count clock selection bit (TMCSR: CSL1, CSL0) to "00<sub>B</sub>", "01<sub>B</sub>", "10<sub>B</sub>".

- In the internal clock mode, the counter decrements in synchronization with the internal clock.

- Three types of count clock cycles are selectable by count clock selection bit (TMCSR: CSL1, CSL0) in timer control status register.

- Edge detection of software trigger or external trigger is specified as an activation trigger.

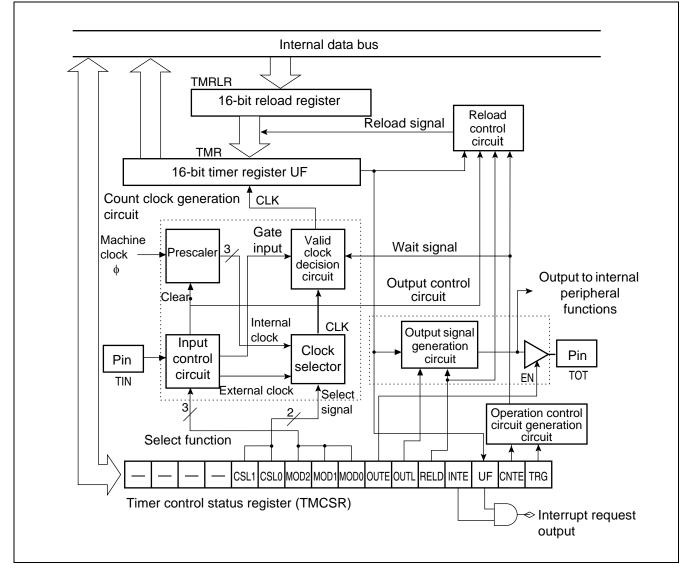

## 16-bit Reload Timer Block Diagram

## 12.7 8/16-bit PPG Timer Outline

The 8/16-bit PPG timer is a 2-channel reload timer module (PPG0 and PPG1) that allows outputting pulses of arbitrary cycle and duty cycle. Combination of the two channels allows selection among the following operations:

- 8-bit PPG output 2-channel independent operation mode

- 16-bit PPG output operation mode

- 8-bit and 8-bit PPG output operation mode

MB90385 series device has two 8/16-bit built-in PPG timers. This section describes functions of PPG0/1. PPG2/3 have the same functions as those of PPG0/1.

## Functions of 8/16-bit PPG Timer

The 8/16-bit PPG timer is composed of four 8-bit reload register (PRLH0/PRLL0, PRLH1/PRLL1) and two PPG down counters (PCNT0, PCNT1).

- Widths of "H" and "L" in output pulse are specifiable independently. Cycle and duty factor of output pulse is specifiable arbitrarily.

- Count clock is selectable among 6 internal clocks.

- The timer is usable as an interval timer, by generating interrupt requests for each interval.

- The time is usable as a D/A converter, with an external circuit.

## 12.10 8/10-bit A/D Converter

The 8/10-bit A/D converter converts an analog input voltage into 8-bit or 10/bit digital value, using the RC-type successive approximation conversion method.

- Input signal is selected among 8 channels of analog input pins.

- Activation trigger is selected among software trigger, internal timer output, and external trigger.

## Functions of 8/10-bit A/D Converter

The 8/10-bit A/D converter converts an analog voltage (input voltage) input to analog input pin into an 8-bit or 10-bit digital value (A/D conversion).

The 8/10-bit A/D converter has the following functions:

- A/D conversion takes a minimum of 6.12 µs\* for 1 channel, including sampling time. (A/D conversion)

- Sampling of one channel takes a minimum of 2.0 µs\*.

- RC-type successive approximation conversion method, with sample & hold circuit is used for conversion.

- Resolution of either 8 bits or 10 bits is specifiable.

- A maximum of 8 channels of analog input pins are allowed for use.

- Generation of interrupt request is allowed, by storing A/D conversion result in A/D data register.

- Activation of EI<sup>2</sup>OS is allowed upon occurrence of an interrupt request. With use of EI<sup>2</sup>OS, data loss is avoided even if A/D conversion is performed successively.

- An activation trigger is selectable among software trigger, internal timer output, and external trigger (fall edge).

- : When operating with 16 MHz machine clock

## 8/10-bit A/D Converter Conversion Mode

| Conversion Mode            | Description                                                                                                                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Singular conversion mode   | The A/D conversion is performed form a start channel to an end channel sequentially. Upon completion of A/D conversion on an end channel, A/D conversion function stops.                          |

| Sequential conversion mode | The A/D conversion is performed form a start channel to an end channel sequentially. Upon completion of A/D conversion on an end channel, A/D conversion function resumes from the start channel. |

| Pausing conversion mode    | The A/D conversion is performed by pausing at each channel. Upon completion of A/D conversion on an end channel, A/D conversion and pause functions resume from the start channel.                |

## 12.11 UART Outline

UART is a general-purpose serial data communication interface for synchronous and asynchronous communication using external devices.

- Provided with bi-directional communication function for both clock-synchronous and clock-asynchronous modes.

- Provided with master/slave communication function (multi-processor mode). (Only master side is available.)

- Interrupt request is generated upon completion of reception, completion of transmission and detection of reception error.

- Ready for expanded intelligent service, El<sup>2</sup>OS.

## Table 12-3. UART Functions

|                                                                             | Description                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data buffer                                                                 | Full-duplex double buffer                                                                                                                                                                                                     |

| Transmission mode                                                           | Clock synchronous (No start/stop bit, no parity bit)<br>Clock asynchronous (start-stop synchronous)                                                                                                                           |

| Baud rate                                                                   | Built-in special-purpose baud-rate generator. Setting is selectable among 8<br>values.<br>Input of external values is allowed.<br>Use of clock from external timer (16-bit reload timer 0) is allowed.                        |

| Data length                                                                 | 7 bits (only asynchronous normal mode)<br>8 bits                                                                                                                                                                              |

| Signaling system                                                            | Non Return to Zero (NRZ) system                                                                                                                                                                                               |

| Reception error detection                                                   | Framing error<br>Overrun error<br>Parity error (not detectable in operation mode 1 (multi-processor mode))                                                                                                                    |

| Interrupt request                                                           | Receive interrupt (reception completed, reception error detected)<br>Transmission interrupt (transmission completed)<br>Ready for expanded intelligent I/O service (El <sup>2</sup> OS) in both transmission and<br>reception |

| Master/slave communication function<br>(asynchronous, multi-processor mode) | Communication between 1 (master) and n (slaves) are available (usable as master only).                                                                                                                                        |

Note: Start/stop bit is not added upon clock-synchronous transmission. Data only is transmitted.

#### Table 12-4. UART Operation Modes

|   | Operation Mode                     | Data L         | ength          | Synchronization | Stop Bit Length    |  |

|---|------------------------------------|----------------|----------------|-----------------|--------------------|--|

|   | Operation mode                     | With Parity    | Without Parity | Synchronization |                    |  |

| 0 | Asynchronous mode<br>(normal mode) | 7-bit or 8-bit |                | Asynchronous    | 1- bit or 2-bit *2 |  |

| 1 | Multi processor mode               | 8+1*1 –        |                | Asynchronous    |                    |  |

| 2 | Synchronous mode                   | 8 –            |                | Synchronous     | No                 |  |

#### -: Disallowed

1: "+1" is an address/data selection bit used for communication control (bit 11 of SCR1 register: A/D).

2: Only 1 bit is detected as a stop bit on data reception.

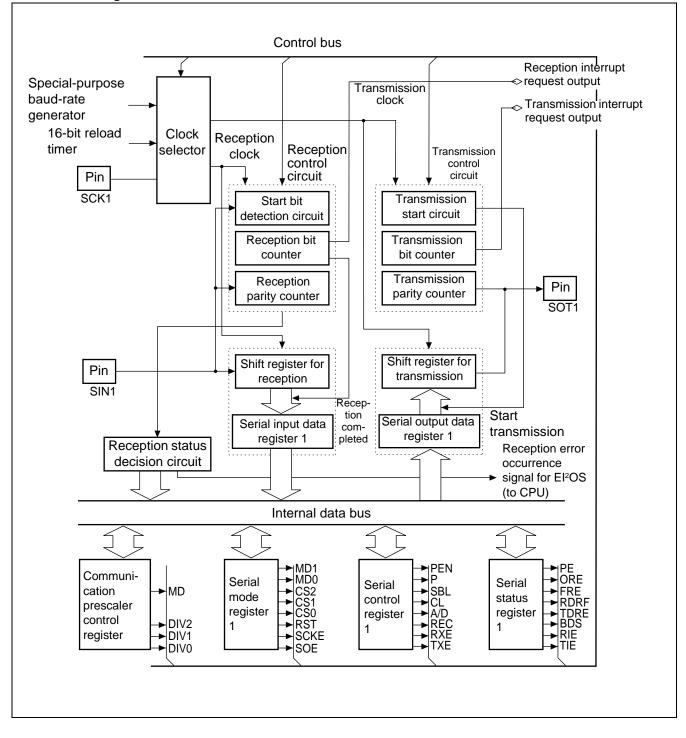

## **UART Block Diagram**

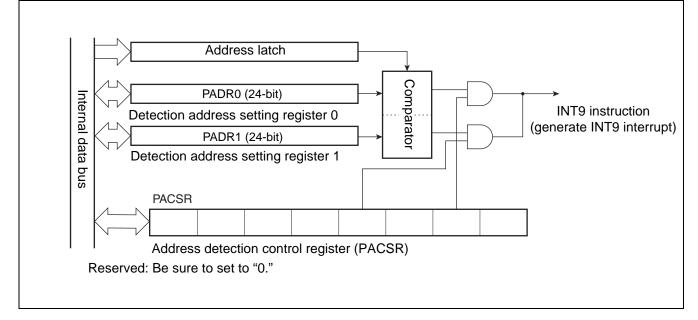

## 12.13 Address Matching Detection Function Outline

The address matching detection function checks if an address of an instruction to be processed next to a currently-processed instruction is identical with an address specified in the detection address register. If the addresses match with each other, an instruction to be processed next in program is forcibly replaced with INT9 instruction, and process branches to the interrupt process program. Using INT9 interrupt, this function is available for correcting program by batch processing.

## Address Matching Detection Function Outline

- An address of an instruction to be processed next to a currently-processed instruction of the program is always retained in an address latch via internal data bus. By the address matching detection function, the address value retained in the address latch is always compared with an address specified in detection address setting register. If the compared address values match with each other, an instruction to be processed next by CPU is forcibly replaced with INT9 instruction, and an interrupt process program is executed.

- Two detection address setting registers are provided (PADR0 and PADR1), and each register is provided with interrupt permission bit. Generation of interrupt, which is caused by address matching between the address retained in address latch and the address specified in address setting register, is permitted and prohibited on a register-by-register basis.

#### Address Matching Detection Function Block Diagram

Address latch

Retains address value output to internal data bus.

- Address detection control register (PACSR) Specifies if interrupt is permitted or prohibited when addresses match with each other.

- Detection address setting (PADR0, PADR1) Specifies addresses to be compared with values in address latch.

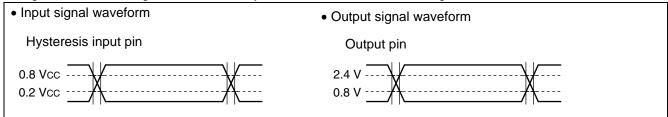

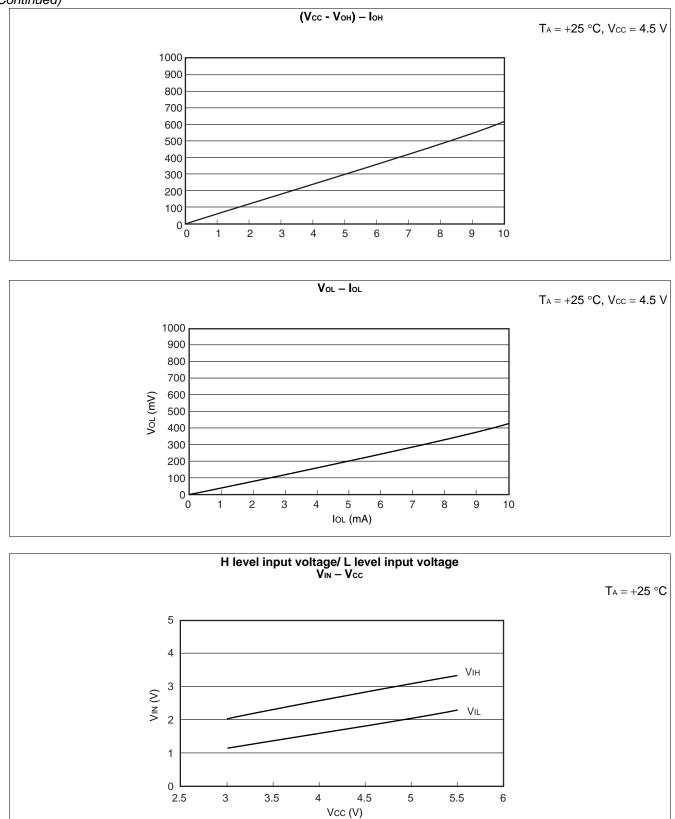

Rating values of alternating current is defined by the measurement reference voltage values shown below:

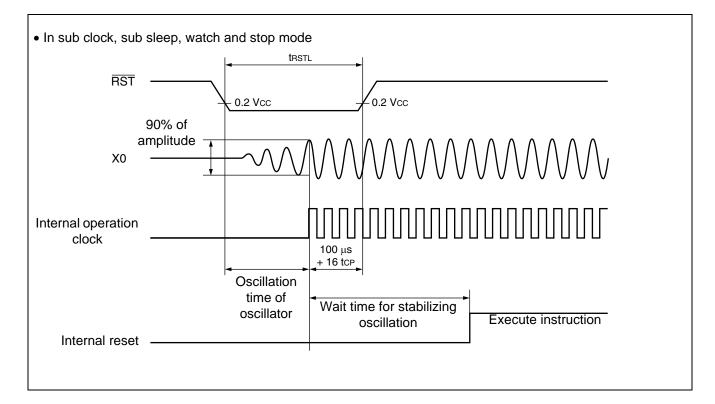

#### 13.4.2 Reset Input Timing

| Parameter Symbol |               | Din Namo | Value                                                                          | Unit | Remarks |                                                                                                |

|------------------|---------------|----------|--------------------------------------------------------------------------------|------|---------|------------------------------------------------------------------------------------------------|

|                  |               |          | Min                                                                            | Max  | Onit    | Nemarks                                                                                        |

| Reset input time | <b>t</b> RSTL | RST      | 16 tce*3                                                                       | -    | ns      | Normal operation                                                                               |

|                  |               |          | Oscillation time of oscillator <sup>*1</sup> + $100 \ \mu s$ + $16 \ tcP^{*3}$ | -    |         | In sub clock <sup>*2</sup> , sub<br>sleep <sup>*2</sup> , watch <sup>*2</sup> and<br>stop mode |

|                  |               |          | 100                                                                            | _    | μS      | In timebase timer                                                                              |

\*1: Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

\*2: Except for MB90F387S and MB90387S.

\*3: Refer to "(1) Clock timing" ratings for tcp (internal operation clock cycle time).

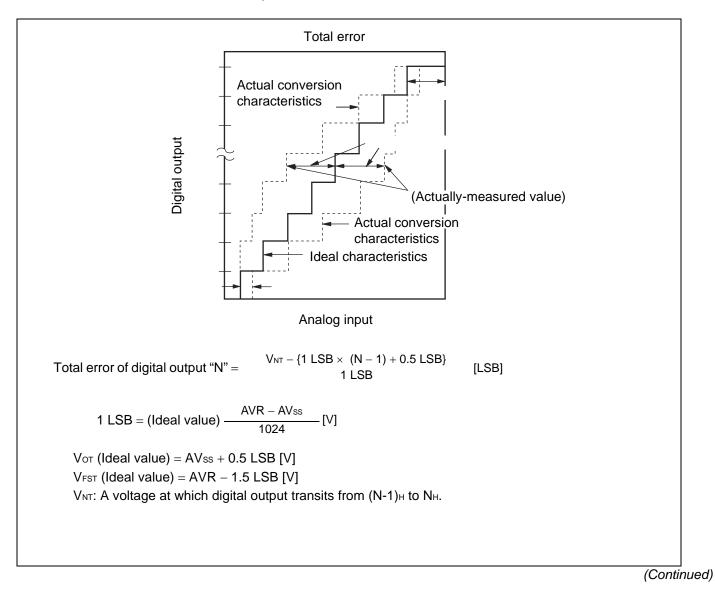

## **13.6 Definition of A/D Converter Terms**

| Resolution:                | Analog variation that is recognized by an A/D converter.                                                                                                                                                                           |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Linear error:              | Deviation between a line across zero-transition line ("00 0000 00 0 0" $\leftrightarrow$ "00 0000 0001") and full-scale transition line ("11 1111 11 1 0" $\leftrightarrow$ "11 1111 1111") and actual conversion characteristics. |

| Differential linear error: | Deviation of input voltage, which is required for changing output code by 1 LSB, from an ideal value.                                                                                                                              |

| Total error:               | Difference between an actual value and an ideal value. A total error includes zero transition error, full-<br>scale transition error, and linear error.                                                                            |

## MB90387/387S/F387/F387S MB90V495G

## (Continued)

## Sales, Solutions, and Legal Information

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

**PSoC®** Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

## Cypress Developer Community

Community | Projects | Video | Blogs | Training | Components

Technical Support cypress.com/support

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

<sup>©</sup> Cypress Semiconductor Corporation, 2004-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or system could cause personal injury, death, or properly damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify a