Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| ackage / Case             | 48-LQFP                 |

|---------------------------|-------------------------|

| ounting Type              | Surface Mount           |

| perating Temperature      | -40°C ~ 105°C (TA)      |

| scillator Type            | External                |

| ata Converters            | A/D 8x8/10b             |

| oltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V             |

| M Size                    | 2K x 8                  |

| PROM Size                 | -                       |

| ogram Memory Type         | Mask ROM                |

| ogram Memory Size         | 64KB (64K x 8)          |

| nber of I/O               | 36                      |

| pherals                   | POR, WDT                |

| nnectivity                | CANbus, SCI, UART/USART |

| eed                       | 16MHz                   |

| re Size                   | 16-Bit                  |

| ore Processor             | F <sup>2</sup> MC-16LX  |

| duct Status               | Active                  |

# 16-bit Microcontrollers F2MC-16LX MB90385 Series

MB90385 series devices are general-purpose high-performance 16-bit micro controllers designed for process control of consumer products, which require high-speed real-time processing. The devices of this series have the built-in full-CAN interface.

The system, inheriting the architecture of F<sup>2</sup>MC family, employs additional instruction ready for high-level languages, expanded addressing mode, enhanced multiply-divide instructions, and enriched bit-processing instructions. Furthermore, employment of 32-bit accumulator achieves processing of long-word data (32 bits).

The peripheral resources of MB90385 series include the following:

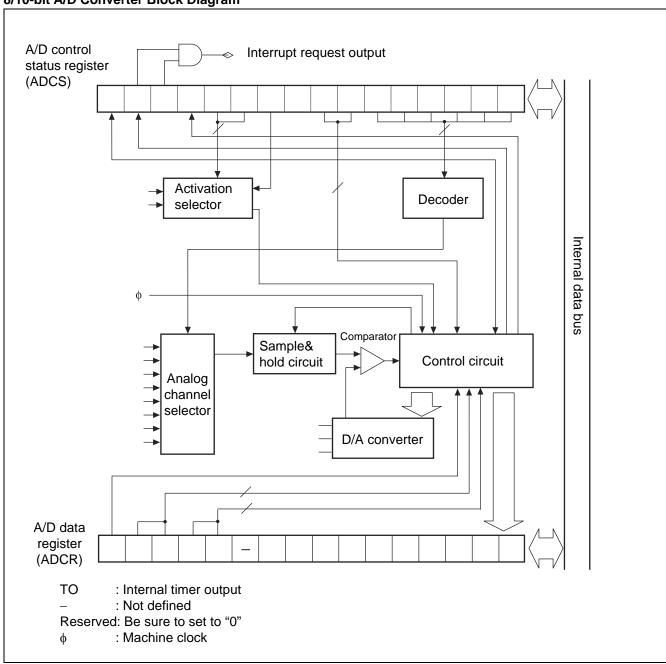

8/10-bit A/D converter, UART (SCI), 8/16-bit PPG timer, 16-bit input-output timer (16-bit free-run timer, input capture 0, 1, 2, 3 (ICU)), and CAN controller.

## **Features**

#### Clock

- Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 4 times of oscillation clock (for 4-MHz oscillation clock, 4 MHz to 16 MHz).

- Operation by sub-clock (8.192 kHz) is allowed. (MB90387, MB90F387)

- Minimum execution time of instruction: 62.5 ns (when operating with 4-MHz oscillation clock, and 4-time multiplied PLL clock).

# 16 Mbyte CPU memory Space

■ 24-bit internal addressing

#### **Instruction System Best Suited to Controller**

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions and RETI instructions

- Enhanced high-precision computing with 32-bit accumulator

# Instruction System Compatible with High-level Language (C language) and Multitask

- Employing system stack pointer

- Enhanced various pointer indirect instructions

- Barrel shift instructions

#### **Increased Processing Speed**

■ 4-byte instruction queue

# Powerful Interrupt Function with 8 Levels and 34 Factors

## **Automatic Data Transfer Function Independent of CPU**

■ Expanded intelligent I/O service function (EI² OS): Maximum of 16 channels

# Low Power Consumption (standby) Mode

■ Sleep mode (a mode that halts CPU operating clock)

- Time-base timer mode (a mode that operates oscillation clock, sub clock, time-base timer and watch timer only)

- Watch mode (a mode that operates sub clock and watch timer only)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU blocking operation mode

#### **Process**

■ CMOS technology

#### I/O Port

■ General-purpose input/output port (CMOS output):

MB90387, MB90F387: 34 ports (including 4 high-current output ports)

MB90387S, MB90F387S: 36 ports (including 4 high-current output ports)

#### Timer

- Time-base timer, watch timer, watchdog timer: 1 channel

- 8/16-bit PPG timer: 8-bit x 4 channels, or 16-bit x 2 channels

- 16-bit reload timer: 2 channels

- 16-bit input/output timer

- 16-bit free run timer: 1 channel

- □ 16-bit input capture: (ICU): 4 channels

Interrupt request is issued upon latching a count value of 16-bit free run timer by detection of an edge on pin input.

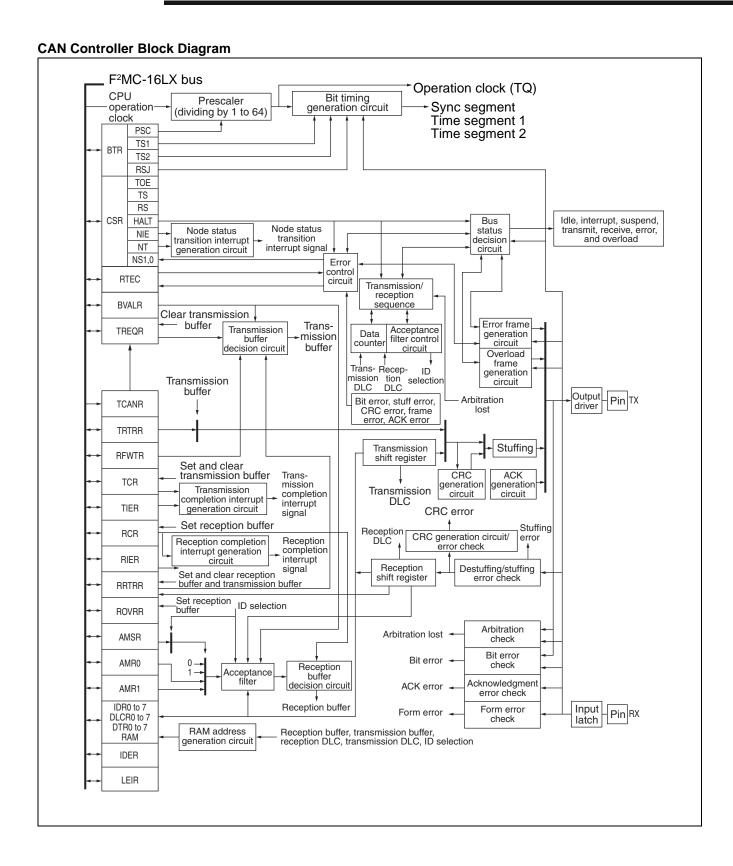

## **CAN Controller: 1 channel**

- Compliant with Ver2.0A and Ver2.0B CAN specifications

- 8 built-in message buffers

- Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)

- CAN wake-up

# **UART (SCI): 1 channel**

- Equipped with full-duplex double buffer

- Clock-asynchronous or clock-synchronous serial transmission is available.

# 6. I/O Circuit Type

| Туре | Circuit                                                                                                                  | Remarks                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| A    | X1<br>X1A<br>X0<br>X0A  Standby control signal                                                                           | <ul> <li>High-rate oscillation feedback resistor, approx.1 MΩ</li> <li>Low-rate oscillation feedback resistor, approx.10 MΩ</li> </ul> |

| В    | R R Hysteresis input                                                                                                     | <ul> <li>■ Hysteresis input with pull-up resistor.</li> <li>■ Pull-up resistor, approx.50 kΩ</li> </ul>                                |

| С    | R                                                                                                                        | ■ Hysteresis input                                                                                                                     |

| D    | P-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  Standby control | <ul> <li>■ CMOS hysteresis input</li> <li>■ CMOS level output</li> <li>■ Standby control provided</li> </ul>                           |

| E    | P-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  Standby control  Analog input        | ■ CMOS hysteresis input ■ CMOS level output ■ Shared for analog input pin ■ Standby control provided                                   |

| Туре | Circuit                                                                                                 | Remarks                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | R                                                                                                       | <ul> <li>Hysteresis input with pull-down resistor</li> <li>Pull-down resistor, approx. 50 kΩ</li> <li>Flash product is not provided with pull-down resistor.</li> </ul> |

|      | R                                                                                                       | Tedition.                                                                                                                                                               |

| G    | P-ch High-current output  High-current output  N-ch  N-ch  Vss  CMOS  hysteresis input  Standby control | <ul> <li>■ CMOS hysteresis input</li> <li>■ CMOS level output (high-current output)</li> <li>■ Standby control provided</li> </ul>                                      |

# 7. Handling Devices

# Do Not Exceed Maximum Rating (preventing "latch up")

- On a CMOS IC, latch-up may occur when applying a voltage higher than Vcc or a voltage lower than Vss to input or output pin, which has no middle or high withstand voltage. Latch-up may also occur when a voltage exceeding maximum rating is applied across Vcc pin and Vss pin.

- Latch-up causes drastic increase of power current, which may lead to destruction of elements by heat. Extreme caution must be taken not to exceed maximum rating.

- When turning on and off analog power source, take extra care not to apply an analog power voltages (AVcc and AVR) and analog input voltage that are higher than digital power voltage (Vcc).

## **Handling Unused Pins**

Leaving unused input pins open may cause permanent destruction by malfunction or latch-up. Apply pull-up or pull-down process to the unused pins using resistors of 2 kΩ or higher. Leave unused input/output pins open under output status, or process as input pins if they are under input status.

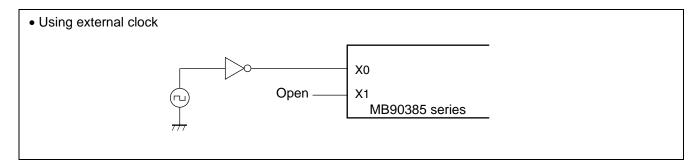

## **Using External Clock**

■ When using an external clock, drive only X0 pin and leave X1 pin open. An example of using an external clock is shown below.

Document Number: 002-07765 Rev. \*A

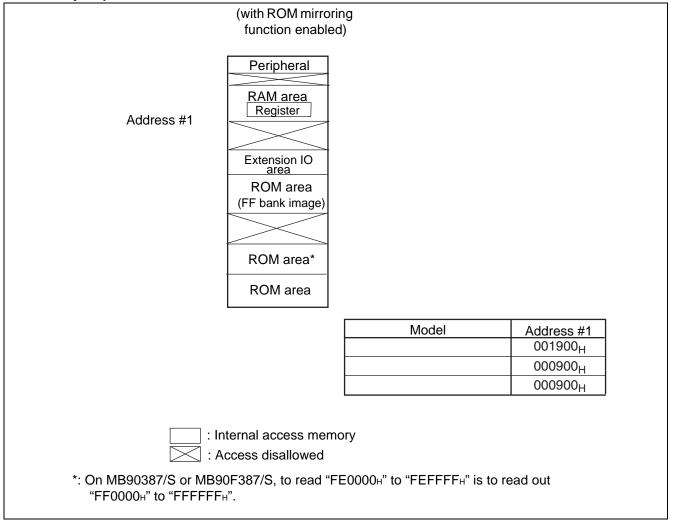

# 9.2 Memory Map

Note: When internal ROM is operating, F<sup>2</sup>MC-16LX allows viewing ROM data image on FF bank at upper-level of 00 bank. This function is called "mirroring ROM," which allows effective use of C compiler small model.

F<sup>2</sup>MC-16LX assigns the same low order 16-bit address to FF bank and 00 bank, which allows referencing table in ROM without specifying "far" using pointer.

For example, when accessing to "00C000H", ROM data at "FFC000H" is accessed actually. However, because ROM area of FF bank exceeds 48 Kbytes, viewing all areas is not possible on 00 bank image. Because ROM data of "FF4000H" to "FFFFFH" is viewed on "004000H" to "00FFFFH" image, store a ROM data table in area "FF4000H" to "FFFFFFH."

| Address             | Register<br>Abbreviation | Register                                  | Read/<br>Write | Resource                                | Initial Value         |

|---------------------|--------------------------|-------------------------------------------|----------------|-----------------------------------------|-----------------------|

| 000038н             |                          | (Reserve                                  | ed area) *     |                                         |                       |

| to<br>00003Fн       |                          |                                           |                |                                         |                       |

| 000040н             | PPGC0                    | PPG0 operation mode control register      | R/W, W         | 8/16-bit PPG timer 0/                   | 0Х000ХХ1в             |

| 000041н             | PPGC1                    | PPG1 operation mode control register      | R/W, W         | 71                                      | 0Х00001в              |

| 000042н             | PPG01                    | PPG0/1 count clock selection register     | R/W            |                                         | 000000XXB             |

| 000043н             |                          | (Reserve                                  | ed area) *     | ·                                       |                       |

| 000044н             | PPGC2                    | PPG2 operation mode control register      | R/W, W         | 8/16-bit PPG timer 2/                   | 0Х000ХХ1в             |

| 000045н             | PPGC3                    | PPG3 operation mode control register      | R/W, W         | ]3                                      | 0Х000001в             |

| 000046н             | PPG23                    | PPG2/3 count clock selection register     | R/W            | ]                                       | 000000XXв             |

| 00047нto<br>00004Fн |                          | (Reserve                                  | ed area) *     |                                         |                       |

| 000050н             | IPCP0                    | Input capture data register 0             | R              | 16-bit input/output                     | XXXXXXXXB             |

| 000051н             |                          |                                           |                | timer                                   | XXXXXXXXB             |

| 000052н             | IPCP1                    | Input capture data register 1             | R              |                                         | XXXXXXXXB             |

| 000053н             |                          |                                           |                |                                         | XXXXXXXXB             |

| 000054н             | ICS01                    | Input capture control status register     | R/W            |                                         | 0000000в              |

| 000055н             | ICS23                    |                                           |                |                                         | 0000000В              |

| 000056н             | TCDT                     | Timer counter data register               | R/W            |                                         | 0000000В              |

| 000057н             |                          |                                           |                |                                         | 0000000В              |

| 000058н             | TCCS                     | Timer counter control status register     | R/W            |                                         | 0000000В              |

| 000059н             |                          | (Reserve                                  | ed area) *     |                                         |                       |

| 00005Ан             | IPCP2                    | Input capture data register 2             | R              | 16-bit input/output                     | XXXXXXXXB             |

| 00005Вн             |                          |                                           |                | timer                                   | XXXXXXXX              |

| 00005Сн             | IPCP3                    | Input capture data register 3             | R              |                                         | XXXXXXXX              |

| 00005Dн             |                          |                                           |                |                                         | XXXXXXXX              |

| 0005Eнtо<br>000065н |                          | (Reserve                                  | ed area) *     |                                         |                       |

| 000066н             | TMCSR0                   | Timer control status register             | R/W            | 16-bit reload timer 0                   | 0000000в              |

| 000067н             |                          |                                           | R/W            | ]                                       | XXXX0000 <sub>B</sub> |

| 000068н             | TMCSR1                   |                                           | R/W            | 16-bit reload timer 1                   | 0000000в              |

| 000069н             |                          |                                           | R/W            |                                         | XXXX0000 <sub>B</sub> |

| 0006Анtо<br>00006Ен |                          | (Reserve                                  | ed area) *     | <u>'</u>                                |                       |

| 00006Fн             | ROMM                     | ROM mirroring function selection register | W              | ROM mirroring function selection module | XXXXXXX1 <sub>B</sub> |

| 000070н             |                          | (Reserve                                  | ed area) *     |                                         |                       |

| to<br>00007Fн       |                          |                                           |                |                                         |                       |

| н080000             | BVALR                    | Message buffer enabling register          | R/W            | CAN controller                          | 0000000В              |

| 000081н             |                          | (Reserve                                  | ed area) *     |                                         |                       |

| 000082н             | TREQR                    | Send request register                     | R/W            | CAN controller                          | 0000000В              |

| Address                  | Register<br>Abbreviation | Register               | Read/<br>Write     | Resource           | Initial Value                                    |

|--------------------------|--------------------------|------------------------|--------------------|--------------------|--------------------------------------------------|

| 003910н                  | PRLL0                    | PPG0 reload register L | R/W                | 8/16-bit PPG timer | XXXXXXXXB                                        |

| 003911н                  | PRLH0                    | PPG0 reload register H | R/W                |                    | XXXXXXXXB                                        |

| 003912н                  | PRLL1                    | PPG1 reload register L | R/W                |                    | XXXXXXXXB                                        |

| 003913н                  | PRLH1                    | PPG1 reload register H | R/W                |                    | XXXXXXXXB                                        |

| 003914н                  | PRLL2                    | PPG2 reload register L | R/W                |                    | XXXXXXXXB                                        |

| 003915н                  | PRLH2                    | PPG2 reload register H | R/W                |                    | XXXXXXXXB                                        |

| 003916н                  | PRLL3                    | PPG3 reload register L | R/W                |                    | XXXXXXXXB                                        |

| 003917н                  | PRLH3                    | PPG3 reload register H | R/W                |                    | XXXXXXXXB                                        |

| 003918н<br>to<br>00392Fн |                          |                        | (Reserved area) *  |                    |                                                  |

| 003930н<br>to<br>003BFFн |                          |                        | (Reserved area) *  |                    |                                                  |

| 003С00н<br>to<br>003С0Fн |                          | RAM                    | (General-purpose R | AM)                |                                                  |

| 003С10н<br>to<br>003С13н | IDR0                     | ID register 0          | R/W                | CAN controller     | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С14н<br>to<br>003С17н | IDR1                     | ID register 1          | R/W                |                    | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С18н<br>to<br>003С1Вн | IDR2                     | ID register 2          | R/W                |                    | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С1Сн<br>to<br>003С1Fн | IDR3                     | ID register 3          | R/W                |                    | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С20н<br>to<br>003С23н | IDR4                     | ID register 4          | R/W                |                    | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С24н<br>to<br>003С27н | IDR5                     | ID register 5          | R/W                |                    | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С28н<br>to<br>003С2Вн | IDR6                     | ID register 6          | R/W                |                    | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С2Сн<br>to<br>003С2Fн | IDR7                     | ID register 7          | R/W                |                    | XXXXXXXB<br>to<br>XXXXXXXXB                      |

| 003С30н,<br>003С31н      | DLCR0                    | DLC register 0         | R/W                |                    | XXXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub> |

| 003С32н,<br>003С33н      | DLCR1                    | DLC register 1         | R/W                |                    | XXXXXXXB,<br>XXXXXXXXB                           |

| 003С34н,<br>003С35н      | DLCR2                    | DLC register 2         | R/W                |                    | XXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub>  |

| 003С36н,<br>003С37н      | DLCR3                    | DLC register 3         | R/W                |                    | XXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub>  |

# 11. Interrupt Sources, Interrupt Vectors, And Interrupt Control Registers

| Intermed Course                                                          | El²OS     | I   | nterrup | t Vector            | Interrupt C | Priority*3             |          |

|--------------------------------------------------------------------------|-----------|-----|---------|---------------------|-------------|------------------------|----------|

| Interrupt Source                                                         | Readiness | Nur | nber    | Address             | ICR         | Address                | Filolity |

| Reset                                                                    | ×         | #08 | 08н     | FFFFDCH             | -           | -                      | High     |

| INT 9 instruction                                                        | ×         | #09 | 09н     | FFFFD8 <sub>H</sub> | -           | _                      | <b>↑</b> |

| Exceptional treatment                                                    | ×         | #10 | 0Ан     | FFFFD4 <sub>H</sub> | -           | _                      |          |

| CAN controller reception completed (RX)                                  | ,         | #11 | 0Вн     | FFFFD0 <sub>H</sub> | ICR00       | 0000В0н*1              |          |

| CAN controller transmission completed (TX) / Node status transition (NS) | ,         | #12 | 0Сн     | FFFFCC <sub>H</sub> |             |                        |          |

| Reserved                                                                 | ×         | #13 | 0Дн     | FFFFC8 <sub>H</sub> | ICR01       | 0000В1н                |          |

| Reserved                                                                 | ×         | #14 | 0Ен     | FFFFC4 <sub>H</sub> |             |                        |          |

| CAN wakeup                                                               | Δ         | #15 | 0Fн     | FFFFC0 <sub>H</sub> | ICR02       | 0000В2н*1              |          |

| Time-base timer                                                          | ×         | #16 | 10н     | FFFFBCH             | -           |                        |          |

| 16-bit reload timer 0                                                    | Δ         | #17 | 11н     | FFFFB8 <sub>H</sub> | ICR03       | 0000ВЗн*1              |          |

| 8/10-bit A/D converter                                                   | Δ         | #18 | 12н     | FFFFB4 <sub>H</sub> |             |                        |          |

| 16-bit free-run timer overflow                                           | Δ         | #19 | 13н     | FFFFB0 <sub>H</sub> | ICR04       | 0000В4н*1              |          |

| Reserved                                                                 | ×         | #20 | 14н     | FFFFACH             |             |                        |          |

| Reserved                                                                 | ×         | #21 | 15н     | FFFFA8 <sub>H</sub> | ICR05       | 0000В5н*1              |          |

| PPG timer ch0, ch1 underflow                                             | ,         | #22 | 16н     | FFFFA4 <sub>H</sub> |             |                        |          |

| Input capture 0-input                                                    | Δ         | #23 | 17н     | FFFFA0 <sub>H</sub> | ICR06       | 0000В6н*1              |          |

| External interrupt (INT4/INT5)                                           | Δ         | #24 | 18н     | FFFF9C <sub>H</sub> |             |                        |          |

| Input capture 1-input                                                    | Δ         | #25 | 19н     | FFFF98 <sub>H</sub> | ICR07       | 0000В7н*2              |          |

| PPG timer ch2, ch3 underflow                                             | ,         | #26 | 1Ан     | FFFF94 <sub>H</sub> |             |                        |          |

| External interrupt (INT6/INT7)                                           | Δ         | #27 | 1Вн     | FFFF90 <sub>H</sub> | ICR08       | 0000В8н*1              |          |

| Watch timer                                                              | Δ         | #28 | 1Сн     | FFFF8C <sub>H</sub> |             |                        |          |

| Reserved                                                                 | ×         | #29 | 1Dн     | FFFF88 <sub>H</sub> | ICR09       | 0000В9н*1              |          |

| Input capture 2-input<br>Input capture 3-input                           | ,         | #30 | 1Ен     | FFFF84 <sub>H</sub> |             |                        |          |

| Reserved                                                                 | ×         | #31 | 1Fн     | FFFF80 <sub>H</sub> | ICR10       | 0000ВАн*1              | 1        |

| Reserved                                                                 | ×         | #32 | 20н     | FFFF7C <sub>H</sub> |             |                        |          |

| Reserved                                                                 | ×         | #33 | 21н     | FFFF78 <sub>H</sub> | ICR11       | 0000BB <sub>H</sub> *1 |          |

| Reserved                                                                 | ×         | #34 | 22н     | FFFF74 <sub>H</sub> |             |                        |          |

| Reserved                                                                 | ×         | #35 | 23н     | FFFF70 <sub>H</sub> | ICR12       | 0000ВСн*1              | →        |

| 16-bit reload timer 1                                                    | 0         | #36 | 24н     | FFFF6C <sub>H</sub> |             |                        | Low      |

Document Number: 002-07765 Rev. \*A Page 21 of 81

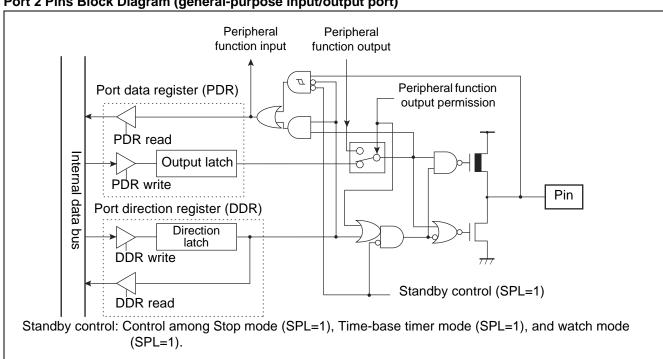

# Port 2 Pins Block Diagram (general-purpose input/output port)

# **Port 2 Registers**

- Port 2 registers include port 2 data register (PDR2) and port 2 direction register (DDR2).

- The bits configuring the register correspond to port 2 pins on a one-to-one basis.

# Relation between Port 2 Registers and Pins

| Port Name          | Bits of Register and Corresponding Pins |      |      |      |      |      |      |      |      |

|--------------------|-----------------------------------------|------|------|------|------|------|------|------|------|

| Port 2             | PDR2,DDR2                               | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| Corresponding pins |                                         | P27  | P26  | P25  | P24  | P23  | P22  | P21  | P20  |

# 12.2 Time-Base Timer

The time-base time is an 18-bit free-run counter (time-base timer counter) that counts up in synchronization with the main clock (dividing main oscillation clock by 2).

- Four choices of interval time are selectable, and generation of interrupt request is allowed for each interval time.

- Provides operation clock signal to oscillation stabilizing wait timer and peripheral functions.

## **Interval Timer Function**

- When the counter of time-base timer reaches an interval time specified by interval time selection bit (TBTC:TBC1, TBC0), an overflow (carrying-over) occurs (TBTC: TBOF=1) and interrupt request is generated.

- If an interrupt by overflow is permitted (TBTC: TBIE=1), an interrupt is generated when overflow occurs (TBTC: TBOF=1).

- The following four interval time settings are selectable:

## **Interval Time of Time-base Timer**

| Count Clock     | Interval Time                          |

|-----------------|----------------------------------------|

| 2/HCLK (0.5 μs) | 212/HCLK (Approx. 1.0 ms)              |

|                 | 2 <sup>14</sup> /HCLK (Approx. 4.1 ms) |

|                 | 216/HCLK (Approx. 16.4 ms)             |

|                 | 219/HCLK (Approx. 131.1 ms)            |

HCLK: Oscillation clock

Values in parentheses "()" are those under operation of 4-MHz oscillation clock.

Document Number: 002-07765 Rev. \*A Page 28 of 81

## 12.5 16-bit Reload Timer

The 16-bit reload timer has the following functions:

- Count clock is selectable among 3 internal clocks and external event clock.

- Activation trigger is selectable between software trigger and external trigger.

- Generation of CPU interrupt is allowed upon occurrence of underflow on 16-bit timer register. Available as an interval timer using the interrupt function.

- When underflow of 16-bit timer register (TMR) occurs, one of two reload modes is selectable between one-shot mode that halts counting operation of TMR, and reload mode that reloads 16-bit reload register value to TMR, continuing TMR counting operation.

- The 16-bit reload timer is ready for expanded intelligent I/O service (El<sup>2</sup>OS).

- MB90385 series device has 2 channels of built-in 16-bit reload timer.

# **Operation Mode of 16-bit Reload Timer**

| Count Clock         | Activation Trigger                 | Operation upon Underflow   |  |  |

|---------------------|------------------------------------|----------------------------|--|--|

| Internal clock mode | Software trigger, external trigger | One-shot mode, reload mode |  |  |

| Event count mode    | Software trigger                   | One-shot mode, reload mode |  |  |

#### **Internal Clock Mode**

- The 16-bit reload timer is set to internal clock mode, by setting count clock selection bit (TMCSR: CSL1, CSL0) to "00<sub>B</sub>", "01<sub>B</sub>", "10<sub>B</sub>".

- In the internal clock mode, the counter decrements in synchronization with the internal clock.

- Three types of count clock cycles are selectable by count clock selection bit (TMCSR: CSL1, CSL0) in timer control status register.

- Edge detection of software trigger or external trigger is specified as an activation trigger.

Document Number: 002-07765 Rev. \*A Page 35 of 81

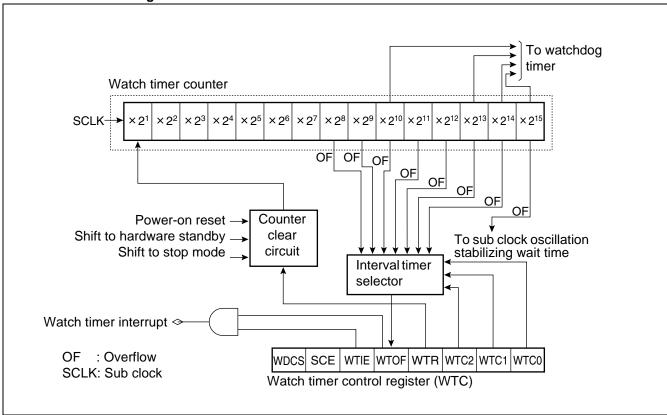

# 12.6 Watch Timer Outline

The watch timer is a 15-bit free-run counter that increments in synchronization with sub clock.

- Interval time is selectable among 7 choices, and generation of interrupt request is allowed for each interval.

- Provides operation clock to the subclock oscillation stabilizing wait timer and watchdog timer.

- Always uses subclock as a count clock regardless of settings of clock selection register (CKSCR).

## **Interval Timer Function**

- In the watch timer, a bit corresponding to the interval time overflows (carry-over) when an interval time, which is specified by interval time selection bit, is reached. Then overflow flag bit is set (WTC: WTOF=1).

- If an interrupt by overflow is permitted (WTC: WTIE=1), an interrupt request is generated upon setting an overflow flag bit.

- Interval time of watch timer is selectable among the following seven choices:

## **Interval Time of Watch Timer**

| Sub Clock Cycle | Interval Time                  |

|-----------------|--------------------------------|

| 1/SCLK (122 μs) | 28/SCLK (31.25 ms)             |

|                 | 29/SCLK (62.5 ms)              |

|                 | 210/SCLK (125 ms)              |

|                 | 2 <sup>11</sup> /SCLK (250 ms) |

|                 | 212/SCLK (500 ms)              |

|                 | 213/SCLK (1.0 s)               |

|                 | 214/SCLK (2.0 s)               |

SCLK: Sub clock frequency

Values in parentheses "()" are calculation when operating with 8.192 kHz clock.

Document Number: 002-07765 Rev. \*A Page 37 of 81

Actual interrupt request number of watch timer is as follows:

Interrupt request number: #28 (1CH)

## **Watch Timer Counter**

A 15-bit up counter that uses sub clock (SCLK) as a count clock.

#### **Counter Clear Circuit**

A circuit that clears the watch timer counter.

# 12.7 8/16-bit PPG Timer Outline

The 8/16-bit PPG timer is a 2-channel reload timer module (PPG0 and PPG1) that allows outputting pulses of arbitrary cycle and duty cycle. Combination of the two channels allows selection among the following operations:

- 8-bit PPG output 2-channel independent operation mode

- 16-bit PPG output operation mode

- 8-bit and 8-bit PPG output operation mode

MB90385 series device has two 8/16-bit built-in PPG timers. This section describes functions of PPG0/1. PPG2/3 have the same functions as those of PPG0/1.

## **Functions of 8/16-bit PPG Timer**

The 8/16-bit PPG timer is composed of four 8-bit reload register (PRLH0/PRLL0, PRLH1/PRLL1) and two PPG down counters (PCNT0, PCNT1).

- Widths of "H" and "L" in output pulse are specifiable independently. Cycle and duty factor of output pulse is specifiable arbitrarily.

- Count clock is selectable among 6 internal clocks.

- The timer is usable as an interval timer, by generating interrupt requests for each interval.

- The time is usable as a D/A converter, with an external circuit.

Document Number: 002-07765 Rev. \*A Page 39 of 81

# 8/10-bit A/D Converter Block Diagram

# MB90387/387S/F387/F387S MB90V495G

(Vcc = 5.0 V±10%, Vss = AVss = 0.0 V, Ta = -40 °C to +105 °C)

| Doromotor             | Cumbal | Pin Name                                      | Conditions                                                                                                                       |     | Value |     | Unit | Remarks                                                         |  |

|-----------------------|--------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|-----------------------------------------------------------------|--|

| Parameter             | Symbol | Pin Name                                      | Conditions                                                                                                                       | Min | Тур   | Max | Unit | Kemarks                                                         |  |

| Power supply current* | Iccl   | Vcc                                           | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>subclock operation,                                                            | _   | 0.3   | 1.2 | mA   | MB90F387/S                                                      |  |

| ourrone               |        |                                               | T <sub>A</sub> = + 25°C                                                                                                          | _   | 40    | 100 | μА   | MB90387/S                                                       |  |

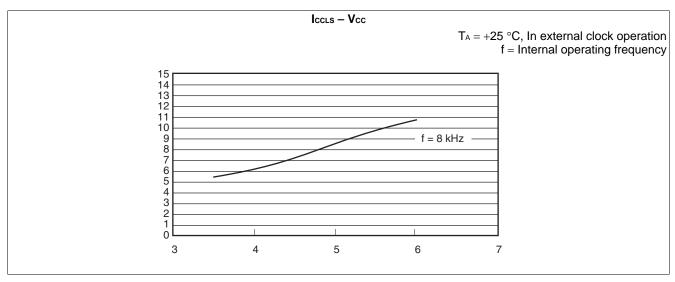

|                       | IccLs  |                                               | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>subclock,<br>sleep mode,<br>T <sub>A</sub> = + 25°C                            | _   | 10    | 30  | μА   |                                                                 |  |

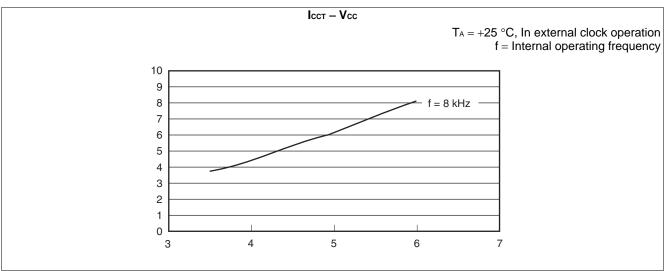

|                       | Ісст   |                                               | Vcc = 5.0 V,<br>Internally operating at 8 kHz,<br>watch mode,<br>T <sub>A</sub> = + 25°C<br>Stopping,<br>T <sub>A</sub> = + 25°C | _   | 8     | 25  | μА   |                                                                 |  |

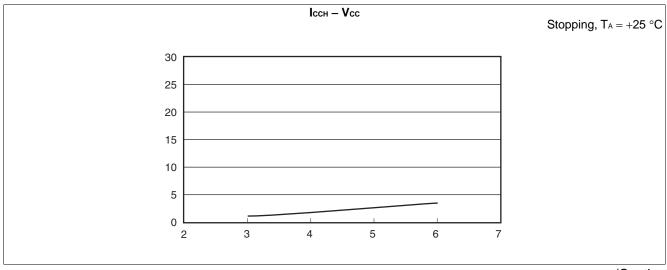

|                       | Іссн   |                                               |                                                                                                                                  | _   | 5     | 20  | μА   |                                                                 |  |

| Input capacity        | Cin    | Other than AVcc,<br>AVss, AVR, C, Vcc,<br>Vss | -                                                                                                                                | _   | 5     | 15  | pF   |                                                                 |  |

| Pull-up<br>resistor   | Rup    | RST                                           | _                                                                                                                                | 25  | 50    | 100 | kΩ   |                                                                 |  |

| Pull-down<br>resistor | RDOWN  | MD2                                           | _                                                                                                                                | 25  | 50    | 100 | kΩ   | Flash product is<br>not provided<br>with pull-down<br>resistor. |  |

<sup>\*:</sup> Test conditions of power supply current are based on a device using external clock.

Document Number: 002-07765 Rev. \*A Page 59 of 81

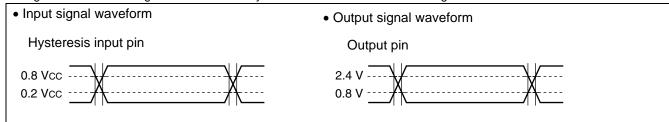

Rating values of alternating current is defined by the measurement reference voltage values shown below:

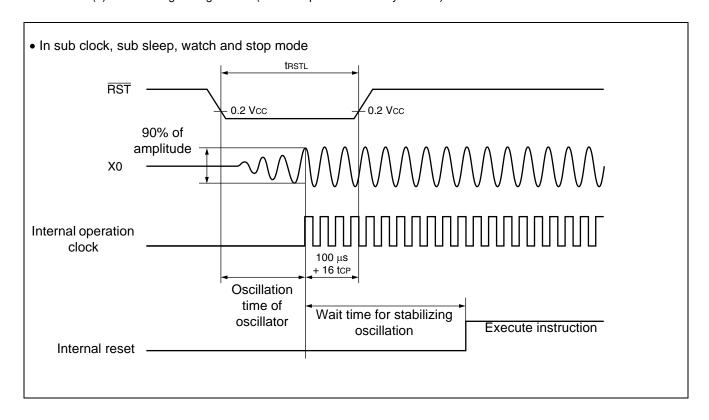

13.4.2 Reset Input Timing

| Parameter        | Symbol          | Din Namo | Value                                                |     | Unit  | Remarks                                                  |  |

|------------------|-----------------|----------|------------------------------------------------------|-----|-------|----------------------------------------------------------|--|

| Parameter        | eter Symbol Pin |          | Min                                                  | Max | Offic | Remarks                                                  |  |

| Reset input time | <b>t</b> RSTL   | RST      | 16 tcp*3                                             | -   | ns    | Normal operation                                         |  |

|                  |                 |          | Oscillation time of oscillator*1 + 100 μs + 16 tcp*3 | -   |       | In sub clock*2, sub<br>sleep*2, watch*2 and<br>stop mode |  |

|                  |                 |          | 100                                                  | _   | μS    | In timebase timer                                        |  |

<sup>\*1:</sup> Oscillation time of oscillator is time that the amplitude reached the 90%. In the crystal oscillator, the oscillation time is between several ms to tens of ms. In ceramic oscillator, the oscillation time is between hundreds of μs to several ms. In the external clock, the oscillation time is 0 ms.

<sup>\*3:</sup> Refer to "(1) Clock timing" ratings for tcp (internal operation clock cycle time).

<sup>\*2:</sup> Except for MB90F387S and MB90387S.

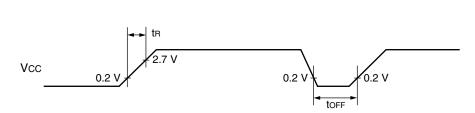

#### 13.4.3 Power-on Reset

$(Vcc = 5.0 \text{ V} \pm 10\%, \text{ Vss} = \text{AVss} = 0.0 \text{ V}, \text{ T}_{A} = -40 \text{ }^{\circ}\text{C to } +105 \text{ }^{\circ}\text{C})$

| Parameter                  | Symbol     | Pin Name | Conditions | Value |     | Unit  | Remarks                     |

|----------------------------|------------|----------|------------|-------|-----|-------|-----------------------------|

| raiailletei                |            |          |            | Min   | Max | Oilit | Remarks                     |

| Power supply rise time     | <b>t</b> R | Vcc      | _          | 0.05  | 30  | ms    |                             |

| Power supply shutdown time | toff       | Vcc      |            | 1     | -   |       | Waiting time until power-on |

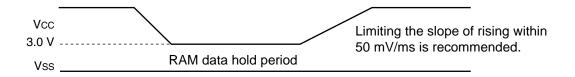

Sudden change of power supply voltage may activate the power-on reset function. When changing power supply voltages during operation, raise the power smoothly by suppressing variation of voltages as shown below. When raising the power, do not use PLL clock. However, if voltage drop is 1V/s or less, use of PLL clock is allowed during operation.

(Continued)